# 8bit Flash MCU, 10bit ADC, E2PROM, 5V

## Description

The EM6819FX-B300 is designed to be battery operated for extended lifetime applications. Its large voltage range from 5V down to 2V makes it a perfect match for today's demanding applications. Brownout and powercheck functions ensure reliable operation at or near undervoltage conditions, offering greater reliability in complex operation modes. Each of the 24 I/Os are freely programmable and the microcontroller has a dual quartz and trimmable RC oscillator up to 15MHz. It has an 8-bit RISC architecture specially designed for very low power consumption. With 2 clocks per instruction, the EM6819FX-B300 executes up to 7.5 MIPS at 15MHz and achieves astonishing 4000 MIPS/Watt.

# Power Management Features for Low-Power application

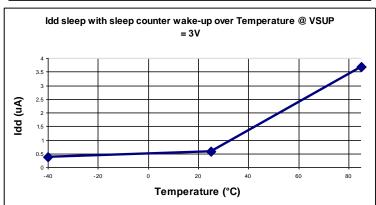

- □ Sleep current 400 nA, typ

- ☐ True low current: typ 126uA at 3V, 1 MIPS

- 800 nA with RTC

- Idle: CPU off, Peripherals on, Currents Down to 770 nA

- Run : CPU on, Peripherals on, Currents Down to 2 uA

## **Features**

- Wide supply voltage range 2V 5V

- ☐ Up to 7.5 MIPS at 15MHz

- On-chip brownout detection

- PowerCheck functions at start-up

- □ 32 Voltage Level Detection on Supply or Input pin

- ☐ 3 terminal Operational Amplifier / Comparator

- □ ADC 10-bit, 8 channel

- □ Temperature sensor

- □ Voltage reference input/output

- ☐ Fast wake-up

- □ Up to 24 fully configurable I/Os

- ☐ Flash read monitoring system

- ☐ Dual clock mode, quartz and RC oscillators:

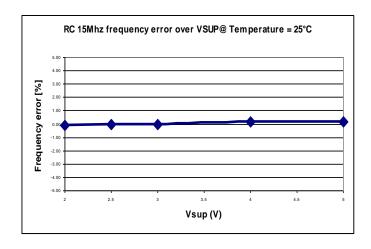

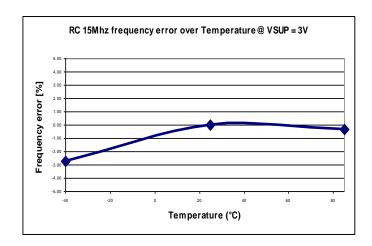

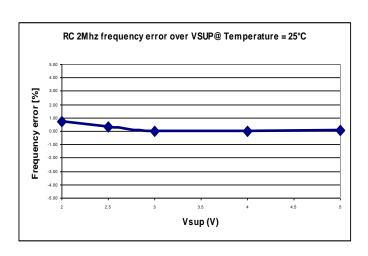

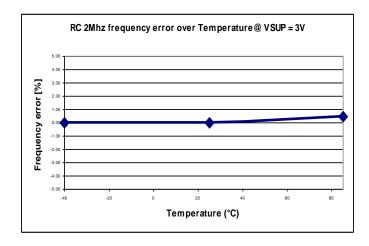

- o 2 MHz 15MHz RC, pre-trimmed

- Low freq RC Oscillator (8kHz)

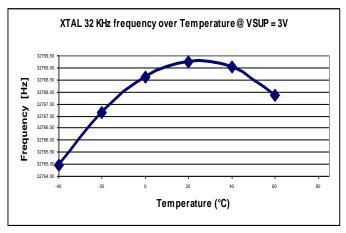

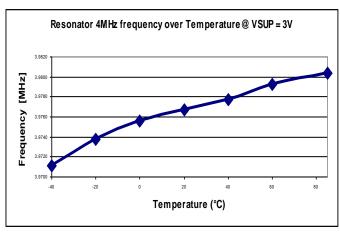

- o 32768 Hz Xtal, 4MHz Resonator, Ext Clock

- 8-bit CoolRISC architecture

- o 16 registers

- o 8\*8bit hardware multiplier

- Power-On-Reset and watchdog

- ☐ GPNVM Memory

- o Sharing Instruction code and data

- ☐ Fully static 512 Byte RAM

- Internal and external interrupts

- □ Frequency generator

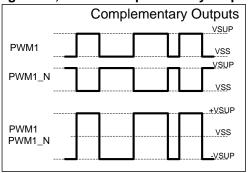

- ☐ 4 independent PWM outputs

- 8/16-bit timers

- Prescaler for RC and XTAL

- SPI interface

- □ Small size, Green mold / lead-free packages

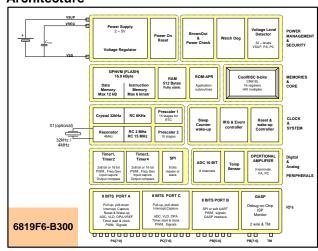

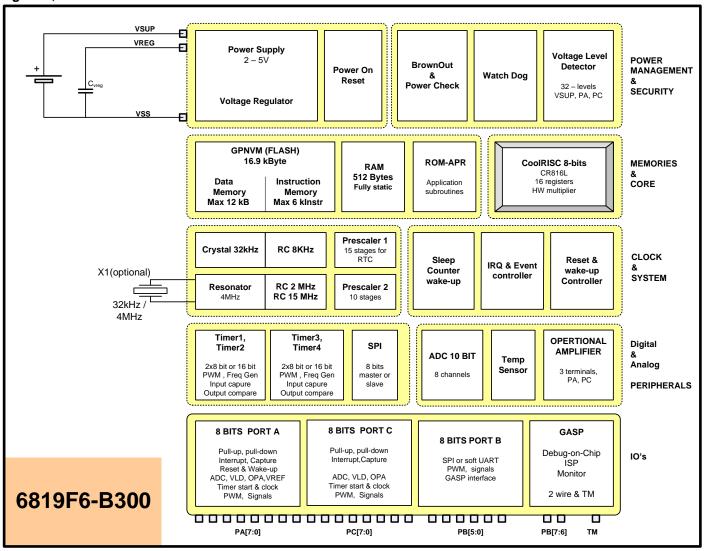

#### **Architecture**

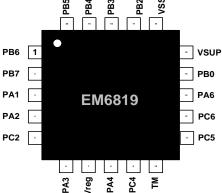

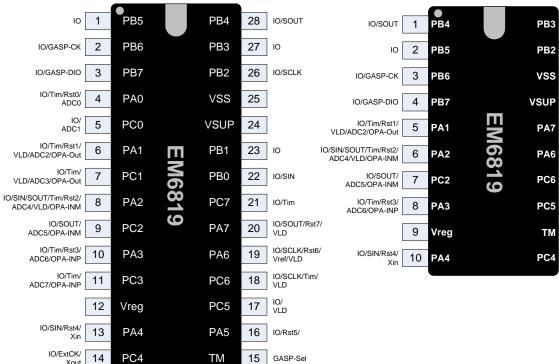

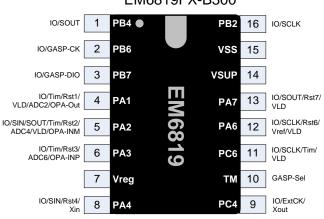

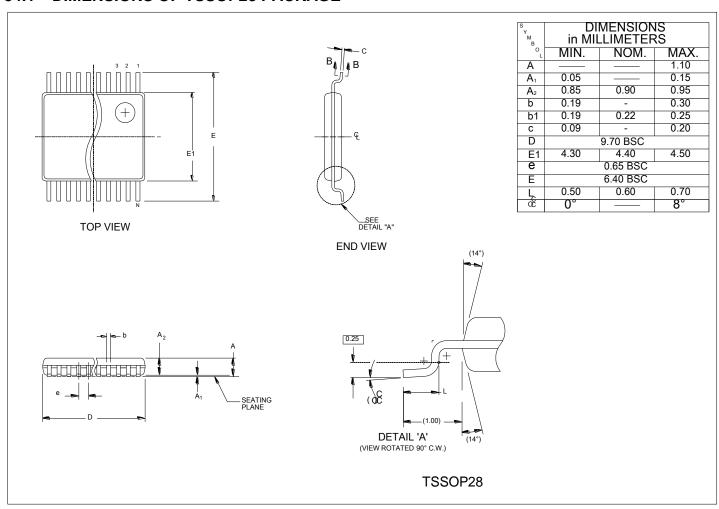

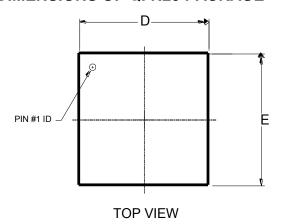

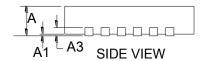

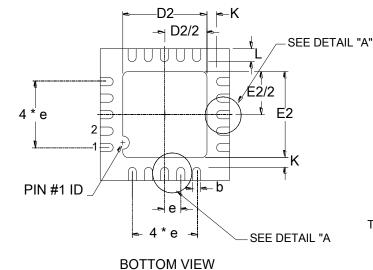

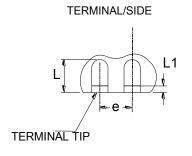

#### Pinout 20 lead QFN

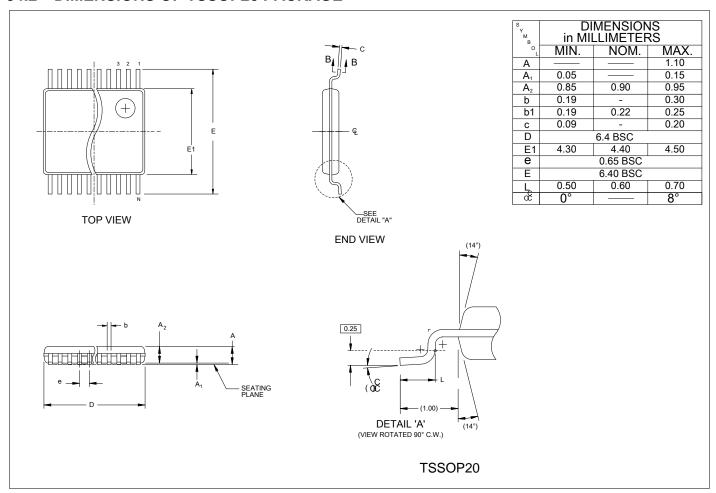

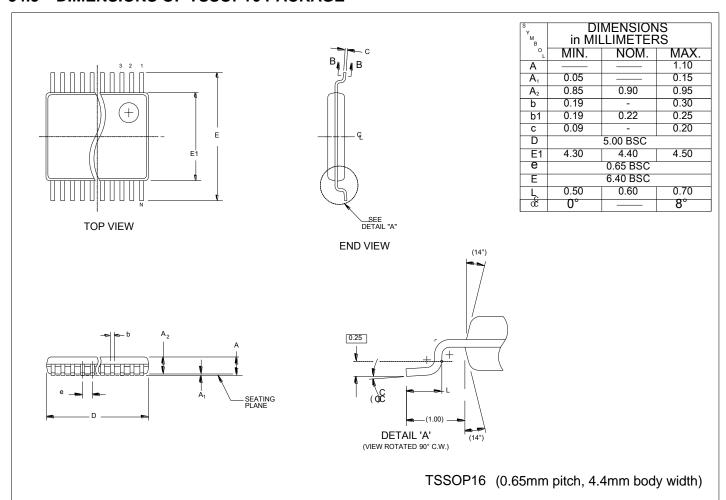

Others include, TSSOP16/20/28

20 Lead QFN 4x4mm body EM6819FX-BXXX

# **Typical Applications**

- Safety and Security devices

- □ Heat Cost Allocation

- □ Sensor Interfaces, Smoke detector

- □ Security

- Body care

- Sports

- Computer peripherals, Bluetooth chipset

- Wireless

### **Tools & Services**

- On chip debug system in the application

- □ ISP (In-system) programming

- □ C-compiler

1

- Windows-based software programs

- Programmer from different vendors

- Dedicated team of engineers for outstanding support

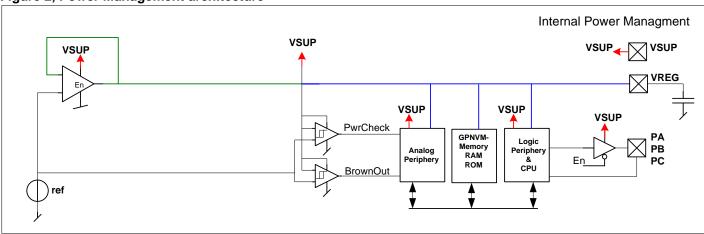

# **Power supply**

- Low power architecture

- Voltage regulator for internal logic supply

- External regulator capacitor

## **CPU**

- 8-bit CoolRisc 816L Core

- 16 internal registers

- 4 hardware subroutine stacks

- 8-bit hardware multiplier

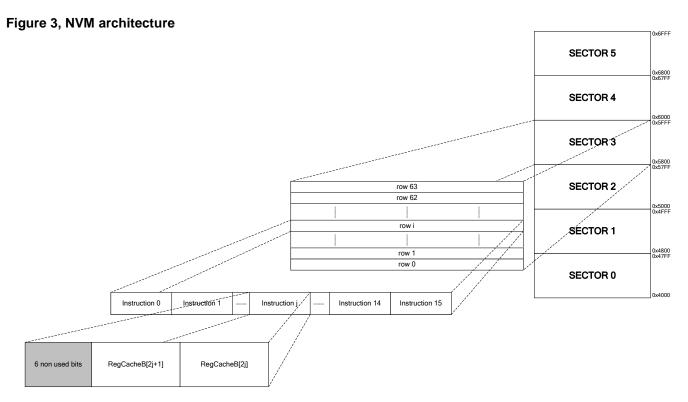

### Flash/EEPROM

- 16.9k Byte shared Genaral Purpose Non Volatile Flash memory

- max 6k Instructions program memory

- max 12 kByte non volatile data memory

#### RAM

- 512 x 8-bit static SRAM

- 48 byte of Ram-cache for EEProm modification support

# **Operating modes**

- Active mode: CPU and peripherals are running

- Standby mode: CPU halted, peripherals on

- Sleep mode: no clocks, data retained

### Resets

- Power On Reset

- Reset from logic watchdog

- Brown out (as voltage supervisory function)

- Reset with Port A selection

- Flags to identify the reset source

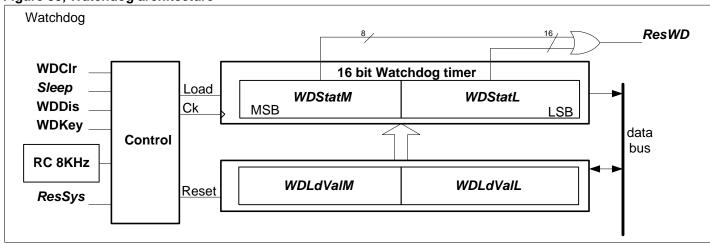

## Watchdog timer

- generation of watchdog reset after time out

- independent low frequency watchdog oscillator

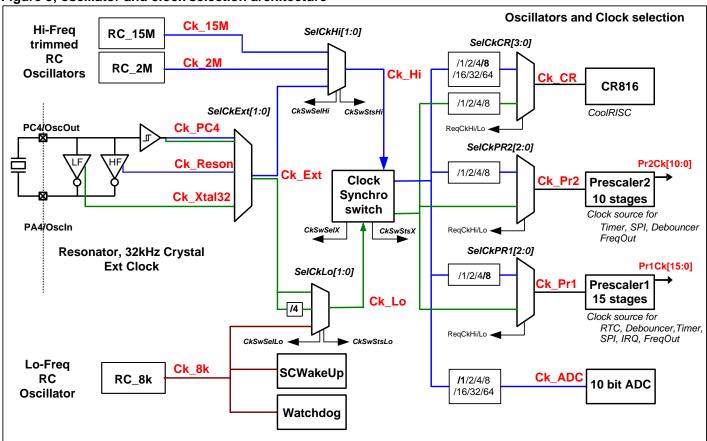

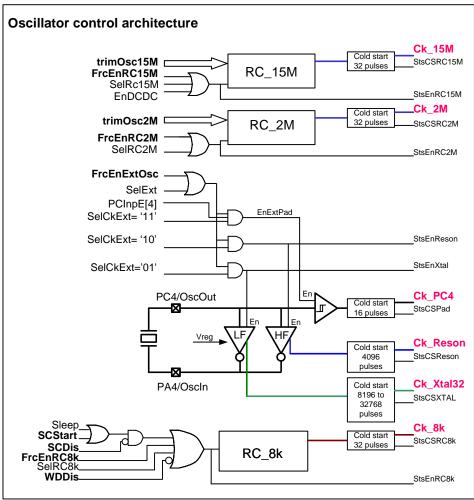

# **Oscillator RC**

- internal RC oscillator, 2MHz and 15MHz pre-trimmed

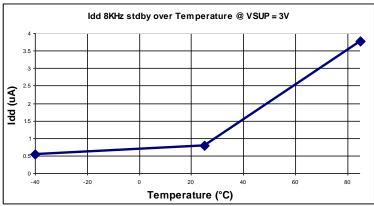

- internal 8 KHz RC Oscillator

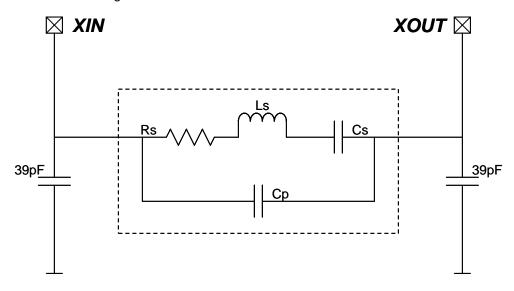

### **External Oscillator**

32 KHz watch type Crystal or 4MHz Resonator

## Prescaler's

- Two clock prescalers (dividers) for the peripheral clock generation:

- Prescaler 1 is a 15-stage divider

- Prescaler 2 is a 10-stage divider

- input clock software selectable

- fix intervall IRQ's

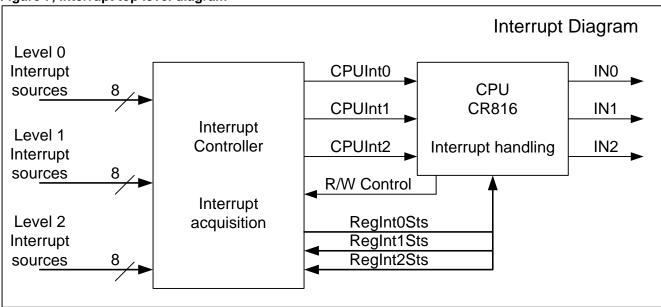

# Interrupt

- external IRQ's from Port A, VLD, Comparator

- internal IRQ's from Timer, Prescaler, ADC, SPI

- Event from SPI/ADC and DoC

# **VLD**

- Detection of 32 voltage levels, internal reference

- Comparison against VSUP, input Pin or Op.Amp output

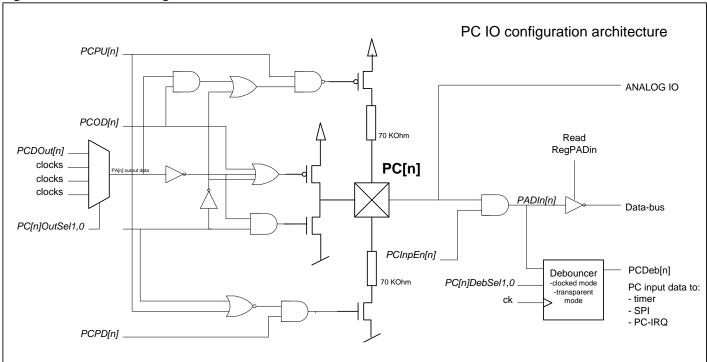

# Parallel In/Output Port A, Port C

- 8-bit wide direct input read

- all functions bit-wise configurable

- Input, output

- Debouncer, IRQ on pos. or neg. edge

- Input combination reset

- Pullup, pulldown or nopull selectable

- Freq. Input for timer

- Analog In/Out

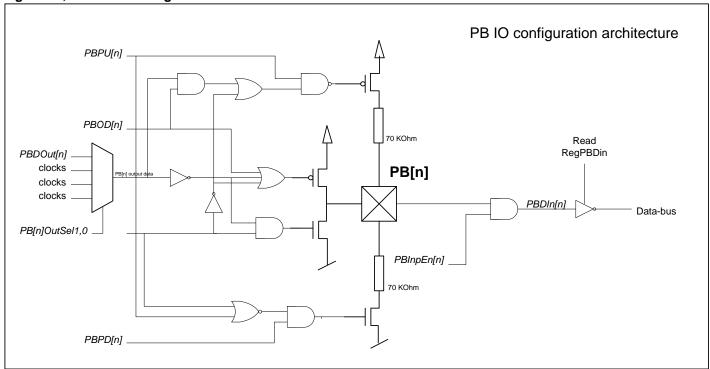

# Parallel In/Output Port B

- 8 multipurpose I/O's

- 8-bit wide direct input read

- CMOS or Nch. Open Drain outputs

- all functions bit-wise configurable

- Input, output

- Pullup, pulldown or nopull selectable

- CMOS or Nch. Open Drain outputs

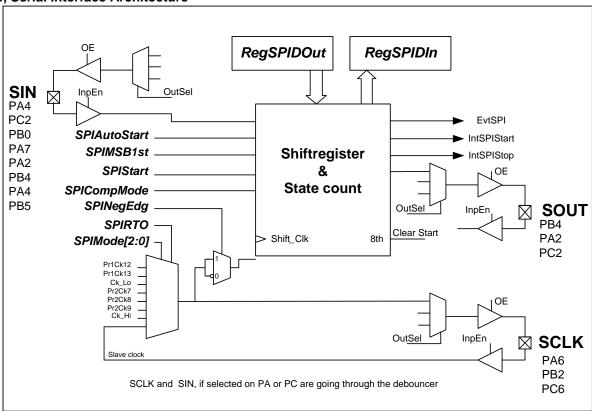

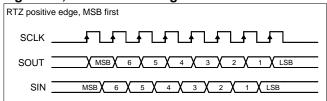

### Serial Port Interface SPI

- 3 wire serial Interface, Sclk, Sin, Sout

- master and Slave mode

- Serial datastream output

- Event / IRQ

- Maped on port outputs

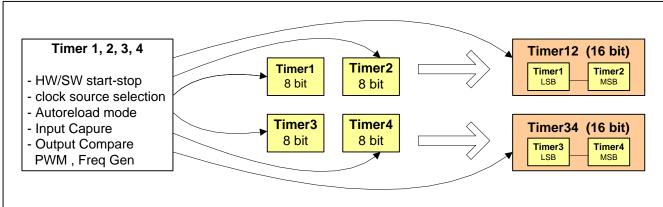

# Timer (4 x 8-bit, or 2 x 16-bit)

- 8 (16) bit wide, Zero Stop and Auto Reload mode

- External signal pulse width measurement

- PWM generation, IRQ

- Event Counter

- Input capture

- Output compare

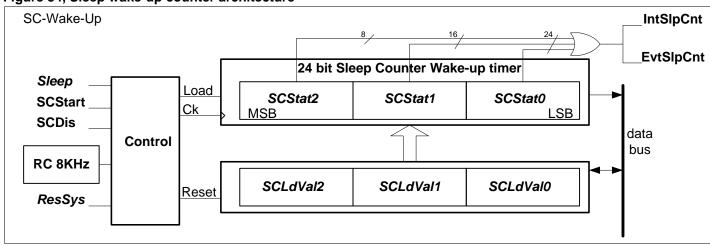

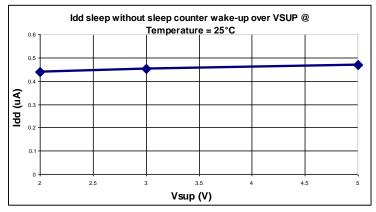

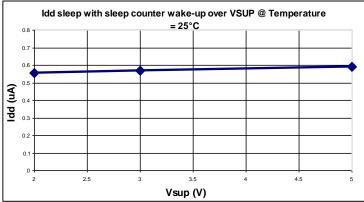

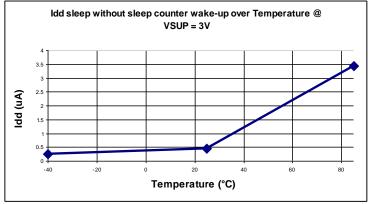

# Sleep Counter Wake-up (SCWUP)

- Automatically wakes up the circuit from sleep mode

- Enable/disable by register

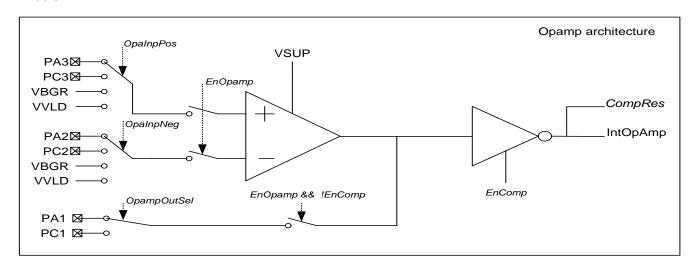

# **Op. Amplifier / Comparator**

- All 3 terminals mapped on PortA/PortC

- Output routed to VLD cell

- Amplifier or Comparator output

## Temp. Sensor

- Fully internal temperature sensor

- Multiplexed input to ADC

#### **Brown Out**

- On-chip Brown-Out detection, reset state

- Power check at Startup

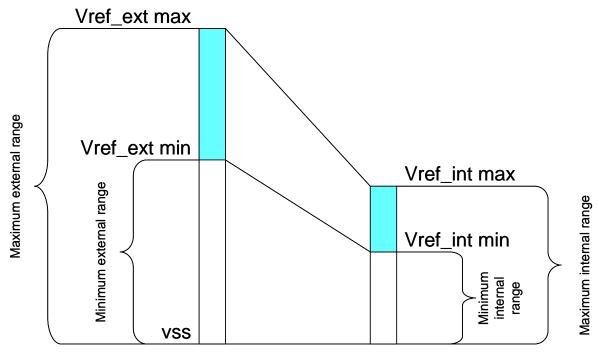

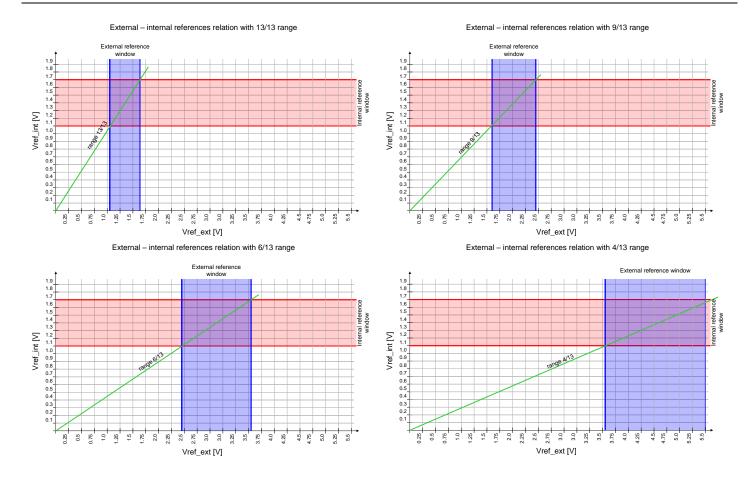

## **ADC**

- 10-bit, 8 channels ADC

- Single or Continuous mode

- External/internal reference voltage available on a pad

- Event / IRQ

# DoC (Debug on Chip)

- 2 wire serial interface debug and programming interface

- Flash programming

- Event / IRQ

| Pin Name | Software selectable functions                                                                                                                                                                                                   | Remarks    |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| PA0      | Input with pullup/pulldown, IRQ capability, CPU read, wake-up, timer1 ext clock.  Output of CPU write and a selection of internal clock and PWM signals.  Analog input for ADC.                                                 |            |

| PA1      | Input with pullup/pulldown, IRQ capability, CPU read, wake-up, timer2 ext clock.  Output of CPU write, selection of internal clock and PWM signals.  Analog: input for ADC and VLD; Output for OPAMP.                           |            |

| PA2      | Input with pullup/pulldown, IRQ capability, CPU read, wake-up, serial data input, timer3 ext clock.  Output of CPU write, serial data out and selection of internal clock and PWM signals  Analog: input for ADC,VLD and Opamp; |            |

| PA3      | Input with pullup/pulldown, IRQ capability, CPU read, wake-up, serial data input, timer4 ext clock.  Output of CPU write, serial data out and selection of internal clock and PWM signals  Analog: input for ADC,VLD and Opamp; |            |

| PA4      | Input with pullup/pulldown, IRQ capability, CPU read, wake-up, serial data.  Output of CPU write and a selection of internal clock and PWM signals.  Analog: XTAL/Resonator connection.                                         |            |

| PA5      | Input with pullup/pulldown, IRQ capability, CPU read, wake-up.  Output of CPU write and a selection of internal clock and PWM signals.                                                                                          |            |

| PA6      | Input with pullup/pulldown, IRQ capability, CPU read, wake-up, serial clock  Output of CPU write, serial clock and a selection of internal clock and PWM signals.  Analog: input for VLD; Output for VBGP                       |            |

| PA7      | Input with pullup/pulldown, IRQ capability, CPU read, wake-up, serial clock  Output of CPU write, serial data and a selection of internal clock and PWM signals.  Analog: input for VLD; Output for internal reference voltage  |            |

| PB0      | Input with pullup/pulldown, CPU read, serial data.  Output of CPU write and a selection of internal clock and PWM signals.                                                                                                      |            |

| PB1      | Input with pullup/pulldown, CPU read.  Output of CPU write and a selection of internal clock and PWM signals.                                                                                                                   |            |

| PB2      | Input with pullup/pulldown, CPU read, serial clock.  Output of CPU write, serial clock and a selection of internal clock and PWM signals.                                                                                       |            |

| PB3      | Input with pullup/pulldown, CPU read.  Output of CPU write and a selection of internal clock and PWM signals.                                                                                                                   |            |

| PB4      | Input with pullup/pulldown, CPU read.  Output of CPU write, serial data and a selection of internal clock and PWM signals.                                                                                                      |            |

| PB5      | Input with pullup/pulldown, CPU read.  Output of CPU write and a selection of internal clock and PWM signals.                                                                                                                   |            |

| PB6      | Input with pullup/pulldown, CPU read.  Output of CPU write and a selection of internal clock and PWM signals.                                                                                                                   | GASP clock |

| PB7      | Input with pullup/pulldown, CPU read.  Output of CPU write and a selection of internal clock and PWM signals.                                                                                                                   | GASP data  |

| PC0      | Input with pullup/pulldown, IRQ capability, CPU read, timer1 ext clock.  Output of CPU write and a selection of internal clock and PWM signals.  Analog input for ADC.                                                          |            |

| PC1      | Input with pullup/pulldown, IRQ capability, CPU read, timer2 ext clock.  Output of CPU write, selection of internal clock and PWM signals.  Analog: input for ADC and VLD; Output for OPAMP.                                    |            |

| PC2      | Input with pullup/pulldown, IRQ capability, CPU read.                                                                                                                                                                           |            |

|      | Output of CPU write, serial data, selection of internal clock and PWM signals . Analog: input for ADC and OPAMP.                                                                            |           |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| PC3  | Input with pullup/pulldown, IRQ capability, CPU read, timer4 ext clock.  Output of CPU write, selection of internal clock and PWM signals.  Analog: input for ADC and OPAMP.                |           |

| PC4  | Input with pullup/pulldown, IRQ capability, CPU read, external clock input Output of CPU write, selection of internal clock and PWM signals . Analog: XTAL/Resonator connection             |           |

| PC5  | Input with pullup/pulldown, IRQ capability, CPU read.  Output of CPU write, selection of internal clock and PWM signals.  Analog: input for VLD.                                            |           |

| PC6  | Input with pullup/pulldown, IRQ capability, CPU read, serial clock, timer1 ext clock Output of CPU write, serial clock, selection of internal clock and PWM signals. Analog: input for VLD. |           |

| PC7  | Input with pullup/pulldown, IRQ capability, CPU read, timer3 ext clock Output of CPU write, selection of internal clock and PWM signals.                                                    |           |

| TM   | GASP mode entry                                                                                                                                                                             | GASP mode |

| VREG | External Capacitance to maintain internal regulated voltage                                                                                                                                 |           |

| VSUP | Main power supply pin.                                                                                                                                                                      |           |

| VSS  | Main GND. This is also the circuit substrate potential.                                                                                                                                     |           |

# **TABLE OF CONTENTS**

| 1. | EM6819 FAMILY (INCLUDING EM6819FX-B300)                                                                                                                                                                                                                                                                                                                            | 11                                                                         |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| 2. | SYSTEM OVERVIEW                                                                                                                                                                                                                                                                                                                                                    | 12                                                                         |

|    | 2.1 OPERATING MODES 2.1.1 Active mode 2.2 LOW POWER MODES 2.2.1 Standby mode 2.2.2 Sleep mode 2.2.3 Sleep Wake-up 2.2.4 Operation mode registers 2.3 REGISTER TYPES 2.4 POWER MANAGEMENT 2.4.1 Brownout 2.4.2 Powercheck 2.4.3 POR 2.4.4 Powermanagment Registers 2.5 REGISTER MAP 2.6 PORT TERMINAL CONNECTION REFERENCE TABLE 2.7 AVAILABLE PACKAGES             | 13<br>13<br>13<br>14<br>14<br>15<br>16<br>17<br>17<br>17<br>17<br>25<br>26 |

| 3. | CPU CORE CR816                                                                                                                                                                                                                                                                                                                                                     | 27                                                                         |

| 4. | 3.1 PM_MISS FUNCTION (FLASH READ MONITOR)  NVM MEMORY                                                                                                                                                                                                                                                                                                              | 27<br><b>28</b>                                                            |

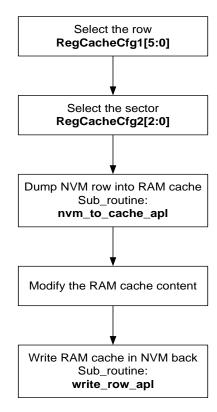

| 5. | 4.1 INTRODUCTION 4.2 NVM ARCHITECTURE 4.3 RAM CACHE 4.4 WRITE DATA IN NVM 4.4.1 Row and sector selection 4.4.2 Fast/slow operation 4.4.3 Erase 4.4.4 Write 4.5 Row 61 SECTOR 5 4.6 Row 62 SECTOR 5 4.6.1 Temperature tolerance 4.7 Row 63 SECTOR 5 4.8 READ DATA IN NVM 4.9 ROW TO CACHE 4.9.1 NVM configuration registers CRC CHECK 5.1 CRC CHECK ON PROGRAM AREA | 28<br>28<br>29<br>29<br>29<br>30<br>31<br>31<br>31<br>32<br>33<br>34<br>35 |

|    | 5.2 CRC CHECK ON PROGRAM AREA  5.2 CRC CHECK ON DATA AREA                                                                                                                                                                                                                                                                                                          | 35                                                                         |

|    | ROM API ROUTINES                                                                                                                                                                                                                                                                                                                                                   | 36                                                                         |

|    | 6.1 BOOT SEQUENCE 6.2 SUB-ROUTINES USED FOR APPLICATION                                                                                                                                                                                                                                                                                                            | 36<br>37                                                                   |

| 7. | RAM                                                                                                                                                                                                                                                                                                                                                                | 38                                                                         |

| 8. | RESET CONTROLLER                                                                                                                                                                                                                                                                                                                                                   | 39                                                                         |

|    | 8.1 RESET SOURCES 8.2 RESET SIGNALS 8.2.1 POR 8.2.2 ResAna 8.2.3 ResSys 8.2.4 Reset Flags 8.3 RESET REGISTERS                                                                                                                                                                                                                                                      | 39<br>39<br>39<br>39<br>39<br>40                                           |

| 9. | OSCILLATOR AND CLOCKING STRUCTURE                                                                                                                                                                                                                                                                                                                                  | 41                                                                         |

|    | 9.1 EXTERNAL CLOCK SELECTION                                                                                                                                                                                                                                                                                                                                       | 42                                                                         |

| 9.2 INTERNAL HIGH AND LOW FREQUENCY CLOCK SELECTION                           | 42               |

|-------------------------------------------------------------------------------|------------------|

| 9.2.1 External clock selection Restrictions                                   | 43               |

| 9.2.2 CPU Clock selection                                                     | 43               |

| 9.2.3 Prescaler1 Clock selection 9.2.4 Prescaler2 Clock selection             | 44<br>44         |

| 9.3 CLOCK CONTROL                                                             | 45               |

| 9.4 OSCILLATORS CONTROL                                                       | 46               |

| 9.5 CLOCK CONTROL REGISTERS                                                   | 48               |

| 10. PRESCALER1                                                                | 50               |

| 10.1 Prescaler1 clock selection                                               | 50               |

| 10.2 PRESCALER1 RESET                                                         | 51               |

| 10.3 Prescaler registers                                                      | 51               |

| 11. PRESCALER2                                                                | 52               |

| 11.1 Prescaler2 clock selection                                               | 52               |

| 11.2 PRESCALER2 RESET                                                         | 52               |

| 11.3 Prescaler2 registers                                                     | 52               |

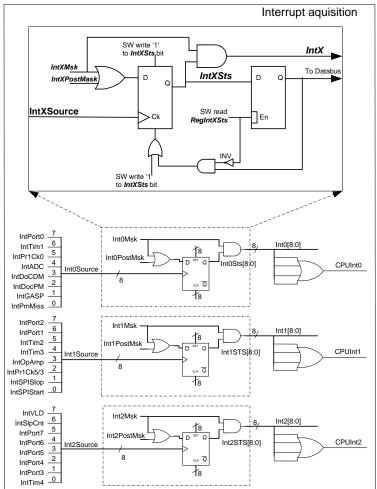

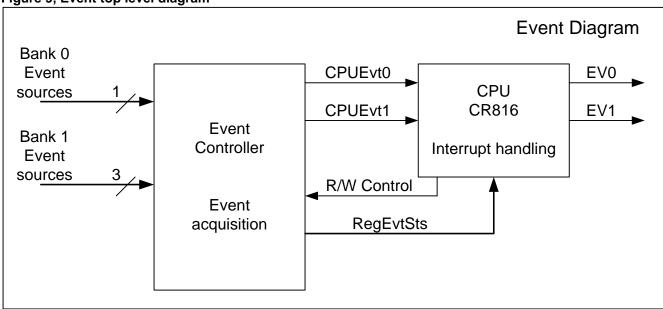

| 12. INTERRUPT AND EVENT CONTROLLER                                            | 53               |

| 12.1 Interrupts General                                                       | 53               |

| 12.1.1 Basic features                                                         | 53               |

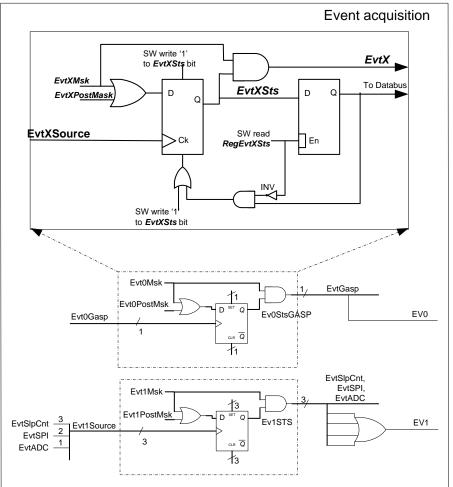

| 12.2 INTERRUPT ACQUISITION                                                    | 54               |

| 12.3 INTERRUPTS FROM IO PORTS                                                 | 55<br>55         |

| 12.4 INTERRUPT ACQUISITION MASKING.  12.4.1 Pre and Postmasking of interrupts | 55<br>55         |

| 12.5 Interrupt acquisition Clearing                                           | 56               |

| 12.5.1 Software Interrupt acquisition set                                     | 56               |

| 12.6 Interrupt Registers                                                      | 56               |

| 12.7 EVENT GENERAL                                                            | 59               |

| 12.7.1 Basic features 12.8 EVENT ACQUISITION                                  | <i>5</i> 9<br>59 |

| 12.9 EVENT MASKING                                                            | 60               |

| 12.10 EVENT ACQUISITION CLEARING                                              | 61               |

| 12.11 SOFTWARE EVENT SETTING                                                  | 61               |

| 12.12 EVENT REGISTERS                                                         | 61               |

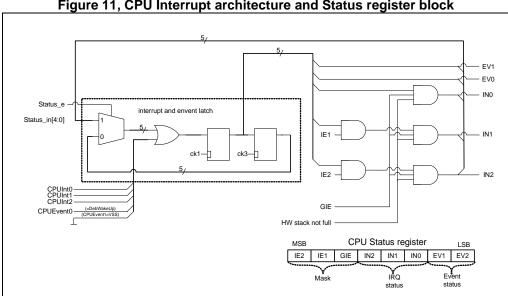

| 13. CPU INTERRUPT AND EVENT HANDLING                                          | 62               |

| 13.1 Interrupt priority                                                       | 62               |

| 13.2 CPU STATUS REGISTER                                                      | 63               |

| 13.3 CPU STATUS REGISTER PIPELINE EXCEPTION                                   | 63               |

| 13.4 PROCESSOR VECTOR TABLE 13.5 CONTEXT SAVING                               | 64<br>64         |

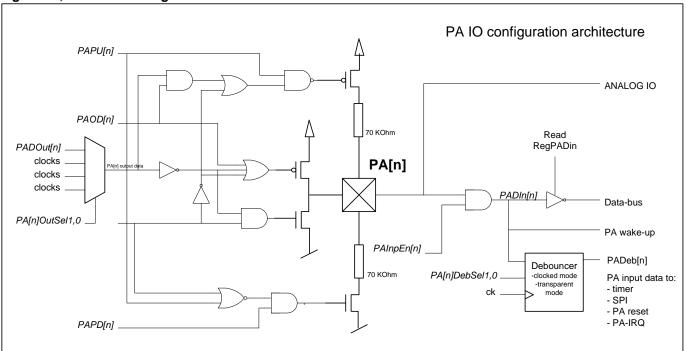

| 14. PORT A                                                                    | 65               |

|                                                                               |                  |

| 14.1 PORT A TERMINAL MAPPING 14.2 PORT A IO OPERATION                         | 65               |

| 14.2 PORT A TO OPERATION  14.3 OUTPUT SIGNALS ON PORT A                       | 66<br>68         |

| 14.4 Port A Debouncer                                                         | 69               |

| 14.5 PORT A INTERRUPT GENERATION                                              | 69               |

| 14.5.1 PA Irq in Active and Standby mode                                      | 69               |

| 14.5.2 PA Irq in Sleep Mode                                                   | 69               |

| 14.6 PORT A RESET FUNCTION 14.7 PORT A REGISTERS                              | 69<br>70         |

| 15. PORT B                                                                    | 70<br><b>72</b>  |

|                                                                               |                  |

| 15.1 PORT B TERMINAL MAPPING 15.2 PORT B IO OPERATION                         | 72<br>72         |

| 15.2.1 Gasp communication on PB7, PB6                                         | 73               |

| 15.3 OUTPUT SIGNALS ON PORT B                                                 | 74               |

| 15.4 PORT B REGISTERS                                                         | 75               |

| 16. PORT C                                                                    | 76               |

| 16.1 PORT C TERMINAL MAPPING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 76       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 16.2 PORT C IO OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 76       |

| 16.3 OUTPUT SIGNALS ON PORT C 16.4 PORT C DEBOUNCER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 78<br>79 |

| 16.5 PORT C DEBOUNCER  16.5 PORT C INTERRUPT GENERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 79       |

| 16.5.1 PC Irg in Active and Standby mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 79       |

| 16.5.2 PC Irq in Sleep Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 79       |

| 16.6 PORT C REGISTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 80       |

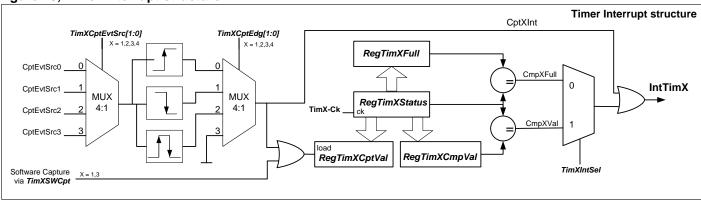

| 17. TIMERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 82       |

| 17.1 TIMER CHAINING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 82       |

| 17.2 TIMER CLOCK SOURCES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 83       |

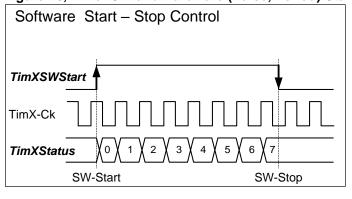

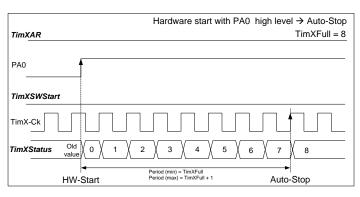

| 17.3 TIMER START                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 84       |

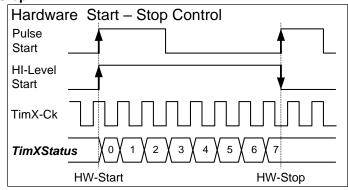

| 17.3.1 Software start - Stop<br>17.3.2 Hardware Start – Stop (period counting)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 84<br>84 |

| 17.3.2 Hardware Start – Stop (period counting) 17.3.3 Hardware Start – Stop (puls counting)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 85       |

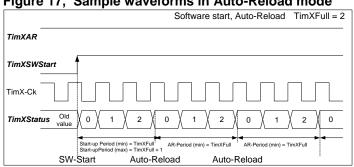

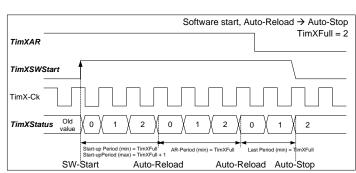

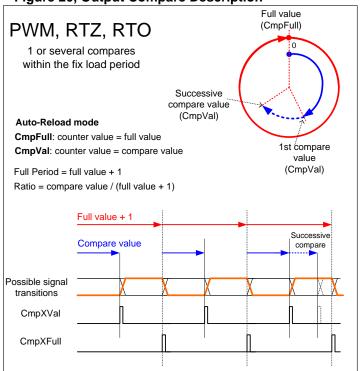

| 17.4 AUTO-RELOAD MODE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 86       |

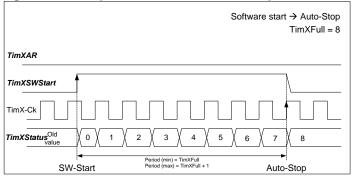

| 17.5 AUTO-STOP MODE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 86       |

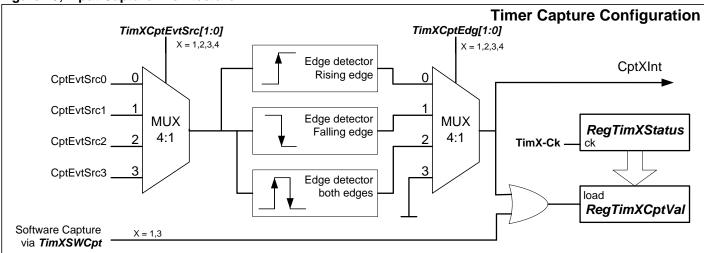

| 17.6 TIMER INPUT CAPTURE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 87       |

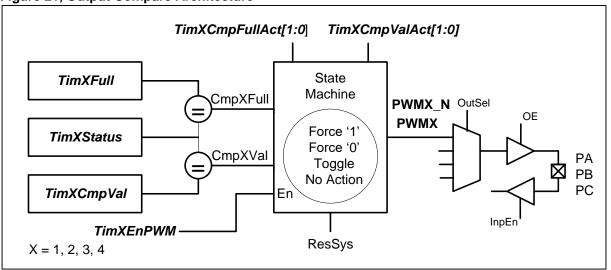

| OUTPUT COMPARE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 89       |

| 17.7 OUTPUT COMPARE - PWMX SIGNAL PORT MAPPING 17.8 TIMER INTERRUPTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 90<br>91 |

| 17.6 TIMER INTERROPTS  17.9 TIMER REGISTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 91       |

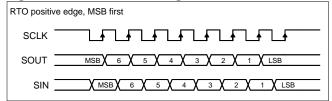

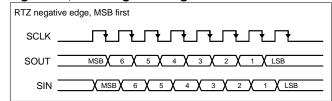

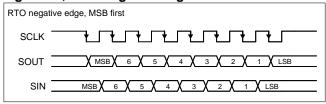

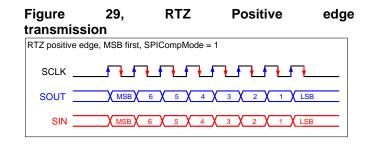

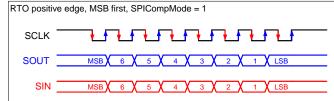

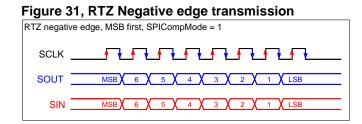

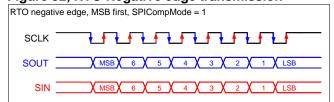

| 18. SPI – SERIAL INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 95       |

| 18.1 SCLK - SPI MASTER/ SLAVE MODE AND CLOCK SELECTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 96       |

| 18.2 SIN PORT MAPPING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 97       |