Data Sheet

**September 26, 2005**

FN7415.1

# TFT-LCD DC/DC with Integrated Amplifiers

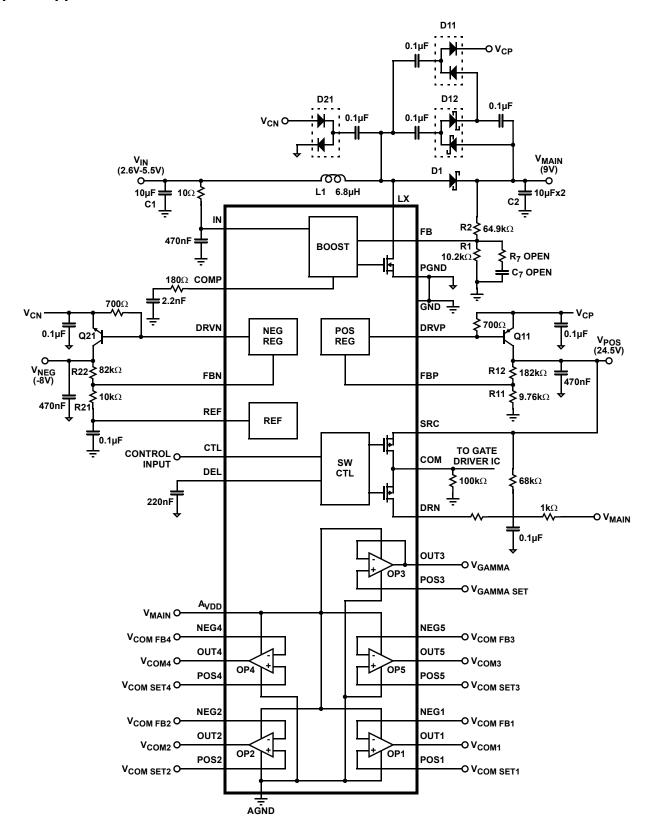

The EL7640, EL7641, and EL7642 integrate a high performance boost regulator with 2 LDO controllers for  $V_{ON}$  and  $V_{OFF}$ , a  $V_{ON}$ -slice circuit with adjustable delay and either one (EL7640), three (EL7641), or five amplifiers (EL7642) for  $V_{COM}$  and  $V_{GAMMA}$  applications.

The boost converter in the EL7640, EL7641, and EL7642 is a current mode PWM type integrating an 18V N-channel MOSFET. Operating at 1.2MHz, this boost can operate in either P-mode for superior transient response, or in PI-mode for tighter output regulation.

Using external low-cost transistors, the LDO controllers provide tight regulation for  $V_{ON}$ ,  $V_{OFF}$ , as well as providing start-up sequence control and fault protection.

The amplifiers are ideal for  $V_{COM}$  and  $V_{GAMMA}$  applications, with 150mA peak output current drive, 12MHz bandwidth, and 12V/ $\mu$ s slew rate. All inputs and outputs are rail-to-rail.

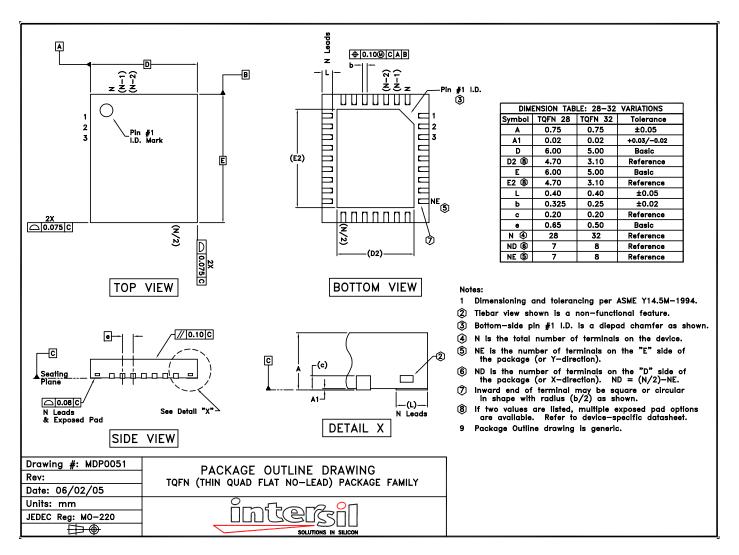

Available in the 32 Ld thin QFN (5mm x 5mm) Pb-free packages, the EL7640, EL7641, and EL7642 are specified for operation over the -40°C to +85°C temperature range.

# Ordering Information

| PART NUMBER<br>(Note) | PART<br>MARKING | TAPE & REEL | PACKAGE<br>(Pb-Free)  | PKG.<br>DWG.# |  |  |  |

|-----------------------|-----------------|-------------|-----------------------|---------------|--|--|--|

| EL7640ILTZ            | 7640ILTZ        | -           | 32 Ld 5x5<br>Thin QFN | MDP0051       |  |  |  |

| EL7640ILTZ-T7         | 7640ILTZ        | 7"          | 32 Ld 5x5<br>Thin QFN | MDP0051       |  |  |  |

| EL7640ILTZ-T13        | 7640ILTZ        | 13"         | 32 Ld 5x5<br>Thin QFN | MDP0051       |  |  |  |

| EL7641ILTZ            | 7641ILTZ        | -           | 32 Ld 5x5<br>Thin QFN | MDP0051       |  |  |  |

| EL7641ILTZ-T7         | 7641ILTZ        | 7"          | 32 Ld 5x5<br>Thin QFN | MDP0051       |  |  |  |

| EL7641ILTZ-T13        | 7641ILTZ        | 13"         | 32 Ld 5x5<br>Thin QFN | MDP0051       |  |  |  |

| EL7642ILTZ            | 7642ILTZ        | -           | 32 Ld 5x5<br>Thin QFN | MDP0051       |  |  |  |

| EL7642ILTZ-T7         | 7642ILTZ        | 7"          | 32 Ld 5x5<br>Thin QFN | MDP0051       |  |  |  |

| EL7642ILTZ-T13        | 7642ILTZ        | 13"         | 32 Ld 5x5<br>Thin QFN | MDP0051       |  |  |  |

NOTE: Intersil Pb-free plus anneal products employ special Pb-free material sets; molding compounds/die attach materials and 100% matte tin plate termination finish, which are RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

#### Features

- · Current mode boost regulator

- Fast transient response

- 1% accurate output voltage

- 18V/3A integrated FET

- >90% efficiency

- 2.6V to 5.5V V<sub>IN</sub> supply

- 2 LDO controllers for V<sub>ON</sub> and V<sub>OFF</sub>

- 2% output regulation

- VON-slice circuit

- · High speed amplifiers

- 150mA short-circuit output current

- 12V/μs slew rate

- 12MHz -3dB bandwidth

- Rail-to-rail inputs and outputs

- · Built-in power sequencing

- · Internal soft-start

- · Multiple overload protection

- · Thermal shutdown

- 32 Ld 5x5 thin QFN package

- · Pb-Free plus anneal available (RoHS compliant)

## **Applications**

- TFT-LCD panels

- · LCD monitors

- Notebooks

- LCD-TVs

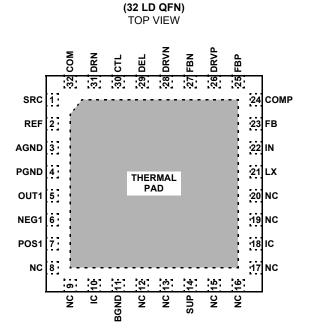

#### **Pinouts**

EL7640

NC = NOT INTERNALLY CONNECTED IC = INTERNALLY CONNECTED

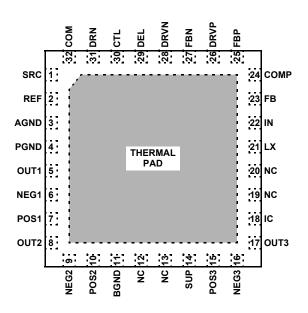

#### **EL7642** (**32 LD QFN**) TOP VIEW

#### **EL7641** (**32 LD QFN**) TOP VIEW

NC = NOT INTERNALLY CONNECTED IC = INTERNALLY CONNECTED

## EL7640, EL7641, EL7642

## **Absolute Maximum Ratings** (T<sub>A</sub> = 25°C)

| IN, CTL to AGND0.3V to +6.5V                                       | COM, DRN to AGND0.3V to V <sub>SRC</sub> +0.3V |

|--------------------------------------------------------------------|------------------------------------------------|

| COMP, FB, FBP, FBN, DEL, REF to AGND0.3V to V <sub>IN</sub> +0.3V  | LX Maximum Continuous RMS Output Current 1.6A  |

| PGND, BGND to AGND                                                 | OUT1, OUT2, OUT3, OUT4, OUT5                   |

| LX to PGND                                                         | Maximum Continuous Output Current ±75mA        |

| SUP to AGND                                                        | Storage Temperature65°C to +150°C              |

| DRVP, SRC to AGND0.3V to +36V                                      | Maximum Continuous Junction Temperature +125°C |

| POS1, NEG1, OUT1, POS2, NEG2, OUT2, POS3, OUT3,                    | Power Dissipation See Curves                   |

| POS4, NEG4, OUT4, POS5, OUT5 to AGND0.3V to V <sub>SUP</sub> +0.3V | Operating Ambient Temperature                  |

| DRVN to AGND                                                       |                                                |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

IMPORTANT NOTE: All parameters having Min/Max specifications are guaranteed. Typical values are for information purposes only. Unless otherwise noted, all tests are at the specified temperature and are pulsed tests, therefore:  $T_J = T_C = T_A$

# **Electrical Specifications** $V_{IN} = 3V$ , $V_{BOOST} = V_{SUP} = 12V$ , $V_{SRC} = 20V$ , Over temperature from -40°C to 85°C. Unless Otherwise Specified.

| PARAMETER                                    | DESCRIPTION                    | CONDITIONS                                     | MIN                      | TYP   | MAX   | UNIT |

|----------------------------------------------|--------------------------------|------------------------------------------------|--------------------------|-------|-------|------|

| SUPPLY                                       |                                |                                                | •                        | U.    | U.    | Į.   |

| V <sub>IN</sub>                              | Input Supply Range             |                                                | 2.6                      |       | 5.5   | V    |

| V <sub>LOR</sub>                             | Undervoltage Lockout Threshold | V <sub>IN</sub> rising                         | 2.4                      | 2.5   | 2.6   | V    |

| V <sub>LOF</sub>                             | Undervoltage Lockout Threshold | V <sub>IN</sub> falling                        | 2.2                      | 2.3   | 2.4   | V    |

| Is                                           | Quiescent Current              | LX not switching                               |                          |       | 2.5   | mA   |

| I <sub>SS</sub>                              | Quiescent Current - Switching  | LX switching                                   |                          | 5     | 10    | mA   |

| T <sub>FD</sub>                              | Fault Delay Time               | C <sub>DEL</sub> = 220nF                       |                          | 52    |       | ms   |

| V <sub>REF</sub>                             | Reference Voltage              | T <sub>A</sub> = 25°C                          | 1.19                     | 1.215 | 1.235 | V    |

|                                              |                                |                                                | 1.187                    | 1.215 | 1.238 | V    |

| SHUTDN                                       | Thermal Shutdown Temperature   |                                                |                          | 140   |       | °C   |

| MAIN BOOST F                                 | REGULATOR                      |                                                | <u> </u>                 |       |       | I.   |

| V <sub>BOOST</sub>                           | Output Voltage Range           | (Note 1)                                       | V <sub>IN</sub> +<br>15% |       | 18    | V    |

| Fosc                                         | Oscillator Frequency           |                                                | 1050                     | 1200  | 1350  | kHz  |

| D <sub>CM</sub>                              | Maximum Duty Cycle             |                                                | 82                       | 85    |       | %    |

| V <sub>FBB</sub>                             | Boost Feedback Voltage         | T <sub>A</sub> = 25°C                          | 1.192                    | 1.205 | 1.218 | V    |

|                                              |                                |                                                | 1.188                    | 1.205 | 1.222 | V    |

| V <sub>FTB</sub>                             | FB Fault Trip Level            | Falling edge                                   | 0.85                     | 0.925 | 1.020 | V    |

| ΔV <sub>BOOST</sub> /<br>ΔI <sub>BOOST</sub> | Load Regulation                | 50mA < I <sub>LOAD</sub> < 250mA               |                          | 0.1   |       | %    |

| $\Delta V_{BOOST}/\Delta V_{IN}$             | Line Regulation                | V <sub>IN</sub> = 2.6V to 5.5V                 |                          | 0.08  |       | %/V  |

| I <sub>FB</sub>                              | Input Bias Current             | V <sub>FB</sub> = 1.35V                        |                          |       | 500   | nA   |

| gmV                                          | FB Transconductance            | dI = ±2.5μA at COMP, FB = COMP                 |                          | 160   |       | μA/V |

| R <sub>ON</sub> LX                           | LX On Resistance               |                                                |                          | 160   |       | mΩ   |

| I <sub>LEAK</sub> LX                         | LX Leakage Current             | V <sub>FB</sub> = 1.35V, V <sub>LX</sub> = 13V |                          | 0.02  | 40    | μA   |

| I <sub>LIM</sub> LX                          | LX Current Limit               | Duty cycle = 65% (Note 1)                      |                          | 3.0   |       | Α    |

| t <sub>SS</sub> B                            | Soft-Start Period              | C <sub>DEL</sub> = 220nF                       |                          | 2     |       | ms   |

# EL7640, EL7641, EL7642

# **Electrical Specifications** $V_{IN} = 3V$ , $V_{BOOST} = V_{SUP} = 12V$ , $V_{SRC} = 20V$ , Over temperature from -40°C to 85°C. Unless Otherwise Specified. **(Continued)**

| PARAMETER                                | DESCRIPTION                       | CONDITIONS                                               | MIN                      | TYP                      | MAX       | UNIT |

|------------------------------------------|-----------------------------------|----------------------------------------------------------|--------------------------|--------------------------|-----------|------|

| OPERATIONAL                              | AMPLIFIERS                        |                                                          |                          |                          |           |      |

| V <sub>SUP</sub>                         | Supply Operating Range            |                                                          | 4.5                      |                          | 18        | V    |

| I <sub>SUP</sub>                         | Supply Current per Amplifier      |                                                          |                          | 600                      | 800       | μA   |

| V <sub>OS</sub>                          | Offset Voltage                    |                                                          |                          | 3                        | 12        | mV   |

| I <sub>B</sub>                           | Input Bias Current                |                                                          | -50                      |                          | +50       | nA   |

| CMIR                                     | Common Mode Input Range           |                                                          | 0                        |                          | $V_{SUP}$ | V    |

| CMRR                                     | Common Mode Rejection Ratio       |                                                          | 60                       | 90                       |           | dB   |

| A <sub>OL</sub>                          | Open Loop Gain                    |                                                          |                          | 110                      |           | dB   |

| V <sub>OH</sub>                          | Output Voltage High               | I <sub>OUT</sub> = 100μA                                 | V <sub>SUP</sub><br>-15  | V <sub>SUP</sub><br>-2   |           | mV   |

|                                          |                                   | I <sub>OUT</sub> = 5mA                                   | V <sub>SUP</sub><br>-250 | V <sub>SUP</sub><br>-150 |           | mV   |

| V <sub>OL</sub>                          | Output Voltage Low                | I <sub>OUT</sub> = -100μA                                |                          | 2                        | 30        | mV   |

|                                          |                                   | I <sub>OUT</sub> = -5mA                                  |                          | 100                      | 150       | mV   |

| I <sub>SC</sub>                          | Short-Circuit Current             |                                                          | 100                      | 150                      |           | mA   |

| I <sub>CONT</sub>                        | Continuous Output Current         |                                                          | ±50                      |                          |           | mA   |

| PSRR                                     | Power Supply Rejection Ratio      |                                                          | 60                       | 100                      |           | dB   |

| BW <sub>-3dB</sub>                       | -3dB Bandwidth                    |                                                          |                          | 12                       |           | MHz  |

| GBWP                                     | Gain Bandwidth Product            |                                                          |                          | 8                        |           | MHz  |

| SR                                       | Slew Rate                         |                                                          |                          | 12                       |           | V/µs |

| POSITIVE LDO                             |                                   |                                                          |                          |                          |           |      |

| V <sub>FBP</sub>                         | Positive Feedback Voltage         | I <sub>DRVP</sub> = 100μA, T <sub>A</sub> = 25°C         | 1.176                    | 1.2                      | 1.224     | V    |

|                                          |                                   | I <sub>DRVP</sub> = 100μA                                | 1.176                    | 1.2                      | 1.229     | V    |

| V <sub>FTP</sub>                         | V <sub>FBP</sub> Fault Trip Level | V <sub>FBP</sub> falling                                 | 0.82                     | 0.9                      | 0.98      | V    |

| I <sub>BP</sub>                          | Positive LDO Input Bias Current   | V <sub>FBP</sub> = 1.4V                                  | -50                      |                          | 50        | nA   |

| ΔV <sub>POS</sub> /<br>ΔI <sub>POS</sub> | FBP Load Regulation               | $V_{DRVP}$ = 25V, $I_{DRVP}$ = 0 to 20µA                 |                          | 0.5                      |           | %    |

| I <sub>DRVP</sub>                        | Sink Current                      | V <sub>FBP</sub> = 1.1V, V <sub>DRVP</sub> = 10V         | 2                        | 4                        |           | mA   |

| I <sub>LEAK</sub> P                      | DRVP Off Leakage Current          | V <sub>FBP</sub> = 1.4V, V <sub>DRVP</sub> = 30V         |                          | 0.1                      | 10        | μA   |

| t <sub>SS</sub> P                        | Soft-Start Period                 | C <sub>DEL</sub> = 220nF                                 |                          | 2                        |           | ms   |

| NEGATIVE LDO                             | )                                 |                                                          |                          |                          |           |      |

| V <sub>FBN</sub>                         | FBN Regulation Voltage            | I <sub>DRVN</sub> = 0.2mA, T <sub>A</sub> = 25°C         | 0.173                    | 0.203                    | 0.233     | V    |

|                                          |                                   | I <sub>DRVN</sub> = 0.2mA                                | 0.171                    | 0.203                    | 0.235     | V    |

| V <sub>FTN</sub>                         | V <sub>FBN</sub> Fault Trip Level | V <sub>FBN</sub> rising                                  | 380                      | 430                      | 480       | mV   |

| I <sub>BN</sub>                          | Negative LDO Input Bias Current   | V <sub>FBN</sub> = 250mV                                 | -50                      |                          | 50        | nA   |

|                                          | FBN Load Regulation               | V <sub>DRVN</sub> = -6V, I <sub>DRVN</sub> = 2μA to 20μA |                          | 0.5                      |           | %    |

| I <sub>DRVN</sub>                        | Source Current                    | V <sub>FBN</sub> = 500mV, V <sub>DRVN</sub> = -6V        | 2                        | 4                        |           | mA   |

| I <sub>LEAK</sub> N                      | DRVN Off Leakage Current          | V <sub>FBP</sub> = 1.35V, V <sub>DRVP</sub> = 30V        |                          | 0.1                      | 10        | μΑ   |

| t <sub>SS</sub> N                        | Soft-start Period                 | C <sub>DEL</sub> = 220nF                                 |                          | 2                        |           | ms   |

# EL7640, EL7641, EL7642

**Electrical Specifications**  $V_{IN}$  = 3V,  $V_{BOOST}$  =  $V_{SUP}$  = 12V,  $V_{SRC}$  = 20V, Over temperature from -40°C to 85°C. Unless Otherwise Specified. (Continued)

| PARAMETER                  | DESCRIPTION                                                  | CONDITIONS                                                                                                 | MIN                | TYP  | MAX                | UNIT |

|----------------------------|--------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|--------------------|------|--------------------|------|

| V <sub>ON</sub> -SLICE CIR | CUIT                                                         |                                                                                                            |                    |      |                    |      |

| $V_{LO}$                   | CTL Input Low Voltage                                        | V <sub>IN</sub> = 2.6V to 5.5V                                                                             |                    |      | 0.4V <sub>IN</sub> | V    |

| V <sub>HI</sub>            | CTL Input High Voltage                                       | V <sub>IN</sub> = 2.6V to 5.5V                                                                             | 0.6V <sub>IN</sub> |      |                    | V    |

| I <sub>LEAK</sub> CTL      | CTL Input Leakage Current                                    | CTL = AGND or IN                                                                                           | -1                 |      | 1                  | μΑ   |

| t <sub>D</sub> rise        | CTL to OUT Rising Prop Delay                                 | 1kΩ from DRN to 8V, $V_{CTL}$ = 0V to 3V step, no load on OUT, measured from $V_{CTL}$ = 1.5V to OUT = 20% |                    | 100  |                    | ns   |

| t <sub>D</sub> fall        | CTL to OUT Falling Prop Delay                                | 1kΩ from DRN to 8V, $V_{CTL}$ = 3V to 0V step, no load on OUT, measured from $V_{CTL}$ = 1.5V to OUT = 80% |                    | 100  |                    | ns   |

| V <sub>SRC</sub>           | SRC Input Voltage Range                                      |                                                                                                            |                    |      | 30                 | V    |

| ISRC                       | SRC Input Current                                            | Start-up sequence not completed                                                                            |                    | 150  | 250                | μΑ   |

|                            |                                                              | Start-up sequence completed                                                                                |                    | 150  | 250                | μΑ   |

| R <sub>ON</sub> SRC        | SRC On Resistance                                            | Start-up sequence completed                                                                                |                    | 5    | 10                 | Ω    |

| R <sub>ON</sub> DRN        | DRN On Resistance                                            | Start-up sequence completed                                                                                |                    | 30   | 60                 | Ω    |

| R <sub>ON</sub> COM        | COM to GND On Resistance                                     | Start-up sequence not completed                                                                            | 350                | 1000 | 1800               | Ω    |

| SEQUENCING                 |                                                              |                                                                                                            |                    |      |                    |      |

| t <sub>ON</sub>            | Turn On Delay                                                | C <sub>DLY</sub> = 0.22µF (See Figure 23)                                                                  |                    | 30   |                    | ms   |

| t <sub>DEL1</sub>          | Delay Between V <sub>BOOST</sub> and V <sub>OFF</sub>        | C <sub>DLY</sub> = 0.22µF (See Figure 23)                                                                  |                    | 10   |                    | ms   |

| t <sub>DEL2</sub>          | Delay Between V <sub>ON</sub> and V <sub>OFF</sub>           | C <sub>DLY</sub> = 0.22µF (See Figure 23)                                                                  |                    | 17   |                    | ms   |

| t <sub>DEL3</sub>          | Delay From V <sub>ON</sub> to V <sub>ON</sub> -slice Enabled | C <sub>DLY</sub> = 0.22μF (See Figure 23)                                                                  |                    | 10   |                    | ms   |

| C <sub>DEL</sub>           | Delay Capacitor                                              |                                                                                                            | 50                 | 220  |                    | nF   |

#### NOTE:

1. Guaranteed by design.

# Pin Descriptions

| PIN NAME | EL7642 | EL7641 | EL7640 | PIN FUNCTION                                                                                                                                            |  |

|----------|--------|--------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SRC      | 1      | 1      | 1      | Upper reference voltage for switch output                                                                                                               |  |

| REF      | 2      | 2      | 2      | Internal reference bypass terminal                                                                                                                      |  |

| AGND     | 3      | 3      | 3      | Analog ground for boost converter and control circuitry                                                                                                 |  |

| PGND     | 4      | 4      | 4      | Power ground for boost switch                                                                                                                           |  |

| OUT1     | 5      | 5      | 5      | Operational amplifier 1 output                                                                                                                          |  |

| NEG1     | 6      | 6      | 6      | Operational amplifier 1 inverting input                                                                                                                 |  |

| POS1     | 7      | 7      | 7      | Operational amplifier 1 non-inverting input                                                                                                             |  |

| OUT2     | 8      | 8      | -      | Operational amplifier 2 output                                                                                                                          |  |

| NEG2     | 9      | 9      | -      | Operational amplifier 2 inverting input                                                                                                                 |  |

| POS2     | 10     | 10     | -      | Operational amplifier 2 non-inverting input                                                                                                             |  |

| BGND     | 11     | 11     | 11     | Operational amplifier ground                                                                                                                            |  |

| POS3     | 12     | 15     | -      | Operational amplifier 3 non-inverting input                                                                                                             |  |

| NEG3     | -      | 16     | -      | Operational amplifier 3 inverting input                                                                                                                 |  |

| OUT3     | 13     | 17     | -      | Operational amplifier 3 output                                                                                                                          |  |

| SUP      | 14     | 14     | 14     | Amplifier positive supply rail. Bypass to BGND with 0.1µF capacitor                                                                                     |  |

| POS4     | 15     | -      | -      | Operational amplifier 4 non-inverting input                                                                                                             |  |

| NEG4     | 16     | -      | -      | Operational amplifier 4 inverting input                                                                                                                 |  |

| OUT4     | 17     | -      | -      | Operational amplifier 4 output                                                                                                                          |  |

| POS5     | 18     | -      | -      | Operational amplifier 5 non-inverting input                                                                                                             |  |

| NEG5     | 19     | -      | -      | Operational amplifier 5 inverting input                                                                                                                 |  |

| OUT5     | 20     | -      | -      | Operational amplifier 5 output                                                                                                                          |  |

| LX       | 21     | 21     | 21     | Main boost regulator switch connection                                                                                                                  |  |

| IN       | 22     | 22     | 22     | Main supply input; bypass to AGND with 1µF capacitor                                                                                                    |  |

| FB       | 23     | 23     | 23     | Main boost feedback voltage connection                                                                                                                  |  |

| COMP     | 24     | 24     | 24     | Error amplifier compensation pin                                                                                                                        |  |

| FBP      | 25     | 25     | 25     | Positive LDO feedback connection                                                                                                                        |  |

| DRVP     | 26     | 26     | 26     | Positive LDO transistor drive                                                                                                                           |  |

| FBN      | 27     | 27     | 27     | Negative LDO feedback connection                                                                                                                        |  |

| DRVN     | 28     | 28     | 28     | Negative LDO transistor driver                                                                                                                          |  |

| DEL      | 29     | 29     | 29     | Connection for switch delay timing capacitor                                                                                                            |  |

| CTL      | 30     | 30     | 30     | Input control for switch output                                                                                                                         |  |

| DRN      | 31     | 31     | 31     | Lower reference voltage for switch output                                                                                                               |  |

| СОМ      | 32     | 32     | 32     | Switch output; when CTL = 1, COM is connected to SRC through a $15\Omega$ resistor; when CTL = 0, COM is connected to DRN through a $30\Omega$ resistor |  |

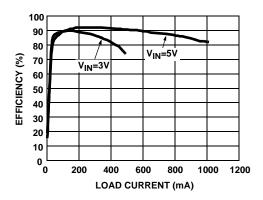

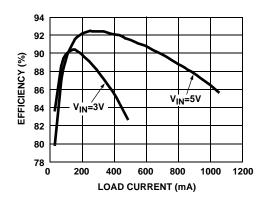

# **Typical Performance Curves**

FIGURE 1. BOOST EFFICIENCY AT V<sub>OUT</sub> = 12V (PI MODE)

FIGURE 2. BOOST EFFICIENCY AT V<sub>OUT</sub> = 12V (P MODE)

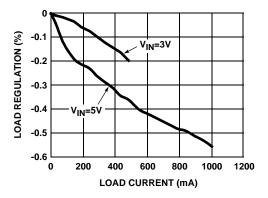

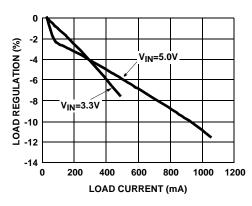

FIGURE 3. BOOST LOAD REGULATION vs LOAD CURRENT (PI MODE)

FIGURE 4. BOOST LOAD REGULATION vs LOAD CURRENT (P MODE)

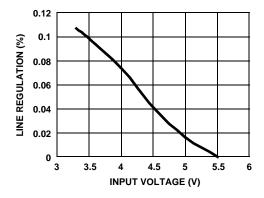

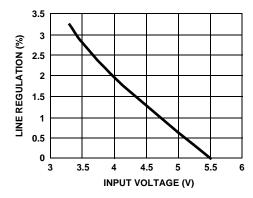

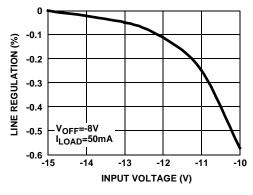

FIGURE 5. BOOST LINE REGULATION vs INPUT VOLTAGE (PI MODE)

FIGURE 6. BOOST LINE REGULATION vs INPUT VOLTAGE (P MODE)

FN7415.1 September 26, 2005

# Typical Performance Curves (Continued)

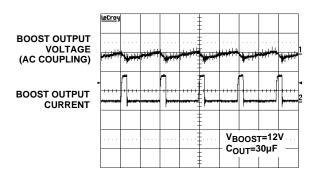

FIGURE 7. BOOST PULSE LOAD TRANSIENT RESPONSE

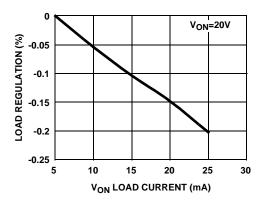

FIGURE 8.  $V_{\mbox{ON}}$  LOAD REGULATION

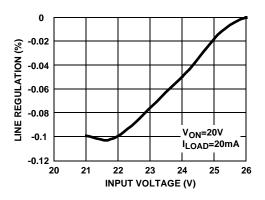

FIGURE 9.  $V_{\mbox{ON}}$  LINE REGULATION

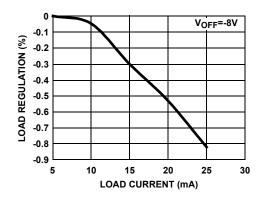

FIGURE 10. V<sub>OFF</sub> LOAD REGULATION

FIGURE 11. V<sub>OFF</sub> LINE REGULATION

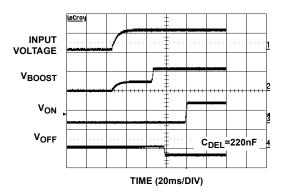

FIGURE 12. START-UP SEQUENCE

### Typical Performance Curves (Continued)

FIGURE 13. START-UP SEQUENCE

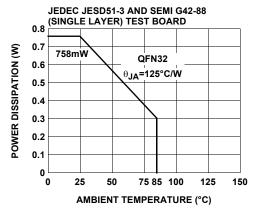

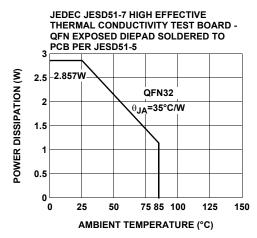

FIGURE 15. PACKAGE POWER DISSIPATION VS AMBIENT TEMPERATURE

## Applications Information

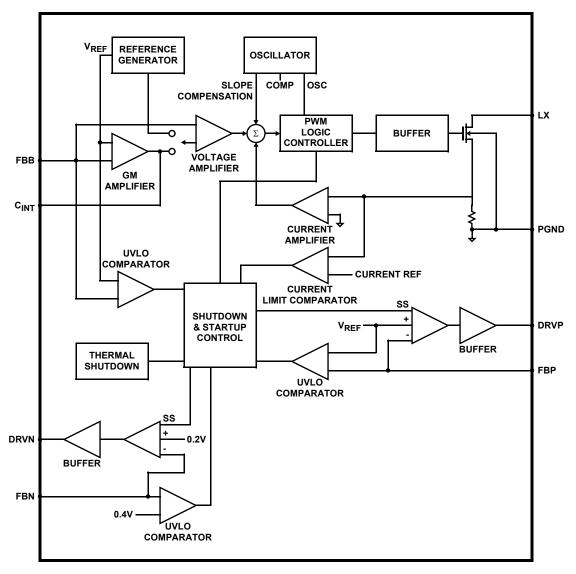

The EL7640, EL7641, EL7642 provide a highly integrated multiple output power solution for TFT-LCD applications. The system consists of one high efficiency boost converter and two low cost linear-regulator controllers (V $_{\rm ON}$  and V $_{\rm OFF}$ ) with multiple protection functions. The block diagram of the whole part is shown in Figure 17. Table 1 lists the recommended components.

The EL7640, EL7641, EL7642 integrate an N-channel MOSFET in boost converter to minimize the external component counts and cost. The  $V_{ON}$ ,  $V_{OFF}$  linear-regulators are independently regulated by using external resistors. To achieve higher voltage than  $V_{BOOST}$ , one or multiple stage charge pumps may be used.

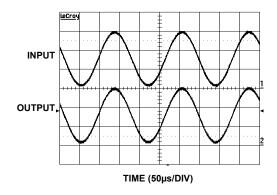

FIGURE 14. OP AMP RAIL-TO-RAIL INPUT/OUTPUT

FIGURE 16. PACKAGE POWER DISSIPATION VS AMBIENT TEMPERATURE

**TABLE 1. RECOMMENDED COMPONENTS**

| DESIGNATION                                         | DESCRIPTION                                                            |

|-----------------------------------------------------|------------------------------------------------------------------------|

| C <sub>1</sub> , C <sub>2</sub> , C <sub>3</sub>    | 10μF, 16V X5R ceramic capacitor (1210)<br>TDK C3216X5R0J106K           |

| D <sub>1</sub>                                      | 1A 20V low leakage schottky rectifier (CASE 457-04) ON SEMI MBRM120ET3 |

| D <sub>11</sub> , D <sub>12</sub> , D <sub>21</sub> | 200mA 30V schottky barrier diode (SOT-23)<br>Fairchild BAT54S          |

| L <sub>1</sub>                                      | 6.8µH 1.3A Inductor<br>TDK SLF6025T-6R8M1R3-PF                         |

| Q <sub>11</sub>                                     | 200mA 40V PNP amplifier (SOT-23)<br>Fairchild MMBT3906                 |

| Q <sub>21</sub>                                     | 200mA 40V NPN amplifier (SOT-23)<br>Fairchild MMBT3904                 |

FIGURE 17. BLOCK DIAGRAM

#### **Boost Converter**

The main boost converter is a current mode PWM converter operating at a fixed frequency. The 1.2MHz switching frequency enables the use of low profile inductor and multilayer ceramic capacitors, which results in a compact, low cost power system for LCD panel design.

The boost converter can operate in continuous or discontinuous inductor current mode. The EL7640, EL7641, EL7642 are designed for continuous current mode, but they can also operate in discontinuous current mode at light load. In continuous current mode, current flows continuously in the inductor during the entire switching cycle in steady state operation. The voltage conversion ratio in continuous current mode is given by:

$$\frac{V_{BOOST}}{V_{IN}} \, = \, \frac{1}{1-D}$$

Where D is the duty cycle of switching MOSFET.

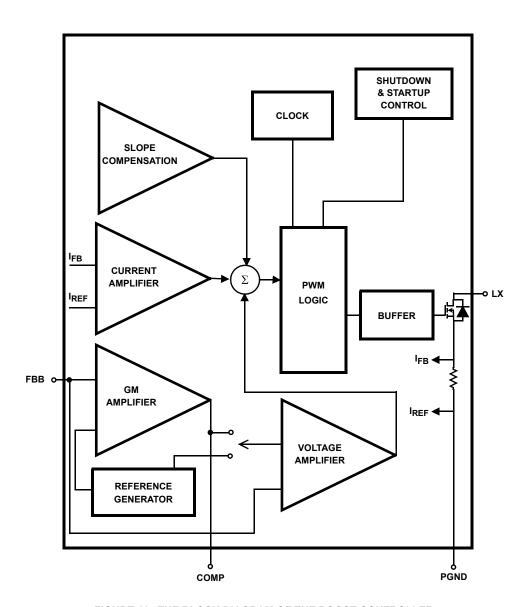

Figure 18 shows the block diagram of the boost controller. It uses a summing amplifier architecture consisting of GM stages for voltage feedback, current feedback and slope compensation. A comparator looks at the peak inductor current cycle by cycle and terminates the PWM cycle if the current limit is reached.

An external resistor divider is required to divide the output voltage down to the nominal reference voltage. Current drawn by the resistor network should be limited to maintain the overall converter efficiency. The maximum value of the resistor network is limited by the feedback input bias current and the potential for noise being coupled into the feedback pin. A resistor network in the order of  $60k\Omega$  is recommended. The boost converter output voltage is determined by the following equation:

$$V_{BOOST} = \frac{R_1 + R_2}{R_1} \times V_{REF}$$

The current through MOSFET is limited to 3A peak. This restricts the maximum output current based on the following equation:

$$I_{OMAX} = \left(I_{LMT} - \frac{\Delta I_L}{2}\right) \times \frac{V_{IN}}{V_O}$$

Where  $\Delta I_{\mbox{\scriptsize L}}$  is peak to peak inductor ripple current, and is set by:

$$\Delta I_{L} = \frac{V_{IN}}{L} \times \frac{D}{f_{S}}$$

where  $f_{\mbox{\scriptsize S}}$  is the switching frequency.

FIGURE 18. THE BLOCK DIAGRAM OF THE BOOST CONTROLLER

The following table gives typical values (margins are considered 10%, 3%, 20%, 10% and 15% on V<sub>IN</sub>, V<sub>O</sub>, L, f<sub>S</sub> and I<sub>I MT</sub>:

TABLE 2.

| V <sub>IN</sub> (V) | V <sub>O</sub> (V) | L (µH) | f <sub>S</sub> (MHz) | I <sub>OMAX</sub> (mA) |

|---------------------|--------------------|--------|----------------------|------------------------|

| 3.3                 | 9                  | 6.8    | 1.2                  | 898                    |

| 3.3                 | 12                 | 6.8    | 1.2                  | 622                    |

| 3.3                 | 15                 | 6.8    | 1.2                  | 458                    |

| 5                   | 9                  | 6.8    | 1.2                  | 1360                   |

| 5                   | 12                 | 6.8    | 1.2                  | 944                    |

| 5                   | 15                 | 6.8    | 1.2                  | 694                    |

#### Input Capacitor

The input capacitor is used to supply the current to the converter. It is recommended that  $C_{IN}$  be larger than  $10\mu F$ . The reflected ripple voltage will be smaller with larger C<sub>IN</sub>. The voltage rating of input capacitor should be larger than maximum input voltage.

#### **Boost Inductor**

The boost inductor is a critical part which influences the output voltage ripple, transient response, and efficiency. Value of  $3.3\mu H$  to  $10\mu H$  inductor is recommended in applications to fit the internal slope compensation. The inductor must be able to handle the following average and peak current:

$$I_{LAVG} = \frac{I_O}{1 - D}$$

$$I_{LPK} = I_{LAVG} + \frac{\Delta I_{L}}{2}$$

#### Rectifier Diode

A high-speed diode is desired due to the high switching frequency. Schottky diodes are recommended because of their fast recovery time and low forward voltage. The rectifier diode must meet the output current and peak inductor current requirements.

### Output Capacitor

The output capacitor supplies the load directly and reduces the ripple voltage at the output. Output ripple voltage consists of two components: the voltage drop due to the inductor ripple current flowing through the ESR of output capacitor, and the charging and discharging of the output capacitor.

$$V_{RIPPLE} = I_{LPK} \times ESR + \frac{V_{O} - V_{IN}}{V_{O}} \times \frac{I_{O}}{C_{OUT}} \times \frac{1}{f_{S}}$$

For low ESR ceramic capacitors, the output ripple is dominated by the charging and discharging of the output capacitor. The voltage rating of the output capacitor should be greater than the maximum output voltage.

NOTE: Capacitors have a voltage coefficient that makes their effective capacitance drop as the voltage across them increases. COLIT in the equation above assumes the effective value of the capacitor at a particular voltage and not the manufacturer's stated value, measured at zero volts.

#### Compensation

The EL7640, EL7641, EL7642 can operate in either P mode or PI mode. Connecting COMP pin directly to V<sub>IN</sub> will enable P mode; For better load regulation, use PI mode with a 2.2nF capacitor and a  $180\Omega$  resistor in series between COMP pin and ground. To improve the transient response, either the resistor value can be increased or the capacitor value can be reduced, but too high resistor value or too low capacitor value will reduce loop stability.

#### **Boost Feedback Resistors**

As the boost output voltage, V<sub>BOOST</sub>, is reduced below 12V the effective voltage feedback in the IC increases the ratio of voltage to current feedback at the summing comparator because R2 decreases relative to R1. To maintain stable operation over the complete current range of the IC, the voltage feedback to the FBB pin should be reduced proportionally, as V<sub>BOOST</sub> is reduced, by means of a series resistor-capacitor network (R7 and C7) in parallel with R1, with a pole frequency (fp) set to approximately 10kHz. for C2 effective =  $10\mu$ F and 4kHz for C2 (effective) =  $30\mu$ F.

$$R7 = ((1/0.1 \times R2) - 1/R1)^{-1}$$

$$C7 = 1/(2 \times 3.142 \times fp \times R7)$$

#### Linear-Regulator Controllers (V<sub>ON</sub> and V<sub>OFF</sub>)

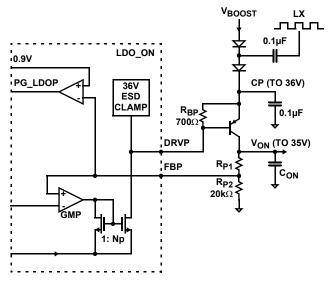

The EL7640, EL7641, EL7642 include 2 independent linear-regulator controllers, in which there is one positive output voltage (V<sub>ON</sub>), and one negative voltage (V<sub>OFF</sub>). The V<sub>ON</sub> and V<sub>OFF</sub> linear-regulator controller function diagram, application circuit and waveforms are shown in Figure 19 and Figure 20 respectively.

FIGURE 19. VON FUNCTIONAL BLOCK DIAGRAM

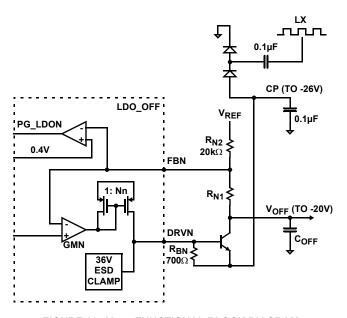

FIGURE 20. V<sub>OFF</sub> FUNCTIONAL BLOCK DIAGRAM

The  $V_{ON}$  power supply is used to power the positive supply of the row driver in the LCD panel. The DC/DC consists of an external diode-capacitor charge pump powered from the inductor (LX) of the boost converter, followed by a low dropout linear regulator (LDO\_ON). The LDO\_ON regulator uses an external PNP transistor as the pass element. The onboard LDO controller is a wide band (>10MHz) transconductance amplifier capable of 5mA output current, which is sufficient for up to 50mA or more output current under the low dropout condition (forced beta of 10). Typical  $V_{ON}$  voltage supported by EL7640, EL7641 and EL7642 ranges from +15V to +36V. A fault comparator is also included for monitoring the output voltage. The undervoltage threshold is set at 25% below the 1.2V reference.

The  $V_{OFF}$  power supply is used to power the negative supply of the row driver in the LCD panel. The DC/DC consists of an external diode-capacitor charge pump powered from the inductor (LX) of the boost converter, followed by a low dropout linear regulator (LDO\_OFF). The LDO\_OFF regulator uses an external NPN transistor as the pass element. The onboard LDO controller is a wide band (>10MHz) transconductance amplifier capable of 5mA output current, which is sufficient for up to 50mA or more output current under the low dropout condition (forced beta of 10). Typical  $V_{OFF}$  voltage supported by EL7640, EL7641 and EL7642 ranges from -5V to -25V. A fault comparator is also included for monitoring the output voltage. The undervoltage threshold is set at 200mV above the 0.2V reference level.

### Set-up Output Voltage

Refer to *Typical Application Diagram*, the output voltages of  $V_{ON}$ ,  $V_{OFF}$  and  $V_{LOGIC}$  are determined by the following equations:

$$V_{ON} = V_{REF} \times \left(1 + \frac{R_{12}}{R_{11}}\right)$$

$$V_{OFF} = V_{REFN} + \frac{R_{22}}{R_{21}} \times (V_{REFN} - V_{REF})$$

Where  $V_{REF} = 1.2V$ ,  $V_{REFN} = 0.2V$ .

# High Charge Pump Output Voltage (>36V) Applications

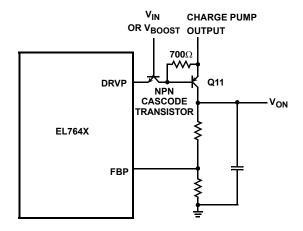

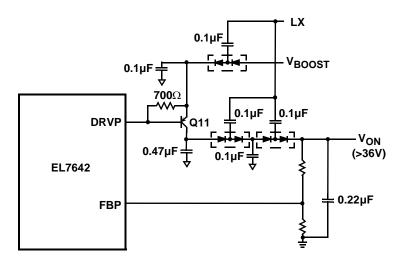

In the applications where the charge pump output voltage is over 36V, an external NPN transistor needs to be inserted in between the DRVP pin and the base of pass transistor Q3 as shown in Figure 21, or the linear regulator can control only one stage charge pump and regulate the final charge pump output as shown in Figure 22.

FIGURE 21. CASCODE NPN TRANSISTOR CONFIGURATION FOR HIGH CHARGE PUMP OUTPUT VOLTAGE (>36V)

13

FIGURE 22. THE LINEAR REGULATOR CONTROLS ONE STAGE OF CHARGE PUMP

# Calculation of the Linear Regulator Base-emitter Resistors (RBP and RBN)

For the pass transistor of the linear regulator, low frequency gain (Hfe) and unity gain frequency (fT) are usually specified in the datasheet. The pass transistor adds a pole to the loop transfer function at fp = fT/Hfe. Therefore, in order to maintain phase margin at low frequency, the best choice for a pass device is often a high frequency low gain switching transistor. Further improvement can be obtained by adding a base-emitter resistor  $R_{BE}$  ( $R_{BP}$ ,  $R_{BL}$ ,  $R_{BN}$  in the Functional Block Diagram), which increases the pole frequency to: fp = fT\*(1+ Hfe \*re/R\_{BE})/Hfe, where re = KT/qlc. So choose the lowest value  $R_{BE}$  in the design as long as there is still enough base current ( $I_B$ ) to support the maximum output current ( $I_C$ ).

We will take as an example the  $V_{ON}$  linear regulator. If a Fairchild MMBT3906 PNP transistor is used as the external pass transistor, Q11 in the application diagram, then for a maximum  $V_{ON}$  operating requirement of 50mA the data sheet indicates Hfe\_min = 60. The base-emitter saturation voltage is: Vbe\_max = 0.7V.

For the EL7540, EL7541 and EL7542, the minimum drive current is:

The minimum base-emitter resistor, RBP, can now be calculated as:

RBP\_min = VBE\_max/(I\_DRVP\_min - Ic/Hfe\_min) =  $0.7V/(2mA - 50mA/60) = 600\Omega$

This is the minimum value that can be used – so, we now choose a convenient value greater than this minimum value; say  $700\Omega$ . Larger values may be used to reduce quiescent current, however, regulation may be adversely affected by supply noise if  $R_{BP}$  is made too high in value.

## Charge Pump

To generate an output voltage higher than  $V_{BOOST}$ , single or multiple stages of charge pumps are needed. The number of stage is determined by the input and output voltage. For positive charge pump stages:

$$N_{POSITIVE} \ge \frac{V_{OUT} + V_{CE} - V_{INPUT}}{V_{INPUT} - 2 \times V_{F}}$$

where  $V_{CE}$  is the dropout voltage of the pass component of the linear regulator. It ranges from 0.3V to 1V depending on the transistor selected.  $V_F$  is the forward-voltage of the charge-pump rectifier diode.

The number of negative charge-pump stages is given by:

$$N_{NEGATIVE} \ge \frac{|V_{OUTPUT}| + V_{CE}}{V_{INPUT} - 2 \times V_{F}}$$

To achieve high efficiency and low material cost, the lowest number of charge-pump stages, which can meet the above requirements, is always preferred.

#### **Charge Pump Output Capacitors**

Ceramic capacitor with low ESR is recommended. With ceramic capacitors, the output ripple voltage is dominated by the capacitance value. The capacitance value can be chosen by the following equation:

$$C_{OUT} \ge \frac{I_{OUT}}{2 \times V_{RIPPLE} \times f_{OSC}}$$

where f<sub>OSC</sub> is the switching frequency.

# Discontinuous/Continuous Boost Operation and its Effect on the Charge Pumps

The EL7640, EL7641 and EL7642  $V_{ON}$  and  $V_{OFF}$  architecture uses LX switching edges to drive diode charge pumps from which LDO regulators generate the  $V_{ON}$  and

$V_{OFF}$  supplies. It can be appreciated that should a regular supply of LX switching edges be interrupted, for example during discontinuous operation at light boost load currents, then this may affect the performance of  $V_{ON}$  and  $V_{OFF}$  regulation – depending on their exact loading conditions at the time.

To optimize  $V_{ON}/V_{OFF}$  regulation, the boundary of discontinuous/continuous operation of the boost converter can be adjusted, by suitable choice of inductor given  $V_{IN}$ ,  $V_{OUT}$ , switching frequency and the  $V_{BOOST}$  current loading, to be in continuous operation.

The following equation gives the boundary between discontinuous and continuous boost operation. For continuous operation (LX switching every clock cycle) we require that:

$I(V_{BOOST\_load}) > D*(1-D)*V_{IN}/(2*L*F_{OSC})$

where the duty cycle, D =  $(V_{BOOST} - V_{IN})/V_{BOOST}$

For example, with  $V_{IN}$  = 5V,  $F_{OSC}$  = 1.2MHz and  $V_{BOOST}$  = 12V we find continuous operation of the boost converter can be guaranteed for:

$L = 10\mu H$  and  $I(V_{BOOST}) > 51mA$

$L = 6.8\mu H$  and  $I(V_{BOOST}) > 74mA$

$L = 3.3\mu H$  and  $I(V_{BOOST}) > 153mA$

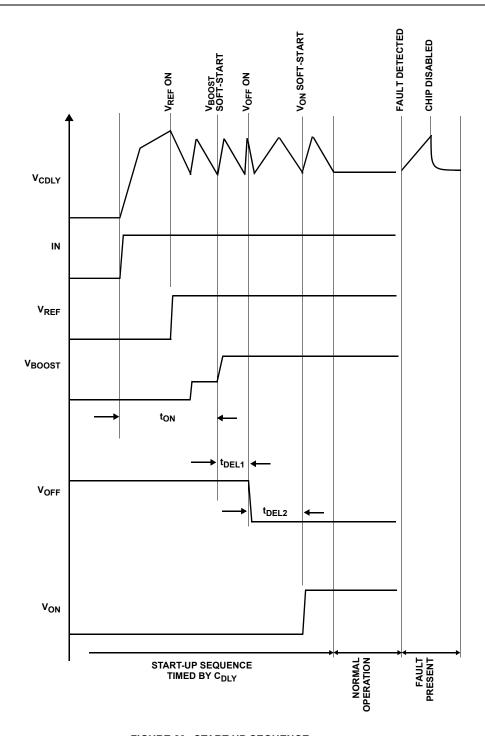

### Start-up Sequence

Figure 23 shows a detailed start-up sequence waveform. For a successful power-up, there should be 6 peaks at  $V_{CDLY}$ . When a fault is detected, the device will latch off until either EN is toggled or the input supply is recycled.

When the input voltage is higher than 2.4V, an internal current source starts to charge  $C_{CDLY}$ . During the initial slow ramp, the device checks whether there is a fault condition. If no fault is found during the initial ramp,  $C_{CDLY}$  is discharged after the first peak.  $V_{REF}$  turns on at the peak of the first ramp.

Initially the boost is not enabled so  $V_{BOOST}$  rises to  $V_{IN}$ - $V_{DIODE}$  through the output diode. Hence, there is a step at  $V_{BOOST}$  during this part of the start-up sequence.

$V_{BOOST}$  soft-starts at the beginning of the third ramp, and is checked at the end of this ramp. The soft-start ramp depends on the value of the  $C_{DLY}$  capacitor. For  $C_{DLY}$  of 220nF, the soft-start time is ~2ms.

V<sub>OFF</sub> turns on at the start of the fourth peak.

$V_{\mbox{ON}}$  is enabled at the beginning of the sixth ramp.  $V_{\mbox{OFF}}$  and  $V_{\mbox{ON}}$  are checked at end of this ramp.

FIGURE 23. START-UP SEQUENCE

# Component Selection for Start-up Sequencing and Fault Protection

The  $C_{REF}$  capacitor is typically set at 220nF and is required to stabilize the  $V_{REF}$  output. The range of  $C_{REF}$  is from 22nF to 1 $\mu$ F and should not be more than five times the capacitor on  $C_{DEL}$  to ensure correct start-up operation.

The  $C_{DEL}$  capacitor is typically 220nF and has a usable range from 47nF minimum to several microfarads – only limited by the leakage in the capacitor reaching  $\mu A$  levels.  $C_{DEL}$  should be at least 1/5 of the value of  $C_{REF}$  (see above). Note with 220nF on  $C_{DEL}$  the fault time-out will be typically 50ms and the use of a larger/smaller value will vary this time proportionally (e.g.  $1\mu F$  will give a fault time-out period of typically 230ms).

#### Fault Sequencing

The EL7640, EL7641 and EL7642 have an advanced fault detection system which protects the IC from both adjacent pin shorts during operation and shorts on the output supplies. A high quality layout/design of the PCB, in respect of grounding quality and decoupling is necessary to avoid falsely triggering the fault detection scheme – especially during start-up. The user is directed to the layout guidelines and component selection sections to avoid problems during initial evaluation and prototype PCB generation.

#### **VON-slice Circuit**

The  $V_{ON}$ -slice circuit functions as a three way multiplexer, switching the voltage on COM between ground, DRN and SRC, under control of the start-up sequence and the CTL pin.

During the start-up sequence, COM is held at ground via an NDMOS FET, with ~1K impedance. Once the start-up sequence has completed ( $C_{DELAY}$  stabilizes at ~1.18V), COM moves to the voltage on DRN. One clock cycle later, CTL is enabled and acts as a multiplexer control such that if CTL = 0, COM = DRN, CTL =  $V_{IN}$ , COM = SRC.

### Op Amps

The EL7640, EL7641 and EL7642 have 1, 3 and 5 amplifiers respectively. The op amps are typically used to drive the TFT-LCD backplane ( $V_{COM}$ ) or the gamma-correction divider string. They feature rail-to-rail input and output capability, they are unity gain stable, and have low power consumption (typical  $600\mu A$  per amplifier). The EL7640, EL7641 and EL7642 have a -3dB bandwidth of 12MHz while maintaining a  $10V/\mu s$  slew rate.

#### Short Circuit Current Limit

The EL7640, EL7641 and EL7642 will limit the short circuit current to  $\pm 180$ mA if the output is directly shorted to the positive or the negative supply. If an output is shorted for a long time, the junction temperature will trigger the Over Temperature Protection limit and hence the part will shut down.

#### **Driving Capacitive Loads**

EL7640, EL7641 and EL7642 can drive a wide range of capacitive loads. As load capacitance increases, however, the –3dB bandwidth of the device will decrease and the peaking will increase. The amplifiers drive 10pF loads in parallel with 10k $\Omega$  with just 1.5dB of peaking, and 100pF with 6.4dB of peaking. If less peaking is desired in these applications, a small series resistor (usually between  $5\Omega$  and  $50\Omega$ ) can be placed in series with the output. However, this will obviously reduce the gain. Another method of reducing peaking is to add a "snubber" circuit at the output. A snubber is a shunt load consisting of a resistor in series with a capacitor. Values of  $150\Omega$  and 10nF are typical. The advantage of a snubber is that it does not draw any DC load current and reduce the gain.

### Over-Temperature Protection

An internal temperature sensor continuously monitors the die temperature. In the event that the die temperature exceeds the thermal trip point, the device will shut down. The upper and lower trigger points are typically set to 130°C and -90°C respectively.

### Layout Recommendation

The device's performance including efficiency, output noise, transient response and control loop stability is dramatically affected by the PCB layout. PCB layout is critical, especially at high switching frequency.

There are some general guidelines for layout:

- Place the external power components (the input capacitors, output capacitors, boost inductor and output diodes, etc.) in close proximity to the device. Traces to these components should be kept as short and wide as possible to minimize parasitic inductance and resistance.

- 2. Place V<sub>REF</sub> and V<sub>DD</sub> bypass capacitors close to the pins.

- Reduce the loop with large AC amplitudes and fast slew rate.

- The feedback network should sense the output voltage directly from the point of load, and be as far away from LX node as possible.

- 5. The power ground (PGND) and signal ground (SGND) pins should be connected at only one point.

- 6. The exposed die plate, on the underneath of the package, should be soldered to an equivalent area of metal on the PCB. This contact area should have multiple via connections to the back of the PCB as well as connections to intermediate PCB layers, if available, to maximize thermal dissipation away from the IC.

- 7. To minimize the thermal resistance of the package when soldered to a multi-layer PCB, the amount of copper track and ground plane area connected to the exposed die plate should be maximized and spread out as far as possible from the IC. The bottom and top PCB areas especially should be maximized to allow thermal dissipation to the surrounding air.

- 8. A signal ground plane, separate from the power ground plane and connected to the power ground pins only at the exposed die plate, should be used for ground return connections for feedback resistor networks (R1, R11, R41) and the V<sub>REF</sub> capacitor, C22, the C<sub>DELAY</sub> capacitor C7 and the integrator capacitor C23.

- Minimize feedback input track lengths to avoid switching noise pick-up.

A demo board is available to illustrate the proper layout implementation.

# **Typical Application Circuit**

## QFN Package Outline Drawing

NOTE: The package drawing shown here may not be the latest version. To check the latest revision, please refer to the Intersil website at http://www.intersil.com/design/packages/index.asp

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com