# RENESAS

EL7584

## 4-Channel DC/DC Converter

#### OBSOLETE PRODUCT FOR A POSSIBLE SUBSTITUTE PRODUCT contact our Technical Support Center at 1-888-INTERSIL or www.intersil.com/tsc

## DATASHEET

FN7317 Rev 2.00 February 4, 2005

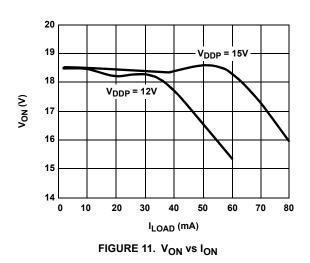

The EL7584 is a 4-channel DC/DC converter IC which is designed primarily for use in TFT-LCD applications. The boost converter has 2V to 14V input capability and provides 5V to 17V output, which powers the column drivers and provides up to 370mA @ 15V. A pair of charge pump control circuits provide outputs to allow the external generation of  $V_{ON}$  and  $V_{OFF}$  supplies at 5V to 40V and 0V to -40V, respectively, each at up to 60mA for  $V_{BOOST}$  = 15V. The  $V_{COM}$  buffer provides up to 50mA continuous output current from 2V to 13V.

The EL7584 features adjustable switching frequency and onchip power sequence to simplify start-up operation. A separate input is available to externally increase the default delay of the positive charge pump. An over-temperature feature is provided to allow the IC to be automatically protected from excessive power dissipation.

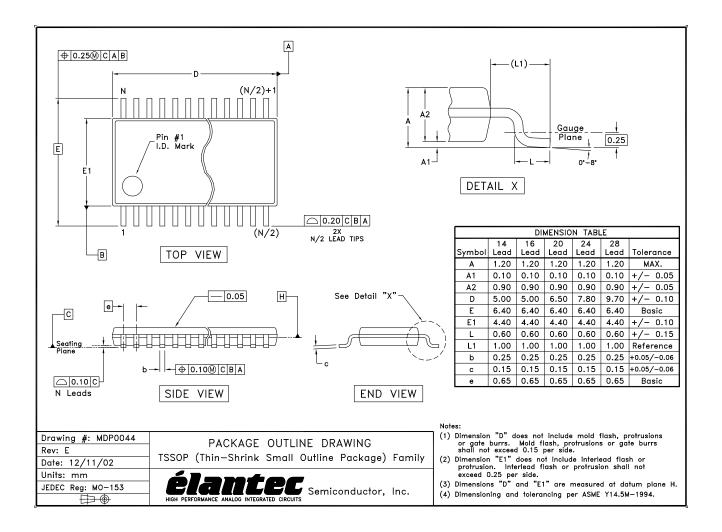

The EL7584 is available in a 24-pin TSSOP package and is specified for operation over the full -40°C to +85°C temperature range.

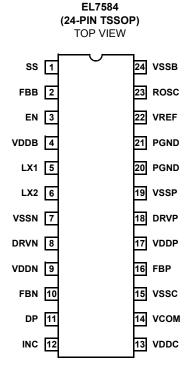

## Pinout

## Features

- TFT-LCD display supply

- Boost regulator

- V<sub>COM</sub> buffer

- V<sub>ON</sub> charge pump

- V<sub>OFF</sub> charge pump

- + 2V to 14V  $\rm V_{IN}$  supply

- 5V < V<sub>BOOST</sub> < 17V

- 2V < V<sub>COM</sub> < 13V

- 5V < V<sub>ON</sub> < 40V

- -40V < V<sub>OFF</sub> < 0V

- V<sub>BOOST</sub> = 15V @ 370mA

- High frequency, small inductor DC/DC boost circuit

- Over 90% efficient DC/DC boost converter capability

- Built-in power-up sequence with adjustable  $\mathsf{V}_{ON}$  delay

- Adjustable frequency

- Adjustable soft-start

- Adjustable outputs

- Over-temperature protection

- Small parts count

- Pb-free available (RoHS compliant)

## Applications

- TFT-LCD panels

- PDAs

## **Ordering Information**

| PART<br>NUMBER                                    | PACKAGE                   | TAPE & REEL | PKG. DWG. # |

|---------------------------------------------------|---------------------------|-------------|-------------|

| EL7584IR                                          | 24-Pin TSSOP              | -           | MDP0044     |

| EL7584IR-T7                                       | 24-Pin TSSOP              | 7"          | MDP0044     |

| EL7584IR-T13                                      | 24-Pin TSSOP              | 13"         | MDP0044     |

| EL7584IRZ<br>(See Note)                           | 24-Pin TSSOP<br>(Pb-free) | -           | MDP0044     |

| EL7584IRZ-T7 24-Pin TSSOP<br>(See Note) (Pb-free) |                           | 7"          | MDP0044     |

| EL7584IRZ-<br>T13 (See Note)                      | 24-Pin TSSOP<br>(Pb-free) | 13"         | MDP0044     |

NOTE: Intersil Pb-free products employ special Pb-free material sets; molding compounds/die attach materials and 100% matte tin plate termination finish, which are RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

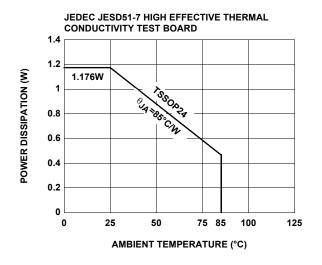

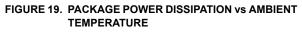

#### Absolute Maximum Ratings (T<sub>A</sub> = 25°C)

| LX Pin Voltage                                             |

|------------------------------------------------------------|

| V <sub>DDB</sub> , V <sub>DDP</sub> , V <sub>DDN</sub>     |

| V <sub>DDC</sub>                                           |

| Maximum Continuous V <sub>BOOST</sub> Output Current 800mA |

Storage Temperature

-65°C to +150°C

Ambient Operating Temperature

-40°C to +85°C

Power Dissipation

See Curves

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

IMPORTANT NOTE: All parameters having Min/Max specifications are guaranteed. Typ values are for information purposes only. Unless otherwise noted, all tests are at the specified temperature and are pulsed tests, therefore:  $T_J = T_C = T_A$

| <b>Electrical Specifications</b> | $V_{IN}$ = 3.3V, $V_{BOOST}$ = 12V, $R_{OSC}$ = 62k $\Omega$ , $T_A$ = 25°C, Unless Otherwise Specified. |

|----------------------------------|----------------------------------------------------------------------------------------------------------|

|----------------------------------|----------------------------------------------------------------------------------------------------------|

| PARAMETER                          | DESCRIPTION                                 | CONDITIONS                                                                                                                          | MIN   | TYP   | MAX   | UNIT     |

|------------------------------------|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|----------|

| DC/DC BOOST                        | CONVERTER                                   | *                                                                                                                                   |       |       |       | <u> </u> |

| IQ1_B                              | Quiescent Current - Shut-down               | EN = 0V                                                                                                                             |       | 0.8   | 10    | μA       |

| IQ2_B                              | Quiescent Current - Switching               | EN = V <sub>DDB</sub>                                                                                                               |       | 4.8   | 8     | mA       |

| V(FBB)                             | Feedback Voltage                            |                                                                                                                                     | 1.275 | 1.300 | 1.325 | V        |

| V <sub>REF</sub>                   | Reference Voltage                           |                                                                                                                                     | 1.260 | 1.310 | 1.360 | V        |

| V <sub>ROSC</sub>                  | Oscillator Set Voltage                      |                                                                                                                                     | 1.260 | 1.325 | 1.390 | V        |

| I(FBB)                             | Feedback Input Bias Current                 |                                                                                                                                     |       | 0.1   |       | μA       |

| V <sub>DDB</sub>                   | Boost Converter Supply Range                |                                                                                                                                     | 2     |       | 17    | V        |

| D <sub>MAX</sub>                   | Maximum Duty Cycle                          |                                                                                                                                     | 85    | 92    |       | %        |

| I(LX) <sub>MAX</sub>               | Peak Internal FET Current                   |                                                                                                                                     |       | 1.75  |       | Α        |

| R <sub>DS-ON</sub>                 | Switch On Resistance                        | at V <sub>BOOST</sub> = 10V, I(LX) total = 350mA                                                                                    |       | 0.22  |       | Ω        |

| ILEAK-SWITCH                       | Switch Leakage Current                      | I(LX) total                                                                                                                         |       |       | 1     | μA       |

| V <sub>BOOST</sub>                 | Output Range                                | V <sub>BOOST</sub> > V <sub>IN</sub> + V <sub>DIODE</sub>                                                                           | 5     |       | 17    | V        |

| $\Delta V_{BOOST} / \Delta V_{IN}$ | Line Regulation                             | 2.7V < V <sub>IN</sub> < 13.2V, V <sub>BOOST</sub> = 15V                                                                            |       | 0.1   |       | %        |

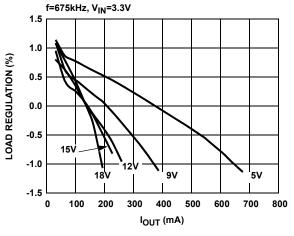

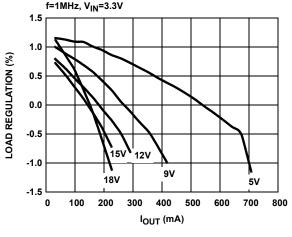

| $\Delta V_{BOOST} / \Delta I_{O1}$ | Load Regulation                             | 50mA < I <sub>O1</sub> < 250mA                                                                                                      |       | 0.5   |       | %        |

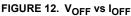

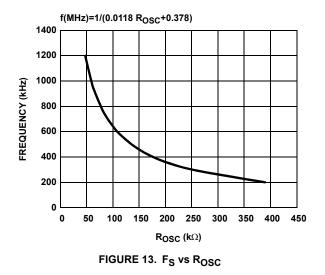

| F <sub>OSC-RANGE</sub>             | Frequency Range                             | $R_{OSC}$ range = 240k $\Omega$ to 60k $\Omega$                                                                                     | 200   |       | 1200  | kHz      |

| F <sub>OSC1</sub>                  | Switching Frequency                         | $R_{OSC} = 62k\Omega$                                                                                                               | 900   | 1000  | 1100  | kHz      |

| V <sub>COM</sub> BUFFER            |                                             |                                                                                                                                     |       |       |       | L        |

| V <sub>DDC</sub>                   | Supply Voltage Range                        |                                                                                                                                     | 6     |       | 15    | V        |

| IQ1, V <sub>DDC</sub>              | V <sub>DDC</sub> Disable Current            | V <sub>DDC</sub> = 12V, EN = 0V                                                                                                     |       | 5.5   | 20    | μA       |

| IQ2, V <sub>DDC</sub>              | V <sub>DDC</sub> Enable Current             | $V_{DDC}$ = 12V, $V_{EN}$ = $V_{DDB}$ , no load                                                                                     |       | 1.7   | 5     | mA       |

| V <sub>COM</sub> -offset           | Accuracy of V <sub>COM</sub> Output Voltage | 2V < V <sub>COM</sub> < (V <sub>DDC</sub> - 2V)                                                                                     | -10   |       | +10   | mV       |

| I(INC)                             | V <sub>COM</sub> Input Bias Currents        | Current magnitude                                                                                                                   | -0.1  | 0.01  | 0.1   | μA       |

| R <sub>O</sub> (V <sub>COM</sub> ) | V <sub>COM</sub> Output Impedance           | $V_{DDC}$ = $V_{BOOST}$ = 12V, $V_{COM}$ = 6V with<br>-100mA < I <sub>LOAD</sub> < 100mA<br>$C_{LOAD}$ for $V_{COM}$ > 0.47µF, MLCC |       | 0.25  |       | Ω        |

| I <sub>COM</sub> (max)             | Output Current Limit                        |                                                                                                                                     |       | 150   |       | mA       |

| PSRR                               | Supply Voltage Rejection                    | V <sub>INC</sub> = V <sub>DDC/2</sub> , 9V < V <sub>DDC</sub> < 15V                                                                 | 60    | 102   |       | dB       |

| CMRR                               | Common Mode Voltage Rejection               | V <sub>DDC</sub> = 12V, 2V < V <sub>INC</sub> < 10V                                                                                 | 60    | 93    |       | dB       |

| PARAMETER              | DESCRIPTION                                 | CONDITIONS                                                           | MIN                   | ТҮР        | MAX       | UNIT    |

|------------------------|---------------------------------------------|----------------------------------------------------------------------|-----------------------|------------|-----------|---------|

|                        |                                             | $V_{\text{DDP}}$ input voltage (normally connected to $V_{\text{B}}$ | <sub>OOST</sub> ) and | d the exte | rnal comp | onent   |

| V <sub>DDP</sub>       | Supply Input for Positive Charge Pump       | Usually connected to V <sub>BOOST</sub> output                       | 5                     |            | 17        | V       |

| IQ1(V <sub>DDP</sub> ) | Quiescent Current - Shut-down               | EN = 0V                                                              |                       | 11.5       | 20        | μA      |

| IQ2(V <sub>DDP</sub> ) | Quiescent Current - Switching               | EN = V <sub>DDB</sub>                                                |                       | 2.3        | 5         | mA      |

| I <sub>DP1</sub>       | Disable Charge Current                      | EN = 0V, DP = 0V                                                     | 1.5                   | 1.9        | 2.5       | mA      |

| I <sub>DP2</sub>       | Enable Discharge Current                    | EN = V <sub>DDB</sub> , DP = 5V                                      | 100                   | 200        | 300       | nA      |

| V(FBP)                 | Feedback Reference Voltage                  |                                                                      | 1.245                 | 1.310      | 1.375     | V       |

| I(FBP)                 | Feedback Input Bias Current                 |                                                                      |                       | 0.1        |           | μA      |

| I(DRVP)                | RMS DRVP Output Current                     | V <sub>DDP</sub> = 12V                                               |                       | 60         |           | mA      |

|                        |                                             | V <sub>DDP</sub> = 6V                                                | 15                    |            |           | mA      |

| ILR_V <sub>ON</sub>    | Load Regulation                             | 5mA < I <sub>L</sub> < 15mA                                          | -0.5                  | 0.03       | 0.5       | %/mA    |

| F <sub>PUMP</sub>      | Charge Pump Frequency                       | Frequency set by R <sub>OSC</sub> - see boost section                | 0.5*F <sub>OSC</sub>  |            |           |         |

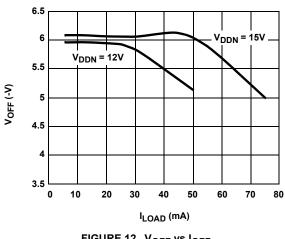

| V <sub>DDN</sub>       |                                             | ne V <sub>DDN</sub> input voltage (normally connected to V           | 5                     |            | 17        | V       |

| IQ1(V <sub>DDN</sub> ) | Quiescent Current - Shut-down               | ENBN = 0V                                                            | 5                     | 4.5        | 20        | ν<br>μA |

| IQ2(V <sub>DDN</sub> ) | Quiescent Current - Switching               | ENBN = V <sub>DDB</sub>                                              |                       | 2.3        | 5         | mA      |

| V(FBN)                 | Feedback Reference Voltage                  | ENDIA - ADDR                                                         | -80                   | 0          | +80       | mV      |

| I(FBN)                 | Feedback Input Bias Current                 | Magnitude of input bias                                              | -00                   | 0.1        | .00       | μΑ      |

| I(DRVN)                | RMS DRVN Output Current                     | V <sub>DDN</sub> = 12V                                               |                       | 60         |           | mA      |

| ()                     |                                             | $V_{\text{DDN}} = 6V$                                                | 15                    |            |           | mA      |

| ILR_V <sub>OFF</sub>   | Load Regulation                             | -15mA < I <sub>L</sub> < -5mA                                        | -0.5                  | 0.03       | 0.5       | %/mA    |

| F <sub>PUMP</sub>      | Charge Pump Frequency                       | Frequency set by R <sub>OSC</sub> - see boost section                | 0.5*F <sub>OSC</sub>  |            |           |         |

| ENABLE CONT            | ROL LOGIC                                   |                                                                      |                       |            |           |         |

| V <sub>HI</sub> -EN    | Enable Input High Threshold                 |                                                                      | 1.6                   |            |           | V       |

| V <sub>LO</sub> -EN    | Enable Input Low Threshold                  |                                                                      |                       |            | 0.5       | V       |

| I(EN)                  | Enable Input Bias Current                   | V <sub>EN</sub> = 5V                                                 |                       | 3.7        | 7.5       | μA      |

|                        | <u> </u>                                    | 1                                                                    | 1                     | I          | 1         | 1       |

| OVER-TEMPER            | ATURE PROTECTION                            |                                                                      |                       |            |           |         |

| OVER-TEMPER            | ATURE PROTECTION Over-temperature Threshold |                                                                      |                       | 130        |           | °C      |

| PIN NUMBER | PIN NAME | PIN TYPE | PIN FUNCTION                                                                                                                                                                 |  |

|------------|----------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1          | SS       | I        | Soft-Start input: a capacitor determines the current limit ramp time.                                                                                                        |  |

| 2          | FBB      | I        | Voltage feedback input determines the value of V <sub>BOOST</sub> .                                                                                                          |  |

| 3          | EN       | I        | Starts internal power sequencing of V <sub>BOOST</sub> , V <sub>OFF</sub> , V <sub>COM</sub> and V <sub>ON</sub> outputs (See Applications Information) ; active HIGH input. |  |

| 4          | VDDB     | Р        | Positive supply for V <sub>BOOST</sub> DC/DC controller.                                                                                                                     |  |

| 5          | LX1      | 0        | Boost inductor saturating MOSFET #1.                                                                                                                                         |  |

| 6          | LX2      | 0        | Boost inductor saturating MOSFET #2.                                                                                                                                         |  |

| 7          | VSSN*    | Р        | Ground return for V <sub>OFF</sub> regulator.                                                                                                                                |  |

| 8          | DRVN     | 0        | Pump capacitor driver for V <sub>OFF</sub> regulator.                                                                                                                        |  |

| 9          | VDDN     | Р        | Positive supply for V <sub>OFF</sub> regulator.                                                                                                                              |  |

| 10         | FBN      | I        | Voltage feedback input determines the value of VOFF.                                                                                                                         |  |

| 11         | DP       | I        | An external capacitor increases V <sub>ON</sub> power up delay time.                                                                                                         |  |

| 12         | INC      | I        | V <sub>COM</sub> Buffer input.                                                                                                                                               |  |

| 13         | VDDC     | Р        | Positive supply for V <sub>COM</sub> Buffer.                                                                                                                                 |  |

| 14         | VCOM     | 0        | V <sub>COM</sub> Buffer output.                                                                                                                                              |  |

| 15         | VSSC*    | Р        | Ground return for V <sub>COM</sub> Buffer.                                                                                                                                   |  |

| 16         | FBP      | I        | Voltage feedback input determines the value of VON.                                                                                                                          |  |

| 17         | VDDP     | Р        | Positive supply for V <sub>ON</sub> regulator.                                                                                                                               |  |

| 18         | DRVP     | 0        | Pump capacitor driver for V <sub>ON</sub> regulator.                                                                                                                         |  |

| 19         | VSSP*    | Р        | Ground return for V <sub>ON</sub> regulator.                                                                                                                                 |  |

| 20         | PGND*    | Р        | Ground return for MOSFET #1.                                                                                                                                                 |  |

| 21         | PGND*    | Р        | Ground return for MOSFET #2.                                                                                                                                                 |  |

| 22         | VREF     | 0        | Voltage reference for V <sub>OFF</sub> feedback .                                                                                                                            |  |

| 23         | ROSC     | I        | An external resistor sets the DC/DC switching frequency.                                                                                                                     |  |

| 24         | VSSB*    | Р        | Ground return for V <sub>BOOST</sub> DC/DC controller.                                                                                                                       |  |

**Pin Descriptions** I = Input, O = Output, S = Supply

NOTE: \*VSSB, VSSC, VSSN, VSSP, and PGND (2) are shorted internally to the device substrate.

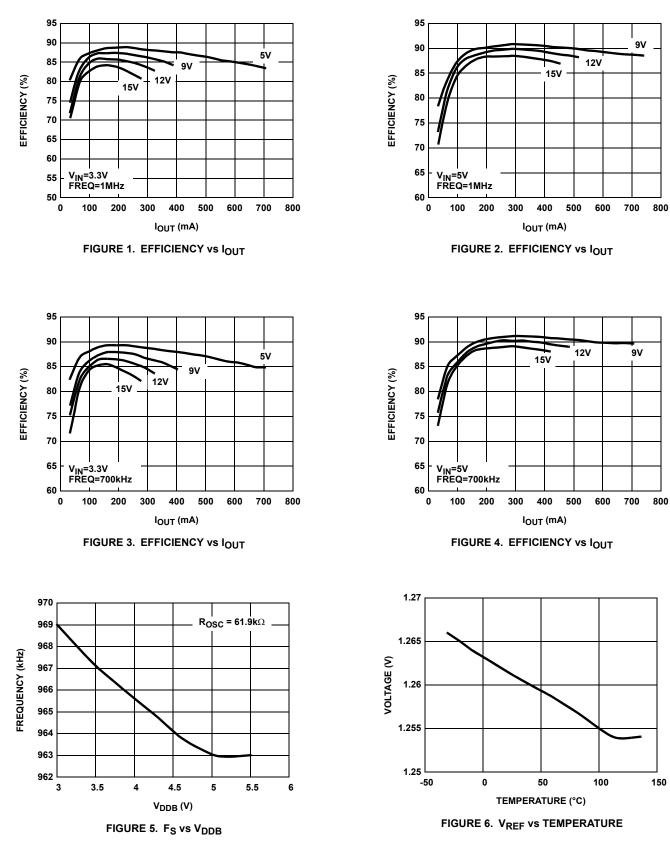

## **Typical Performance Curves**

RENESAS

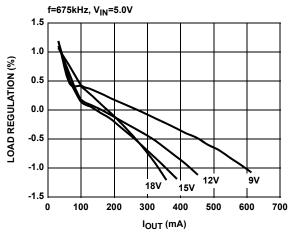

## Typical Performance Curves (Continued)

FIGURE 7. LOAD REGULATION vs IOUT

FIGURE 8. LOAD REGULATION vs IOUT

## Typical Performance Curves (Continued)

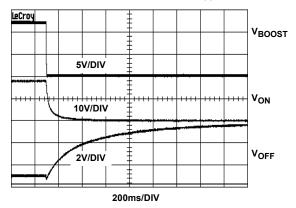

100K & 0.1µF DELAY NETWORK ON ENP, C<sub>SS</sub>=0.1µF

FIGURE 15. POWER-DOWN

V<sub>IN</sub>=3.3V, V<sub>OUT</sub>=11.3V, I<sub>OUT</sub>=50mA

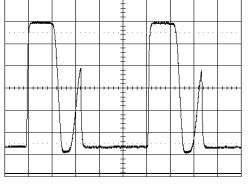

FIGURE 17. LX WAVEFORM - DISCONTINUOUS MODE

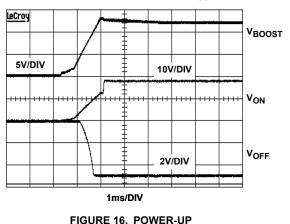

100K & 0.1µF DELAY NETWORK ON ENP, CSS=0.1µF

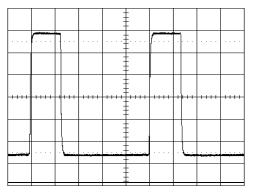

V<sub>IN</sub>=3.3V, V<sub>OUT</sub>=11.3V, I<sub>OUT</sub>=250mA

## Typical Performance Curves (Continued)

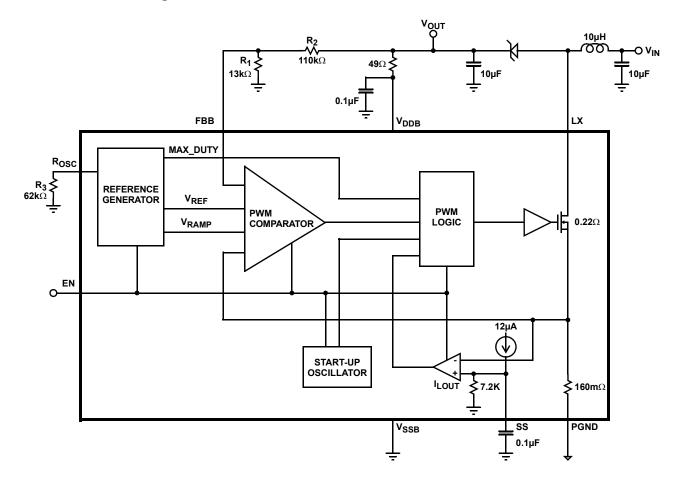

## Functional Block Diagram

## Applications Information

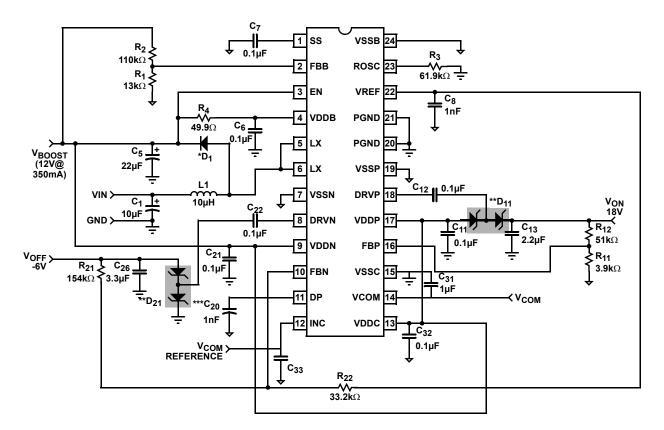

The EL7584 is high efficiency multiple output power solution designed specifically for thin-film transistor (TFT) liquid crystal display (LCD) applications. The device contains one high current boost converter and two low power charge pumps ( $V_{ON}$  and  $V_{OFF}$ ).

The boost converter contains an integrated N-channel MOSFET to minimize the number of external components. The converter output voltage can be set from 5V to 18V with external resistors. The V<sub>ON</sub> and V<sub>OFF</sub> charge pumps are independently regulated to positive and negative voltages using external resistors. Output voltages as high as 40V can be achieved with additional capacitors and diodes.

#### **Boost Converter**

The boost converter operates in constant frequency pulsewidth-modulation (PWM) mode. Quiescent current for the EL7584 is only 5mA when enabled, and since only the low side MOSFET is used, switch drive current is minimized. 90% efficiency is achieved in most common application operating conditions.

A functional block diagram with typical circuit configuration is shown on previous page. Regulation is performed by the PWM comparator which regulates the output voltage by comparing a divided output voltage with an internal reference voltage. The PWM comparator outputs its result to the PWM logic. The PWM logic switches the MOSFET on and off through the gate drive circuit. Its switching frequency is external adjustable with a resistor from timing control pin (R<sub>OSC</sub>) to ground. The boost converter has 200kHz to 1.2MHz operating frequency range.

#### Start-Up

After  $V_{DDB}$  reaches a threshold of about 2V, the power MOSFET is controlled by the start-up oscillator, which generates fixed duty-ratio of 0.5 - 0.7 at a frequency of several hundred kilohertz. This will boost the output voltage, providing the initial output current load is not too great (<250mA).

When  $V_{DDB}$  reaches about 3.7V, the PWM comparator takes over the control. The duty ratio will be decided by the multiple-input direct summing comparator, Max\_Duty signal (about 90% duty-ratio), and the Current Limit Comparator, whichever is the smallest.

The soft-start is provided by the current limit comparator. As the internal  $12\mu$ A current source charges the external soft-start capacitor, the peak MOSFET current is limited by the voltage on the capacitor. This in turn controls the rising rate of output voltage.

The regulator goes through the start-up sequence as well after the EN signal is pulled to HI.

#### Steady-State Operation

When the output reaches the preset voltage, the regulator operates at steady state. Depending on the input/output condition and component, the inductor operates at either continuous-conduction mode or discontinuous-conduction mode.

In the continuous-conduction mode, the inductor current is a triangular waveform and LX voltage a pulse waveform. In the discontinuous-conduction mode, the inductor current is completely 'dried-out' before the MOSFET is turned on again. The input voltage source, the inductor, and the MOSFET and output diode parasitic capacitors forms a resonant circuit. Oscillation will occur in this period. This oscillation is normal and will not affect the regulation.

At very low load, the MOSFET will skip pulse sometimes. This is normal.

#### **Current Limit**

The MOSFET is current limited to <1.75Amps (nominal). This restricts the maximum output current  $I_{OMAX}$  based on the following formula:

$$I_{OMAX} = \left(I_{LMT} - \frac{\Delta L}{2}\right) \times \frac{V_{IN}}{V_{O}}$$

where:

•  $\Delta I_L$  is the inductor peak-to-peak current ripple and is decided by:

$$\Delta I_{L} = \frac{V_{IN}}{L} \times \frac{D}{F_{S}}$$

• D is the MOSFET turn-on radio and is decided by:

$$\mathsf{D} = \frac{\mathsf{V}_{\mathsf{O}} - \mathsf{V}_{\mathsf{IN}}}{\mathsf{V}_{\mathsf{O}}}$$

•  $F_S$  is the switching frequency.

The following table gives typical values: (Margins are considered 10%, 3%, 20%, 10%, and 15% on  $V_{IN}$ ,  $V_O$ , L,  $F_S$ , and  $I_{LMT}$ , respectively)

| V <sub>IN</sub> (V) | V <sub>O</sub> (V) | L (MH) | F <sub>S</sub> (kHz) | I <sub>OMAX</sub> (mA) |

|---------------------|--------------------|--------|----------------------|------------------------|

| 3.3                 | 9                  | 10     | 1000                 | 430                    |

| 3.3                 | 12                 | 10     | 1000                 | 320                    |

| 3.3                 | 15                 | 10     | 1000                 | 250                    |

| 5                   | 9                  | 10     | 1000                 | 650                    |

| 5                   | 12                 | 10     | 1000                 | 470                    |

| 5                   | 15                 | 10     | 1000                 | 370                    |

| 12                  | 18                 | 10     | 1000                 | 830                    |

TABLE 1. MAXIMUM CONTINUOUS OUTPUT CURRENT

## **Component Considerations**

#### Input Capacitor

It is recommended that  $C_{IN}$  is larger than  $10\mu\text{F}.$ Theoretically, the input capacitor has ripple current of  $\Delta\text{I}_L.$ Due to high-frequency noise in the circuit, the input current ripple may exceed the theoretical value. Larger capacitor will reduce the ripple further.

#### **Boost Inductor**

The inductor has peak and average current decided by:

$I_{LPK} = I_{LAVG} + \frac{\Delta I_{L}}{2}$  $I_{LAVG} = \frac{I_{O}}{1 - D}$

The inductor should be chosen to be able to handle this current. Furthermore, due to the fixed internal compensation, it is recommended that maximum inductance of  $10\mu$ H and  $15\mu$ H to be used in the 5V and 12V or higher output voltage, respectively.

The output diode has average current of  $I_O$ , and peak current the same as the inductor's peak current. Schottky diode is recommended and it should be able to handle those currents.

#### Feedback Resistor Network

An external resistor divider is required to divide the output voltage down to the nominal reference voltage. Current drawn by the resistor network should be limited to maintain the overall converter efficiency. The maximum value of the resistor network is limited by the feedback input bias current and the potential for noise being coupled into the feedback pin. A resistor network in the order of  $200k\Omega$  is recommended. The boost converter output voltage is determined by the following relationship:

$$V_{BOOST} = \frac{R_1 + R_2}{R_1} \times V_{FBB}$$

where V<sub>FBB</sub> is 1.300V.

#### Schottky Diode

Speed, forward voltage drop, and reverse current are the three most critical specifications for selecting the Schottky diode. The entire output current flows through the diode, so the diode average current is the same as the average load current and the peak current is the same as the inductor peak current. When selecting the diode, one must consider the forward voltage drop at the peak diode current. On the Elantec demo board, MBRM120 is selected. Its forward voltage drop is 450mV at 1A forward current.

#### **Output Capacitor**

The EL7584 is specially compensated to be stable with capacitors which have a worst-case minimum value of  $10\mu$ F at the particular V<sub>OUT</sub> being set. Output ripple voltage requirements also determine the minimum value and the type of capacitors. Output ripple voltage consists of two components - the voltage drop caused by the switching current though the ESR of the output capacitor and the charging and discharging of the output capacitor:

$$V_{RIPPLE} = I_{LPK} \times ESR + \frac{V_{OUT} - V_{IN}}{V_{OUT}} \times \frac{I_{OUT}}{C_{OUT} \times FS}$$

For low ESR ceramic capacitors, the output ripple is dominated by the charging/discharging of the output capacitor.

In addition to the voltage rating, the output capacitor should also be able to handle the RMS current is given by:

$$I_{\text{CORMS}} = \sqrt{(1 - D) \times \left(D + \frac{\Delta I_{L}^{2}}{I_{LAVG}^{2}} \times \frac{1}{12}\right)} \times I_{LAVG}$$

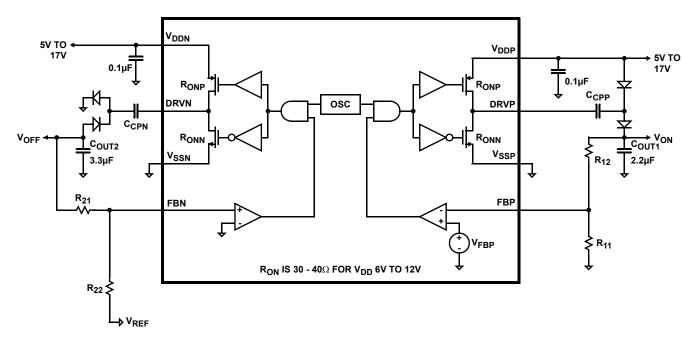

## Positive and Negative Charge Pump (V\_ON and V\_OFF)

The EL7584 contains two independent charge pumps (see charge pump block and connection diagram.) The negative charge pump inverts the V<sub>DDN</sub> supply voltage and provides a regulated negative output voltage. The positive charge pump doubles the V<sub>DDP</sub> supply voltage and provides a regulated positive output voltage. The regulation of both the negative and positive charge pumps is generated by the internal comparator that senses the output voltage and compares it with and internal reference. The switching frequency of the charge pump is set to ½ the boost converter switching frequency.

The pumps use pulse width modulation to adjust the pump period, depending on the load present. The pumps are shortcircuit protected to 180mA at 12V supply and can provide 15mA to 60mA for 6V to 12V supply.

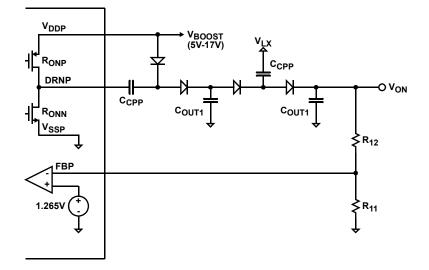

## Single Stage Charge Pump

#### Positive Charge Pump Design Considerations

A single stage charge pump is shown above. The maximum  $V_{ON}$  output voltage is determined by the following equation:

$$V_{ON}(max) \le 2 \times V_{DDCPP} - I_{OUT} \times 2 \times (R_{ONN} + R_{ONP}) - 2 \times V_{DIODE} - I_{OUT} \times \frac{1}{0.5 \times F_S \times C_{CPP}} - I_{OUT} \times \frac{1}{0.5 \times F_S \times C_{OUT1}} + \frac{1}{0.5 \times F_S \times C_{OUT1}} +$$

where:

• R<sub>ONN</sub> and R<sub>ONP</sub> resistance values depend on the V<sub>DDP</sub> voltage levels. For 12V supply, R<sub>ON</sub> is typically 33 $\Omega$ . For 6V supply, R<sub>ON</sub> is typically 45 $\Omega$ .

If additional stage is required, the LX switching signal is recommended to drive the additional charge pump diodes. The drive impedance at the LX switching is typically 150m $\Omega$ . The figure below illustrates an implementation for two-stage positive charge pump circuit.

## Two-Stage Positive Charge Pump Circuit

The maximum  $V_{\mbox{ON}}$  output voltage for N+1 stage charge pump is:

$$V_{ON}(max) \le 2 \times V_{DDP} - I_{OUT} \times 2 \times (R_{ONN} + R_{ONP}) - 2 \times V_{DIODE} - I_{OUT} \times \frac{1}{0.5 \times F_S \times C_{CPP}} - I_{OUT} \times \frac{1}{0.5 \times F_S \times C_{OUT1}} + N \times V_{LX}(max) - N \times \left(2 \times V_{DIODE} + I_{OUT} \times \frac{1}{0.5 \times F_S \times C_{CPP}} + I_{OUT} \times \frac{1}{0.5 \times F_S \times C_{OUT1}}\right)$$

$\mathsf{R}_{11}$  and  $\mathsf{R}_{12}$  set the  $\mathsf{V}_{ON}$  output voltage:

$$V_{ON} = V_{FBP} \times \frac{R_{11} + R_{12}}{R_{11}}$$

where V<sub>FBP</sub> is 1.310V.

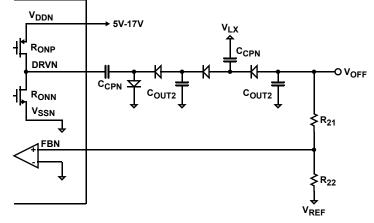

#### Negative Charge Pump Design Considerations

The criteria for the negative charge pump is similar to the positive charge pump. For a single stage charge pump, the maximum  $V_{\mbox{OFF}}$  output voltage is:

$$V_{OFF}(max) \ge I_{OUT} \times 2 \times (R_{ONN} + R_{ONP}) + 2 \times V_{DIODE} - I_{OUT} \times \frac{1}{0.5 \times F_S \times C_{CPN}} - I_{OUT} \times \frac{1}{0.5 \times F_S \times C_{OUT2}} - V_{DDN} \times \frac{1}{0.5 \times F_S \times C$$

Similar to positive charge pump, if additional stage is required, the LX switching signal is recommended to drive the additional charge pump diodes. The figure on the next page shows a two stage negative charge pump circuit.

### Two-Stage Negative Charge Pump Circuit

The maximum  $V_{OFF}$  output voltage for N+1 stage charge pump is:

$V_{OFF}(max) \ge I_{OUT} \times 2 \times (R_{ONN} + R_{ONP}) + 2 \times V_{DIODE} - I_{OUT} \times \frac{1}{0.5 \times F_S \times C_{CPN}} - I_{OUT} \times \frac{1}{0.5 \times F_S \times C_{OUT2}} - V_{DDN} - N \times V_{LX}(max) + N \times \left(2 \times V_{DIODE} + I_{OUT} \times \frac{1}{0.5 \times F_S \times C_{CPN}} + I_{OUT} \times \frac{1}{0.5 \times F_S \times C_{OUT2}}\right)$

R<sub>21</sub> and R<sub>22</sub> determine V<sub>OFF</sub> output voltage:

$$V_{OFF} = -V_{REF} \times \frac{R_{21}}{R_{22}}$$

where V<sub>REF</sub> is 1.310V.

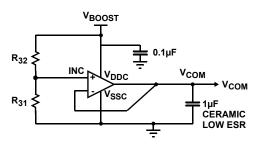

#### The V<sub>COM</sub> Buffer

The  $V_{COM}$  buffer is designed to control the voltage on the back plane of an LCD display. This plane is capacitively coupled to the pixel drive voltage which alternately cycles positive and negative at the line rate for the display. Thus the amplifier must be capable of sourcing and sinking capacitive pulses of current, which can occasionally be quite large (a few 100mA for typical applications).

The use of the V<sub>COM</sub> Buffer is illustrated in Figure 21. Here, a voltage, corresponding to the mid-DAC potential, is generated by a resistive divider and buffered by the amplifier. The amplifier's stability is designed to be dominated by the load capacitance, thus for very short duration pulses (< 1µs) the output capacitor supplies the current. For longer pulses the V<sub>COM</sub> buffer supplies the current. By virtue of its high transconductance which progressively increases as more current is drawn, it can maintain regulation within 5mV as currents up to 50mA are drawn, while consuming only 1.5mA of quiescent current.

If  $V_{BOOST}$  exceeds 15V,  $V_{DDC}$  must be protected from overvoltage by including a zener diode between  $V_{BOOST}$  and  $V_{DDC}$ .

FIGURE 21. V<sub>COM</sub> USED AS A VOLTAGE BUFFER

As with any high performance buffer, there are several design issues that must be considered when using the part. These are summarized below.

#### Good Decoupling of Power Supplies

This is essential for this component and  $1\mu$ F ceramic low ESR decoupling capacitors are recommended. These should be placed close to the pins.

#### Choice of Output Capacitor

A 1µF ceramic capacitor with low ESR (X5R or X7R type) is recommended for this amplifier. This capacitor determines the stability of the amplifier. Reducing it will make the amplifier less stable, and should be avoided. With a 1µF capacitor, the unity gain bandwidth of the amplifier is close to

500kHz when reasonable currents are being drawn. (For lower load currents, the gain and hence bandwidth progressively decreases.) This means the active transconductance is:

$2\pi\times1\mu F\times500 kHz~=~3.14S$

This high transconductance indicates why it is important to have a low ESR capacitor.

lf:

```

• ESR * 3.14 > 1

```

then the capacitor will not force the gain to roll off below unity, and subsequent poles can affect stability. The recommended capacitor has an ESR of 10mΩ, but to this must be added the resistance of the board trace between the capacitor and the V<sub>COM</sub> pin, where the sense connection is made internally - therefore this should be kept short. Also ground resistance between the capacitor and the base of R<sub>2</sub> must be kept to a minimum. These constraints should be considered when laying out the PCB.

If the capacitor is increased above 1µF, stability is generally improved and short pulses of current will cause a smaller "perturbation" on the V<sub>COM</sub> voltage. The speed of response of the amplifier is however degraded as its bandwidth is decreased. At capacitor values around 10µF, a subtle interaction with internal DC gain boost circuitry will decrease the phase margin and may give rise to some overshoot in the response. The amplifier will remain stable, though.

#### **Response to High Current Spikes**

The V<sub>COM</sub> amplifier's output current is limited to 180mA. This limit level, which is roughly the same for sourcing and sinking, is included to maintain reliable operation of the part. It does not necessarily prevent a large temperature rise if the current is maintained. (In this case the whole chip may be shut down by the thermal trip to protect functionality.) If the display occasionally demands current pulses higher than this limit, the reservoir capacitor will provide the excess and the amplifier will top the reservoir capacitor back up once the pulse has stopped. This will happen on the  $\mu$ s time scale in practical systems and for pulses 2 or 3 times the current limit, the V<sub>COM</sub> voltage will have settled again before the next line is processed.

#### **Power-Up Sequencing**

With the components shown in the application diagram the on-chip power-up sequencing operates as follows.

When the EN pin is taken to logic 1, the following sequence is followed by on-chip functions:

The boost circuit and negative charge pumps are enabled. V<sub>BOOST</sub> rises at a rate set by the boost load capacitor, the external load, and the boost's current limit (controlled by the SS pin input.) Similarly, V<sub>OFF</sub> falls in voltage determined by the load capacitor, the V<sub>OFF</sub> load, and the current capability of these negative charge pumps (which is rising as  $\mathsf{V}_{BOOST}$  and hence  $\mathsf{V}_{DDN}$  rises.)

- 2. When V<sub>BOOST</sub> reaches a voltage such that V(FBB)> 1.13V and V<sub>OFF</sub> first reaches its required regulation voltage, the V<sub>COM</sub> regulator is enabled and V<sub>COM</sub> rises at a rate determined by the V<sub>COM</sub> load capacitor, the load on V<sub>COM</sub>, and the current limit of the V<sub>COM</sub> amplifier.

- 3. When V<sub>COM</sub> rises to within 100mV of V(INC), an internal delay circuit triggers and, for V<sub>DDP</sub> = 12V, a default delay of approximately 3.5ms is introduced before the positive charge pump is then enabled. This delay can be increased externally by connecting a capacitor between DP and V<sub>SSP</sub>. A 1nF capacitor will typically increase the delay before V<sub>ON</sub> becomes enabled to 80ms.

The enabled states of the on-chip functions become independent of V<sub>BOOST</sub>, V<sub>OFF</sub>, V<sub>COM</sub>, and V<sub>ON</sub> once each is triggered. The chip may be reset by forcing EN to logic 0 and allowing sufficient time for the various supplies to discharge sufficiently before taking EN to 1 again.

#### **Over-Temperature Protection**

An internal temperature sensor continuously monitors the die temperature. In the event that die temperature exceeds the thermal trip point, the device will shut down and disable itself. The upper and lower trip points are typically set to 130°C and 90°C respectively.

#### PCB Layout Guidelines

Careful layout is critical in the successful operation of the application. The following layout guidelines are recommended to achieve optimum performance.

- 1.  $V_{\mbox{REF}}$  and  $V_{\mbox{DDB}}$  bypass capacitors should be placed next to the pins.

- 2. Place the boost converter diode and inductor close to the LX pins.

- 3. Place the boost converter output capacitor close to the PGND pins.

- 4. Locate feedback dividers close to their respected feedback pins to avoid switching noise coupling into the high impedance node.

- 5. Place the charge pump feedback resistor network after the diode and output capacitor node to avoid switching noise.

- 6. All low-side feedback resistors should be connected directly to  $V_{SSB}$ .  $V_{SSB}$  should be connected to the power ground at one point only.

A demo board is available to illustrate the proper layout implementation.

## Typical Application Circuit

\* MBRM120LT3

\*\* BAT54S

\*\*\*  $\rm C_{20}$  is optional if extended  $\rm V_{ON}$  delay is required

#### Package Outline Drawing

NOTE: The package drawing shown here may not be the latest version. To check the latest revision, please refer to the Intersil website at <http://www.intersil.com/design/packages/index.asp>

© Copyright Intersil Americas LLC 2003-2005. All Rights Reserved. All trademarks and registered trademarks are the property of their respective owners.

For additional products, see www.intersil.com/en/products.html

Intersil products are manufactured, assembled and tested utilizing ISO9001 quality systems as noted in the quality certifications found at <a href="http://www.intersil.com/en/support/qualandreliability.html">www.intersil.com/en/support/qualandreliability.html</a>

Intersil products are sold by description only. Intersil may modify the circuit design and/or specifications of products at any time without notice, provided that such modification does not, in Intersil's sole judgment, affect the form, fit or function of the product. Accordingly, the reader is cautioned to verify that datasheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com