Ver.:1.0

## **TFT LCD Specification**

## Model Name: 990001265 (EJ030NA-01B)

This technical specification is subjected to change without notice

### **Table of Contents**

| NO. | Item                       | Page  |

|-----|----------------------------|-------|

|     | Cover Sheet                | 1     |

|     | Table of Contents          | 2     |

|     | Record of Revision         | 3     |

| 1   | Features                   | 4     |

| 2   | General Specifications     | 4     |

| 3   | Input / Output Terminals   | 5,6   |

| 4   | Absolute Maximum Ratings   | 7     |

| 5   | Electrical Characteristics | 7,8   |

| 6   | Timing Chart               | 9     |

| 7   | Power sequence             | 10,11 |

| 8   | Serial interface           | 12~14 |

| 9   | Application circuit        | 15    |

| 10  | Initial code setting       | 16    |

| 11  | Register map               | 17~19 |

| 12  | Register description       | 20~28 |

| 13  | Optical Characteristics    | 29,30 |

| 14  | Reliability                | 31    |

| 15  | Handling Cautions          | 32    |

| 16  | Mechanical Drawing         | 33,34 |

| 17  | Packing Drawing            | 35,36 |

### 990001265 project

### **Record of Revision**

| Rev | Issue Date | Description                                          |  |  |  |  |  |  |

|-----|------------|------------------------------------------------------|--|--|--|--|--|--|

| 0.1 | 2011/05/16 | New created                                          |  |  |  |  |  |  |

| 0.2 | 2011/06/03 | Update Packing Drawing                               |  |  |  |  |  |  |

| 0.3 | 2011/06/09 | pdated the EE/ME/DQA design concept after DR confirm |  |  |  |  |  |  |

| 0.4 | 2011/06/29 | pdate EE power consumption and Application circuit   |  |  |  |  |  |  |

| 0.5 | 2011/08/01 | pdate EE SPI timing                                  |  |  |  |  |  |  |

| 1.0 | 2011/12/05 | Final version                                        |  |  |  |  |  |  |

|     |            |                                                      |  |  |  |  |  |  |

|     |            |                                                      |  |  |  |  |  |  |

|     |            |                                                      |  |  |  |  |  |  |

|     |            |                                                      |  |  |  |  |  |  |

|     |            |                                                      |  |  |  |  |  |  |

|     |            |                                                      |  |  |  |  |  |  |

|     |            |                                                      |  |  |  |  |  |  |

|     |            |                                                      |  |  |  |  |  |  |

|     |            |                                                      |  |  |  |  |  |  |

|     |            |                                                      |  |  |  |  |  |  |

|     |            |                                                      |  |  |  |  |  |  |

|     |            |                                                      |  |  |  |  |  |  |

|     |            |                                                      |  |  |  |  |  |  |

|     |            |                                                      |  |  |  |  |  |  |

|     |            |                                                      |  |  |  |  |  |  |

|     |            |                                                      |  |  |  |  |  |  |

|     |            |                                                      |  |  |  |  |  |  |

|     |            |                                                      |  |  |  |  |  |  |

|     |            |                                                      |  |  |  |  |  |  |

|     |            |                                                      |  |  |  |  |  |  |

|     |            |                                                      |  |  |  |  |  |  |

|     |            |                                                      |  |  |  |  |  |  |

|     |            |                                                      |  |  |  |  |  |  |

|     |            |                                                      |  |  |  |  |  |  |

|     |            |                                                      |  |  |  |  |  |  |

### 1. FEATURES

The 3.0" LCD module is the active matrix color TFT LCD module applied by a-si TFT(Amorphous silicon TFT) technology. The product is designed for the requirement of the green product, and the specification complies with CMI's "Green Product Chemical Substance Specification Standard Hand Book".

### 2. GENERAL SPECIFICATIONS

| Item                        | Description        | Unit |

|-----------------------------|--------------------|------|

| Display Size (Diagonal)     | 3.0                | Inch |

| Display Type                | Transmissive       | -    |

| Active Area (HxV)           | 60.03125 X 45      | mm   |

| Number of Dots (HxV)        | 960 x 480          | dot  |

| Dot Pitch (HxV)             | 62.5 x 93.75       | um   |

| Color Arrangement           | RGB Delta          | -    |

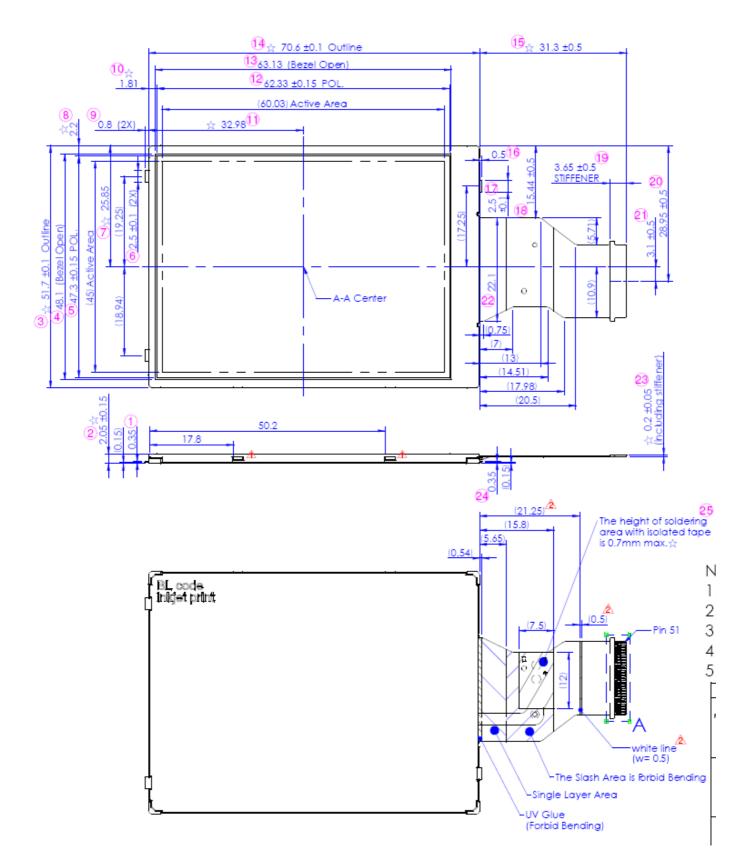

| Outline Dimension (HxVxT) * | 70.6 X 51.7 X 2.05 | mm   |

| Weight                      | 15.95              | g    |

| Panel surface treatment     | HC                 | -    |

\*Exclude FPC and protrusions.

\*With WV film

\*HC: Hard Coating (3H)

\*Gray Scale Inversion (6 o'clock): Outer Lead Bonding at right side

### **3. INPUT/OUTPUT TERMINALS**

### 3.1 TFT LCD Panel

Recommend connector:

Compatible with Molex 5025985191

| Pin | Symbol  | I/O | Description                                    | Remark |

|-----|---------|-----|------------------------------------------------|--------|

| 1   | GND     | Р   | Ground supply for internal circuit             |        |

| 2   | GRB     | Ι   | Global reset pin                               |        |

| 3   | CS      | Ι   | Serial communication chip select               |        |

| 4   | SDIN    | Ι   | Serial communication data input                |        |

| 5   | SCLK    | Ι   | Serial communication clock input               |        |

| 6   | VDDIO   | Р   | Power supply for digital interface             |        |

| 7   | VDD_18V | С   | Power setting capacitor connect pin            |        |

| 8   | DCLK    | Ι   | Clock signal, latching data at the rising edge |        |

| 9   | VS      | Ι   | Vertical sync input, negative polarity         |        |

| 10  | HS      | Ι   | Horizontal sync input, negative polarity       |        |

| 11  | DY7     | Ι   | Data input                                     |        |

| 12  | DY6     | Ι   | Data input                                     |        |

| 13  | DY5     | Ι   | Data input                                     |        |

| 14  | DY4     | Ι   | Data input                                     |        |

| 15  | DY3     | Ι   | Data input                                     |        |

| 16  | DY2     | Ι   | Data input                                     |        |

| 17  | DY1     | Ι   | Data input                                     |        |

| 18  | DY0     | Ι   | Data input                                     |        |

| 19  | DC7     | Ι   | Data input                                     |        |

| 20  | DC6     | Ι   | Data input                                     |        |

| 21  | DC5     | Ι   | Data input                                     |        |

| 22  | DC4     | Ι   | Data input                                     |        |

| 23  | DC3     | Ι   | Data input                                     |        |

| 24  | DC2     | Ι   | Data input                                     |        |

| 25  | DC1     | Ι   | Data input                                     |        |

| 26  | DC0     | Ι   | Data input                                     |        |

| 27  | VCOMH   | С   | Power setting capacitor for VCOMH              |        |

| 28  | VCOMH   | С   | Power setting capacitor for VCOMH              |        |

| 29  | VCOML   | С   | Power setting capacitor for VCOML              |        |

| 30  | VCOML   | С   | Power setting capacitor for VCOML              |        |

| 31  | VDD     | Р   | Power supply for internal circuit              |        |

## 990001265 project

| 32 | VDD   | Р | Power supply for internal circuit     |        |  |  |

|----|-------|---|---------------------------------------|--------|--|--|

| 33 | GND   | Р | Ground supply for internal circuit    |        |  |  |

| 34 | VINT2 | С | Power setting capacitor connect pin   |        |  |  |

| 35 | V9    | С | Power setting capacitor connect pin   |        |  |  |

| 36 | V10   | С | Power setting capacitor connect pin   |        |  |  |

| 37 | VINT1 | С | Power setting capacitor connect pin   |        |  |  |

| 38 | VINT1 | С | Power setting capacitor connect pin   |        |  |  |

| 39 | AGND  | Р | Ground supply for charge pump circuit |        |  |  |

| 40 | V1    | С | Power setting capacitor connect pin   |        |  |  |

| 41 | V2    | С | Power setting capacitor connect pin   |        |  |  |

| 42 | V3    | С | Power setting capacitor connect pin   |        |  |  |

| 43 | V4    | С | Power setting capacitor connect pin   |        |  |  |

| 44 | V5    | С | Power setting capacitor connect pin   |        |  |  |

| 45 | V6    | С | Power setting capacitor connect pin   |        |  |  |

| 46 | VGH   | С | Power setting capacitor connect pin   |        |  |  |

| 47 | V7    | С | Power setting capacitor connect pin   |        |  |  |

| 48 | V8    | С | Power setting capacitor connect pin   |        |  |  |

| 49 | VGL   | С | Power setting capacitor connect pin   |        |  |  |

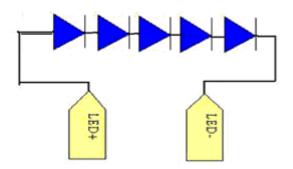

| 50 | LED+  | Р | LED power anode                       | Note 2 |  |  |

| 51 | LED-  | Р | LED power cathode                     | Note 2 |  |  |

**Note 1:** I : Input, O : Output, C : Capacitor Pin, P : Power(in)

Note 2: The figure below shows the connection of backlight LED.

### 4. ABSOLUTE MAXIMUM RATINGS

| Item                  | Symbol           | Min. | Max.    | Unit |

|-----------------------|------------------|------|---------|------|

| Power supply (pump)   | VDD              | -0.3 | +4.0    | V    |

| Power supply for IO   | VDDIO            | -0.3 | VDD+0.3 | V    |

| Storage temperature   | T <sub>STG</sub> | -30  | 80      | °C   |

| Operating temperature | T <sub>OPR</sub> | 0    | 60      | °C   |

### 5. ELECTRICAL CHARACTERISTICS

Driving TFT LCD Panel

GND=0V, Ta=25℃

| Item                                      |            | Symbol          | MIN           | TYP  | MAX           | Unit | Remark                                      |  |

|-------------------------------------------|------------|-----------------|---------------|------|---------------|------|---------------------------------------------|--|

| Power Supply Voltage                      |            | VDD             | 3.00          | 3.30 | 3.60          | V    |                                             |  |

| Power Supply for IO                       |            | VDDIO           | 1.65          | 1.8  | VDD           | V    |                                             |  |

| Input Signal                              | Low Level  | V <sub>IL</sub> | GND           | -    | 0.3x<br>VDDIO | V    | VSYNC, HSYNC,<br>DCLK, DG[0:7],             |  |

| Voltage                                   | High Level | V <sub>IH</sub> | 0.7x<br>VDDIO | -    | VDDIO         | V    | DB[0:7], SDIN,<br>SCLK, CS, GRB,<br>Note5-1 |  |

| Panel Power Consumption                   |            | W <sub>P</sub>  | -             | 60   | -             | mW   |                                             |  |

| Panel Power Consumption<br>(Standby mode) |            | I <sub>ST</sub> |               |      | 35            | uA   | DCLK stop,<br>Data keep low                 |  |

Note5-1: Overshoot swing: Low level: -0.3V ~ High level: VDDIO+0.3V

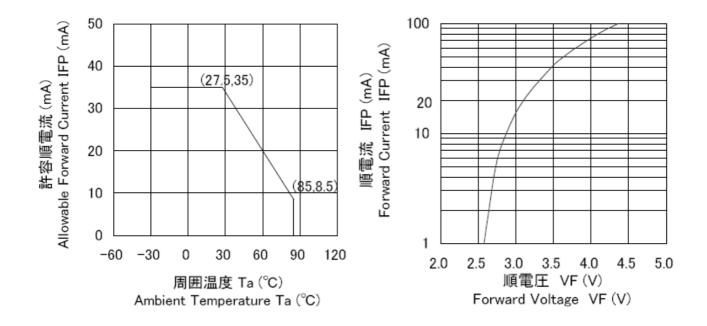

### **Driving Backlight**

Ta=25℃

| Item                        | Symbol         | MIN | TYP | MAX   | Unit | Remark   |

|-----------------------------|----------------|-----|-----|-------|------|----------|

| Forward Current             | I <sub>F</sub> |     | 25  | 27    | mA   | Note 5-2 |

| Forward Current Voltage     | $V_{F}$        |     | 16  | 17.5  | V    |          |

| Backlight Power Consumption | $W_{BL}$       |     | 400 | 472.5 | mW   |          |

Note 5-2: Backlight driving circuit is recommended as the fix current circuit.

\* Ta: Ambient Temperature

\* High temperature operation: Test current refers the diagram as following

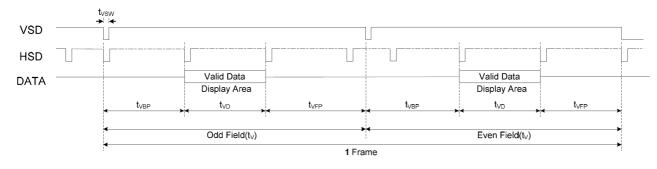

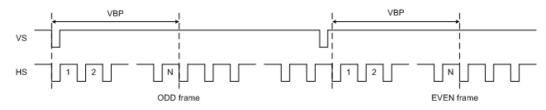

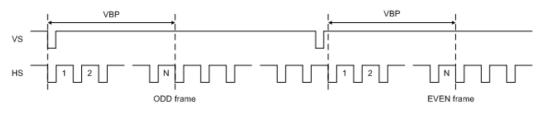

### 6. TIMING CHART

### 6.1 YUV720 16-bit Parallel input timing

#### Total Area (t<sub>H</sub>)

#### NTSC

|                | Parameter      |             | Symbol            | Min.  | Тур.  | Max.                | Unit | Remark |

|----------------|----------------|-------------|-------------------|-------|-------|---------------------|------|--------|

| DCLK frequency |                |             | f <sub>DCLK</sub> | 18.6  | 27    | 29.7                | MHz  |        |

| Hsync          | Period         |             | t <sub>H</sub>    | 764   | 858   | 1920                | DCLK |        |

|                | Display period | l           | t <sub>HD</sub>   |       | 720   |                     | DCLK |        |

|                | Back porch     |             | t <sub>HBP</sub>  | 10    | 40    | 255                 | DCLK |        |

|                | Front porch    | Front porch |                   | -     | 98    | -                   | DCLK |        |

|                | Pulse Width    |             | t <sub>HPW</sub>  | 1     | 20    | t <sub>HBP</sub> -1 | DCLK |        |

| Vsync          | Period         | Period      |                   | 485.5 | 524.5 | 575.5               | HS   |        |

|                | Display period | l           | t <sub>VD</sub>   |       | 480   |                     | HS   |        |

|                | Back porch     | Odd field   | t                 | 3     | 27    | 31                  | HS   |        |

|                | Back porch     | Even field  | t <sub>VBP</sub>  | 3.5   | 27.5  | 31.5                | 115  |        |

|                | Front porch    | Odd field   | t                 | -     | 17.5  | -                   | HS   |        |

|                | From porch     | Even field  | t <sub>VFP</sub>  | -     | 17    | -                   | нз   |        |

|                | Pulse Width    | Pulse Width |                   | -     | 1     | -                   | DCLK |        |

|                | 1 Frame        |             | -                 | -     | 1049  | -                   | HS   |        |

PAL

| Parameter      |                | Symbol           | Min.              | Тур.  | Max.                | Unit  | Remark |  |

|----------------|----------------|------------------|-------------------|-------|---------------------|-------|--------|--|

| DCLK frequency |                |                  | f <sub>DCLK</sub> | 17.8  | 26.8                | 29.5  | MHz    |  |

| Hsync          | Period         |                  | t <sub>H</sub>    | 764   | 858                 | 1920  | DCLK   |  |

|                | Display period |                  | t <sub>HD</sub>   |       | 720                 | •     | DCLK   |  |

|                | Back porch     |                  | t <sub>HBP</sub>  | 10    | 40                  | 255   | DCLK   |  |

|                | Front porch    | Front porch      |                   | -     | 98                  | -     | DCLK   |  |

| Pulse Width    |                | t <sub>HPW</sub> | 1                 | 20    | t <sub>HBP</sub> -1 | DCLK  |        |  |

| Vsync          | Period         | Period           |                   | 581.5 | 624.5               | 680.5 | HS     |  |

|                | Display period | Display period   |                   |       | 576                 |       | HS     |  |

|                | Deals march    | Odd field        |                   | 3     | 30                  | 34    | HS     |  |

|                | Back porch     | Even field       | t <sub>VBP</sub>  | 3.5   | 30.5                | 34.5  | пъ     |  |

|                | Front porch    | Odd field        |                   | -     | 18.5                | -     | HS     |  |

|                | Fiont porch    | Even field       | t <sub>VFP</sub>  | -     | 18                  | -     | пъ     |  |

|                | Pulse Width    |                  | t <sub>vsw</sub>  | -     | 1                   | -     | DCLK   |  |

|                | 1 Frame        |                  | -                 | -     | 1249                | -     | HS     |  |

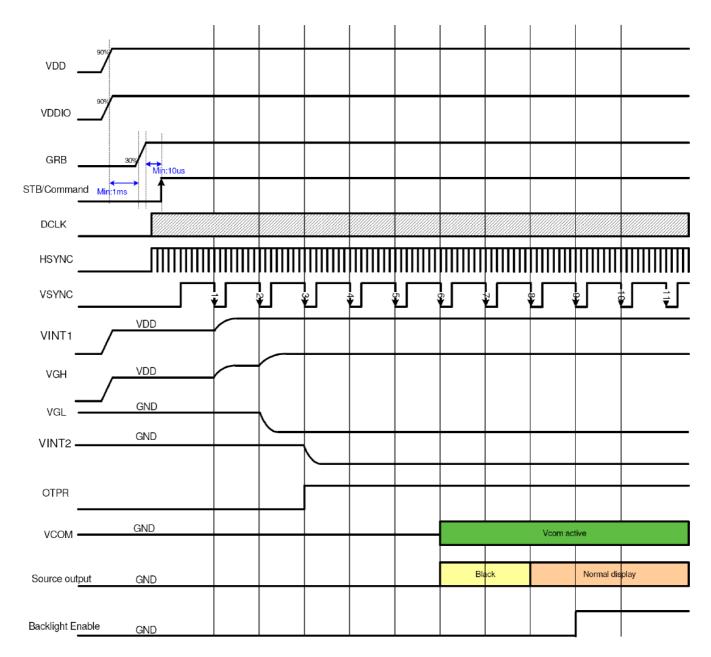

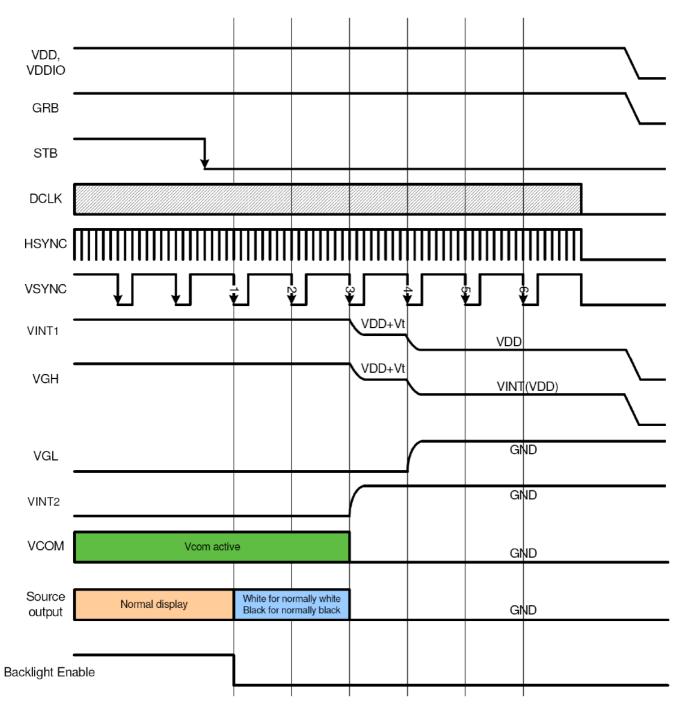

### 7. POWER SEQUENCE

7.1 Power On Sequence

7.2 Power off Sequence

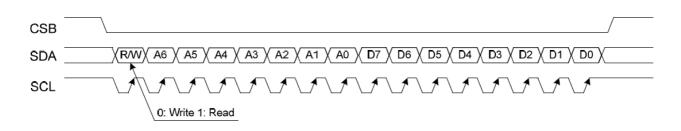

### **8. SERIAL INTERFACE**

### 8.1 SPI command format

### Note:

- Each serial command consists of 16 bits of data that is loaded one bit a time at the rising edge of serial clock SCL. Command loading operation starts from the falling edge of CSB and is completed at the next rising edge of CSB.

- The serial control block is operational after power on reset, but commands are established by the VS signal.

If command is transferred multiple times for the same register, the last command before the VS signal is valid.

- > If less than 16 bits of SCL are input while CSB is low, the transferred data is ignored.

- > If longer than 16 bits of SCL are input while CSB is low, the transferred data is ignored.

- > Serial commands can be accepted in the stand-by mode.

### 8.2 SPI timing

#### (VDD=3.0~3.6V, VDD=VDDIO, GND=AGND= 0V, $T_{OPR}$ = -10°C to 60°C)

| Parameter                      | Symbol            | Min. | Тур. | Max. | Unit | Remark |

|--------------------------------|-------------------|------|------|------|------|--------|

| Write timing                   |                   |      |      |      |      |        |

| CSB falling to SCL rising time | T <sub>SCL</sub>  | 200  | -    | -    | ns   |        |

| SCL pulse high period          | T <sub>ICWH</sub> | 100  | -    | -    | ns   |        |

| SCL pulse low period           | T <sub>ICWL</sub> | 100  | -    | -    | ns   |        |

| SDA data input setup time      | T <sub>ISU</sub>  | 100  | -    | -    | ns   |        |

| SDA data input hold time       | T <sub>IHD</sub>  | 100  | -    | -    | ns   |        |

| SCL rising to CSB rising time  | T <sub>ISC</sub>  | 100  | -    | -    | ns   |        |

| CSB rising to falling time     | T <sub>ICD</sub>  | 400  | -    | -    | ns   |        |

## 990001265 project

| Parameter                            | Symbol            | Min. | Тур. | Max. | Unit | Remark             |

|--------------------------------------|-------------------|------|------|------|------|--------------------|

| Read timing                          |                   |      |      |      |      |                    |

| CSB falling to SCL rising time       | T <sub>SCL</sub>  | 200  | -    | -    | ns   |                    |

| SCL pulse high period                | T <sub>ICWH</sub> | 500  | -    | -    | ns   |                    |

| SCL pulse low period                 | T <sub>ICWL</sub> | 500  | -    | -    | ns   |                    |

| SDA data input setup time            | T <sub>ISU</sub>  | 100  | -    | -    | ns   |                    |

| SDA data input hold time             | T <sub>IHD</sub>  | 100  | -    | -    | ns   |                    |

| SCL rising to CSB rising time        | T <sub>ISC</sub>  | 100  | -    | -    | ns   |                    |

| SCL falling to SDA output delay time | T <sub>CDD</sub>  | -    | -    | 100  | ns   | SDA at output mode |

| CSB rising to falling time           | T <sub>ICD</sub>  | 400  | -    | -    | ns   |                    |

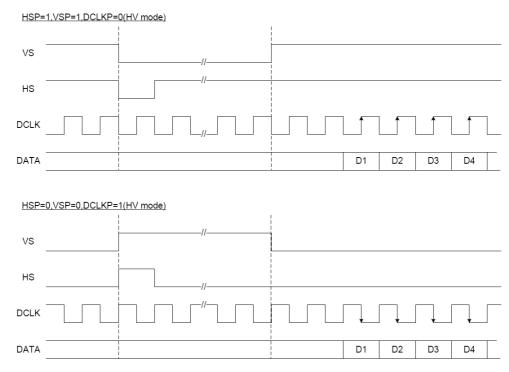

### 8.3 Input timing

(VDD=3.0~3.6V, VDD=VDDIO, GND=AGND= 0V,  $T_{OPR}$  = -10 $^\circ\!{\rm C}$  to 60 $^\circ\!{\rm C}$  )

| Parameter              | Symbol                      | Min. | Тур. | Max. | Unit | Remark                               |

|------------------------|-----------------------------|------|------|------|------|--------------------------------------|

| VDD slew rate          | T <sub>POR</sub>            | 0.1  | -    | 30   | ms   | From 0V to 90%VDD                    |

| GRB active pulse width | T <sub>GRB</sub>            | 1    | -    | -    | ms   | VDDIO=3.3V                           |

| VDD resettle time      | T <sub>RES</sub>            | 1    | -    | -    | S    |                                      |

| DCLK clock pulse width | T <sub>DCLK</sub>           | -    | 37   | -    | ns   | 16-bit 720 YUV mode                  |

| DCLK clock pulse high  | T <sub>CWH</sub>            | 7    | -    | -    | ns   |                                      |

| DCLK clock pulse low   | T <sub>CWL</sub>            | 7    | -    | -    | ns   |                                      |

| VS setup time          | $\mathrm{T}_{\mathrm{VSU}}$ | 6    | -    | -    | ns   |                                      |

| VS hold time           | $\mathrm{T}_{\mathrm{VHU}}$ | 6    | -    | -    | ns   |                                      |

| HS setup time          | $\mathrm{T}_{\mathrm{HSU}}$ | 6    | -    | -    | ns   |                                      |

| HS hold time           | T <sub>HHD</sub>            | 6    | -    | -    | ns   |                                      |

| Data setup time        | T <sub>DSU</sub>            | 6    | -    | -    | ns   | DR0~DR7, DG0~DG7,<br>DB0~DB7 to DCLK |

| Data hold time         | T <sub>DHD</sub>            | 6    | -    | -    | ns   | DR0~DR7, DG0~DG7,<br>DB0~DB7 to DCLK |

**Timing Waveform**

### 9. Application circuit

| Pin Name | Capacitor              | Pin Name | Capacitor               |

|----------|------------------------|----------|-------------------------|

| V1       |                        | VDD_18V  | 1uF / 6.3V / 10% / X5R  |

| V2       | 1uF / 6.3V / 10% / X5R | VCOMH    | 2.2uF / 10V / 10% / X5R |

| V3       |                        | VCOML    | 2.2uF / 10V / 10% / X5R |

| V4       | 1uF / 6.3V / 10% / X5R | VDD      | 1uF / 6.3V / 10% / X5R  |

| V5       | 1uF / 16V / 10% / X5R  | VINT2    | 1uF / 6.3V / 10% / X5R  |

| V6       |                        | VINT1    | 2.2uF / 10V / 10% / X5R |

| V7       | 4E / 401/ / 40%/ / XED | VGH      | 1uF / 25V / 10% / X5R   |

| V8       | 1uF / 16V / 10% / X5R  | VGL      | 1uF / 16V / 10% / X5R   |

| V9       | 4E / 40V / 40% / XED   | VDDIO    | 1uF / 6.3V / 10% / X5R  |

| V10      | 1uF / 10V / 10% / X5R  |          |                         |

### **10. Initial code setting**

| Name                | Address | Setting | Note                         |

|---------------------|---------|---------|------------------------------|

| RSTB                | 0x05    | 0x1E    | In refresh mode, don't set . |

| PFM_EN              | 0x05    | 0x5C    |                              |

| NARROW/Contrast_SEL | 0x02    | 0x14    | Default                      |

| Brightness          | 0x03    | 0x40    | Default                      |

| IF_SEL              | 0x04    | 0x6B    | Default                      |

| HBLK_EN/VBP         | 0x06    | 0x1B    | Default                      |

| HBP                 | 0x07    | 0x28    | Default                      |

| CbCr/VSP/HSP/DCLKP  | 0x0C    | 0x06    | Default                      |

| Contrast_8bit       | 0x0D    | 0x40    | Default                      |

| SUB Contrast_R      | 0x0E    | 0x40    | Default                      |

| SUB Brightness_R    | 0x0F    | 0x40    | Default                      |

| SUB Contrast_B      | 0x10    | 0x40    | Default                      |

| SUB Brightness_B    | 0x11    | 0x40    | Default                      |

| VGL                 | 0x2F    | 0x40    | Default                      |

| VGH                 | 0x5A    | 0x02    | Default                      |

|                     | 0x30    | 0x07    |                              |

|                     | 0x31    | 0x57    |                              |

|                     | 0x32    | 0x53    |                              |

|                     | 0x33    | 0x77    |                              |

| Positive Gamma      | 0x34    | 0XB8    |                              |

|                     | 0x35    | 0xBD    |                              |

|                     | 0x36    | 0XB8    |                              |

|                     | 0x37    | 0XE7    |                              |

|                     | 0x38    | 0x04    |                              |

|                     | 0x39    | 0xFF    |                              |

|                     | 0x40    | 0x0B    |                              |

|                     | 0x41    | 0xB8    |                              |

|                     | 0x42    | 0xAB    |                              |

|                     | 0x43    | 0XB9    |                              |

| Negative Gamma      | 0x44    | 0x6A    |                              |

| negative Gaillina   | 0x45    | 0x56    |                              |

|                     | 0x46    | 0x61    |                              |

|                     | 0x47    | 0x08    |                              |

|                     | 0x48    | 0x0F    |                              |

|                     | 0x49    | 0x0F    |                              |

| STB                 | 0x2B    | 0x01    |                              |

### 11. Register map

|        | D7              | D6   | D5 | D4             | D3        | D2      | D1     | D0      | HEX |  |  |  |  |  |

|--------|-----------------|------|----|----------------|-----------|---------|--------|---------|-----|--|--|--|--|--|

| R02h   | Narrow          | х    | х  | Contrast<br>SW |           | Contra  | ast_A  |         | 14  |  |  |  |  |  |

|        | 0               | 0    | 0  | 1              | 0         | 1       | 0      | 0       |     |  |  |  |  |  |

| R03h   | Brightness      |      |    |                |           |         |        |         |     |  |  |  |  |  |

|        | 0               | 1    | 0  | 0              | 0         | 0       | 0      | 0       | 40  |  |  |  |  |  |

| R04h   |                 | IF_S | EL |                | NTS       | C/PAL   | UD     | SHL     | 6B  |  |  |  |  |  |

|        | 0               | 1    | 1  | 0              | 1         | 0       | 1      | 1       | 00  |  |  |  |  |  |

| R05h   | x               | RSTB | х  | x              | х         | VGHL_EN | PFM_EN | х       | 5C  |  |  |  |  |  |

|        | 0               | 1    | 0  | 1              | 1         | 1       | 0      | 0       | 50  |  |  |  |  |  |

| R06h   | HBLK_EN         | х    | х  |                |           | VBLK    |        |         | 1B  |  |  |  |  |  |

| Room   | 0               | 0    | 0  | 1              | 1         | 0       | 1      | 1       |     |  |  |  |  |  |

| R07h   |                 |      |    | HE             | BLK       |         |        |         | 28  |  |  |  |  |  |

| 1.0711 | 0               | 0    | 1  | 0              | 1         | 0       | 0      | 0       | 20  |  |  |  |  |  |

| R0Ch   | VS              | Т    | х  | CbCr           | х         | VDpol   | HDpol  | DCLKpol | 6   |  |  |  |  |  |

| Ruch   | 0               | 0    | 0  | 0              | 0         | 1       | 1      | 0       | 0   |  |  |  |  |  |

| R0Dh   | Contrast_B      |      |    |                |           |         |        |         |     |  |  |  |  |  |

| Robh   | 0               | 1    | 0  | 0              | 0         | 0       | 0      | 0       | 40  |  |  |  |  |  |

| R0Eh   | SUB_ Contrast_R |      |    |                |           |         |        |         |     |  |  |  |  |  |

| NULII  | 0               | 1    | 0  | 0              | 0         | 0       | 0      | 0       | 40  |  |  |  |  |  |

| R0Fh   |                 |      |    | SUB_ Bri       | ghtness_  | R       |        |         | 40  |  |  |  |  |  |

| RUFII  | 0               | 1    | 0  | 0              | 0         | 0       | 0      | 0       | 40  |  |  |  |  |  |

| R10h   |                 |      |    | SUB_C          | ontrast_B | }       |        |         | 40  |  |  |  |  |  |

| RIUII  | 0               | 1    | 0  | 0              | 0         | 0       | 0      | 0       | 40  |  |  |  |  |  |

| R11h   |                 |      |    | SUB_ Brig      | ghtness_  | В       |        |         | 40  |  |  |  |  |  |

|        | 0               | 1    | 0  | 0              | 0         | 0       | 0      | 0       | 40  |  |  |  |  |  |

| R13h   | REGSEL          | х    | х  | x              | х         | х       | х      | х       | 0   |  |  |  |  |  |

| RIJI   | 0               | 0    | 0  | 0              | 0         | 0       | 0      | 0       | 0   |  |  |  |  |  |

| R1Bh   |                 |      |    | VCC            | ОМН       |         |        |         | B3  |  |  |  |  |  |

|        | 1               | 0    | 1  | 1              | 0         | 0       | 1      | 1       | 60  |  |  |  |  |  |

| D10h   |                 |      |    | VC             | OML       |         |        |         | 76  |  |  |  |  |  |

| R1Ch   | 0               | 1    | 1  | 1              | 0         | 1       | 1      | 0       | 76  |  |  |  |  |  |

| DODH   | х               | х    | Х  | x              | х         | х       | х      | STB     | 1   |  |  |  |  |  |

| R2Bh   | 0               | 0    | 0  | 0              | 0         | 0       | 0      | 1       | I   |  |  |  |  |  |

990001265 project

| R2Fh    | VGL_SEL x x x |     |   |   |   |   | х       | x x   |    |  |

|---------|---------------|-----|---|---|---|---|---------|-------|----|--|

| 1\21 11 | 0             | 1   | 0 | 0 | 0 | 0 | 0       | 0     | 40 |  |

| R5Ah    | х             | х   | х | х | Х | ١ | /GH_SEL |       | 2  |  |

| RJAH    | 0             | 0   | 0 | 0 | 0 | 0 | 1       | 0     | 2  |  |

|         | v             | v v | х | v | X | v | Gate    | Input |    |  |

| R5Ch    | X             | Х   | * | X | X | X | Sequ    | ence  | 2  |  |

|         | 0             | 0   | 0 | 0 | 0 | 0 | 1       | 0     |    |  |

| R30h   |           | VSF         | 2  |   |      | VS  | P1  |   | 7  |  |

|--------|-----------|-------------|----|---|------|-----|-----|---|----|--|

| RJUII  | 0         | 0           | 0  | 0 | 0    | 1   | 1   | 1 | '  |  |

| R31h   |           | VP          | 7  |   |      | VF  | 20  |   | 57 |  |

| K3 III | 0         | 1           | 0  | 1 | 0    | 1   | 1   | 1 | 57 |  |

| R32h   |           | ٧P          | 19 |   |      | VP  | 13  |   | 53 |  |

| 13211  | 0 1       | 1           | 0  | 1 | 0    | 0   | 1   | 1 | 55 |  |

| R33h   | VP40 VP27 |             |    |   |      |     |     |   | 77 |  |

| 13311  | 0         | 1           | 1  | 1 | 0    | 1   | 1   | 1 |    |  |

| R34h   | VP85 VP59 |             |    |   |      | B8  |     |   |    |  |

| 172411 | 1         | 0           | 1  | 1 | 1    | 0   | 0   | 0 | 00 |  |

| R35h   |           | VP1         | 59 |   |      | BD  |     |   |    |  |

| 13311  | 1         | 0           | 1  | 1 | 1    | 1   | 0   | 1 | Ъυ |  |

| R36h   |           | VP2         | 30 |   |      |     | B8  |   |    |  |

| 13011  | 1         | 0           | 1  | 1 | 1    | 0   | 0   | 0 | DO |  |

| R37h   |           | VP2         | 52 |   |      | VP2 | 249 |   | E7 |  |

| 13711  | 1         | 1           | 1  | 0 | 0    | 1   | 1   | 1 |    |  |

| R38h   | х         | x x x VP255 |    |   | 4    |     |     |   |    |  |

| 13011  | 0         | 0           | 0  | 0 | 0    | 1   | 0   | 0 | 4  |  |

| R39h   |           | VSF         | P4 |   | VSP3 |     |     |   | FF |  |

| 172911 | 1         | 1           | 1  | 1 | 1    | 1   | 1   | 1 |    |  |

### 990001265 project

| R40h    |           | VSI | N2  |   |      | VS  | N1  |    | В  |  |  |  |

|---------|-----------|-----|-----|---|------|-----|-----|----|----|--|--|--|

| 114011  | 0         | 0   | 0   | 0 | 1    | 0   | 1   | 1  | Б  |  |  |  |

| R41h    |           | VN  | 17  |   |      | NV  | 10  | 10 |    |  |  |  |

| 1\4 111 | 1         | 0   | 1   | 1 | 1    | 0   | 0   | 0  | B8 |  |  |  |

| R42h    |           | VN  | 19  |   |      | VN  | 13  |    | AB |  |  |  |

| 1\4211  | 1         | 0   | 1   | 0 | 1    | 0   | 1   | 1  | AD |  |  |  |

| R43h    |           | VN  | 40  |   |      | VN  | 27  |    | В9 |  |  |  |

| 114511  | 1         | 0   | 1   | 1 | 1    | 0   | 0   | 1  | Da |  |  |  |

| R44h    | VN85 VN59 |     |     |   |      |     | 6A  |    |    |  |  |  |

| 114411  | 0         | 1   | 1   | 0 | 1    | 0   | 1   | 0  |    |  |  |  |

| R45h    |           | VN1 | 59  |   |      | 56  |     |    |    |  |  |  |

| 114511  | 0         | 1   | 0   | 1 | 0    | 1   | 1   | 0  | 00 |  |  |  |

| R46h    |           | VN2 | 230 |   |      | 61  |     |    |    |  |  |  |

| 114011  | 0         | 1   | 1   | 0 | 0    | 0   | 0   | 1  | 01 |  |  |  |

| R47h    |           | VN2 | 252 |   |      | VN2 | 249 |    | 8  |  |  |  |

| 124711  | 0         | 0   | 0   | 0 | 1    | 0   | 0   | 0  | 0  |  |  |  |

| R48h    | х         | х   | х   | х |      | VN2 | 255 |    | F  |  |  |  |

| 114011  | 0         | 0   | 0   | 0 | 1    | 1   | 1   | 1  |    |  |  |  |

| R49h    |           | VSI | N4  |   | VSN3 |     |     |    | F  |  |  |  |

| 114311  | 0         | 0   | 0   | 0 | 1    | 1   | 1   | 1  | I  |  |  |  |

### 12. Register description

Register setting - R2

| I | Reg | Address |    |    |    |    |    |    |    |           | Data |    |                   |    |        |          |    |

|---|-----|---------|----|----|----|----|----|----|----|-----------|------|----|-------------------|----|--------|----------|----|

| I | NO  | R/W     | A6 | A5 | A4 | A3 | A2 | A1 | A0 | D7        | D6   | D5 | D4                | D3 | D2     | D1       | D0 |

| Ī | R2  | 1/0     | 0  | 0  | 0  | 0  | 0  | 1  | 0  | Narrow(0) | 0    | 0  | Contrast<br>SW(1) |    | Contra | st_A(4h) | )  |

#### R2[3:0] - CONTRAST\_A: RGB contrast setting

| CON-<br>TRAST_A | Contrast gain(0.25/bit) |

|-----------------|-------------------------|

| 0000            | 0                       |

| 0100            | 1 (Default)             |

| 1111            | 3.75                    |

#### R2[4] - CONTRAST\_SW: 4-bit or 8-bit contrast selection

| CON-<br>TRAST_SW | Description                        |

|------------------|------------------------------------|

| 0                | 4bit contrast (R02[3:0])           |

| 1                | 8bit contrast (R0D[7:0]) (Default) |

#### R2[7] – Normal/Narrow display selection

| CON-<br>TRAST_SW | Function                 |

|------------------|--------------------------|

| 0                | Normal display (Default) |

| 1                | Narrow Display           |

D7=1:Narrow display

| D7=0:Normal display                                                        |

|----------------------------------------------------------------------------|

| The display at both side of the panel is black display at NW and NB panel. |

| It doesn't support 16-bit/24-bit RGB mode.                                 |

#### Register setting - R3

| Reg | Address |    |    |    |    |    |    |    |                 | Data |    |    |    |    |    |    |  |  |

|-----|---------|----|----|----|----|----|----|----|-----------------|------|----|----|----|----|----|----|--|--|

| NO  | R/W     | A6 | A5 | A4 | A3 | A2 | A1 | A0 | D7              | D6   | D5 | D4 | D3 | D2 | D1 | D0 |  |  |

| R3  | 1/0     | 0  | 0  | 0  | 0  | 0  | 1  | 1  | Brightness(40h) |      |    |    |    |    |    |    |  |  |

#### R3[7:0] – BRIGHTNESS: RGB brightness level setting

| BRIGHT-<br>NESS | Brightness gain(1 step/bit) |

|-----------------|-----------------------------|

| 00h             | Dark(-64)                   |

| 40h             | Center(0) (Default)         |

| FFh             | Bright(+191)                |

#### Register setting – R4

| Reg |     |    |    | Add | ress |    |    | Data |              |    |    |    |                    |    |    |        |

|-----|-----|----|----|-----|------|----|----|------|--------------|----|----|----|--------------------|----|----|--------|

| NO  | R/W | A6 | A5 | A4  | A3   | A2 | A1 | A0   | D7           | D6 | D5 | D4 | D3                 | D2 | D1 | D0     |

| R4  | 1/0 | 0  | 0  | 0   | 0    | 1  | 0  | 0    | IF_SEL(0110) |    |    |    | NTSC/PAL(10) UD(1) |    |    | SHL(1) |

#### R4[0] -SHL: Horizontal shift direction setting

| HDIR | Function                                                                        |

|------|---------------------------------------------------------------------------------|

| 0    | Shift from right to left, Last data = Y1←Y2…Y959←Y960 = First<br>data           |

| 1 1  | Shift from left to right, First data = Y1→Y2…Y959→Y960 = Last<br>data (Default) |

#### R4[1] – UD: Vertical shift direction setting

| VDIR | Function                                                                     |

|------|------------------------------------------------------------------------------|

| 0    | Shift from down to up, Last line = L1←L2…L479←L480 = First<br>line           |

| 1 1  | Shift from up to down, First line = L1→L2…L479→L480 = Last<br>line (Default) |

#### R4[3:2] – NTSC/PAL: NTSC or PAL input mode selection

| NTSC | C/PAL | MODE                     |  |  |  |  |  |  |  |  |

|------|-------|--------------------------|--|--|--|--|--|--|--|--|

| D3   | D2    | MODE                     |  |  |  |  |  |  |  |  |

| 0    | 0     | PAL                      |  |  |  |  |  |  |  |  |

| 0    | 1     | NTSC                     |  |  |  |  |  |  |  |  |

| 1    | Х     | Auto detection (Default) |  |  |  |  |  |  |  |  |

#### R4[7:4] - IF\_SEL: Input data format selection

|    | IF_S | SEL |    | INPUT TIMING FORMAT         |

|----|------|-----|----|-----------------------------|

| D7 | D6   | D5  | D4 | INPUT TIMING FORMAT         |

| 0  | 0    | 0   | 0  | 8-bit RGB through mode      |

| 0  | 0    | 0   | 1  | 24-bit RGB DA mode          |

| 0  | 0    | 1   | 0  | 8-bit RGB DA mode           |

| 0  | 0    | 1   | 1  | 24-bit RGB through mode     |

| 0  | 1    | 0   | 0  | 16-bit YUV640 mode          |

| 0  | 1    | 1   | 0  | 16-bit YUV720 mode(Default) |

| 1  | 0    | 0   | 0  | 8-bit RGBD 320 mode         |

| 1  | 0    | 1   | 0  | 8-bit RGBD 360 mode         |

| 1  | 1    | 0   | 0  | 8-bit YUV640 mode           |

| 1  | 1    | 0   | 1  | 8-bit YUV720 mode           |

| 1  | 1    | 1   | 0  | 16-bit RGB through mode     |

| 1  | 1    | 1   | 1  | 16-bit RGB DA mode          |

#### Register setting - R5

| Reg | Address |    |    |    |    |    |    |    |    | Data    |    |    |    |                |               |    |  |

|-----|---------|----|----|----|----|----|----|----|----|---------|----|----|----|----------------|---------------|----|--|

| NO  | R/W     | A6 | A5 | A4 | A3 | A2 | A1 | A0 | D7 | D6      | D5 | D4 | D3 | D2             | D1            | D0 |  |

| R5  | 1/0     | 0  | 0  | 0  | 0  | 1  | 0  | 1  | 0  | RSTB(1) | 0  | 1  | 1  | VGHL_EN<br>(1) | PFM_EN<br>(1) | 0  |  |

#### R5[1] - PFM\_EN: Shut down for back light power converter

| PFM_EN | Function                                                                                 |

|--------|------------------------------------------------------------------------------------------|

| 0      | The back light power converter is off                                                    |

| 1      | The back light power converter is controlled by STB's power<br>on/off sequence (Default) |

#### R5[2] - VGHL\_EN: Shut down for VGH/VGL charge pump

| VGHL_EN | Function                                                |

|---------|---------------------------------------------------------|

| 0       | VGH/VGL charge pump is always off                       |

| 1       | VGH/VGL charge pump is controlled by STB's power on/off |

| I       | sequence (Default)                                      |

#### R5[6] - RSTB: Register reset setting

| RSTB | Function                                                    |

|------|-------------------------------------------------------------|

|      | Global reset activation register. After global reset opera- |

| 0    | tion is down,                                               |

|      | this register will be set to "1" automatically.             |

| 1    | Normal operation (Default)                                  |

#### Register setting - R6

| Reg |     | -  |    | Add | ress |    |    |    | Data       |    |    |          |    |    |    |    |

|-----|-----|----|----|-----|------|----|----|----|------------|----|----|----------|----|----|----|----|

| NO  | R/W | A6 | A5 | A4  | A3   | A2 | A1 | A0 | D7         | D6 | D5 | D4       | D3 | D2 | D1 | D0 |

| R6  | 1/0 | 0  | 0  | 0   | 0    | 1  | 1  | 0  | HBLK_EN(0) | 0  | 0  | VBP(1Bh) |    |    |    |    |

#### R6[4:0] - VBP: Vertical blanking setting

| DC[4:0] | VE          | 3P          | Linit |

|---------|-------------|-------------|-------|

| R6[4:0] | NTSC        | PAL         | Unit  |

| 00h~03h | 3           | 3~6         |       |

| 04h~1Ah | 4~26        | 7~29        |       |

| 1Bh     | 27(Default) | 30(Default) | HS    |

| 1Fh     | 31          | 34          |       |

HBLK\_EN: Refer horizontal back porch setting table at R07h.

#### Register setting – R7

| cgic |     | ing in |    |     |      |      |    |    |       |          |    |    |    |    |    |    |    |

|------|-----|--------|----|-----|------|------|----|----|-------|----------|----|----|----|----|----|----|----|

|      | Reg |        |    |     | Add  | ress |    |    | Data  |          |    |    |    |    |    |    |    |

|      | NO  | R/W    | A6 | A5  | A4   | A3   | A2 | A1 | A0    | D7       | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|      | R7  | 1/0    | 0  | 0   | 0    | 0    | 1  | 1  | 1     | HBP(28h) |    |    |    |    |    |    |    |

|      |     |        |    | HS  |      |      |    |    |       |          |    |    |    | _  |    |    |    |

|      |     |        |    | DAT | ГА — | i    |    | _  | Valio | l Data   |    |    |    | _  |    |    |    |

HBP

#### R7[7:0] - HBP: Horizontal blanking setting

| HBLK_E<br>N<br>(Reg. 6) | (D7-D0) | HBP         | Remark    |

|-------------------------|---------|-------------|-----------|

|                         | 0~A     | 10          |           |

| 0 or 1                  | 28h     | 40(Default) | 8-bit RGB |

|                         | FFh     | 255         |           |

| 0                       | -       | 40(fixed)   |           |

|                         | 0~A     | 10          | Others    |

| 1                       | 28h     | 40          | Outers    |

|                         | FFh     | 255         |           |

# CHINEL INNOLUX

### 990001265 project

| <br>logiolo | a oounig | 1.00 |    |     |      |    |    |      |     |       |    |         |    |         |        |              |

|-------------|----------|------|----|-----|------|----|----|------|-----|-------|----|---------|----|---------|--------|--------------|

| Reg         |          |      |    | Add | ress |    |    | Data |     |       |    |         |    |         |        |              |

| NO          | R/W      | A6   | A5 | A4  | A3   | A2 | A1 | A0   | D7  | D6    | D5 | D4      | D3 | D2      | D1     | D0           |

| R0C         | 1/0      | 0    | 0  | 0   | 1    | 1  | 0  | 0    | VST | Г (0) | 0  | CbCr(0) | 0  | VSPI(1) | HSP(1) | DCLKP<br>(0) |

#### R0C[0] - DCLKP: DCLK polarity selection

| DCLKpol | Function                    |

|---------|-----------------------------|

| 0       | Positive polarity (Default) |

| 1       | Negative polarity           |

#### R0C[1] – HSP: Hsync polarity selection

| Hdpol                                  | Function                    |  |  |  |  |  |  |  |  |  |

|----------------------------------------|-----------------------------|--|--|--|--|--|--|--|--|--|

| 0                                      | Positive polarity           |  |  |  |  |  |  |  |  |  |

| 1                                      | Negative polarity (Default) |  |  |  |  |  |  |  |  |  |

| R0C[2] – VSP: Vsync polarity selection |                             |  |  |  |  |  |  |  |  |  |

| Vdpol                                  | Function                    |  |  |  |  |  |  |  |  |  |

| 0                                      | Positive polarity           |  |  |  |  |  |  |  |  |  |

| 1                                      | Negative polarity (Default) |  |  |  |  |  |  |  |  |  |

#### R0C[4] – CbCr: Cb & Cr exchange, valid for 8-bit YUV mode

| D4 | CbCr Function           |

|----|-------------------------|

| 0  | Cb -> Y -> Cr (Default) |

| 1  | Cr -> Y -> Cb           |

#### R0C[7:6] – VST: Vertical back porch selection

Refer to Vertical back porch table

Vertical back porch table

### 990001265 project

#### 8/16/24-bit RGB mode / 320 Dummy RGB / 360 Dummy RGB

| VS | ST | Vertical back porch | Linit |  |

|----|----|---------------------|-------|--|

| D7 | D6 | ODD / EVEN frame    | Unit  |  |

| Х  | 0  | N / N (Default)     | 110   |  |

| Х  | 1  | N / N-1             | HS    |  |

N according as the register VBP(R6h[4:0])

8/16-bit YUV mode

| VS | ST            | Vertical back porch | Linit |  |  |  |

|----|---------------|---------------------|-------|--|--|--|

| D7 | D6            | Unit                |       |  |  |  |

| 0  | 0             |                     |       |  |  |  |

| 0  | 1             | N / N+1             | HS    |  |  |  |

| 1  | 0             | N+1 / N             | по    |  |  |  |

| 1  | 1 1 N+1 / N+1 |                     |       |  |  |  |

N according as the register VBP(R6h[4:0])

#### Register setting - R0D

| Reg |     |    |    | Add | ress |    |    | Data |                 |    |    |    |    |    |    |    |

|-----|-----|----|----|-----|------|----|----|------|-----------------|----|----|----|----|----|----|----|

| NO  | R/W | A6 | A5 | A4  | A3   | A2 | A1 | A0   | D7              | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| RD  | 1/0 | 0  | 0  | 0   | 1    | 1  | 0  | 1    | Contrast_B(40h) |    |    |    |    |    |    |    |

#### R0D[7:0] - Contrast\_B: RGB contrast level setting, the gain changes (1/64)/bit

| (MSB-ML<br>B) | Contrast Gain |

|---------------|---------------|

| 00h           | 0             |

| 40h           | 1(Default)    |

| FFh           | 3.984         |

#### Register setting - R0E

| Reg | Address |    |    |    |    |    |    |    |    | Data                |    |    |    |    |    |    |  |

|-----|---------|----|----|----|----|----|----|----|----|---------------------|----|----|----|----|----|----|--|

| NO  | R/W     | A6 | A5 | A4 | A3 | A2 | A1 | A0 | D7 | D6                  | D5 | D4 | D3 | D2 | D1 | D0 |  |

| R0E | 1/0     | 0  | 0  | 0  | 1  | 1  | 1  | 0  | 0  | SUB_Contrast_R(40h) |    |    |    |    |    |    |  |

R0E[6:0] - SUB-Contrast: R sub-contrast level setting, the gain changes (1/256)step/bit

| (MSB-ML<br>B) | Contrast Gain |

|---------------|---------------|

| 00h           | 0.75          |

| 40h           | 1(Default)    |

| 7Fh           | 1.246         |

#### Register setting – R0F

| Reg | Address |                          |   |   |   |   |   |   |   | Address Data           |  |        |          |         |  |  |  |  |

|-----|---------|--------------------------|---|---|---|---|---|---|---|------------------------|--|--------|----------|---------|--|--|--|--|

| NO  | R/W     | R/W A6 A5 A4 A3 A2 A1 A0 |   |   |   |   |   |   |   | D7 D6 D5 D4 D3 D2 D1 D |  |        |          |         |  |  |  |  |

| R0F | 1/0     | 0                        | 0 | 0 | 1 | 1 | 1 | 1 | 0 |                        |  | SUB_Br | ightness | _R(40h) |  |  |  |  |

|     |         |                          |   |   |   |   |   |   |   |                        |  |        |          |         |  |  |  |  |

#### R0F[6:0] - SUB\_Brightness: R sub-brightness level setting, setting accuracy: 1 step / bit

| (MSB-ML<br>B) | Brightness Gain     |

|---------------|---------------------|

| 00h           | Dark(-64)           |

| 40h           | Center(0) (Default) |

| 7Fh           | Bright(+63)         |

#### Register setting – R10

| Reg |     |                          |  | Add | ress |  |  |  |  |  | Da | ata   |          |        |    |    |

|-----|-----|--------------------------|--|-----|------|--|--|--|--|--|----|-------|----------|--------|----|----|

| NO  | R/W | R/W A6 A5 A4 A3 A2 A1 A0 |  |     |      |  |  |  |  |  | D5 | D4    | D3       | D2     | D1 | D0 |

| R10 | 1/0 | 1/0 0 0 1 0 0 0          |  |     |      |  |  |  |  |  |    | SUB_C | contrast | B(40h) |    |    |

#### R10[6:0] - SUB-Contrast: B sub-contrast level setting, the gain changes (1/256)step/bit

| (MSB-ML<br>B) | Contrast Gain |

|---------------|---------------|

| 00h           | 0.75          |

| 40h           | 1(Default)    |

| 7Fh           | 1.246         |

#### Register setting - R11

| Reg | Address                  |  |  |  |  |  |  |  |   | Idress Data             |    |    |    |    |    |    |  |

|-----|--------------------------|--|--|--|--|--|--|--|---|-------------------------|----|----|----|----|----|----|--|

| NO  | R/W A6 A5 A4 A3 A2 A1 A0 |  |  |  |  |  |  |  |   | D6                      | D5 | D4 | D3 | D2 | D1 | D0 |  |

| R11 | 1/0 0 0 1 0 0 1          |  |  |  |  |  |  |  | 0 | 0 SUB_Brightness_B(40h) |    |    |    |    |    |    |  |

#### R11[6:0] - SUB\_Brightness: B sub-brightness level setting, setting accuracy: 1 step / bit

| (MSB-ML<br>B) | Brightness Gain     |

|---------------|---------------------|

| 00h           | Dark(-64)           |

| 40h           | Center(0) (Default) |

| 7Fh           | Bright(+63)         |

#### Register setting - R13

| Reg | Address |                          |   |   |   |   |   |   |        |    |    | Dat | a  |    |    |    |

|-----|---------|--------------------------|---|---|---|---|---|---|--------|----|----|-----|----|----|----|----|

| NO  | R/W     | R/W A6 A5 A4 A3 A2 A1 A0 |   |   |   |   |   |   |        | D6 | D5 | D4  | D3 | D2 | D1 | D0 |

| R13 | 1/0     | 0                        | 0 | 1 | 0 | 0 | 1 | 1 | REGSEL | 0  | 0  | 0   | 0  | 0  | 0  | 0  |

#### R13[7] – REGSEL: OTP function control

| REGSEL | Description                                  |

|--------|----------------------------------------------|

| 0      | VCOMH and VCOML were according as OTP memory |

| 0      | (Default)                                    |

| 1      | VCOMH and VCOML were according as the regis- |

| 1      | ters(R1Bh/R1Ch)                              |

Note: If OTP didn't programming, VCOMH and VCOML were according as the registers

#### Register setting – R1B

| Reg |                          |   |   | Add | ress |   |   |   |  |    | Da | ata  |        |    |    |    |

|-----|--------------------------|---|---|-----|------|---|---|---|--|----|----|------|--------|----|----|----|

| NO  | R/W A6 A5 A4 A3 A2 A1 A0 |   |   |     |      |   |   |   |  | D6 | D5 | D4   | D3     | D2 | D1 | D0 |

| R1B | 1/0                      | 0 | 0 | 1   | 1    | 0 | 1 | 1 |  |    |    | VCOM | H(9Dh) |    |    |    |

#### R1B[7:0] - VCOMH: VCOMH level adjustment( 1 step : 10 mV)

| VCOMH level | (Unit : V)     |

|-------------|----------------|

| 00h         | 2.35           |

|             |                |

| 9Dh         | 3.92 (Default) |

|             |                |

| FBh         | 4.86           |

| FCh | 4.87 |

|-----|------|

| FDh | 4.88 |

| FEh | 4.89 |

| FFh | 4.9  |

#### Register setting - R1C

| Re  | Address |    |    |    |    |    |    |    |            |    |    | Da | ata |    |    |    |

|-----|---------|----|----|----|----|----|----|----|------------|----|----|----|-----|----|----|----|

| NC  | R/W     | A6 | A5 | A4 | A3 | A2 | A1 | A0 | D7         | D6 | D5 | D4 | D3  | D2 | D1 | D0 |

| R10 | 2 1/0   | 0  | 0  | 1  | 1  | 1  | 0  | 0  | VCOML(60h) |    |    |    |     |    |    |    |

#### R1C[7:0] - VCOML: VCOML level adjustment( 1 step : 10 mV)

| VCOMLlevel | (Unit : V)      |

|------------|-----------------|

| 00h        | -2.7            |

|            |                 |

| 60h        | -1.74 (Default) |

|            |                 |

| F9h        | -0.21           |

| FAh        | -0.2            |

| FBh        | -0.2            |

| FCh        | -0.2            |

| FDh        | -0.2            |

| FEh        | -0.2            |

| FFh        | -0.2            |

#### Register setting – R2B

| Reg |     | Address |    |    |    |    |    |    |    |    | Data |    |    |    |    |        |  |  |

|-----|-----|---------|----|----|----|----|----|----|----|----|------|----|----|----|----|--------|--|--|

| NO  | R/W | A6      | A5 | A4 | A3 | A2 | A1 | A0 | D7 | D6 | D5   | D4 | D3 | D2 | D1 | D0     |  |  |

| R2B | 1/0 | 0       | 1  | 0  | 1  | 0  | 1  | 1  | 0  | 0  | 0    | 0  | 0  | 0  | 0  | STB(0) |  |  |

#### R2B[0] - STB: Standby (power saving) mode setting

| STB | Function               |

|-----|------------------------|

| 0   | Standby mode (Default) |

| 1   | Normal operation       |

#### Register setting - R2F

| Reg | Address |    |    |    |    |    |    |    |              |    |    | Da | ata |    |    |    |

|-----|---------|----|----|----|----|----|----|----|--------------|----|----|----|-----|----|----|----|

| NO  | R/W     | A6 | A5 | A4 | A3 | A2 | A1 | A0 | D7           | D6 | D5 | D4 | D3  | D2 | D1 | D0 |

| R2F | 1/0     | 0  | 1  | 0  | 1  | 1  | 1  | 1  | VGL_SEL(010) |    | 0  | 0  | 0   | 0  | 0  |    |

R2F[7:5] - VGL\_SEL: VGL voltage selection

|    | Bit |    | Output          |

|----|-----|----|-----------------|

| D7 | D6  | D5 | VGL (V)         |

| 0  | 0   | 0  | -8.0            |

| 0  | 0   | 1  | -9.0            |

| 0  | 1   | 0  | -10.0 (Default) |

| 0  | 1   | 1  | -11.0           |

| 1  | 0   | 0  | -7.0            |

| 1  | 0   | 1  | -7.0            |

| 1  | 1   | 0  | -12.0           |

| 1  | 1   | 1  | -12.0           |

### 990001265 project

#### Register setting – R5A

| Reg |     | Address |    |    |    |    |    |    |    |    |    | Da | ata |     |        |      |

|-----|-----|---------|----|----|----|----|----|----|----|----|----|----|-----|-----|--------|------|

| NO  | R/W | A6      | A5 | A4 | A3 | A2 | A1 | A0 | D7 | D6 | D5 | D4 | D3  | D2  | D1     | D0   |

| R5A | 1/0 | 1       | 0  | 1  | 1  | 0  | 1  | 0  | 0  | 0  | 0  | 0  | 0   | VGł | H_SEL( | 101) |

#### R5A[2:0] - VGH\_SEL: VGH voltage selection

|    | Bit |    | Output         |

|----|-----|----|----------------|

| D2 | D1  | D0 | VGH (V)        |

| 0  | 0   | 0  | 13.0           |

| 0  | 0   | 1  | 14.0           |

| 0  | 1   | 0  | 15.0 (Default) |

| 0  | 1   | 1  | 16.0           |

| 1  | 0   | 0  | 17.0           |

| 1  | 0   | 1  | 18.0           |

| 1  | 1   | 0  | 18.0           |

| 1  | 1   | 1  | 18.0           |

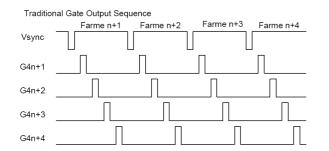

#### Register setting – R5C

| Reg |     | Address |    |    |    |    |    |    |    |    | Data |    |    |    |     |     |  |  |

|-----|-----|---------|----|----|----|----|----|----|----|----|------|----|----|----|-----|-----|--|--|

| NO  | R/W | A6      | A5 | A4 | A3 | A2 | A1 | A0 | D7 | D6 | D5   | D4 | D3 | D2 | D1  | D0  |  |  |

| R5C | 1/0 | 1       | 0  | 1  | 1  | 1  | 0  | 0  | 0  | 0  | 0    | 0  | 0  | 0  | GO_ | SEQ |  |  |

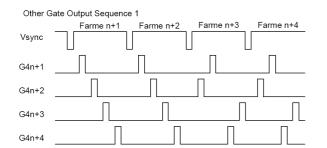

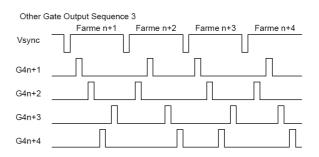

#### R5C[1:0] – GO\_SEQ: Gate output sequence setting

| NTSC | C/PAL | Description                           |

|------|-------|---------------------------------------|

| D1   | D0    | Description                           |

| 0    | 0     | Traditional gate output sequence      |

| 0    | 1     | Other gate output sequence1           |

| 1    | 0     | Other gate output sequence2 (Default) |

| 1    | 1     | Other gate output sequence3           |

### 990001265 project

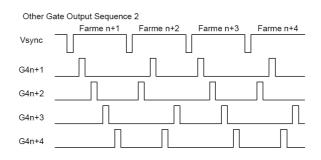

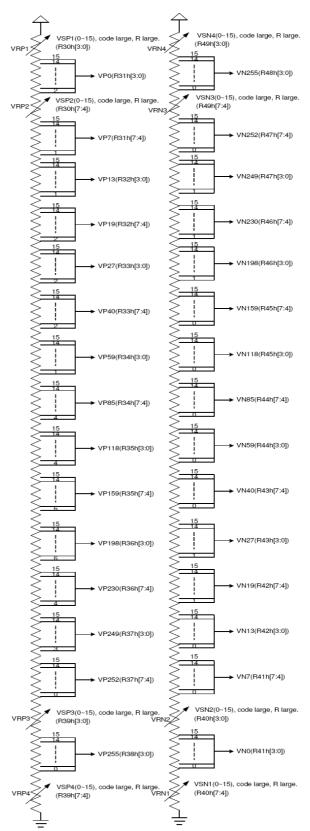

### Gamma Register Setting- R30h~R49h

| Gamma |           | Setting | Gamma |           | Setting |

|-------|-----------|---------|-------|-----------|---------|

| point | Register  | •       | point | Register  | •       |

|       |           | range   | ·     |           | range   |

| VSP1  | R30h[3:0] | 0~15    | VSN4  | R49h[7:4] | 0~15    |

| VP0   | R31h[3:0] | 2~15    | VN255 | R48h[3:0] | 0~15    |

| VSP2  | R30h[7:4] | 0~15    | VSN3  | R49h[3:0] | 0~15    |

| VP7   | R31h[7:4] | 1~15    | VN252 | R47h[7:4] | 0~15    |

| VP13  | R32h[3:0] | 1~15    | VN249 | R47h[3:0] | 1~15    |

| VP19  | R32h[7:4] | 2~15    | VN230 | R46h[7:4] | 1~15    |

| VP27  | R33h[3:0] | 2~15    | VN198 | R46h[3:0] | 1~15    |

| VP40  | R33h[7:4] | 2~15    | VN159 | R45h[7:4] | 0~15    |

| VP59  | R34h[3:0] | 1~15    | VN118 | R45h[3:0] | 0~15    |

| VP85  | R34h[7:4] | 4~15    | VN85  | R44h[7:4] | 0~15    |

| VP118 | R35h[3:0] | 4~15    | VN59  | R44h[3:0] | 0~15    |

| VP159 | R35h[7:4] | 6~15    | VN40  | R43h[7:4] | 0~15    |

| VP198 | R36h[3:0] | 6~15    | VN27  | R43h[3:0] | 1~15    |

| VP230 | R36h[7:4] | 4~15    | VN19  | R42h[7:4] | 1~15    |

| VP249 | R37h[3:0] | 3~15    | VN13  | R42h[3:0] | 0~15    |

| VP252 | R37h[7:4] | 0~15    | VN7   | R41h[7:4] | 0~15    |

| VSP3  | R39h[3:0] | 0~15    | VSN2  | R40h[7:4] | 0~15    |

| VP255 | R38h[3:0] | 0~15    | VN0   | R41h[3:0] | 0~15    |

| VSP4  | R39h[7:4] | 0~15    | VSN1  | R40h[3:0] | 0~15    |

Note:

- The registers VSPn/VSNn adjust the value of the resistor VRPn/VRNn.

- When n=1 and n=4 affect the voltage of all gamma point at the resistor string.

- When n=2 affects the voltage of all gamma point at resistor string besides VP0/VN0.

- When n=3 affects the voltage of all gamma point at resistor string besides VP255/VN255.

### **13. OPTICAL CHARACTERISTICS**

### 13-1. Optical Specification

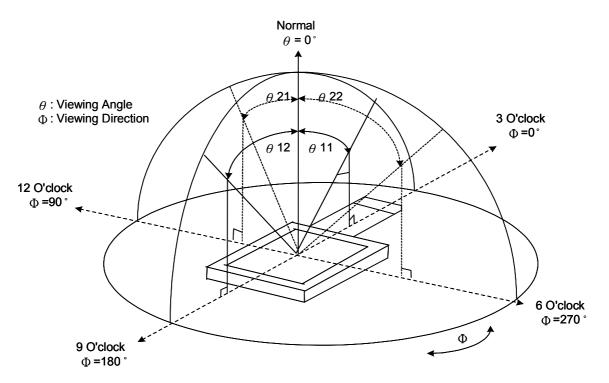

| ltem                             |            | Symbol         | Condition | MIN  | TYP  | MAX  | Unit              | Remarks   |

|----------------------------------|------------|----------------|-----------|------|------|------|-------------------|-----------|

|                                  |            | ⊖11            |           |      | 60   | -    |                   |           |

|                                  | •          | ⊖1 <b>2</b>    | CR ≥ 10   |      | 60   | -    | Dograa            | Note 13-1 |

| Viewing Angle                    | 5          | <b>⊖21</b>     | CR 2 10   |      | 50   | -    | Degree            | NOLE 13-1 |

|                                  |            | <b>⊖22</b>     |           |      | 55   | -    |                   |           |

| Contrast Ratio                   | C          | CR             |           |      | 500  | -    |                   | Note 13-2 |

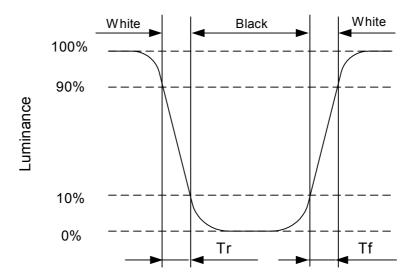

| Response Tim                     | е          | Tr+Tf          |           | -    | 35   |      | ms                | Note 13-3 |

| Luminance (I <sub>F</sub> =25mA) | I          | L              | ⊖=0°      | 400  | 500  |      | cd/m <sup>2</sup> | Note 13-4 |

| Chromaticity White               |            | X <sub>W</sub> |           | 0.25 | 0.30 | 0.35 |                   | Note 13-5 |

| VIIIte                           |            | Уw             |           | 0.27 | 0.32 | 0.37 |                   | NOLE 13-5 |

| Uniformity                       | Uniformity |                |           | 70   |      |      | %                 |           |

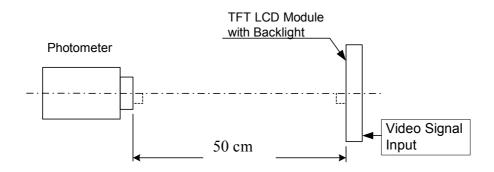

### 13-2. Basic Measure Conditions

(1) Driving voltage

Vcc= 3.3 V

- (2) Ambient Temperature: Ta=25°C

- (3) Testing Point: Measure in the display center point and the test angle  $\ominus$  =0 °

- (4) LED Current:  $I_F$ =25mA.

- (5) Testing Facility

Environmental illumination: ≤ 1 Lux

Note 13-1: Viewing angle diagrams:

Note 13-2: Contrast Ratio:

Contrast ratio is measured in optimum common electrode voltage.

$CR = \frac{Luminance with white image}{Luminance with black image}$

Note 13-3: Definition of response time:

Note 13-4: Luminance:

Test Point: Display Center

Note 13-5: Chromaticity: The same test condition as Note 13-4.

### 14. RELIABILITY

| No | Test Item                                  | Condition                                      |  |  |  |

|----|--------------------------------------------|------------------------------------------------|--|--|--|

| 1  | High Temperature Operation                 | Ta=+60°C, 240hrs                               |  |  |  |

| 2  | High Temperature & High Humidity Operation | Ta=+40°C, 95% RH, 240hrs                       |  |  |  |

| 3  | Low Temperature Operation                  | Ta= 0°C , 240hrs                               |  |  |  |

| 4  | High Temperature Storage (non-operation)   | Ta=+80°C, 240hrs                               |  |  |  |

| 5  | Low Temperature Storage (non-operation)    | Ta=-30℃, 240hrs                                |  |  |  |

| 6  | Thermal Shack (non energtion)              | -30°C                                          |  |  |  |

|    | Thermal Shock (non-operation)              | 30 min 30 min                                  |  |  |  |

| 7  | Posistance to Static Electricity Discharge | C=200pF, R=0Ω;                                 |  |  |  |

|    | Resistance to Static Electricity Discharge | Discharge: ±150V                               |  |  |  |

|    | (non-operation)                            | 3 times / Terminal                             |  |  |  |

| 8  |                                            | Frequency: 10~55Hz; Amplitude: 1.5mm           |  |  |  |

|    | Vibration (non-operation)                  | Sweep Time: 11min                              |  |  |  |

|    |                                            | Test Time: 2 hrs for each direction of X, Y, Z |  |  |  |

| 9  | Shock (non-onoration)                      | Acceleration: 100G; Period: 6ms                |  |  |  |

|    | Shock (non-operation)                      | Directions: ±X, ±Y, ±Z; Cycles: Twice          |  |  |  |

Ta: Ambient Temperature

- \* For environment stress test, the image quality guarantee after recover time 2 hours at ambient environment.

- \* Polarizer cosmetic is not guarantee after reliability test.

### **15. HANDLING CAUTIONS**

15.1 ESD (Electrical Static Discharge) Strategy

ESD will cause serious damage of the panel, ESD strategy is very important in handling. Following items are the recommend ESD strategy

- (1) In handling LCD panel, please wear non-charged material gloves. And the conduction ring connect wrist to the earth and the conducting shoes to the earth is necessary.

- (2) The machine and working table for the panel should have ESD prohibition strategy.

- (3) In handling the panel, ionize flowing decrease the charge in the environment is necessary.

- (4) In the process of assembly the module, shield case should connect to the ground.

### 15.2 Environment

- (1) Working environment of the panel should in the clean room.

- (2) The front polarizer is easy damaged, handle it carefully and do not scratch it by sharp material.

- (3) Panel has polarizer protective film in the surface please remove the protection film of polarizer slowly with ionized air to prevent the electrostatic discharge.

- 15.3 Others

- (1) Turn off the power supply before connecting and disconnecting signal input cable.

- (2) The connection area of FPC and panel is very weak, do not handle panel only by FPC or bend FPC.

- (3) Water drop on the surface or condensation as panel power on will corrode panel electrode.

- (4) As the packing bag open, watch out the environment of the panel storage. High temperature and high humidity environment is prohibited.

- (5) When the TFT LCD module is broken, please watch out whether liquid crystal leaks out or not. If your hand touches liquid crystal, wash your hand cleanly by water and soap as soon as possible.

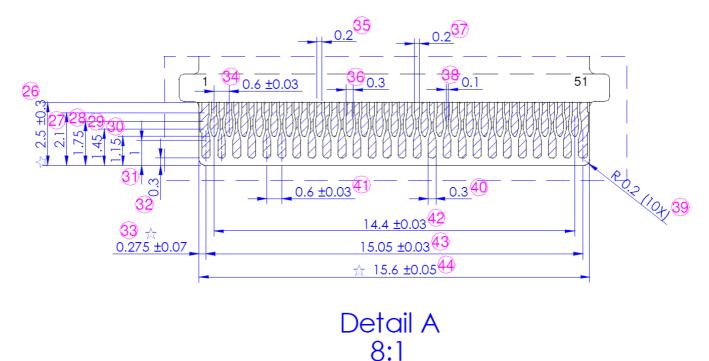

**16. MECHANICAL DRAWING**

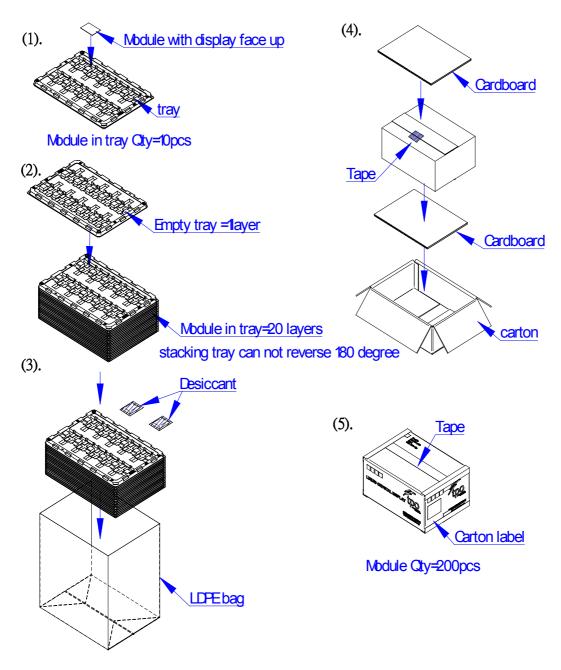

17. Packing Drawing

- 3.0" module (EJ030NA-01B) delivery packing method

- (1). Module packed into tray cavity (with Module display face up).

- (2). Tray stacking with 20 layers and with 1 empty tray above the stacking tray unit.2pcs desiccant put above the empty tray

- (3). Stacking tray unit put into the LDPE bag and fix by adhesive tape.

- (4). Put 1pc cardboard inside the carton bottom, and then pack the package unit into the carton. Put 1pc cardboard above the package unit.

- (5). Carton tapping with adhesive tape.

### (6). Lot Number

Describe: there are two lines. In the first line, the first is model, such as "990001265", the second is type name, such as "EJ030NA-01B", and the second line is LN of 13 sequences.

| Z1 | Z2 Z3 | Z4 | Z5 | Z6 | Z7 | Z8 | Z9 | Z10 | Z11 | Z12 | Z13 |  |

|----|-------|----|----|----|----|----|----|-----|-----|-----|-----|--|

|----|-------|----|----|----|----|----|----|-----|-----|-----|-----|--|

Definition as follows:

Z1: Code of assembly factory buildings, LCM1:K ; LCM2:H

Z2: Lot type: N, R, S, M.....

Z3: The last code is producing year, such as 2010 is"0".

Z4~Z5: The code is producing week

Z6~Z9: The codes are SN.

Z10: The code of reserve number is A.

Z11: The No.11 code is dot.

Z12~Z13: The codes are Sub ID.

(7). Bottom Metal Shot-Case Mark

Describe: The mark defined with the permutation of numeral and alphabet in random.

Each mark represented for one operator and won't be repeated.

Lot3 marks on right-bottom corner and OQC marks on left-top corner (FPC toward down side).

OQC mark will keep 100% mark until customer's approval that CMI can sampling this process.

\* When wipe mark out from S/C, please don't let Alcohol solvent permeate into panel inside.