Freescale Semiconductor Engineering Bulletin EB632 Rev. 2, 1/2005

# Functional Differences Between MSC8101 (Mask 2K42A) and MSC8103 (Mask 2K87M)

# 1 Introduction

This document describes the differences between MSC8101 mask set 2K42A and MSC8103 mask set 2K87M. These differences include:

System Interface Unit (SIU) changes:

— Internal Memory Map Register (IMMR) MASKNUM field value

— Addition of the Internal Memory Map Mirror Register (IMMMR)

- Reset changes:

- Modes

- Hard Reset Configuration Word (HRCW) layout

- Boot source changes

- Clock changes

- Clock scheme

- System Clock Mode Register (SCMR)

- Addition of the CLKODIS field to the System Clock Control Register (SCCR)

- Clock modes

- CLKIN to CLKOUT delay change

- Maximum clock frequencies change

- Memory map addition of IMMMR

- ORx in UPM mode, bit 27 functionality difference

- Host interface (HDI16) changes

- Direct memory access (DMA) controller transfer code (TC) definitions

### CONTENTS

| 1  | Introduction1                 |

|----|-------------------------------|

| 2  | Summary of Differences2       |

| 3  | SIU                           |

| 4  | Reset6                        |

| 5  | Boot9                         |

| 6  | Clock System                  |

| 7  | Memory Map                    |

| 8  | ORx in UPM Mode22             |

| 9  | HDI16                         |

| 10 | DMA Transfer Code Definitions |

| 11 | Interrupt System              |

| 12 | Debugging                     |

| 13 | EFCOP                         |

| 14 | CPM                           |

| 15 | Errata                        |

| А  | Bootloader Program            |

© Freescale Semiconductor, Inc., 2002, 2005. All rights reserved.

#### Summary of Differences

- Interrupt system changes:

- CPM Low Interrupt Priority Registers (SCPRR\_L and SCPRR\_L\_EXT) definitions

Assignment of interrupt vector 44 to transmission convergence (TC) layer request

- Debugging system changes:

- JTAG ID

٠

- EOnCE Status Register (ESR) values

- Removal of Enhanced Filter Coprocessor (EFCOP) support

- Communications processor module (CPM) changes:

- RISC Controller Configuration Register (RCCR)

- Dual-port RAM

- Addition of ROM-based inverse multiplexing for ATM (IMA) microcode

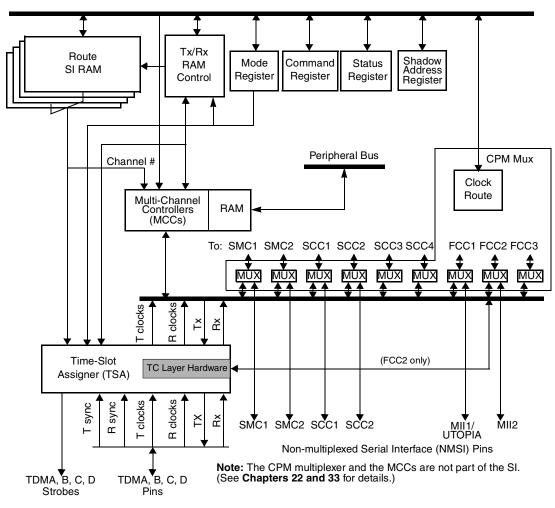

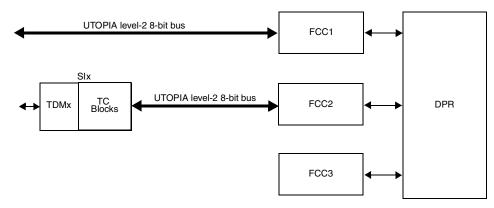

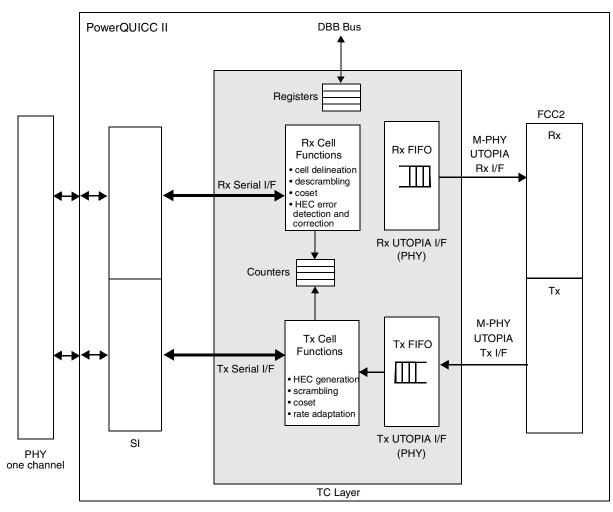

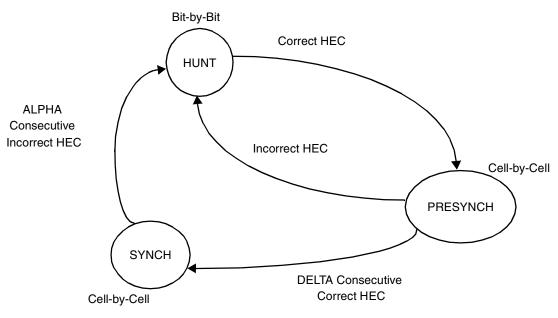

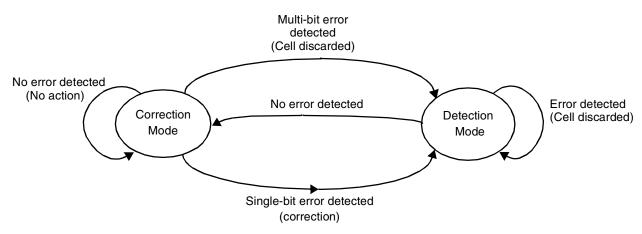

- Addition of TC layer functionality to the time-slot assigner (TSA) with support through FCC2

- Addition of new MCC host commands

- Errata

- New bootloader program

# 2 Summary of Differences

Table 1 lists a summary of the differences between MSC8101 mask set 2K42A and MSC8103 mask set 2K87M.

| Module              | Function                                       | MSC8101 Mask Set 2K42A                                                            | MSC8103 Mask Set 2K87M                                                                                                                    |  |  |  |

|---------------------|------------------------------------------------|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| System<br>Interface | Internal Memory Map Register<br>(IMMR)         | MASKNUM bit field = 0x02                                                          | MASKNUM bit field = 0x12                                                                                                                  |  |  |  |

| Unit (SIU)          | Internal Memory Map Mirror<br>Register (IMMMR) | Not supported                                                                     | Added                                                                                                                                     |  |  |  |

| Reset               | Supported modes                                | Host reset and hardware reset                                                     | Host reset, hardware reset, and reduced reset                                                                                             |  |  |  |

|                     | Hardware reset configuration word              | Seventeen fields defined                                                          | Eighteen fields definedsoftware watchdog disable (SWDIS) bit added                                                                        |  |  |  |

| Boot                | Boot sources supported                         | From host (HDI16) or external memory (system bus)                                 | From host (HDI16), external memory<br>(system bus), or serial EPROM (I <sup>2</sup> C<br>interface)                                       |  |  |  |

| Clock               | Clock Scheme                                   | Clock scheme configures SPLL PDF,<br>SPLL MF, and Bus DF                          | Clock scheme configures SPLL PDF,<br>SPLL MF, Bus DF, CPM DF, Core DF,<br>CPLL PDF, and CPLL MF                                           |  |  |  |

|                     | System Clock Mode Register<br>(SCMR)           | Defines seven fields                                                              | Defines eight fields                                                                                                                      |  |  |  |

|                     | System Clock Control Register (SCCR)           | Defines one field (DFBRG)                                                         | Defines two fields (CLKODIS and<br>DFBRG)                                                                                                 |  |  |  |

|                     | Clock modes                                    | Two valid modes                                                                   | Twenty-seven valid modes                                                                                                                  |  |  |  |

|                     | CLKIN-to-CLKOUT delay                          | A function of frequency                                                           | Not a function of frequency                                                                                                               |  |  |  |

|                     | Enabling the DLL                               | DLL-enabled mode is not supported and designs must use a zero-delay clock buffer. | To enable the DLL, the zero-delay clock<br>buffer recommended for the 2K42A<br>mask set must be placed in PLL-bypass<br>mode or replaced. |  |  |  |

|                     | Disabling the DLL                              |                                                                                   | For clock modes 5, 6, 46, and 57, apply offsets to DLL-disabled timing.                                                                   |  |  |  |

|                     | Maximum clock frequencies                      | BCLK/CLKOUT/SCLK = 68.75 MHz<br>CPMCLK = 137.5 MHz<br>DSPCLK = 275 MHz            | BCLK/CLKOUT/SCLK = 100 MHz<br>CPMCLK = 200 MHz<br>DSPCLK = 300 MHz                                                                        |  |  |  |

| Module                                            | Function                                               | MSC8101 Mask Set 2K42A                                                                     | MSC8103 Mask Set 2K87M                                                                                                                               |  |  |

|---------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Memory Map                                        | IMMMR                                                  | Not supported                                                                              | Added                                                                                                                                                |  |  |

|                                                   | SCCR                                                   | Not supported                                                                              | Added                                                                                                                                                |  |  |

| Memory<br>Controller                              | ORx in UPM mode                                        | Bit 27 is a Wait State bit. When bit 27 is set, it add one wait state to the memory cycle. | Bit 27 is reserved.                                                                                                                                  |  |  |

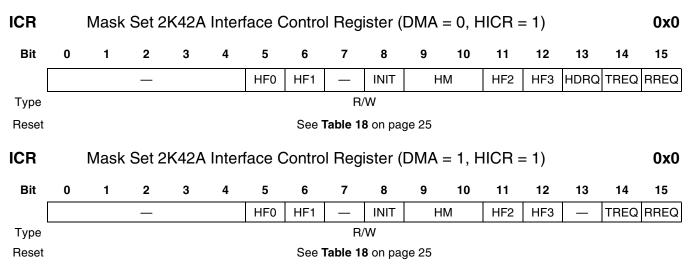

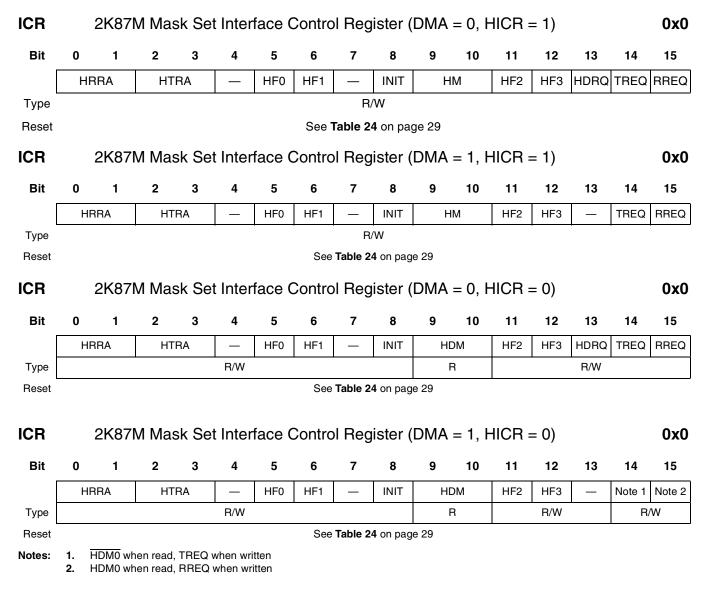

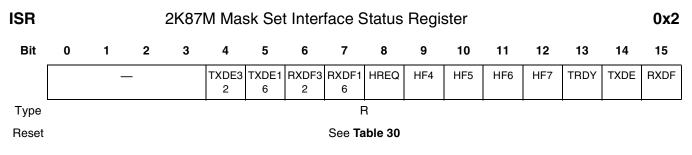

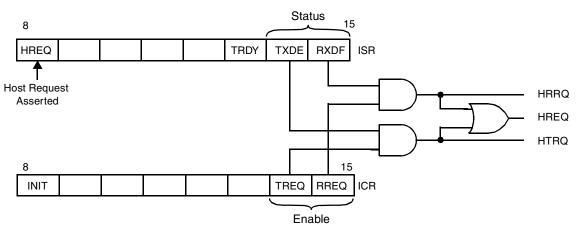

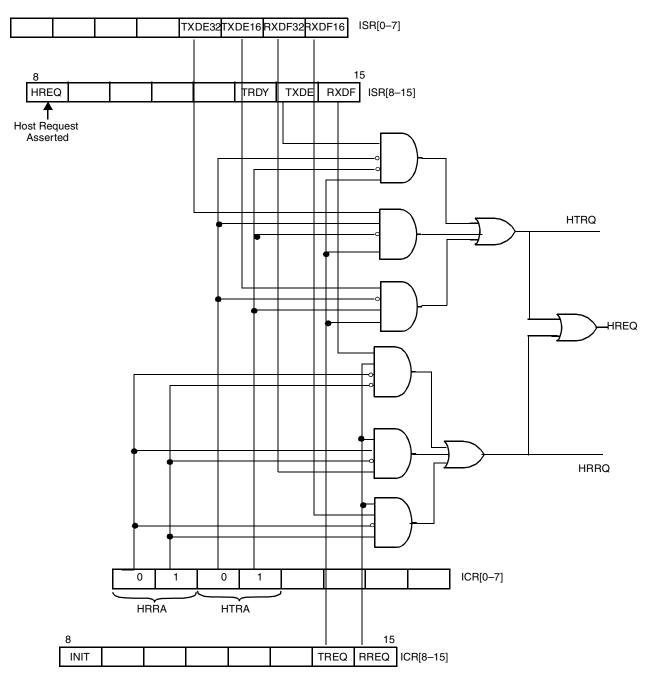

| Host Port<br>(HDI16)                              | ICR and ISR                                            | ICR and ISR do not support HDI6 bursts<br>of different sizes                               | ICR and ISR redefined to support HDI16<br>burst of several sizes.                                                                                    |  |  |

| Direct<br>Memory<br>Access<br>(DMA)<br>controller | Transfer Code (TC) bit definitions                     | As defined in <b>Table 31</b> of this document.                                            | The Transfer Code (TC) bit definitions<br>are modified to conform to the original<br>specification as listed in <b>Table 31</b> of this<br>document. |  |  |

| Interrupts                                        | SCPRR_L and SCPRR_L_EXT<br>YC1P-YC8P field definitions | The value 100 is reserved.                                                                 | The value 100 = "TC layer asserts its request in the YCCn position."                                                                                 |  |  |

|                                                   | Interrupt vector 44                                    | Reserved                                                                                   | Assigned to TC layer interrupt.                                                                                                                      |  |  |

| JTAG/                                             | JTAG ID                                                | 0x0188101D                                                                                 | 0x1188101D                                                                                                                                           |  |  |

| EOnCE<br>system                                   | EOnCE Status Register (ESR) values                     | ESR[REVNO] = 1<br>ESR[CORETP] = 0                                                          | ESR[REVNO] = 2<br>ESR[CORETP] = 2                                                                                                                    |  |  |

| EFCOP                                             | Enhanced Filter Coprocessor                            | Supported as defined in the MSC8101<br>Reference Manual                                    | Not supported                                                                                                                                        |  |  |

| СРМ                                               | RISC Controller Configuration<br>Register (RCCR)       | Enable RAM Microcode (ERAM) field 3 bits wide                                              | Enable RAM Microcode (ERAM) field<br>changed to 4 bits wide                                                                                          |  |  |

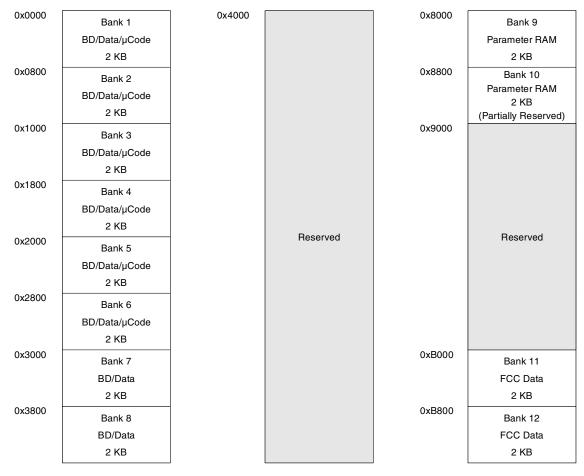

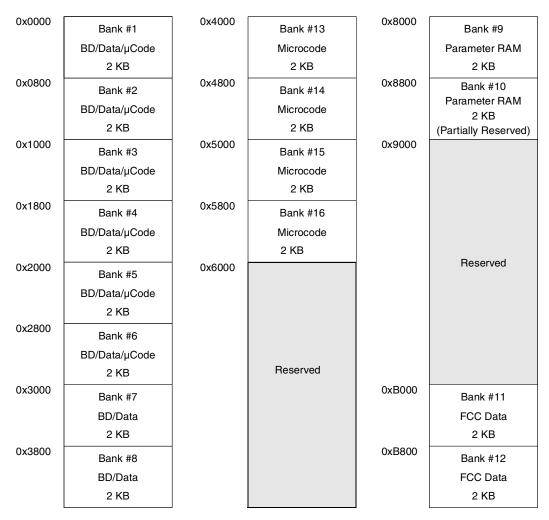

|                                                   | Dual-port RAM                                          | 24 KB                                                                                      | 32 KB                                                                                                                                                |  |  |

|                                                   | IMA functionality                                      | Not available                                                                              | Added                                                                                                                                                |  |  |

|                                                   | Serial Interface (SI) and time-slot assigner (TSA)     | No TSA layer functionality.                                                                | TC layer functionality added to the TSA for ATM with a new interrupt (vector 44)                                                                     |  |  |

| All                                               | Errata                                                 | Documented in the current errata list                                                      | See <b>Table 48</b> , <b>Table 49</b> , and <b>Table 50</b> for details.                                                                             |  |  |

| Bootloader<br>Program                             | Code list                                              | Available upon request.                                                                    | Listed in Appendix A                                                                                                                                 |  |  |

Table 1. Difference Summary for MSC8101 Mask Set 2K42A and MSC8103 Mask Set 2K87M (Continued)

# 3 SIU

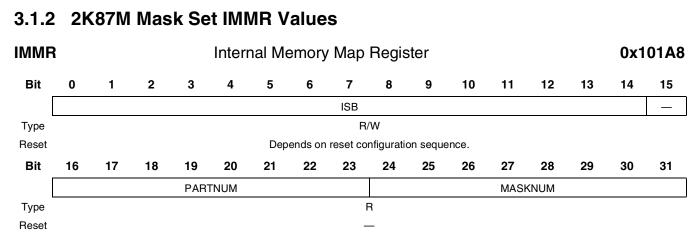

## 3.1 Internal Memory Map Register (IMMR) Change

The IMMR is updated in 2K87M to reflect the mask change. The MASKNUM bit field has changed to 0x12 to reflect the correct revision level.

IMMR identifies a specific device as well as the base address for the internal memory map. Software can deduce availability and location of any on-chip system resources from the values in IMMR. PARTNUM and MASKNUM are mask programmed and cannot be changed for any particular device.

| Bits               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Settings                                      |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| <b>ISB</b><br>0–14 | Internal Space Base<br>Defines the base address of the internal memory space. The value of ISB is configured at<br>reset to one of seven addresses; the software can then change it to any value. The default<br>address is based on the ISB bits in the Hard Reset Configuration Word. The default is zero,<br>which maps to address 0xF0000000.<br>ISB defines the 15 msbs of the memory map register base address. IMMR itself is mapped<br>into the internal memory space region. As soon as the ISB is written with a new base<br>address, the IMMR base address is relocated according to the ISB. ISB enables the<br>configuration of multiple-MSC8101 systems. | Implementation-dependent                      |

| <br>15             | Reserved. Write to zero for future compatibility.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                               |

| PARTNUM<br>16–23   | <b>Part Number</b><br>This field is mask-programmed with a code corresponding to the part number of the part on which the SIU is located. It helps factory test and user code that is sensitive to part changes. This field changes when the part number changes. For example, it would change if any new module is added or if the size of any memory module changes. It does not change if the part is changed to fix a bug in an existing module.                                                                                                                                                                                                                   | The MSC8101 has an ID of 0x50.                |

| MASKNUM<br>24–31   | <b>Mask Number</b><br>This field is mask-programmed with a code corresponding to the mask number of the part<br>on which the SIU is located. It helps factory test and user code that is sensitive to part<br>changes. It is programmed in a commonly changed layer and should be changed for all<br>mask set changes.                                                                                                                                                                                                                                                                                                                                                 | The MSC8101 mask set 2K42A has an ID of 0x02. |

Table 2.

IMMR Bit Descriptions

SIU

IMMR identifies a specific device as well as the base address for the internal memory map. Software can deduce availability and location of any on-chip system resources from the values in IMMR. PARTNUM and MASKNUM are mask programmed and cannot be changed for any particular device.

| Bits                    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Settings                                         |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|

| <b>ISB</b><br>0–14      | Internal Space Base<br>Defines the base address of the internal memory space. The value of ISB is configured at<br>reset to one of seven addresses; the software can then change it to any value. The default<br>address is based on the ISB bits in the Hard Reset Configuration Word. The default is zero,<br>which maps to address 0xF0000000.<br>ISB defines the 15 msbs of the memory map register base address. IMMR itself is mapped<br>into the internal memory space region. As soon as the ISB is written with a new base<br>address, the IMMR base address is relocated according to the ISB. ISB enables the<br>configuration of multiple-MSC8103 systems. | Implementation-dependent                         |

| <br>15                  | Reserved. Write to zero for future compatibility.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                  |

| <b>PARTNUM</b><br>16–23 | <b>Part Number</b><br>This field is mask-programmed with a code corresponding to the part number of the part on which the SIU is located. It helps factory test and user code that is sensitive to part changes. This field changes when the part number changes. For example, it would change if any new module is added or if the size of any memory module changes. It does not change if the part is changed to fix a bug in an existing module.                                                                                                                                                                                                                   | The MSC8103 has an ID of 0x50.                   |

| MASKNUM<br>24–31        | <b>Mask Number</b><br>This field is mask-programmed with a code corresponding to the mask number of the part<br>on which the SIU is located. It helps factory test and user code that is sensitive to part<br>changes. It is programmed in a commonly changed layer and should be changed for all<br>mask set changes.                                                                                                                                                                                                                                                                                                                                                 | The MSC8103 mask set<br>2K87M has an ID of 0x12. |

### Table 3. IMMR Bit Descriptions

## 3.2 Internal Memory Map Mirror Register (IMMMR)

The 2K87M mask set adds a new Internal Memory Map Mirror Register (IMMMR) which has a fixed address controlled by the QBus Bank 1 (0x00F8FFC0) and the same register fields as the IMMR. It reflects the contents of the IMMR. If the ISB in the IMMR is modified, the base address of all SIU and CPM registers, including the IMMR, changes to the new value selected by the ISB. In such a case, the device or external masters may not be able to access the registers. Since the IMMMR does not reside in the same base memory area, it is always available at its fixed address. You can read the current ISB value from the IMMMR and determine the current internal base address from that value.

Functional Differences Between MSC8101 (Mask 2K42A) and MSC8103 (Mask 2K87M), Rev. 2

SIU

# 4 Reset

The 2K42A mask set offers two options for programming the Hard Reset Configuration Word (HRCW). The 2K87M mask set offers three options. In addition, the structure of the HRCW itself is different between the two mask sets.

# 4.1 Reset Configuration Options

Table 4 shows the options for programming the HRCW for each of the mask sets.

| 2K42A                                                                                                    | 2K87M                                                                                                                                                                                                                                                                                                               |

|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Host reset. Through the HDI16 from a host<br>Hardware reset. Through the system bus from external memory | Host reset. Through the HDI16 from a host.<br>Hardware reset. Through the system bus from external memory.<br>Reduced reset. From a serial EPROM using the I <sup>2</sup> C protocol. Limited<br>fields of the hard reset configuration word are configured via the<br>appropriate data bus bits on the system bus. |

## 4.1.1 Configuration Modes

The 2K42A mask set defines the configuration modes as shown in Table 5.

| Table 5. | MSC8101 2 | 2K42A Mask | Set Reset | Configuration Modes |

|----------|-----------|------------|-----------|---------------------|

|----------|-----------|------------|-----------|---------------------|

| RSTCONF | HPE/EE1 | BTM[0-1]/<br>EE[4-5] | Mode                                |  |  |  |  |  |  |

|---------|---------|----------------------|-------------------------------------|--|--|--|--|--|--|

| 1       | 1       | 01                   | host reset configuration            |  |  |  |  |  |  |

| 0       | 0       | 00                   | master hardware reset configuration |  |  |  |  |  |  |

| 1       | 0       | 00                   | slave hardware reset configuration  |  |  |  |  |  |  |

The 2K87M mask set adds a third "reduced reset configuration" method of programming the reset configuration word, in addition to the host reset and hardware reset configuration methods.

| RSTCONF | HPE/EE1 | BTM[0-1]/<br>EE[4-5] | Mode                                |

|---------|---------|----------------------|-------------------------------------|

| 1       | 1       | 01                   | host reset configuration            |

| 0       | 0       | 00                   | master hardware reset configuration |

| 1       | 0       | 00                   | slave hardware reset configuration  |

| 0       | 0       | 10                   | master reduced reset configuration  |

| 1       | 0       | 10                   | slave reduced reset configuration   |

Table 6. MSC8103 2K87M Mask Set Reset Configuration Modes

## 4.1.2 Reduced Reset Configuration Information for Mask Set 2K87M

Reduced reset configuration is executed for serial boot only. Only the NMI\_OUT (bit 12), ISB (bits 13–15), SWDIS (bit 26), and DLLDIS (bit 27) fields in the Hard Reset Configuration Word (HRCW) can be programmed using this method. The rest of the bits are programmed to their default values, but they can be reprogrammed later after reset. **Table 7** describes the 2K87M mask set hard reset configuration word. .

Reset

The major features of the reduce reset configuration include:

- The MSC8103 samples the signals described in **Table 6** at the rising edge of **PORESET**. If the configured boot mode is serial, the values for the NMI\_OUT, ISB, SWDIS, and DLLDIS fields are programmed from the system data bus. The mapping of the bits on the data bus is the same as for hardware reset configuration mode.

- MODCK\_H cannot be programmed using this method and the value is set by default to 000. Therefore, only clock modes 0–1 and 4–7 can be used with this boot mode.

- In reduced configuration mode, the internal reset is extended for 1024 CLKIN cycles.

- Although there is no default HRCW in this mode, the bits in the HRCW that are not programmed assume the default values.

- During the first 8 CLKIN cycles D[12–15] and D[26–27] are sampled to configure the NMI\_OUT, ISB, SWDIS, and DLLDIS fields in the HRCW. All other data bus bits are ignored. The simplest configuration scenario, where all data bus pins are ignored is not available for this mode.

- HRESET in simple slave mode does not change the reset configuration. In master/slave mode, HRESET does cause a new reset configuration.

- Configuration from EPROM for single or multiple chip is available only for the mentioned above 6 bits. All other bits on data bus are ignored.

- Multiple chip configuration in a system with no EPROM is also available only for the mentioned above 6 bits. All other bits on data bus are ignored.

## 4.2 Hard Reset Configuration Word Changes

The 2K87M mask set of the MSC8103 adds the SWDIS field (bit 26) and changes the definition of the ISB field (bits 13–15).

| Bit   | 0    | 1    | 2    | 3   | 4  | 5  | 6     | 7    | 8   | 9   | 10    | 11     | 12  | 13     | 14  | 15 |

|-------|------|------|------|-----|----|----|-------|------|-----|-----|-------|--------|-----|--------|-----|----|

|       | EARB | EXMC | IRQ7 | EBM | BF | PS | SCDIS | ISPS | IRI | °C  | DP    | PC     | NMI |        | ISB |    |

|       |      |      | INT  |     |    |    |       |      |     |     |       |        | OUT |        |     |    |

| Туре  |      |      |      |     |    |    |       | R/W  |     |     |       |        |     |        |     |    |

| Reset | 0    | 0    | 0    | 0   | 0  | 0  | 0     | 0    | 0   | 0   | 0     | 0      | 0   | 0      | 0   | 0  |

| Bit   | 16   | 17   | 18   | 19  | 20 | 21 | 22    | 23   | 24  | 25  | 26    | 27     | 28  | 29     | 30  | 31 |

|       | —    | BBD  | M    | ИR  | -  | _  | TC    | PC   | BC  | IPC | SWDIS | DLLDIS | N   | IODCK_ | Н   | —  |

| Туре  |      |      |      |     |    |    |       | R/W  |     |     | -     | _      |     |        |     |    |

| Reset | 0    | 0    | 0    | 0   | 0  | 0  | 0     | 0    | 0   | 0   | 0     | 0      | 0   | 0      | 0   | 0  |

### MSC8103 2K87M Mask Set Hard Reset Configuration Word

| Table 7. | MSC8103 2K87M Mask Set Hard Reset Configuration Word Bit Descriptions |  |

|----------|-----------------------------------------------------------------------|--|

|          |                                                                       |  |

| Name              | Reset | Description                                                                                                   | Settings                                                                                                                                  |

|-------------------|-------|---------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| <b>EARB</b><br>0  | 0     | External Arbitration<br>Defines the initial value for PPC_ACR[EARB].                                          | 0 = No external arbitration is assumed<br>1 = External arbitration is assumed                                                             |

| EXMC<br>1         | 0     | External MEMC<br>Defines the initial value of BR0[EMEMC].                                                     | 0 = No external memory controller is assumed<br>1 = External memory controller is assumed                                                 |

| IRQ7 INT<br>2     | 0     | IRQ7 or INT_OUT Selection                                                                                     | 0 = $\overline{IRQ7}/\overline{INT}$ DUT pin is $\overline{IRQ7}$<br>1 = $\overline{IRQ7}/\overline{INT}$ DUT pin is $\overline{INT}$ DUT |

| <b>EBM</b><br>3   | 0     | External 60x-compatible Bus Mode<br>Defines the initial value of BCR[EBM].                                    |                                                                                                                                           |

| <b>BPS</b><br>4–5 | 0     | <b>Boot Port Size</b><br>Defines the initial value of BR0[PS], the port size for memory<br>controller bank 0. | 00 = 64-bit port size<br>01 = 8-bit port size<br>10 = 16-bit port size<br>11 = 32-bit port size                                           |

| Name                    | Reset | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Settings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|-------------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| SCDIS<br>6              | 0     | SC140 Disabled<br>Enables/disables the SC140. This bit cannot be changed after<br>reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0 = SC140 enabled<br>1 = SC140 disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| ISPS<br>7               | 0     | Internal Space Port Size<br>Defines the initial value of BCR[ISPS]. This bit must be set in<br>order to use the host interface. Setting ISPS configures the<br>MSC8103 to respond to accesses from a 32-bit external master<br>to its internal space. This bit cannot be changed after reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0 = 60x-compatible data bus is 64 bits wide<br>1 = 60x-compatible data bus is 32 bits wide<br>(lower 32 bits; upper 32 bits reserved for HD116                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| <b>IRPC</b><br>8–9      | 0     | Interrupt Pin Configuration<br>Defines the initial value of SIUMCR[IRPC].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| <b>DPPC</b><br>10–11    | 0     | Data Parity Pin Configuration<br>Defines the initial value of SIUMCR[DPPC].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| <b>NMI OUT</b><br>12    | 0     | NMI OUT<br>Defines the host core to handle a non-maskable Interrupt (NMI)<br>event.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0 = NMI is serviced by SC140 core<br>1 = NMI is routed to external pin and serviced by<br>the external host                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| <b>ISB</b><br>13–15     | 0     | Initial Internal Space Base Select<br>Defines the initial value of IMMR(ISB[0–14]) and determines the<br>base address of the internal memory space and the DSPRAM<br>base address on the local bus. Note that the SC140 core internal<br>address space spans from 0x0000000–0x00FFFFF (16 MB).<br>Therefore it is not advisable to map the Internal Memory Map<br>Register (IMMR) in this space, since the SC140 core cannot<br>access the registers of the SIU and CPM. QBus banks are<br>mapped to address 0x00F00000, so using ISB value 101 causes<br>the Dual-Port RAM (DPRAM) address space and the QBus<br>address space to overlap. Modifying the QBus Base Registers to<br>another address allows the user to access the DPRAM address<br>space. | ISB         Internal Memory         DSPRAM (Bank           10)         000         0xF000000         0x0200000           001         0xF0F00000         0x0300000           010         0xFF0F00000         0x0300000           011         0xFF00000         0x0500000           010         Reserved         Reserved           101         0x0F00000         0x0700000           110         0x0F00000         0x0800000           111         0x0FF00000         0x0900000           Note: The 2K87M mask adds the DSPRAM location to the areas controlled by these bits. |  |  |

| —<br>16                 | 0     | Reserved. Write to zero for future compatibility.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| BBD<br>17               | 0     | Bus Busy Disable<br>Defines the initial value of SIUMCR[BBD].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| <b>MMR</b><br>18–19     | 0     | Mask Masters Requests<br>Defines the initial value of SIUMCR[MMR].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| <br>20–21               | 0     | Reserved. Write to zero for future compatibility.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| <b>TCPC</b><br>22–23    | 0     | Transfer Code Pin Configuration<br>Defines the initial value of SIUMCR[TCPC].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| BC1PC<br>24–25          | 0     | BC1PC Value<br>Defines the initial value of SIUMCR[BC1PC].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| SWDIS<br>26             | 0     | Software Watchdog Disable<br>Defines the initial state of the Software Watchdog Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <ul> <li>0 = Software Watchdog Timer enabled</li> <li>1 = Software Watchdog Timer disabled</li> <li>Note: This field is undefined in the 2K42A mask set.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| DLLDIS<br>27            | 0     | DLL Disable<br>Defines whether the DLL mechanism is disabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0 = No DLL bypass<br>1 = DLL bypass                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| <b>MODCK_H</b><br>28–30 | 0     | MODCK High Order Bits<br>High-order bits of the MODCK bus, which determine the clock<br>reset configuration.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|                         | 0     | Reserved. Write to zero for future compatibility.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

Table 7. MSC8103 2K87M Mask Set Hard Reset Configuration Word Bit Descriptions (Continued)

# 5 Boot

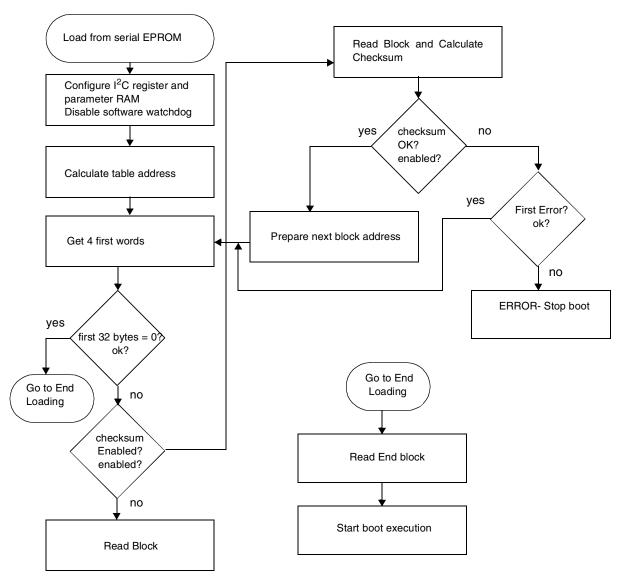

The 2K42A mask set does not support a serial boot mode. The 2K87M mask set supports a serial boot mode with a reduced reset configuration. The following sections describe the serial boot mode operations.

# 5.1 Boot Mode Definition Changes

The boot modes for mask set 2K42A are defined by the values of BTM[0–1] when sampled on the rising edge of PORESET, as follows:

| BTM0 | BTM1 | Boot Source     |

|------|------|-----------------|

| 0    | 0    | External memory |

| 0    | 1    | HDI16           |

| 1    | 0    | Reserved        |

| 1    | 1    | Reserved        |

The boot modes for mask set 2K87M are defined by the values of BTM[0–1] when sampled on the rising edge of PORESET, as follows:

| BTM0 | BTM1 | Boot Source      |

|------|------|------------------|

| 0    | 0    | External memory  |

| 0    | 1    | HDI16            |

| 1    | 0    | Serial interface |

| 1    | 1    | Reserved         |

# 5.2 Serial EPROM Boot Procedure

The MSC8103 core programs the I<sup>2</sup>C registers and parameter RAM and prepares buffers and buffer descriptors (BDs) for the boot loading process. The MSC8103 I<sup>2</sup>C interface is programmed as the master, and it accesses the slave address 0b1010111 to read the boot source code. Booting the MSC8103 through the serial EPROM is useful for systems in which the MSC8103s are connected only through serial interfaces, such as TDM, Ethernet, ATM, and so forth.

**Note:** The bootloader supports access to serial EPROMS with a user-defined device address and 2-byte address specifications.

# 5.3 Software Watchdog Handling

The software watchdog timer can be enabled by clearing the SWDIS bit as part of the reduced reset configuration process. In serial boot mode, if the SWDIS bit is cleared, the bootloader program periodically executes a special service sequence to prevent the time-out of its counter and the assertion of a hardware reset during the bootloading process. For details on the software watchdog, refer to **Section 4.2.5**, *Software Watchdog Timer*, and **Section 4.3**, *SIU Programming Model* in the *MSC8103 Reference Manual*.

Boot

## 5.4 Source Program Data Stream Structure

The source program can be organized into several blocks. Each block can be either a data block or an instruction block, and it can be loaded to a different specified destination. Each block contains the block size, the location where the block is loaded, source program words, checksum, checksum enable and the location from which the next block is loaded.

When each block word is loaded, the routine calculates a checksum by XORing the current word bit by bit with the result of XORing previous words. The value of bit *i* of the current result is equal to XORing bit *i* of the current word with bit *i* of the previous result. After the entire block is loaded, the calculated checksum is compared to the loaded checksum. The checksum comparison and calculation can be skipped by clearing checksum enable bit. The last block is a special block that indicates end of code. It contains the boot execution start address. **Figure 1** shows the stream structure.

Figure 1. Boot Code Stream Structure

## 5.5 Source Program Block Structure

The data stream source programs must be structured in the format shown in Table 8.

| Word               | Description                                                                                  |

|--------------------|----------------------------------------------------------------------------------------------|

| 1                  | Block size + checksum enable bit (see Figure 2 for layout description)                       |

| 2                  | Next block address                                                                           |

| 3                  | Address where the first block of the source program is to be loaded, most significant part   |

| 4                  | Address where the first block of the source program is to be loaded, least significant part  |

| 5                  | First word of source program                                                                 |

| n                  | Last word of source program                                                                  |

| n + 1              | Checksum—xor for first block                                                                 |

| n + 2              | Checksum—xor for first block                                                                 |

| 2nd offset + 1     | Block size + checksum enable bit                                                             |

| 2nd offset + 2     | Next block address                                                                           |

| 2nd offset + 3     | Address where the second block of the source program is to be loaded, most significant part  |

| 2nd offset + 4     | Address where the second block of the source program is to be loaded, least significant part |

| 2nd offset + 5     | First word of source program                                                                 |

| 2nd offset + n     | Last word of source program                                                                  |

| 2nd offset +n + 1  | Checksum—xor for second block                                                                |

| 2nd offset + n + 2 | Checksum—xor for second block                                                                |

Table 8. Block Structure

|             |                  |   |   |   |   |   |   |   |          |   |    |    |    |    |    | Boot |

|-------------|------------------|---|---|---|---|---|---|---|----------|---|----|----|----|----|----|------|

| Bit         | 0                | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8        | 9 | 10 | 11 | 12 | 13 | 14 | 15   |

| Description | CSE <sup>1</sup> |   |   |   |   |   |   | В | lock Siz | e |    |    |    |    |    |      |

**Notes:** 1. CSE = checksum enable. Set this bit when a checksum comparison is needed.

2. Since the EPROMS that support the  $l^2C$  protocol are small, 15 bits are sufficient to define the block size.

#### Figure 2. Checksum Enable Bit + Block Size

In addition, the following rules apply:

- The source data must be in big-endian format, with the most significant part at the lower-order address.

- To enable checksum, set the CSE bit. To disable checksum, clear the CSE bit.

- Block size includes the checksum and checksum.

- Each address must be aligned on a 16-byte boundary.

- Maximum size for a block is 64 KB.

- Checksum is performed on all block words, including addresses and sizes.

- The block size should be a multiple of 32 bits.

- If the next block address is 0x0, the bootloader treats the next block as sequential.

- All addresses should be located in SRAM. The address should be given as a DSP internal address.

The end of the boot code stream is indicated by a special boot end block with the structure shown in Table 9.

|  | Table 9. | Structure of the Boot End Block |

|--|----------|---------------------------------|

|--|----------|---------------------------------|

| Word | Description                                |

|------|--------------------------------------------|

| 1    | 0x0000                                     |

| 2    | 0x0000                                     |

| 3    | Boot start address, most significant part  |

| 4    | Boot start address, least significant part |

| 5    | 0x0000                                     |

| 6    | 0x0000                                     |

| 7    | Checksum—xor                               |

| 8    | Checksum—xor                               |

The first two words indicate the end of the source blocks. At least one block of source code must be loaded when the bootloader is invoked. The boot start address indicates the address at which the boot program execution starts. This address must be aligned on a 16-byte boundary. The bootloader routine expects at least one code block in addition to the boot end block. The sequence is repeated for subsequent blocks, until the final block in the data stream is reached.

## 5.6 Load Procedure

The bootloader program uses the  $I^2C$  serial interface to access data in the EPROM and to program the  $I^2C$  parameter RAM and registers. The  $I^2C$  uses BDs and buffers to read and write data. The bootloader prepares and keeps track of the BDs and buffers for program loading.

To enable multi-master support, the first 14 bytes of the EPROM are reserved for an address table, which is also accessed in single-master mode. The table entries contain the location of the boot code. The loading process starts by calculating the entry address and reading the boot code location address. Then the code loading starts by reading the first 4 block words from the EPROM. The size of block, where to load it, the location of the next block in EPROM, and checksum enable are extracted.

#### Boot

**Note:** The bootloader supports access to serial EPROMs up to 512 KB with an address specification that is accessed by 2 bytes.

The bootloader allocates a buffer for the first code block according to the address and size given in the opening 4 words and creates a BD that describes it. After the BD is ready, the bootloader starts reading the code block from the EPROM. If checksum is enabled, the bootload calculates a checksum on the block word and compares the calculated checksum to the loaded checksum. If the checksum is correct, the bootloader continues to the next block. If the checksum fails, the bootloader tries to read the block again. After a second unsuccessful try, the bootloader aborts.

To skip the checksum comparison, clear the checksum enable bit. If checksum is disabled, the bootloader program continues loading the next code block after finishing the current one. When all code blocks are loaded, boot execution starts from the start address given in the end block.

The bootloader program polls the BDs to check when a code block has been received. It does not use interrupts.

The load procedure is described in Figure 3.

Figure 3. Serial Boot Load Procedure

# 5.7 I<sup>2</sup>C Clocking

The MSC8103 I<sup>2</sup>C interface accesses the serial EPROM using a clock frequency derived by dividing the core frequency by 4000. This division sets the I<sup>2</sup>C clock to 75 KHz or less, a clock frequency that most EPROMs support. If the MSC8103 I<sup>2</sup>C gets an NAK during transmission, that is, the EPROM does not respond to the address asserted by MSC8103, the boot loader stops execution. If the software watchdog timer is enabled, the counter will eventually expire causing a system reset. After reset, the bootloading process restarts.

# 5.8 Reset Configuration Word

The only reset configuration mode that can be used while serial boot mode is enabled is reduced configuration word. In the reduced configuration word, only the NMI\_OUT, ISB, SWDIS, and DLLDIS fields can be set. For details, see **Section 4.1.2**.

# 5.9 Default Programming During Boot

The bootloader routine provides default programming for parts of the MSC8103. The routine programs the UPMC and the GPCM as required to support the internal SRAM and peripherals. The UPMC is programmed to support the bus-to-CPM clock ratio. The routine checks the value of the SCMR[BUSDF] bits and selects the bus-to-CPM clock ratio. The routine also programs the correct values for the ELIR[A–F] registers in the programmable interrupt controller (PIC) to determine the interrupt mode (edge-triggered or level-triggered).

# 5.10 Multi-Processor Booting from a Serial EPROM

The I<sup>2</sup>C protocol supports multi-master environments. All MSC8103 booting devices act as I<sup>2</sup>C masters and try to access the serial EPROM. The first 14 bytes of the serial EPROM are reserved for an address table. Each master accesses a different entry in the table according to its ISB[0–2] bits in the IMMR, allowing seven I<sup>2</sup>C masters in the system. Each entry in the table contains the actual address where the boot program resides in the 2-byte increments. The master accesses the table, reads the boot location address, and starts loading boot from there. If two or more masters try to put information onto the bus, the first to produce a 1 when another produces a 0 loses the arbitration (collision). If a collision occurs, the master that loses the arbitration retries.

**Note:** If there are less than seven masters and not all 14 bytes of the table are needed, the boot code can start inside the first 14 bytes of the table.

A MSC8103  $I^2C$  master should access a table entry equal to its ISB[0–2] value multiplied by two. The bootloading process always starts by accessing the address table. In a single master environment, the boot code may start immediately after the address entry.

**Note:** During the booting process, multiple masters should not address each other. There is no support for multimaster errors.

# 5.11 Boot Code Changes

The boot code for the 2K87M mask set supports the  $I^2C$  protocol. In addition, the code reflects changes in the device design that fix a host checksum errata, make the SRAM base address ISB dependent, and allow the software watchdog timer to be enabled or disabled via software. For a detailed listing of the updated boot code, see **Appendix A**.

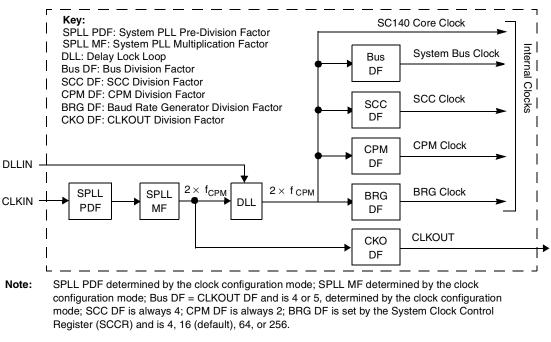

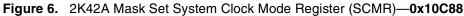

# 6.1 Clock Scheme Modifications

The MSC8101 mask set 2K42A and the MSC8103 mask set 2K87M use different clock schemes. The following paragraphs describe the clock schemes.

## 6.1.1 Mask Set 2K42A Clock Scheme

Six bit values map the MSC8101 clocks to one of the valid configuration mode options. Each option determines the CLKIN, SC140 core, system bus, SCC clock, CPM, and CLKOUT frequencies. The six bit values are derived from three dedicated input pins (MODCK[1–3]) and three bits from the reset configuration word (MODCK\_H). To configure the SPLL pre-division factor, SPLL multiplication factor, and the frequencies for the SC140 core, SCC clocks, CPM parallel I/O ports, and system buses, the MODCK[1–3] pins are sampled and combined with the MODCK\_H values when the internal power-on reset (internal PORESET) is deasserted. Clock configuration changes only when the internal PORESET signal is deasserted.

The following factors are configured:

- SPLL pre-division factor (SPLL PDF)

- SPLL multiplication factor (SPLL MF)

- Bus post-division factor (Bus DF)

**Figure 4** shows the functional block diagram for the 2K42A mask set. The 2K42A mask set contains an internal system phase-lock loop (SPLL)

Figure 4. MSC8101 Clock Functional Block Diagram for 2K42A Mask Set

The SCC division factor (SCC DF) is fixed at 4 and the CPM division factor (CPM DF) is fixed at 2. The BRG division factor (BRG DF) is configured through the System Clock Control Register (SCCR) and can be 4, 16 (default after reset), 64, or 256.

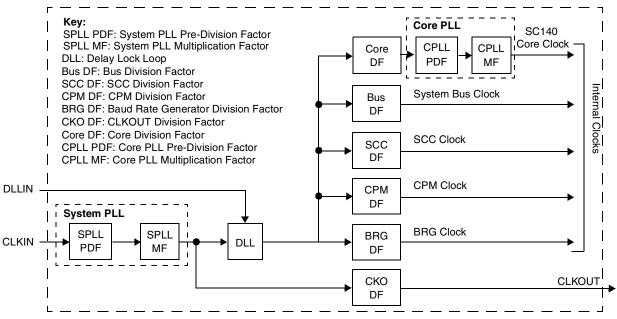

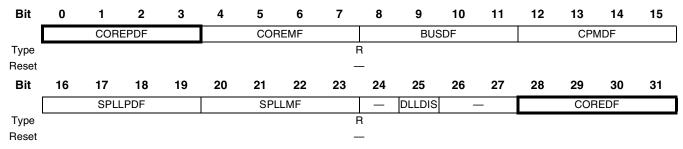

## 6.1.2 Mask Set 2K87M Clock Scheme

Six bit values map the MSC8101 clocks to one of the valid configuration mode options. Each option determines the CLKIN, SC140 core, system bus, SCC clock, CPM, and CLKOUT frequencies. The six bit values are derived from three dedicated input pins (MODCK[1–3]) and three bits from the hard reset configuration word (MODCK\_H). To configure the SPLL pre-division factor, SPLL multiplication factor, and the frequencies for the SC140 core, SCC clocks, CPM parallel I/O ports, and system buses, the MODCK[1–3] pins are sampled and combined with the MODCK\_H values when the internal power-on reset (internal PORESET) is deasserted. Clock configuration changes only when the internal PORESET signal is deasserted.

The following factors are configured:

- SPLL pre-division factor (SPLL PDF)

- SPLL multiplication factor (SPLL MF)

- Bus post-division factor (Bus DF)

- CPM division factor (CPM DF)

- Core division factor (Core DF)

- CPLL pre-division factor (CPLL PDF)

- CPLL multiplication factor (CPLL MF)

**Figure 5** shows the functional block diagram for the 2K87M mask set. The 2K87M mask set contains an internal system phase-lock loop (SPLL) and a core phase-lock loop (CPLL).

Figure 5. MSC8103 Clock Functional Block Diagram for 2K87M Mask Set

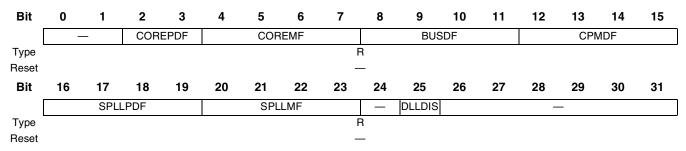

# 6.2 System Clock Mode Register (SCMR) Changes

The 2K42A and 2K87M mask sets use different SCMR definitions. The following sections describe the SCMR definitions for each mask set.

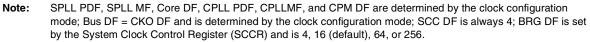

## 6.2.1 2K42A Mask Set SCMR Field Definitions

SCMR is a read-only register that is updated during power-on reset (PORESET) and provides the mode control signals to the PLLs, DLL, and clock logic. This register reflects the currently defined configuration settings.

| Name                    | Defa                  | ults       | Description                  | Sottingo                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------------------|-----------------------|------------|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit No.                 | PORESET               | Hard Reset | Description                  | Settings                                                                                                                                                                                                                                                                                                                                                                                                |

| 0–1                     | _                     | _          | Reserved                     |                                                                                                                                                                                                                                                                                                                                                                                                         |

| COREPDF<br>2–3          | Configuration<br>Pins | Unaffected | Core PLL Pre-Division Factor | Not used.                                                                                                                                                                                                                                                                                                                                                                                               |

| COREMF<br>4–7           | Configuration<br>Pins | Unaffected | Core Multiplication Factor   | Not used                                                                                                                                                                                                                                                                                                                                                                                                |

| BUSDF<br>8–11           | Configuration<br>Pins | Unaffected | 60x Bus Division Factor      | 0010         Bus DF = 3           0011         Bus DF = 4           0100         Bus DF = 5           All other combinations not used.                                                                                                                                                                                                                                                                  |

| <b>CPMDF</b><br>12–15   | Configuration<br>Pins | Unaffected | CPM Division Factor          | 0001 CPM DF = 2<br>All other combinations are not used.                                                                                                                                                                                                                                                                                                                                                 |

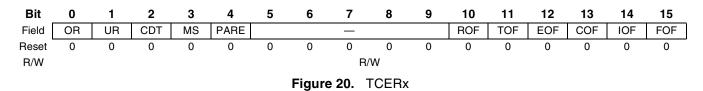

| <b>SPLLPDF</b><br>16–19 | Configuration<br>Pins | Unaffected | SPLL Pre-Division Factor     | 0000         SPLL PDF = 1           0001         SPLL PDF = 2           0010         SPLL PDF = 3           0011         SPLL PDF = 4           All other combinations not used                                                                                                                                                                                                                         |