DS91M040 125 MHz Quad M-LVDS Transceiver

# DS91M040 125 MHz Quad M-LVDS Transceiver

#### **General Description**

The DS91M040 is a quad M-LVDS transceiver designed for driving / receiving clock or data signals to / from up to four multipoint networks.

M-LVDS (Multipoint LVDS) is a new family of bus interface devices based on LVDS technology specifically designed for multipoint and multidrop cable and backplane applications. It differs from standard LVDS in providing increased drive current to handle double terminations that are required in multipoint applications. Controlled transition times minimize reflections that are common in multipoint configurations due to unterminated stubs. M-LVDS devices also have a very large input common mode voltage range for additional noise margin in heavily loaded and noisy backplane environments.

A single DS91M040 channel is a half-duplex transceiver that accepts LVTTL/LVCMOS signals at the driver inputs and converts them to differential M-LVDS signal levels. The receiver inputs accept low voltage differential signals (LVDS, BLVDS, M-LVDS, LVPECL and CML) and convert them to 3V LVC-MOS signals. The DS91M040 supports both M-LVDS type 1 and type 2 receiver inputs.

#### Features

- DC 125 MHz / 250 Mbps low jitter, low skew, low power operation

- Wide Input Common Mode Voltage Range allows up to ±2V of GND noise

- Conforms to TIA/EIA-899 M-LVDS Standard

- Pin selectable M-LVDS receiver type (1 or 2)

- Controlled transition times (2.0 ns typ) minimize reflections

- 8 kV ESD on M-LVDS I/O pins protects adjoining components

- Flow-through pinout simplifies PCB layout

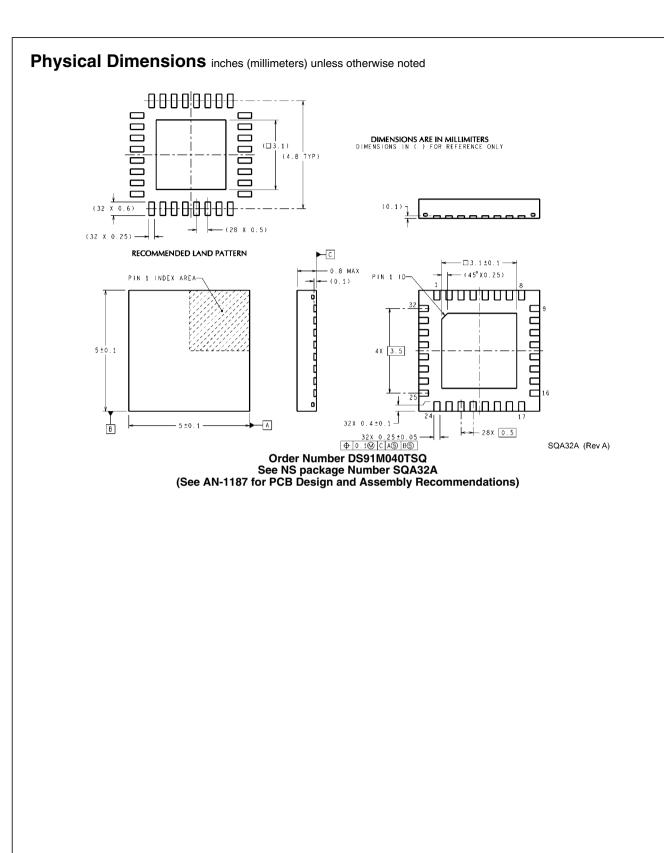

- Small 5 mm x 5 mm LLP-32 space saving package

#### Applications

- Multidrop / Multipoint clock and data distribution

- High-Speed, Low Power, Short-Reach alternative to TIA/ EIA-485/422

- Clock distribution in AdvancedTCA (ATCA) and MicroTCA (µTCA) backplanes

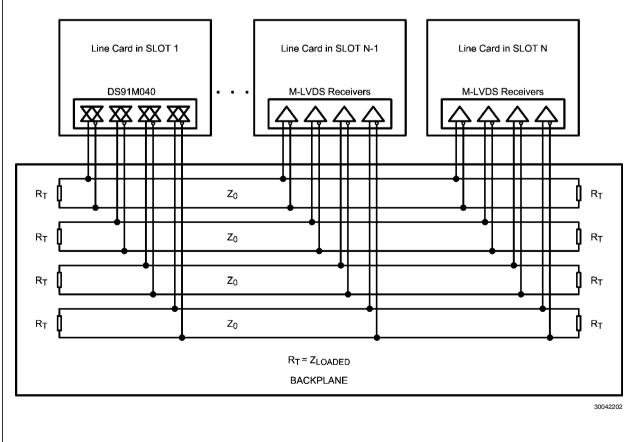

# **Typical Application**

# **Ordering Information**

| Order Number | <b>Receiver Input</b> | Function                | Package Type |

|--------------|-----------------------|-------------------------|--------------|

| DS91M040TSQ  | Type 1 or 2           | Quad M-LVDS Transciever | LLP-32       |

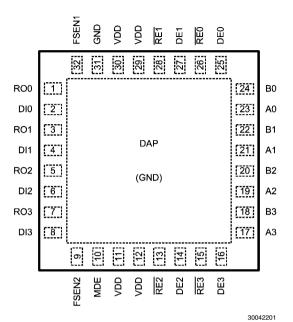

# **Connection Diagram**

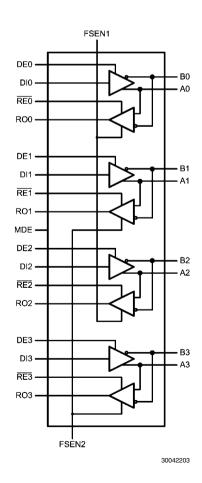

# Logic Diagram

#### **Pin Descriptions**

| Number         | Name            | I/O, Type   | Description                                                                                                                                                                                  |

|----------------|-----------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 3, 5, 7     | RO              | O, LVCMOS   | Receiver output pin.                                                                                                                                                                         |

| 26, 28, 13, 15 | RE              | I, LVCMOS   | Receiver enable pin: When $\overline{RE}$ is high, the receiver is disabled.<br>When $\overline{RE}$ is low, the receiver is enabled. There is a 300 k $\Omega$ pullup resistor on this pin. |

| 25, 27, 14, 16 | DE              | I, LVCMOS   | Driver enable pin: When DE is low, the driver is disabled. When DE is high, the driver is enabled. There is a 300 k $\Omega$ pulldown resistor on this pin.                                  |

| 2, 4, 6, 8     | DI              | I, LVCMOS   | Driver input pin.                                                                                                                                                                            |

| 31, DAP        | GND             | Power       | Ground pin and pad.                                                                                                                                                                          |

| 17, 19, 21, 23 | А               | I/O, M-LVDS | Non-inverting driver output pin/Non-inverting receiver input pin                                                                                                                             |

| 18, 20, 22, 24 | В               | I/O, M-LVDS | Inverting driver output pin/Inverting receiver input pin                                                                                                                                     |

| 11, 12, 29, 30 | V <sub>DD</sub> | Power       | Power supply pin, +3.3V ± 0.3V                                                                                                                                                               |

| 32             | FSEN1           | I, LVCMOS   | Failsafe enable pin with a 300 k $\Omega$ pullup resistor. This pin<br>enables Type 2 receiver on inputs 0 and 2.<br>FSEN1 = L> Type 1 receiver inputs<br>FSEN1 = H> Type 2 receiver inputs  |

| 9              | FSEN2           | I, LVCMOS   | Failsafe enable pin with a 300 k $\Omega$ pullup resistor. This pin<br>enables Type 2 receiver on inputs 1 and 3.<br>FSEN2 = L> Type 1 receiver inputs<br>FSEN2 = H> Type 2 receiver inputs  |

| 10             | MDE             | I, LVCMOS   | Master enable pin. When MDE is H, the device is powered up.<br>When MDE is L, the device overrides all other control and powers<br>down.                                                     |

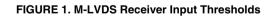

#### **M-LVDS Receiver Types**

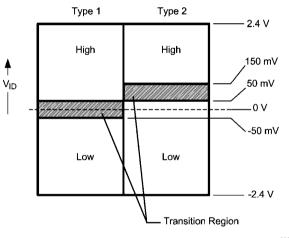

The EIA/TIA-899 M-LVDS standard specifies two different types of receiver input stages. A type 1 receiver has a conventional threshold that is centered at the midpoint of the input amplitude,  $V_{ID}/2$ . A type 2 receiver has a built in offset that is 100mV greater then  $V_{ID}/2$ . The type 2 receiver offset acts as a failsafe circuit where open or short circuits at the input will always result in the output stage being driven to a low logic state.

30042240

### Absolute Maximum Ratings (Note 4)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| Power Supply Voltage        | -0.3V to +4V                      |

|-----------------------------|-----------------------------------|

| LVCMOS Input Voltage        | -0.3V to (V <sub>DD</sub> + 0.3V) |

| LVCMOS Output Voltage       | -0.3V to (V <sub>DD</sub> + 0.3V) |

| M-LVDS I/O Voltage          | -5.5V to +5.5V                    |

| M-LVDS Output Short Circuit |                                   |

| Current Duration            | Continuous                        |

| Junction Temperature        | +140°C                            |

| Storage Temperature Range   | -65°C to +150°C                   |

| Lead Temperature Range      |                                   |

| Soldering (4 sec.)          | +260°C                            |

| Maximum Package Power Dissi | pation @ +25°C                    |

| SQ Package                  | 833 mW                            |

| Derate SQ Package           | 6.67  mW/°C above +25°C           |

| Package Thermal Resistance  |                                   |

| $\theta_{JA}$               | +150°C/W                          |

| $\theta_{JC}$               | +63.8°C/W                         |

|                             |                                   |

| ESD Susceptibility |        |

|--------------------|--------|

| HBM (Note 1)       | ≥8 kV  |

| MM (Note 2)        | ≥250V  |

| CDM (Note 3)       | ≥1250V |

Note 1: Human Body Model, applicable std. JESD22-A114C Note 2: Machine Model, applicable std. JESD22-A115-A Note 3: Field Induced Charge Device Model, applicable std. JESD22-C101-C

# Recommended Operating Conditions

|                                            | Min  | Тур | Max      | Units |

|--------------------------------------------|------|-----|----------|-------|

| Supply Voltage, V <sub>DD</sub>            | 3.0  | 3.3 | 3.6      | V     |

| Voltage at Any Bus Terminal                | -1.4 |     | +3.8     | V     |

| (Separate or Common-Mode)                  |      |     |          |       |

| Differential Input Voltage V <sub>ID</sub> |      |     | 2.4      | V     |

| LVTTL Input Voltage High V <sub>IH</sub>   | 2.0  |     | $V_{DD}$ | V     |

| LVTTL Input Voltage Low $V_{IL}$           | 0    |     | 0.8      | V     |

| Operating Free Air                         |      |     |          |       |

| Temperature T <sub>A</sub>                 | -40  | +25 | +85      | °C    |

### DC Electrical Characteristics (Notes 5, 6, 7, 9)

Over recommended operating supply and temperature ranges unless otherwise specified.

| Symbol               | Parameter                                                              | Conditions                                                |        | Min                     | Тур  | Max                | Units |

|----------------------|------------------------------------------------------------------------|-----------------------------------------------------------|--------|-------------------------|------|--------------------|-------|

| M-LVDS D             | river                                                                  |                                                           |        |                         |      |                    |       |

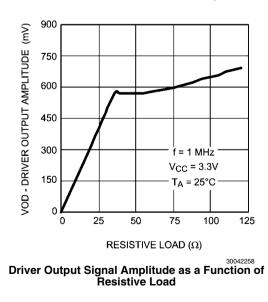

| IV <sub>AB</sub> I   | Differential output voltage magnitude                                  | $R_{L} = 50\Omega, C_{L} = 5 \text{ pF}$                  |        | 480                     |      | 650                | mV    |

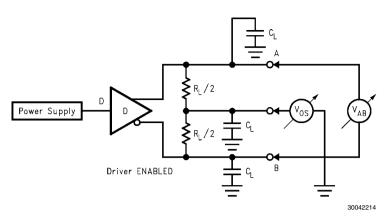

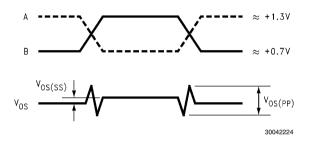

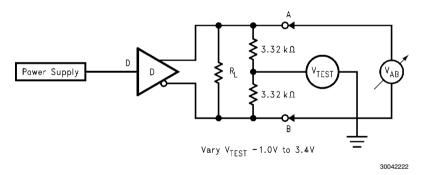

| $\Delta V_{AB}$      | Change in differential output voltage magnitude between logic states   | Figures 2, 4                                              |        | -50                     | 0    | +50                | mV    |

| V <sub>OS(SS)</sub>  | Steady-state common-mode output voltage                                | $R_{L} = 50\Omega, C_{L} = 5 \text{ pF}$                  |        | 0.3                     | 1.6  | 2.1                | V     |

| ΔV <sub>OS(SS)</sub> | Change in steady-state common-mode output voltage between logic states | Figures 2, 3                                              | 0      |                         | +50  | mV                 |       |

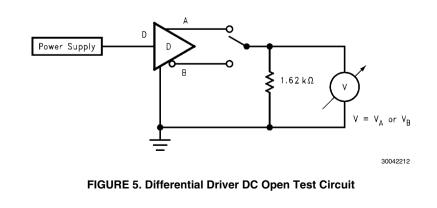

| V <sub>A(OC)</sub>   | Maximum steady-state open-circuit output voltage                       | Figure 5                                                  |        | 0                       |      | 2.4                | V     |

| V <sub>B(OC)</sub>   | Maximum steady-state open-circuit output voltage                       |                                                           |        | 0                       |      | 2.4                | V     |

| V <sub>P(H)</sub>    | Voltage overshoot, low-to-high level output (Note 12)                  | $R_L = 50\Omega, C_L = 5pF, C_D = 0.5 pF$<br>Figures 7, 8 |        |                         |      | 1.2V <sub>SS</sub> | V     |

| V <sub>P(L)</sub>    | Voltage overshoot, high-to-low level output<br>(Note 12)               |                                                           |        | -0.2V <sub>S</sub><br>s |      |                    | V     |

| I <sub>IH</sub>      | High-level input current (LVTTL inputs)                                | V <sub>IH</sub> = 2.0V                                    |        | -15                     |      | 15                 | μA    |

| I <sub>IL</sub>      | Low-level input current (LVTTL inputs)                                 | V <sub>IL</sub> = 0.8V                                    |        | -15                     |      | 15                 | μA    |

| V <sub>CL</sub>      | Input Clamp Voltage (LVTTL inputs)                                     | I <sub>IN</sub> = -18 mA                                  |        | -1.5                    |      |                    | V     |

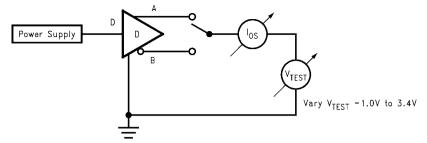

| I <sub>os</sub>      | Differential short-circuit output current (Note 8)                     | Figure 6                                                  |        | -43                     |      | 43                 | mA    |

| M-LVDS R             | eceiver                                                                |                                                           |        |                         |      |                    |       |

| V <sub>IT+</sub>     | Positive-going differential input voltage threshold                    | See Function Tables Type 1<br>Type 2                      |        |                         | 16   | 50                 | mV    |

|                      |                                                                        |                                                           |        |                         | 100  | 150                | mV    |

| V <sub>IT-</sub>     | Negative-going differential input voltage threshold                    | See Function Tables                                       | Type 1 | -50                     | 20   |                    | mV    |

|                      |                                                                        |                                                           | Type 2 | 50                      | 94   |                    | mV    |

| V <sub>OH</sub>      | High-level output voltage (LVTTL output)                               | I <sub>OH</sub> = -8mA                                    |        | 2.4                     | 2.7  |                    | V     |

| V <sub>OL</sub>      | Low-level output voltage (LVTTL output)                                | I <sub>OL</sub> = 8mA                                     |        |                         | 0.28 | 0.4                | V     |

| I <sub>oz</sub>      | TRI-STATE output current                                               | V <sub>O</sub> = 0V or 3.6V                               |        | -10                     |      | 10                 | μA    |

| I <sub>OSR</sub>     | Short-circuit receiver output current (LVTTL output)                   | $V_{O} = 0V$                                              |        |                         | -50  | -90                | mA    |

www.national.com

| Symbol               | Parameter                                                                           | Conditions                                                       | Min | Тур | Max | Units |

|----------------------|-------------------------------------------------------------------------------------|------------------------------------------------------------------|-----|-----|-----|-------|

| M-LVDS B             | Bus (Input and Output) Pins                                                         | •                                                                | I   |     |     |       |

| I <sub>A</sub>       | Transceiver input/output current                                                    | V <sub>A</sub> = 3.8V, V <sub>B</sub> = 1.2V                     |     |     | 32  | μA    |

|                      |                                                                                     | V <sub>A</sub> = 0V or 2.4V, V <sub>B</sub> = 1.2V               | -20 |     | +20 | μA    |

|                      |                                                                                     | $V_{A} = -1.4V, V_{B} = 1.2V$                                    | -32 |     |     | μA    |

| I <sub>B</sub>       | Transceiver input/output current                                                    | V <sub>B</sub> = 3.8V, V <sub>A</sub> = 1.2V                     |     |     | 32  | μA    |

|                      |                                                                                     | $V_{B} = 0V \text{ or } 2.4V, V_{A} = 1.2V$                      | -20 |     | +20 | μA    |

|                      |                                                                                     | $V_{B} = -1.4V, V_{A} = 1.2V$                                    | -32 |     |     | μA    |

| I <sub>AB</sub>      | Transceiver input/output differential current $(I_A - I_B)$                         | $V_{A} = V_{B}, -1.4V \le V \le 3.8V$                            | -4  |     | +4  | μA    |

| I <sub>A(OFF)</sub>  | Transceiver input/output power-off current                                          | $V_A = 3.8V, V_B = 1.2V,$<br>DE = V <sub>CC</sub> = 1.5V         |     |     | 32  | μA    |

|                      |                                                                                     | $V_A = 0V \text{ or } 2.4V, V_B = 1.2V,$<br>DE = $V_{CC} = 1.5V$ | -20 |     | +20 | μA    |

|                      |                                                                                     | $V_A = -1.4V, V_B = 1.2V,$<br>DE = $V_{CC} = 1.5V$               | -32 |     |     | μA    |

| I <sub>B(OFF)</sub>  | Transceiver input/output power-off current                                          | $V_B = 3.8V, V_A = 1.2V,$<br>DE = V <sub>CC</sub> = 1.5V         |     |     | 32  | μA    |

|                      |                                                                                     | $V_B = 0V \text{ or } 2.4V, V_A = 1.2V,$<br>DE = $V_{CC} = 1.5V$ | -20 |     | +20 | μA    |

|                      |                                                                                     | $V_B = -1.4V, V_A = 1.2V,$<br>DE = V <sub>CC</sub> = 1.5V        | -32 |     |     | μA    |

| I <sub>AB(OFF)</sub> | Transceiver input/output power-off differential current $(I_{A(OFF)} - I_{B(OFF)})$ | $V_A = V_B, -1.4V \le V \le 3.8V,$<br>$V_{DD} = 1.5V, DE = 1.5V$ | -4  |     | +4  | μA    |

| C <sub>A</sub>       | Transceiver input/output capacitance                                                | V <sub>DD</sub> = OPEN                                           |     | 7.8 |     | pF    |

| C <sub>B</sub>       | Transceiver input/output capacitance                                                |                                                                  |     | 7.8 |     | pF    |

| C <sub>AB</sub>      | Transceiver input/output differential capacitance                                   |                                                                  |     | 3   |     | pF    |

| C <sub>A/B</sub>     | Transceiver input/output capacitance balance ( $C_A/C_B$ )                          |                                                                  |     | 1   |     |       |

| SUPPLY C             | CURRENT (V <sub>cc</sub> )                                                          |                                                                  |     |     |     |       |

| I <sub>CCD</sub>     | Driver Supply Current                                                               | $R_L = 50\Omega$ , DE = H, $\overline{RE} = H$                   |     | 67  | 75  | mA    |

| I <sub>ccz</sub>     | TRI-STATE Supply Current                                                            | $DE = L, \overline{RE} = H$                                      |     | 22  | 26  | mA    |

| I <sub>CCR</sub>     | Receiver Supply Current                                                             | $DE = L, \overline{RE} = L$                                      |     | 32  | 38  | mA    |

| ICCPD                | Power Down Supply Current                                                           | MDE = L                                                          |     | 3   | 5   | mA    |

Note 4: "Absolute Maximum Ratings" indicate limits beyond which damage to the device may occur, including inoperability and degradation of device reliability and/or performance. Functional operation of the device and/or non-degradation at the Absolute Maximum Ratings or other conditions beyond those indicated in the Recommended Operating Conditions is not implied. The Recommended Operating Conditions indicate conditions at which the device is functional and the device should not be operated beyond such conditions.

Note 5: The Electrical Characteristics tables list guaranteed specifications under the listed Recommended Operating Conditions except as otherwise modified or specified by the Electrical Characteristics Conditions and/or Notes. Typical specifications are estimations only and are not guaranteed.

Note 6: Current into device pins is defined as positive. Current out of device pins is defined as negative. All voltages are referenced to ground except  $V_{OD}$  and  $\Delta V_{OD}$ .

Note 7: Typical values represent most likely parametric norms for  $V_{DD}$  = +3.3V and  $T_A$  = +25°C, and at the Recommended Operation Conditions at the time of product characterization and are not guaranteed.

Note 8: Output short circuit current (I<sub>OS</sub>) is specified as magnitude only, minus sign indicates direction only.

Note 9: C<sub>L</sub> includes fixture capacitance and C<sub>D</sub> includes probe capacitance.

www.national.com

#### Switching Characteristics (Notes 10, 11, 17)

Over recommended operating supply and temperature ranges unless otherwise specified.

|                    | mended operating supply and temperature ran |                                            |     |      |      |       |

|--------------------|---------------------------------------------|--------------------------------------------|-----|------|------|-------|

| Symbol             | Parameter                                   | Conditions                                 | Min | Тур  | Max  | Units |

| DRIVER AC S        | SPECIFICATIONS                              | 1                                          |     |      |      |       |

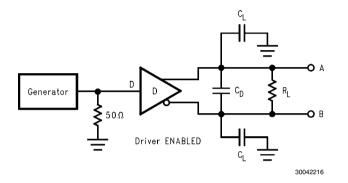

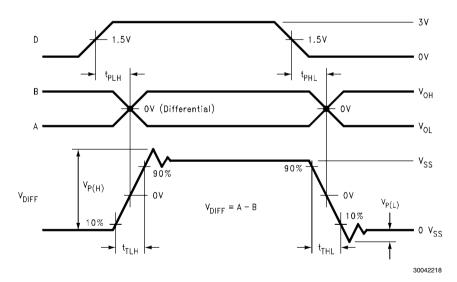

| t <sub>PLH</sub>   | Differential Propagation Delay Low to High  | $R_{L} = 50\Omega, C_{L} = 5 \text{ pF},$  | 1.5 | 3.3  | 5.5  | ns    |

| t <sub>PHL</sub>   | Differential Propagation Delay High to Low  | $C_{\rm D} = 0.5  \rm pF$                  | 1.5 | 3.3  | 5.5  | ns    |

| t <sub>SKD1</sub>  | Pulse Skew (Notes 12, 13)                   | Figures 7, 8                               |     | 30   | 125  | ps    |

| t <sub>SKD2</sub>  | Channel-to-Channel Skew (Notes 12, 14)      |                                            |     | 100  | 200  | ps    |

| t <sub>SKD3</sub>  | Part-to-Part Skew (Notes 12, 15)            |                                            |     | 0.8  | 1.6  | ns    |

| t <sub>SKD4</sub>  | Part-to-Part Skew (Notes 12, 16)            |                                            |     |      | 4    | ns    |

| t <sub>TLH</sub>   | Rise Time (Note 12)                         |                                            | 1.2 | 2.0  | 3.0  | ns    |

| t <sub>THL</sub>   | Fall Time (Note 12)                         |                                            | 1.2 | 2.0  | 3.0  | ns    |

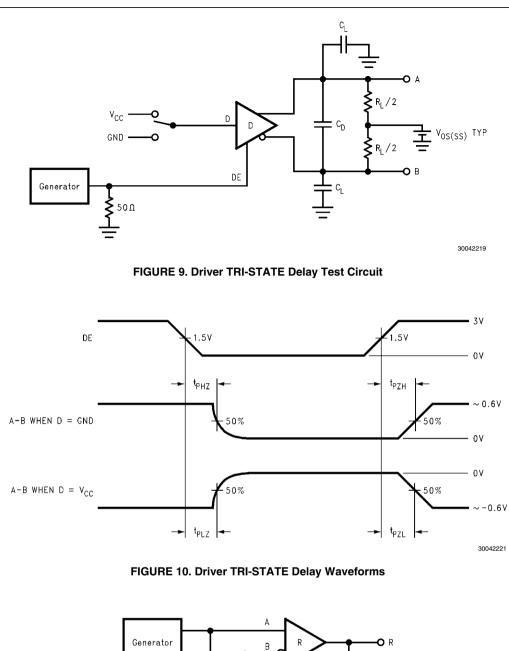

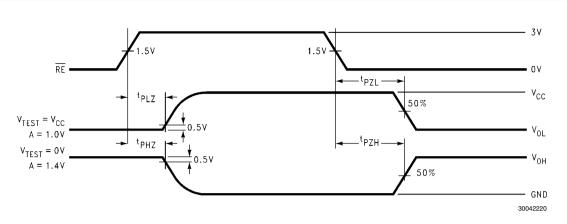

| t <sub>PZH</sub>   | Enable Time (Z to Active High)              | $R_{L} = 50\Omega, C_{L} = 5 \text{ pF},$  |     | 7.5  | 11.5 | ns    |

| t <sub>PZL</sub>   | Enable Time (Z to Active Low )              | C <sub>D</sub> = 0.5 pF                    |     | 8.0  | 11.5 | ns    |

| t <sub>PLZ</sub>   | Disable Time (Active Low to Z)              | Figures 9, 10                              |     | 7.0  | 11.5 | ns    |

| t <sub>PHZ</sub>   | Disable Time (Active High to Z)             |                                            |     | 7.0  | 11.5 | ns    |

| <b>RECEIVER A</b>  | C SPECIFICATIONS                            |                                            |     |      |      |       |

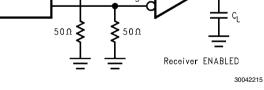

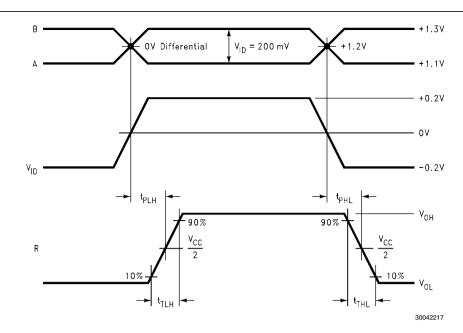

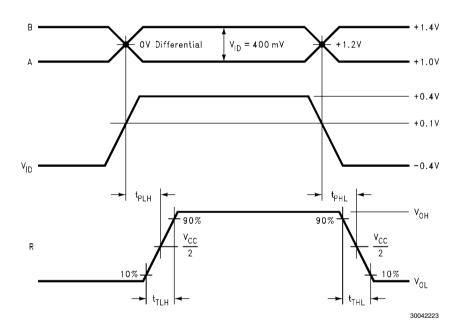

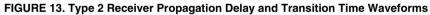

| t <sub>PLH</sub>   | Propagation Delay Low to High               | C <sub>L</sub> = 15 pF                     | 1.5 | 3.0  | 4.5  | ns    |

| t <sub>PHL</sub>   | Propagation Delay High to Low               | Figures 11, 12, 13                         | 1.5 | 3.1  | 4.5  | ns    |

| t <sub>SKD1A</sub> | Pulse Skew (Receiver Type 1)                |                                            |     | 55   | 325  | ps    |

|                    | (Notes 12, 13)                              |                                            |     |      |      |       |

| t <sub>SKD1B</sub> | Pulse Skew (Receiver Type 2)                |                                            |     | 475  | 800  | ps    |

|                    | (Notes 12, 13)                              | _                                          |     |      |      |       |

| t <sub>SKD2</sub>  | Channel-to-Channel Skew (Notes 12, 14)      | _                                          |     | 60   | 300  | ps    |

| t <sub>SKD3</sub>  | Part-to-Part Skew (Notes 12, 15)            | _                                          |     | 0.6  | 1.2  | ns    |

| t <sub>SKD4</sub>  | Part-to-Part Skew (Notes 12, 16)            | _                                          |     |      | 3    | ns    |

| t <sub>TLH</sub>   | Rise Time (Note 12)                         | _                                          | 0.3 | 1.1  | 1.6  | ns    |

| t <sub>THL</sub>   | Fall Time (Note 12)                         |                                            | 0.3 | 0.65 | 1.6  | ns    |

| t <sub>PZH</sub>   | Enable Time (Z to Active High)              | $R_{L} = 500\Omega, C_{L} = 15 \text{ pF}$ |     | 3    | 5.5  | ns    |

| t <sub>PZL</sub>   | Enable Time (Z to Active Low)               | Figures 14, 15                             |     | 3    | 5.5  | ns    |

| t <sub>PLZ</sub>   | Disable Time (Active Low to Z)              |                                            |     | 3.5  | 5.5  | ns    |

| t <sub>PHZ</sub>   | Disable Time (Active High to Z)             |                                            |     | 3.5  | 5.5  | ns    |

| GENERIC AC         | SPECIFICATIONS                              | i                                          |     |      |      |       |

| t <sub>WKUP</sub>  | Wake Up Time (Note 12)                      |                                            |     |      | 500  | ms    |

|                    | (Master Device Enable (MDE) time)           |                                            |     |      |      |       |

| f <sub>MAX</sub>   | Maximum Operating Frequency (Note 12)       |                                            | 125 |      |      | MHz   |

Note 10: The Electrical Characteristics tables list guaranteed specifications under the listed Recommended Operating Conditions except as otherwise modified or specified by the Electrical Characteristics Conditions and/or Notes. Typical specifications are estimations only and are not guaranteed.

Note 11: Typical values represent most likely parametric norms for  $V_{DD}$  = +3.3V and  $T_A$  = +25°C, and at the Recommended Operation Conditions at the time of product characterization and are not guaranteed.

Note 12: Specification is guaranteed by characterization and is not tested in production.

Note 13: t<sub>SKD1</sub>, It<sub>PLHD</sub> – t<sub>PHLD</sub>I, Pulse Skew, is the magnitude difference in differential propagation delay time between the positive going edge and the negative going edge of the same channel.

Note 14:  $t_{SKD2}$ , Channel-to-Channel Skew, is the difference in propagation delay ( $t_{PLHD}$  or  $t_{PHLD}$ ) among all output channels.

Note 15: t<sub>SKD3</sub>, Part-to-Part Skew, is defined as the difference between the minimum and maximum differential propagation delays. This specification applies to devices at the same V<sub>DD</sub> and within 5°C of each other within the operating temperature range.

**Note 16:**  $t_{SKD4}$ , Part-to-Part Skew, is the differential channel-to-channel skew of any event between devices. This specification applies to devices over recommended operating temperature and voltage ranges, and across process distribution.  $t_{SKD4}$  is defined as IMax – MinI differential propagation delay. **Note 17:**  $C_1$  includes fixture capacitance and  $C_p$  includes probe capacitance.

Note 18: Measured on a clock edge with a histogram and an acummulation of 1500 histogram hits. Input stimulus jitter is subracted geometrically.

#### **Test Circuits and Waveforms**

FIGURE 4. Differential Driver Full Load Test Circuit

30042225

FIGURE 6. Differential Driver Short-Circuit Test Circuit

FIGURE 7. Driver Propagation Delay and Transition Time Test Circuit

FIGURE 8. Driver Propagation Delays and Transition Time Waveforms

www.national.com

FIGURE 12. Type 1 Receiver Propagation Delay and Transition Time Waveforms

FIGURE 14. Receiver TRI-STATE Delay Test Circuit

FIGURE 15. Receiver TRI-STATE Delay Waveforms

#### **Truth Tables**

#### DS91M040 Transmitting

|    | Inputs | Out | puts |   |

|----|--------|-----|------|---|

| RE | DE     | DI  | В    | Α |

| Х  | н      | Н   | L    | Н |

| Х  | н      | L   | н    | L |

| Х  | L      | Х   | Z    | Z |

#### X — Don't care condition

Z — High impedance state

#### DS91M040 as Type 1 Receiving

|      | Inputs |    |          |    |  |  |  |

|------|--------|----|----------|----|--|--|--|

| FSEN | RE     | DE | A – B    | RO |  |  |  |

| L    | L      | L  | ≥ +0.05V | Н  |  |  |  |

| L    | L      | L  | ≤ -0.05V | L  |  |  |  |

| L    | L      | L  | 0V       | Х  |  |  |  |

| L    | Н      | L  | Х        | Z  |  |  |  |

#### DS91M040 as Type 2 Receiving

|      | Inputs |    |          |   |  |  |  |  |

|------|--------|----|----------|---|--|--|--|--|

| FSEN | RE     | DE | A – B    | R |  |  |  |  |

| Н    | L      | L  | ≥ +0.15V | Н |  |  |  |  |

| н    | L      | L  | ≤ +0.05V | L |  |  |  |  |

| н    | L      | L  | 0V       | L |  |  |  |  |

| Н    | н      | L  | Х        | Z |  |  |  |  |

X — Don't care condition

Z — High impedance state

χ. - Don't care condition Z — High impedance state

#### DS91M040 Type 1 Receiver Input Threshold Test Voltages

| Applied         | Voltages        | Resulting Differential Input<br>Voltage | Resulting Common-Mode<br>Input Voltage | Receiver<br>Output |

|-----------------|-----------------|-----------------------------------------|----------------------------------------|--------------------|

| V <sub>IA</sub> | V <sub>IB</sub> | V <sub>ID</sub>                         | V <sub>ICM</sub>                       | R                  |

| 2.400V          | 0.000V          | 2.400V                                  | 1.200V                                 | Н                  |

| 0.000V          | 2.400V          | -2.400V                                 | 1.200V                                 | L                  |

| 3.800V          | 3.750V          | 0.050V                                  | 3.775V                                 | н                  |

| 3.750V          | 3.800V          | -0.050V                                 | 3.775V                                 | L                  |

| -1.350V         | -1.400V         | 0.050V                                  | -1.375V                                | Н                  |

| -1.400V         | -1.350V         | –0.050V                                 | –1.375V                                | L                  |

H — High Level L — Low Level

Output state assumes that the receiver is enabled ( $\overline{RE} = L$ )

#### DS91M040 Type 2 Receiver Input Threshold Test Voltages

| Applied Voltages |                 | Resulting Differential Input<br>Voltage | Resulting Common-Mode<br>Input Voltage | Receiver<br>Output |

|------------------|-----------------|-----------------------------------------|----------------------------------------|--------------------|

| V <sub>IA</sub>  | V <sub>IB</sub> | V <sub>ID</sub>                         | V <sub>IC</sub>                        | R                  |

| 2.400V           | 0.000V          | 2.400V                                  | 1.200V                                 | Н                  |

| 0.000V           | 2.400V          | -2.400V                                 | 1.200V                                 | L                  |

| 3.800V           | 3.650V          | 0.150V                                  | 3.725V                                 | н                  |

| 3.800V           | 3.750V          | 0.050V                                  | 3.775V                                 | L                  |

| -1.250V          | -1.400V         | 0.150V                                  | -1.325V                                | н                  |

| -1.350V          | -1.400V         | 0.050V                                  | –1.375V                                | L                  |

H — High Level

L — Low Level

Output state assumes that the receiver is enabled ( $\overline{RE} = L$ )

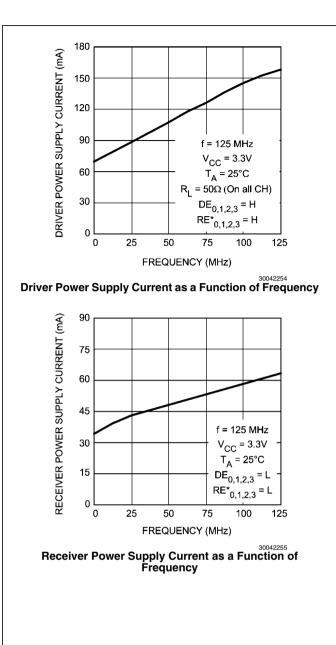

# Typical Performance

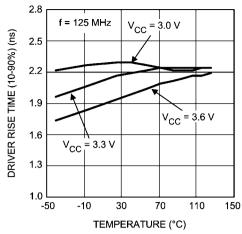

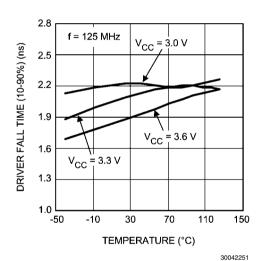

Driver Rise Time as a Function of Temperature

Driver Fall Time as a Function of Temperature

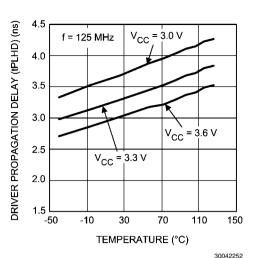

Driver Propagation Delay (tPLHD) as a Function of Temperature

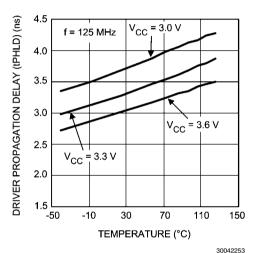

Driver Propagation Delay (tPHLD) as a Function of Temperature

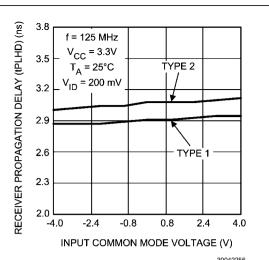

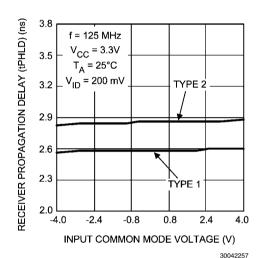

Receiver Propagation Delay (tPLHD) as a Function of Input Common Mode Voltage

Receiver Propagation Delay (tPHLD) as a Function of Input Common Mode Voltage

# Notes

| For more National Semiconductor product information and proven design tools, visit the following Web sites at: |                              |                         |                                |  |  |

|----------------------------------------------------------------------------------------------------------------|------------------------------|-------------------------|--------------------------------|--|--|

| Pr                                                                                                             | oducts                       | Design Support          |                                |  |  |

| Amplifiers                                                                                                     | www.national.com/amplifiers  | WEBENCH                 | www.national.com/webench       |  |  |

| Audio                                                                                                          | www.national.com/audio       | Analog University       | www.national.com/AU            |  |  |

| Clock Conditioners                                                                                             | www.national.com/timing      | App Notes               | www.national.com/appnotes      |  |  |

| Data Converters                                                                                                | www.national.com/adc         | Distributors            | www.national.com/contacts      |  |  |

| Displays                                                                                                       | www.national.com/displays    | Green Compliance        | www.national.com/quality/green |  |  |

| Ethernet                                                                                                       | www.national.com/ethernet    | Packaging               | www.national.com/packaging     |  |  |

| Interface                                                                                                      | www.national.com/interface   | Quality and Reliability | www.national.com/quality       |  |  |

| LVDS                                                                                                           | www.national.com/lvds        | Reference Designs       | www.national.com/refdesigns    |  |  |

| Power Management                                                                                               | www.national.com/power       | Feedback                | www.national.com/feedback      |  |  |

| Switching Regulators                                                                                           | www.national.com/switchers   |                         |                                |  |  |

| LDOs                                                                                                           | www.national.com/ldo         |                         |                                |  |  |

| LED Lighting                                                                                                   | www.national.com/led         |                         |                                |  |  |

| PowerWise                                                                                                      | www.national.com/powerwise   |                         |                                |  |  |

| Serial Digital Interface (SDI)                                                                                 | www.national.com/sdi         |                         |                                |  |  |

| Temperature Sensors                                                                                            | www.national.com/tempsensors |                         |                                |  |  |

| Wireless (PLL/VCO)                                                                                             | www.national.com/wireless    |                         |                                |  |  |

THE CONTENTS OF THIS DOCUMENT ARE PROVIDED IN CONNECTION WITH NATIONAL SEMICONDUCTOR CORPORATION ("NATIONAL") PRODUCTS. NATIONAL MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE ACCURACY OR COMPLETENESS OF THE CONTENTS OF THIS PUBLICATION AND RESERVES THE RIGHT TO MAKE CHANGES TO SPECIFICATIONS AND PRODUCT DESCRIPTIONS AT ANY TIME WITHOUT NOTICE. NO LICENSE, WHETHER EXPRESS, IMPLIED, ARISING BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT.

TESTING AND OTHER QUALITY CONTROLS ARE USED TO THE EXTENT NATIONAL DEEMS NECESSARY TO SUPPORT NATIONAL'S PRODUCT WARRANTY. EXCEPT WHERE MANDATED BY GOVERNMENT REQUIREMENTS, TESTING OF ALL PARAMETERS OF EACH PRODUCT IS NOT NECESSARILY PERFORMED. NATIONAL ASSUMES NO LIABILITY FOR APPLICATIONS ASSISTANCE OR BUYER PRODUCT DESIGN. BUYERS ARE RESPONSIBLE FOR THEIR PRODUCTS AND APPLICATIONS USING NATIONAL COMPONENTS. PRIOR TO USING OR DISTRIBUTING ANY PRODUCTS THAT INCLUDE NATIONAL COMPONENTS, BUYERS SHOULD PROVIDE ADEQUATE DESIGN, TESTING AND OPERATING SAFEGUARDS.

EXCEPT AS PROVIDED IN NATIONAL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, NATIONAL ASSUMES NO LIABILITY WHATSOEVER, AND NATIONAL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THE SALE AND/OR USE OF NATIONAL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

National Semiconductor and the National Semiconductor logo are registered trademarks of National Semiconductor Corporation. All other brand or product names may be trademarks or registered trademarks of their respective holders.

#### Copyright© 2008 National Semiconductor Corporation

For the most current product information visit us at www.national.com

National Semiconductor Americas Technical Support Center Email: support@nsc.com Tel: 1-800-272-9959 National Semiconductor Europe Technical Support Center Email: europe.support@nsc.com German Tel: +49 (0) 180 5010 771 English Tel: +44 (0) 870 850 4288 National Semiconductor Asia Pacific Technical Support Center Email: ap.support@nsc.com National Semiconductor Japan Technical Support Center Email: jpn.feedback@nsc.com

www.national.com