# PRELIMINARY

September 2002

# DS25C400 **Quad 2.5 Gbps Serializer/Deserializer General Description**

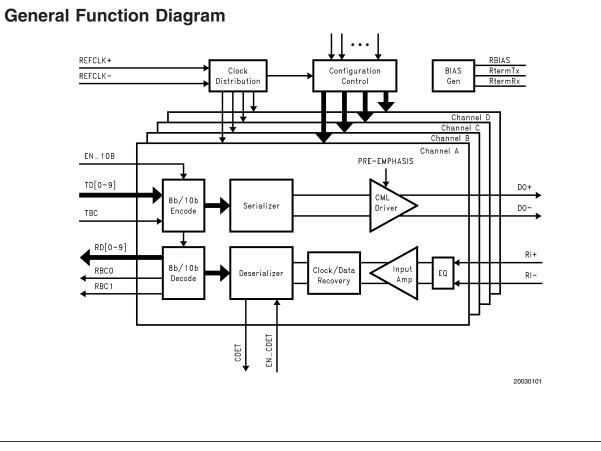

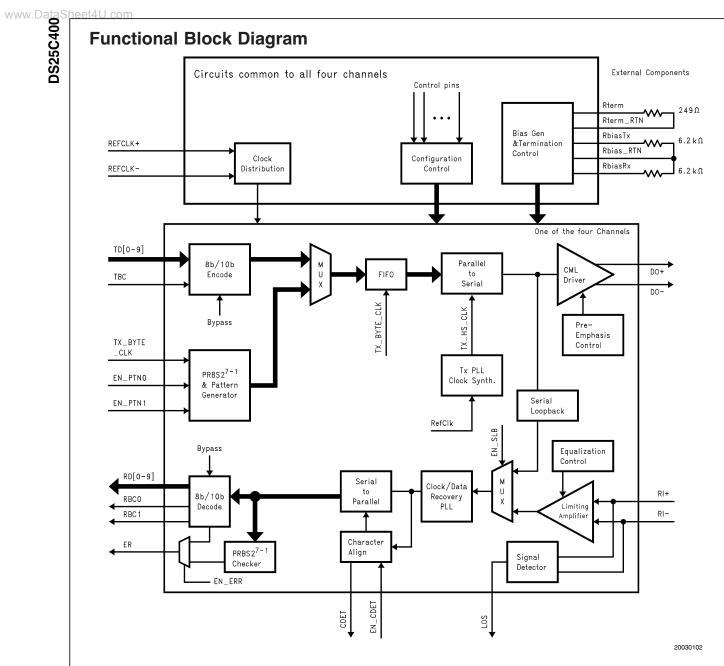

#### The DS25C400 is a four-channel serializer/deserializer (SERDES) for high-speed serial data transmission over controlled impedance transmission media such as a printed circuit board backplane or twin-axial cable. It is capable of transmitting and receiving serial data of 2.125 - 2.5 Gbps or 1.0625 - 1.25 Gbps per channel.

Each transmit section of the DS25C400 contains a low-jitter clock synthesizer, an 8-bit or 10-bit parallel to serial converter with built in 8b/10b encoder, and a CML output driver with selectable pre-emphasis optimized for backplane applications. Its receive section contains an input limiting amplifier with on-chip terminations and selectable equalization levels, a clock/data recovery PLL, a comma detector and a serial to parallel converter with built-in 8b/10b decoder.

The DS25C400 has built-in local loopback test mode, pseudo-random pattern generator and error detector to support self-testing.

The DS25C400 requires no external components for its clock synthesizers and clock recovery PLL's. Three external resistors are needed to set the proper bias currents and compensate for process variations to achieve tight tolerance on-chip terminations.

## Features

- Quad Serializer/Deserializer

- Data rate per channel: 2.125 2.5 Gbps or 1.0625 -1.25 Gbps

- Supports 106.25 125 MHz differential reference input clock

- Low jitter clock synthesizers for clock distribution

- 8-bit or 10-bit parallel I/O Interface conforms to SSTL 18 Class 1 (also interfaces to 1.8V HSTL or 1.8V IVCMOS)

- On-chip 8b/10b encoder and decoder

- High speed serial CML drivers

- High speed serial CML on-chip terminations

- Selectable pre-emphasis and equalization

- On-chip Comma Detect for character alignment

- On-chip local loopback test mode

- On-chip pattern generator and error checker to support BIST

- Hot plug protection

- Low power, 420 mW (typ) per channel

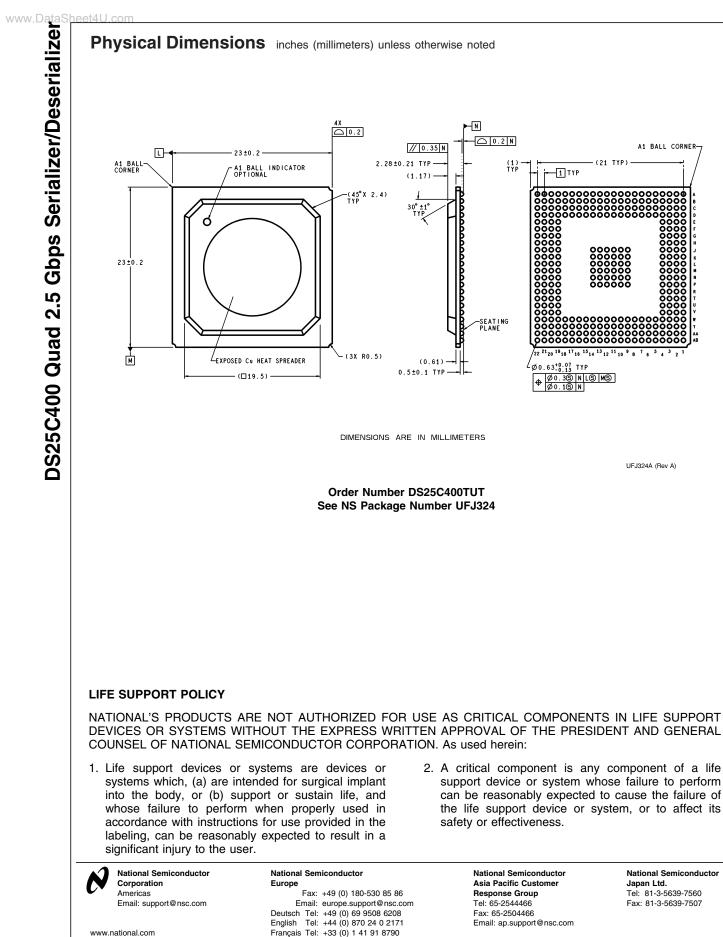

- 324-ball TE-PBGA package

- Operating temperature –40°C to +85°C

# Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| -                                      | -                                   |

|----------------------------------------|-------------------------------------|

| Supply Voltage                         |                                     |

| (V <sub>DDO</sub> , DV <sub>DD</sub> ) | -0.3V to +2.3V                      |

| Supply Voltage                         |                                     |

| Supply voltage                         |                                     |

| $(V_{DDIO}, V_{DDHS}, V_{DDB})$        | -0.3V to +3.0V                      |

| SSTL Input Voltage                     | –0.3V to (V <sub>DDQ</sub> + 0.3V)  |

| LVCMOS Input Voltage                   | –0.3V to (DV <sub>DD</sub> + 0.3V)  |

| LVCMOS Output Voltage                  | –0.3V to (DV <sub>DD</sub> + 0.3V)  |

| CML Receiver Input Voltage             | –0.3V to (V <sub>DDHS</sub> + 0.3V) |

| CML Driver Output Voltage              | –0.3V to (V <sub>DDHS</sub> + 0.3V) |

| Junction Temperature                   | +125°C                              |

| Storage Temperature                    | –65°C to +150°C                     |

| Lead Temperature                       |                                     |

| Soldering, 4 Seconds                   | +260°C                              |

|                                        |                                     |

| Maximum Package Power Dissipation at 2 | 5°C         |

|----------------------------------------|-------------|

| DS25C400TUT                            | 5.68 W      |

| Derating above 25°C                    | 45.45 mW/°C |

| Thermal Resistance, $\theta_{JA}$      | 22 °C/W     |

| Junction-to-case Conductive            |             |

| Thermal Resistance, $\theta_{JC}$      | 6.5 °C/W    |

| ESD Rating                             |             |

| HBM, 1.5 kΩ, 100 pF                    | >2 kV       |

| EIAJ, 0Ω, 200 pF                       | >200 V      |

# Recommended Operating Conditions

|                                                                | Min   | Тур | Мах   | Unit              |

|----------------------------------------------------------------|-------|-----|-------|-------------------|

| Supply Voltage                                                 |       |     |       |                   |

| $V_{DDQ}$ and $DV_{DD}$ to DGND                                | 1.7   | 1.8 | 1.9   | V                 |

| $V_{\text{DDIO}},V_{\text{DDHS}}$ and $V_{\text{DDB}}$ to DGND | or AG | AND |       |                   |

|                                                                | 2.35  | 2.5 | 2.65  | V                 |

| Temperature                                                    | -40   | 25  | 85    | °C                |

| Supply Noise Amplitude                                         |       |     | <100r | mV <sub>P-P</sub> |

| Supply Noise Frequency                                         |       |     | <1    | MHz               |

## **Electrical Characteristics**

Over recommended operating supply and temperature ranges unless otherwise specified.

| Symbol               | Parameter                 | Conditions                                                       | Min                        | Typ<br>(Note 2)  | Мах                        | Units |

|----------------------|---------------------------|------------------------------------------------------------------|----------------------------|------------------|----------------------------|-------|

| SSTL_18              | DC SPECIFICATIONS—Paral   | lel I/O, Class I                                                 | •                          |                  |                            |       |

| V <sub>REF</sub>     | Reference Voltage         |                                                                  | 0.83                       | 0.90             | 0.97                       | V     |

| V <sub>TT</sub>      | Termination Voltage       |                                                                  | V <sub>REF</sub> –<br>0.04 | V <sub>REF</sub> | V <sub>REF</sub> +<br>0.04 | V     |

| V <sub>IH</sub> (dc) | High Level Input Voltage  |                                                                  | V <sub>REF</sub><br>+0.125 |                  | V <sub>DDQ</sub><br>+0.300 | V     |

| V <sub>IH</sub> (ac) | AC Input Logic High       |                                                                  | V <sub>REF</sub><br>+0.250 |                  |                            | V     |

| V <sub>IL</sub> (dc) | Low Level Input Voltage   |                                                                  | -0.300                     |                  | V <sub>REF</sub><br>–0.125 | V     |

| V <sub>IL</sub> (ac) | AC Input Logic Low        |                                                                  |                            |                  | V <sub>REF</sub><br>-0.250 | V     |

| I <sub>IH</sub>      | High Level Input Current  | $V_{IN} = V_{DDQ} = 1.9 V$                                       | -10                        |                  | +50                        | μΑ    |

| l <sub>IL</sub>      | Low Level Input Current   | $V_{IN} = GND, V_{DDQ} = 1.9 V$                                  | -10                        |                  | +10                        | μA    |

| V <sub>OH</sub> (dc) | High Level Output Voltage | $I_{OH} = -6.3$ mA, Unterminated,<br>$C_L = 8pF$                 | V <sub>DDQ</sub><br>-0.400 |                  |                            | v     |

|                      |                           | Terminated, R = 50 $\Omega$ to V <sub>TT</sub>                   | V <sub>DDQ</sub><br>-0.550 |                  |                            | v     |

| V <sub>OL</sub> (dc) | Low Level Output Voltage  | $I_{OL} = 6.3 \text{ mA}$ , Unterminated,<br>$C_L = 8 \text{pF}$ |                            |                  | 0.400                      | V     |

|                      |                           | Terminated, R = 50 $\Omega$ to V <sub>TT</sub>                   |                            |                  | 0.550                      | V     |

| LVCMOS               | DC SPECIFICATIONS-Cont    | rol Pins EIA/JESD8-7 Compliant                                   |                            |                  |                            |       |

| V <sub>IH</sub>      | High Level Input Voltage  |                                                                  | 0.65*<br>DV <sub>DD</sub>  |                  | DV <sub>DD</sub>           | v     |

| V <sub>IL</sub>      | Low Level Input Voltage   |                                                                  | 0                          |                  | 0.35*<br>DV <sub>DD</sub>  | v     |

www.DataSheet4U.com Electrical Characteristics Over recommended operating supply and temperature ranges unless otherwise specified. (Continued)

| Symbol               | Parameter                   | Conditions                                                          | Min              | Typ<br>(Note 2) | Мах                       | Units             |

|----------------------|-----------------------------|---------------------------------------------------------------------|------------------|-----------------|---------------------------|-------------------|

| LVCMOS               | DC SPECIFICATIONS—Contro    | I Pins EIA/JESD8-7 Compliant                                        |                  | · · · ·         |                           |                   |

| н                    | High Level Input Current    | $V_{IN} = DV_{DD} = 1.9 V$                                          |                  | 0.1             |                           | mA                |

|                      |                             | (input and pull-low)                                                |                  | 0.1             |                           | IIIA              |

| I <sub>IH</sub>      | High Level Input Current    | $V_{IN} = DV_{DD} = 1.9 V$                                          | -10              |                 | +10                       | μA                |

|                      |                             | (input with pull-high)                                              | -10              |                 | ŦĨŬ                       | μΛ                |

| I <sub>IL</sub>      | Low Level Input Current     | $V_{IN} = GND, DV_{DD} = 1.9 V$                                     | -10              |                 | +10                       | μΑ                |

|                      |                             | (input with pull-low)                                               |                  |                 |                           | P.7 1             |

| IL                   | Low Level Input Current     | $V_{IN} = GND, DV_{DD} = 1.9 V$                                     |                  | -0.1            |                           | mA                |

|                      |                             | (input with pull-high)                                              |                  | -               |                           |                   |

| V <sub>он</sub>      | High Level Output Voltage   | $I_{OH} = -2 \text{ mA}$                                            | DV <sub>DD</sub> |                 |                           | V                 |

|                      |                             |                                                                     | -0.45            |                 |                           |                   |

| V <sub>OL</sub>      | Low Level Output Voltage    | I <sub>OL</sub> = 2 mA                                              |                  |                 | 0.45                      | V                 |

|                      | CURRENT                     | 1                                                                   |                  | 1 1             |                           |                   |

| DD                   | Total Supply Current        | K28.5 pattern at 2.5 Gbps with no                                   |                  |                 |                           |                   |

|                      |                             | pre-emphasis. SSTL outputs no load                                  |                  |                 |                           |                   |

|                      |                             | termination resistors, Tx high speed                                |                  |                 |                           |                   |

|                      |                             | serial outputs driving $100\Omega$                                  |                  |                 |                           |                   |

|                      |                             | differential, no high speed Rx input data.                          |                  |                 |                           |                   |

|                      |                             |                                                                     |                  | 570             | 600                       |                   |

|                      |                             | $V_{\text{DDHS}} + V_{\text{DDIO}} + V_{\text{DDB}}$                |                  | 572             |                           | mA                |

|                      | <b>T</b> + + <b>D</b> = 0 = | $DV_{DD} + V_{DDQ}$                                                 |                  | 130             | 136.5                     | mA                |

| D                    | Total Power Consumption     | K28.5 pattern at 2.5 Gbps with no                                   |                  |                 |                           |                   |

|                      |                             | pre-emphasis. SSTL outputs no load                                  |                  |                 |                           |                   |

|                      |                             | termination resistors, Tx high speed                                |                  |                 |                           |                   |

|                      |                             | serial outputs driving 100Ω<br>differential, no high speed Rx input |                  |                 |                           |                   |

|                      |                             | data.                                                               |                  |                 |                           |                   |

|                      |                             | SERDES and SSTL I/O                                                 |                  | 1708            | 1940                      | mW                |

| RECOMM               |                             | -OCK (REFCLK±) AC coupled differen                                  | tial cianal      | 1700            | 1340                      | 11100             |

| VIDS <sub>RCLK</sub> |                             | Terminated by $50\Omega$ parallel                                   | tiai signai      |                 |                           |                   |

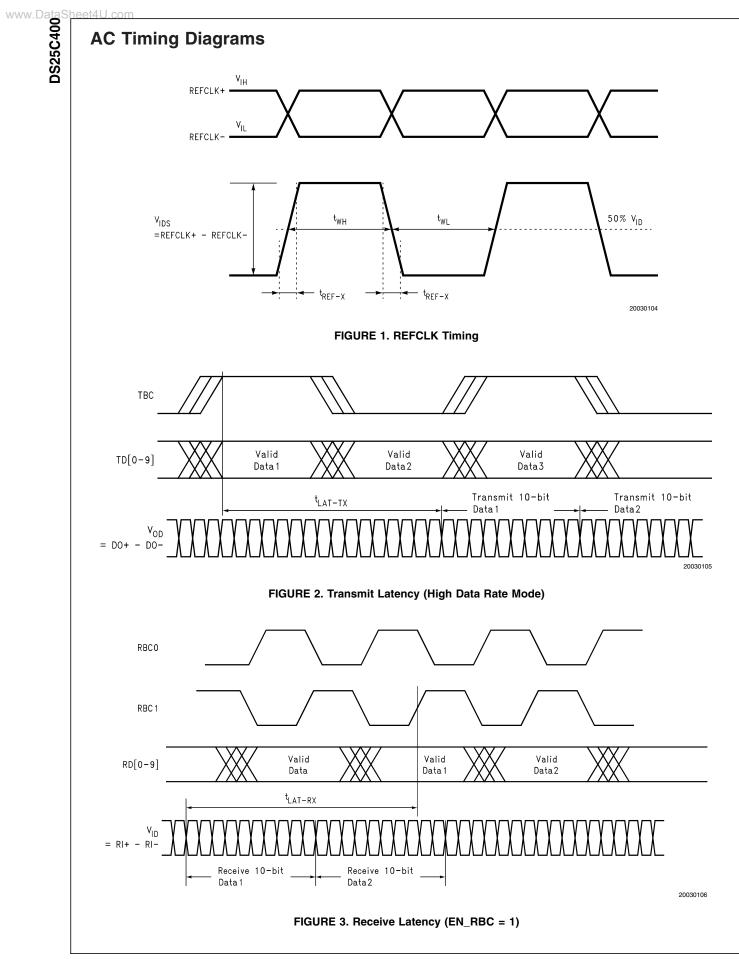

| VIDORCLK             | Figure 1                    | termination                                                         | 600              |                 | 1500                      | mV <sub>p</sub> . |

| V <sub>ICM</sub>     | Common Mode Voltage         | Terminated by $50\Omega$ Parallel                                   |                  |                 | V                         |                   |

| V ICM                | Common Mode Voltage         | Termination                                                         | 1.0              |                 | V <sub>DDHS</sub><br>-0.5 | V                 |

| R <sub>REFCLK</sub>  | Input Termination to GND    | Equivalent Parallel Input Termination                               |                  |                 | 0.0                       |                   |

| REFCLK               |                             | at REFCLK+ or REFCLK- to GND                                        |                  | 100             |                           | Ω                 |

| REF                  | REFCLK Frequency Range      |                                                                     | 106.25           |                 | 125                       | MHz               |

| df <sub>REF</sub>    | REFCLK Frequency Variation  | Variation from Nominal Frequency                                    | -100             |                 | +100                      | ppm               |

| REF-DC               | REFCLK Duty Cycle (Note 3)  | Between 50% of the differential                                     |                  |                 |                           |                   |

| REF-DC               |                             | voltage across REFCLK+ and                                          | 40               | 50              | 60                        | %                 |

|                      |                             | REFCLK-                                                             |                  |                 |                           | ,.                |

| REF-RJ               | REFCLK Input                |                                                                     |                  |                 |                           |                   |

| NEF-NJ               | Random (rms) Jitter         |                                                                     |                  | 3               | 5                         | ps                |

| REF-RJ               | REFCLK Input                |                                                                     |                  |                 |                           |                   |

| ILEF-PJ              | Peak-to-Peak Jitter         |                                                                     |                  | 25              | 40                        | ps                |

|                      |                             | Transition time between 20% and                                     |                  |                 |                           |                   |

| BEE-Y                | REFCLK Transition Time      |                                                                     |                  | 1               |                           | 1                 |

| REF-X                | REFCLK Transition Time      | 80% of the differential voltage across                              | 0.2              |                 | 1                         | ns                |

**Electrical Characteristics** Over recommended operating supply and temperature ranges unless otherwise specified. (Continued)

| Symbol               | Parameter                              | Conditions                                  | Min    | Typ<br>(Note 2)   | Мах  | Units             |

|----------------------|----------------------------------------|---------------------------------------------|--------|-------------------|------|-------------------|

| SERIALIZ             | ÆR                                     |                                             |        |                   |      | 1                 |

| DR <sub>DO</sub>     | Transmit Data Rate                     | Data Rate at DO±                            |        |                   |      |                   |

|                      |                                        | High Data Rate Mode (EN_HDR = 1)            | 2.125  |                   | 2.5  | Gbps              |

|                      |                                        | Low Data Rate Mode (EN_HDR = 0)             | 1.0625 |                   | 1.25 | Gbps              |

| V <sub>ODS</sub>     | Output Differential Voltage            | DO+, DO- are terminated by external         |        |                   |      |                   |

|                      | Swing (DO+ – DO–) WITHOUT              | 50 $\Omega$ to V <sub>DDHS</sub>            | 850    | 1065              | 1280 | mV <sub>p-p</sub> |

|                      | Pre-emphasis                           | PSEL1 = 0, PSEL0 = 0                        |        |                   |      |                   |

|                      | Output Differential Voltage            | DO+, DO- are terminated by external         |        |                   |      |                   |

|                      | Swing (DO+ – DO–) WITH                 | 50 $\Omega$ to V <sub>DDHS</sub>            |        |                   |      |                   |

|                      | Pre-emphasis                           | PSEL1 = 0, PSEL0 = 1                        | TBD    | 1330              | TBD  | mV <sub>p-p</sub> |

|                      |                                        | PSEL1 = 1, PSEL0 = 0                        | TBD    | 1600              | TBD  |                   |

|                      |                                        | PSEL1 = 1, PSEL0 = 1                        | TBD    | 1850              | TBD  |                   |

| V <sub>CM</sub>      | Output Common Mode Offset              | DO+, DO- are terminated by external         |        | V <sub>DDHS</sub> |      |                   |

|                      | Voltage WITHOUT                        | 50 $\Omega$ to V <sub>DDHS</sub>            | -10%   | ● DDHS<br>-0.3    | +10% | V                 |

|                      | Pre-emphasis                           | PSEL1 = 0, PSEL0 = 0                        |        | 0.0               |      |                   |

|                      | Output Common Mode Offset              | DO+, DO- are terminated by external         |        |                   |      |                   |

|                      | Voltage WITH Pre-emphasis              | 50 $\Omega$ to V <sub>DDHS</sub>            |        | V <sub>DDHS</sub> |      |                   |

|                      |                                        | PSEL1 = 0, PSEL0 = 1                        | -10%   | -0.37             | +10% | V                 |

|                      |                                        | PSEL1 = 1, PSEL0 = 0                        |        | V <sub>DDHS</sub> |      |                   |

|                      |                                        |                                             |        | -0.43             |      |                   |

|                      |                                        | PSEL1 = 1, PSEL0 = 1                        |        | V <sub>DDHS</sub> |      |                   |

|                      |                                        |                                             |        | -0.50             |      |                   |

| R <sub>DO</sub>      | Output Resistance                      | On-chip termination DO+ or DO- to           | 45     | 50                | 55   | Ω                 |

| _                    |                                        | $V_{\text{DDHS}}, \text{RTERM} = 249\Omega$ |        |                   |      |                   |

| C <sub>DO</sub>      | Capacitance to GND                     | DO+ or DO- to GND                           |        | 1                 |      | pF                |

| t <sub>DO-X</sub>    | Serial Data Output Transition          | Measured between 20% and 80% of             | 100    | 120               | 160  | ps                |

|                      | Time                                   | V <sub>ODS</sub>                            |        |                   |      | · ·               |

| $JIT_{DO-DJ}$        | Serial Data Output                     | Output K28.5 at 2.5 Gbps                    |        |                   |      |                   |

|                      | Deterministic Jitter                   |                                             |        | 0.1               | 0.13 | UI                |

|                      | (Peak-to-Peak),                        |                                             |        |                   |      |                   |

| <u>ит</u>            | (Notes 4, 5)                           | Output D01 5 at 0.5 Chas                    |        |                   |      |                   |

| JIT <sub>DO-RJ</sub> | Serial Data Output Random              | Output D21.5 at 2.5 Gbps                    |        | 0.12              | 0.15 |                   |

|                      | Jitter (Peak-to-Peak),<br>(Notes 4, 5) |                                             |        | 0.13              | 0.15 | U                 |

| пт                   | Serial Data Output Total Jitter,       | Output K28.5 pattern at 2.5 Gbps at         |        |                   |      |                   |

| JIT <sub>DO-TJ</sub> | (Notes 4, 5)                           | BER of $10^{-12}$                           |        | 0.2               | 0.25 | UI                |

| +                    | Transmit Latency Figure 2              | Transmit K28.5 from TD[0–9] to DO±          |        |                   |      |                   |

| t <sub>LAT-TX</sub>  |                                        | at 2.5 Gbps, $EN_{10B} = 1$                 | 35     |                   | 48   | Bits              |

|                      |                                        | Transmit K28.5 from TD[0–9] to DO $\pm$     |        |                   |      |                   |

|                      |                                        | at 2.5 Gbps, EN_10B = 0                     | 45     |                   | 58   | Bits              |

| t <sub>DO-LOCK</sub> | Lock Time                              | Time to achieve frequency lock to           |        |                   |      |                   |

| DO-LOCK              |                                        | REFCLK. Output K28.5 at 2.5 Gbps.           |        |                   | 0.5  | ms                |

| DESERIA              | LIZEB                                  |                                             |        |                   |      |                   |

| DR <sub>RI</sub>     | Receive Data Rate                      | High Data Rate (EN_HDR = 1)                 | 2.125  |                   | 2.5  | Gbps              |

| - · ·RI              |                                        | Low Data Rate ( $EN_HDR = 0$ )              | 1.0625 |                   | 1.25 | Gbps              |

| VIDS                 | Differential Input Voltage             | $RI_{+} - RI_{-}$                           | 200    |                   |      | - ·               |

| VIDS <sub>RI</sub>   | Differential Input Voltage             |                                             | 200    |                   | 1500 | mV <sub>p-p</sub> |

| R <sub>RI</sub>      | Input Termination to V <sub>DDHS</sub> | On-chip termination RI+ to RI- to           |        |                   |      |                   |

|                      |                                        |                                             |        | 50                |      |                   |

|                      |                                        | EN_RAC = 0, RTERM = 249Ω:                   | 45     | 50                | 55   | Ω                 |

www.DataSheet4U.com Electrical Characteristics Over recommended operating supply and temperature ranges unless otherwise specified. (Continued)

| Symbol                | Parameter                      | Conditions                                    | Min               | Typ<br>(Note 2)   | Мах               | Units            |

|-----------------------|--------------------------------|-----------------------------------------------|-------------------|-------------------|-------------------|------------------|

| DESERIA               | LIZER                          | 1                                             | 1                 | 1                 |                   |                  |

| C <sub>RI</sub>       | Input Capacitance to GND       | RI+ or RI- to GND                             |                   | 1                 |                   | pF               |

| V <sub>RI-BIAS</sub>  | Input Bias Voltage             | DC bias at RI+ or RI- when                    | 0.9*              | 0.91*             | 0.92*             |                  |

|                       |                                | configure for AC couple                       |                   |                   |                   | V                |

|                       |                                | $(EN_RAC = 1)$                                | V <sub>DDHS</sub> | V <sub>DDHS</sub> | V <sub>DDHS</sub> |                  |

| R <sub>RIAC</sub>     | Equivalent Parallel Input      | Equivalent parallel termination at RI+        |                   |                   |                   |                  |

|                       | Termination                    | or RI– to GND                                 |                   |                   |                   |                  |

|                       |                                | EN_RAC = 1, RTERM = 249Ω:                     | 45                | 50                | 55                | Ω                |

| t <sub>LAT-RX</sub>   | Receive Latency Figure 3       | Receive K28.5 from RI± to RD[0-9]             | 76                |                   | 95                | Bits             |

|                       |                                | at 2.5 Gbps, EN_10B = 1                       |                   |                   |                   | Dito             |

|                       |                                | Receive K28.5 from RI± to RD[0-9]             | 86                |                   | 105               | Bits             |

|                       |                                | at 2.5 Gbps, EN_10B = 0                       |                   |                   |                   |                  |

| JIT <sub>RI-TL</sub>  | Input Jitter Tolerance Without | Receiving RPAT pattern at 2.5Gbps             |                   |                   |                   |                  |

|                       | Equalizer,                     | at BER of 10 <sup>-12</sup> of random jitter  | 0.22              |                   |                   | UI               |

|                       | (Notes 4, 5)                   | (1.5MHz to 1.25GHz)                           |                   |                   |                   |                  |

|                       |                                | Receiving RPAT pattern at 2.5Gbps             |                   |                   |                   |                  |

|                       |                                | at BER of 10 <sup>-12</sup> of non-sinusoidal | 0.5               |                   |                   | U                |

|                       |                                | deterministic jitter (1.5MHz to               |                   |                   |                   | _                |

|                       |                                | 1.25GHz)                                      |                   |                   |                   |                  |

| F <sub>FRI-LOCK</sub> | Receiver Lock Range            | Input data rate reference to local            | -200              |                   | +200              | ppm              |

|                       | · · · · · -·                   | transmit data rate                            |                   |                   |                   |                  |

| t <sub>RI-LOCK</sub>  | Maximum Lock Time              |                                               |                   |                   | 500               | μs               |

| LOS <sub>TH</sub>     | Loss of Signal Detect          | Loss of Signal OFF                            |                   |                   | 200               | mV <sub>p-</sub> |

|                       | Thresholds                     | Loss of Signal ON                             | 80                |                   |                   | mV <sub>p-</sub> |

| T <sub>LOSOFF</sub>   | Loss of Signal Detect Off      | Loss of signal OFF time.                      |                   |                   | 100               | μs               |

|                       | Timing                         | $VIDS = 200 \text{ mV}_{p-p}$                 |                   |                   |                   | P                |

| T <sub>LOSON</sub>    | Loss of Signal Detect on       | Loss of signal ON time.                       |                   |                   | 100               | μs               |

|                       | Timing                         | VIDS = 80 mV <sub>p-p</sub>                   |                   |                   |                   |                  |

|                       |                                | ow-Data-Rate Mode at 1.25 Gbps, EN_           |                   |                   | [                 | 1                |

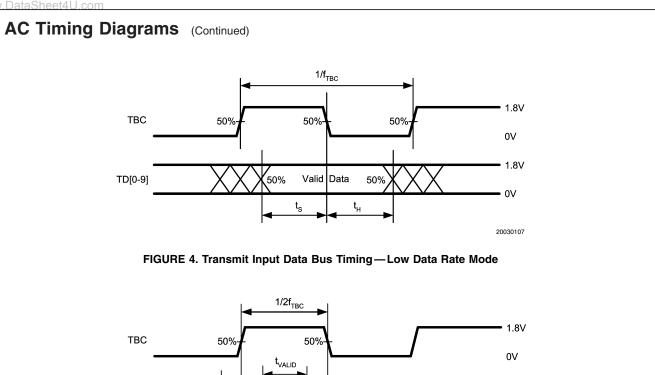

| t <sub>s</sub>        | Setup Time Figure 4            | TBC Falling Edge to TD[0-9] Valid             | 1.4               |                   |                   | ns               |

| t <sub>H</sub>        | Hold Time Figure 4             | TBC Falling Edge to TD[0-9] Invalid           | 1.4               |                   |                   | ns               |

| f <sub>твс</sub>      | TBC Frequency                  | At Line Date Rate of 1.0625 Gbps              |                   | 106.25            |                   | MHz              |

|                       |                                | At Line Date Rate of 1.25 Gbps                |                   | 125               |                   | MHz              |

| TIMING S              |                                | igh-Data-Rate Mode at 2.5 Gbps, EN_I          | IDR = 1           |                   |                   |                  |

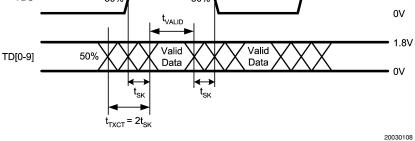

| t <sub>valid</sub>    | Valid Time Figure 5            | TBC and TD[0-9] Valid                         | 1.0               |                   |                   | ns               |

| t <sub>sk</sub>       | Edge Skew Figure 5             | TBC and TD[0-9] Valid                         |                   |                   | 1.5               | ns               |

| t <sub>TXCT</sub>     | Transition Time Figure 5       | TBC or TD[0-9] Transition Time                |                   |                   | 3.0               | ns               |

| f <sub>твс</sub>      | TBC Frequency                  | At Line Data Rate of 2.125 Gbps               |                   | 106.25            |                   | MHz              |

|                       |                                | At Line Data Rate of 2.5 Gbps                 |                   | 125               |                   | MHz              |

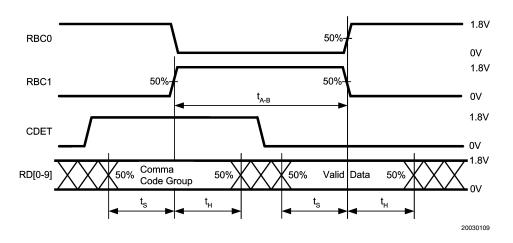

| TIMING S              | PECIFICATIONS — Deserializer   | , High-Data-Rate Mode at 2.5 Gbps, EN         | I_RBC = 0         |                   |                   |                  |

| t <sub>s</sub>        | Setup Time Figure 6            | RBC1 or RBC0 Rising Edge to the               |                   |                   |                   |                  |

|                       |                                | Corresponding Data Word at                    | 1.4               |                   |                   | ns               |

|                       |                                | RD[0-9] Valid                                 |                   |                   |                   |                  |

| t <sub>H</sub>        | Hold Time Figure 6             | RBC1 or RBC0 Rising Edge to the               |                   |                   |                   |                  |

|                       |                                | Corresponding Data Word at                    | 1.4               |                   |                   | ns               |

|                       |                                | RD[0–9] Invalid                               |                   |                   |                   |                  |

| t <sub>DC</sub>       | Duty Cycle                     | RBC1 or RBC0 Duty Cycle                       | 40                |                   | 60                | %                |

| t <sub>A-B</sub>      | RBC Clock Skew Figure 6        | Rising Edge of RBC1 to Rising Edge            | 0.0               |                   | 4.0               |                  |

|                       | -                              | of RBC0                                       | 3.8               | 1                 | 4.2               | ns               |

**Electrical Characteristics** Over recommended operating supply and temperature ranges unless otherwise specified. (Continued)

| Symbol            | Parameter                    | Conditions                                                                    | Min         | Typ<br>(Note 2) | Max | Units |

|-------------------|------------------------------|-------------------------------------------------------------------------------|-------------|-----------------|-----|-------|

| TIMING S          | PECIFICATIONS — Deserializer | , High-Data-Rate Mode at 2.5 Gbps, EN                                         | _RBC = 0    |                 |     |       |

| f <sub>RBC</sub>  | RBC Frequency                | At Line Date Rate of 2.125 Gbps                                               |             | 106.25          |     | MHz   |

|                   |                              | At Line Date Rate of 2.5 Gbps                                                 |             | 125             |     | MHz   |

| TIMING S          | PECIFICATIONS — Deserializer | , Low-Data-Rate Mode at 1.25 Gbps, EN                                         | $N_RBC = 0$ |                 |     |       |

| t <sub>s</sub>    | Setup Time Figure 6          | RBC1 Rising Edge to RD[0-9] Valid                                             | 3.0         |                 |     | ns    |

| t <sub>H</sub>    | Hold Time Figure 6           | RBC1 Rising Edge to RD[0-9] Invalid                                           | 3.0         |                 |     | ns    |

| t <sub>DC</sub>   | Duty Cycle                   | RBC1 Duty Cycle                                                               | 40          |                 | 60  | %     |

| t <sub>A-B</sub>  | RBC Clock Skew Figure 6      | Rising Edge of RBC1 to Rising Edge<br>of RBC0                                 | 7.6         |                 | 8.4 | ns    |

| f <sub>BBC</sub>  | RBC Frequency                | At Line Date Rate of 1.0625 Gbps                                              |             | 53.125          |     | MHz   |

| 1.20              |                              | At Line Date Rate of 1.25 Gbps                                                |             | 62.5            |     | MHz   |

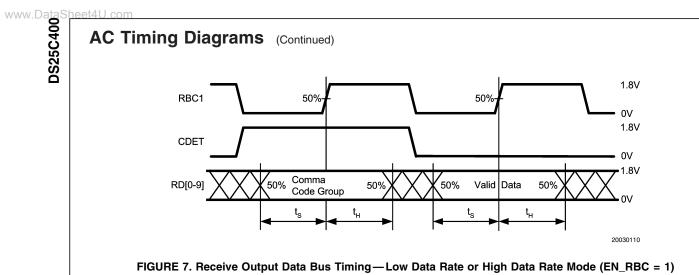

| TIMING S          | PECIFICATIONS — Deserializer | , High-Data-Rate Mode at 2.5 Gbps, EN                                         | _RBC = 1    | II              |     | 1     |

| t <sub>s</sub>    | Setup Time Figure 7          | RBC1 Rising Edge to RD[0-9] Valid                                             | 1.4         |                 |     | ns    |

| t <sub>H</sub>    | Hold Time Figure 7           | RBC1 Rising Edge to RD[0-9] Invalid                                           | 1.4         |                 |     | ns    |

| f <sub>RBC</sub>  | RBC Frequency                | At High Data Rate (EN_HDR = 1)<br>2.125 Gbps                                  |             | 212.5           |     | MHz   |

|                   |                              | At High Data Rate (EN_HDR = 1)<br>2.5 Gbps                                    |             | 250             |     | MHz   |

| t <sub>xRBC</sub> | RBC Transition Time          | $V_{REF} - 0.25 V$ to $V_{REF} + 0.25 V$                                      | 0.4         | 0.6             | 0.8 | ns    |

| t <sub>x</sub>    | Output Data Transition Time  | For RD[0-9], CDET, LOS and ER<br>pins. Measured between 20% and<br>80% Levels | 0.6         | 1.0             | 1.5 | ns    |

| TIMING S          | PECIFICATIONS — Deserializer | , Low-Data-Rate Mode at 1.25 Gbps, EN                                         | N_RBC = 1   |                 |     |       |

| t <sub>s</sub>    | Setup Time Figure 7          | RBC1 Rising Edge to RD[0-9] Valid                                             | 3.0         |                 |     | ns    |

| t <sub>H</sub>    | Hold Time Figure 7           | RBC1 Rising Edge to RD[0-9] Invalid                                           | 3.0         |                 |     | ns    |

| f <sub>RBC</sub>  | RBC Frequency                | At Low Data Rate (EN_HDR = 0)<br>1.0625 Gbps                                  |             | 106.25          |     | MHz   |

|                   |                              | At Low Data Rate (EN_HDR = 0)<br>1.25 Gbps                                    |             | 125             |     | MHz   |

Note 1: "Absolute Maximum Ratings" are the ratings beyond which the safety of the device cannot be guaranteed. They are not meant to imply that the device should be operated at these limits.

Note 2: Typical parameters are measured at  $V_{DDQ}$  = 1.8 V,  $DV_{DD}$  = 1.8 V,  $V_{DDHS}$  = 2.5 V,  $V_{DDIO}$  = 2.5 V,  $V_{DDB}$  = 2.5 V,  $T_A$  = 25°C. They are for reference purposes, and are not production-tested.

Note 3: Duty cycle is defined as high period ( $t_{WH}$ ) or low period ( $t_{WL}$ ) ratio to clock period ( $t_{WH} + t_{WL}$ ), measured at 50% of the differential voltage across REFCLK+ and REFCLK-.

Note 4: K28.5 is a repeating periodic pattern (hex: 283, 17C - bin: 110000 0101, 001111 1010). D21.5 is a repeating periodic pattern (hex: 155 - bin: 1010101010). RPAT is a random data pattern with valid 8b/10b data codes of K28.5, K28.5, D3.1, D7.2, D11.3, D15.4, D19.5, D23.6, D27.7, D20.0, D21.1, D25.2 (hex: 283, 283, 263, 288, 30B, 2C5, 153, 197, 1E4, 0B4, 255, 299).

**Note 5:** Output Jitter and Jitter Tolerance are measured through characterization on sample basis. They are not production-tested. Output jitter is measured at a sample size of TBD. REFCLK $\pm$  differential amplitude is 1.2 V<sub>p-p</sub> with jitter of 3 ps (rms) or 25 ps (pk-pk) for Tx output jitter testing.

FIGURE 5. Transmit Input Data Timing—High Data Rate Mode

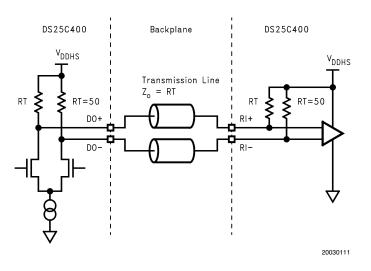

# Termination at the High Speed Interface

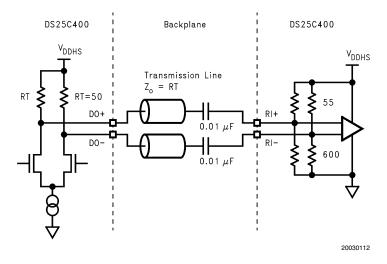

FIGURE 8. High Speed Interface — Direct-Coupled Mode (EN\_RAC = 0)

FIGURE 9. High Speed Interface — AC-Coupled Mode (EN\_RAC = 1)

# **Termination at REFCLK**

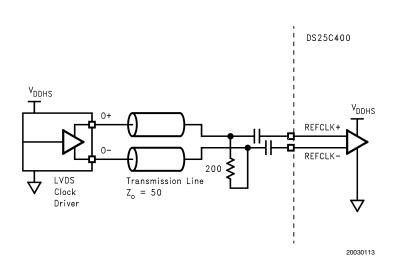

FIGURE 10. LVDS Terminations at REFCLK±

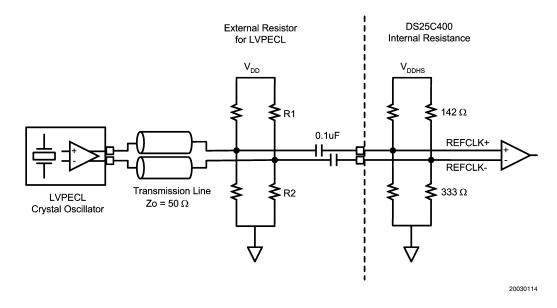

FIGURE 11. LVPECL Terminations at REFCLK±

The inputs to the DS25C400 have parallel termination resistors, the venin equivalent to 100 $\Omega$  single-ended. The value of R1 and R2 must be selected such that  $V_T$  =  $V_{DD}$  – 2V and that the equivalent resistance is also 100 $\Omega$  single-ended. Termination values for different V<sub>DD</sub> supply voltages: For V<sub>DD</sub> = 2.5V; R1 = 500  $\Omega$ ; R2 = 125.5  $\Omega$ For V<sub>DD</sub> = 3.3V; R1 = 253  $\Omega$ ; R2 = 165  $\Omega$ For V<sub>DD</sub> = 5.0V; R1 = 167  $\Omega$ ; R2 = 250  $\Omega$  Termination at the Parallel I/O Interface

DS25C400

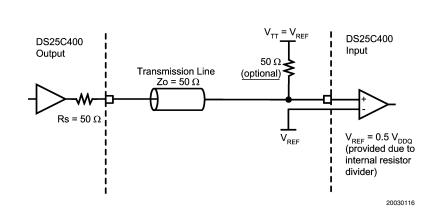

FIGURE 12. SSTL\_18 Class 1, 1.8V HSTL or 1.8V LVCMOS I/O Termination

|             |                                          |    | A                | в                  | c                | D                 | ш        | Ŀ                | 9      | н       | ſ                | ×       | L                | Σ                | z                 | д                | ч       | F                 | n                | >                | w       | ×                 | AA               | AB                |    |

|-------------|------------------------------------------|----|------------------|--------------------|------------------|-------------------|----------|------------------|--------|---------|------------------|---------|------------------|------------------|-------------------|------------------|---------|-------------------|------------------|------------------|---------|-------------------|------------------|-------------------|----|

|             |                                          | 22 | EQ0_A            | AGND               | VDDHS            | VDDHS             | RI_A+    | RI_A-            | VDDHS  | RI_B-   | RI_B+            | AGND    | RES5             | RES6             | AGND              | RI_C+            | RI_C-   | VDDHS             | RI_D-            | RI_D+            | VDDHS   | VDDHS             | AGND             | DGND              | 22 |

|             |                                          | 21 | EQ1_A            | EQ0_B              | AGND             | V <sub>DDHS</sub> | DGND     | DV <sub>DD</sub> | VDDHS  | AGND    | DV <sub>DD</sub> | лорна   | AGND             | AGND             | V <sub>DDHS</sub> | DV <sub>DD</sub> | AGND    | V <sub>DDHS</sub> | DVDD             | DGND             | VDDHS   | AGND              | RES20            | RES22             | 21 |

|             |                                          | 20 | VDDHS            | EQ1_B              | AGND             | P0_A+             | - Y - OQ | DV <sub>DD</sub> | RES8   | RES9    | DV <sub>DD</sub> | -8-D0   | D0_B+            | +0-01            | D0_C-             | DV <sub>DD</sub> | RES 10  | RES11             | DV <sub>DD</sub> | -D0D             | +0_0d   | AGND              | RES 19           | RES 18            | 20 |

|             |                                          | 19 | EQ0_C            | EQ0_D              | EQ1_C            | RES4              | AGND     | DGND             | VDDHS  | AGND    | DGND             | DGND    | AGND             | лоди             | DGND              | DGND             | AGND    | VDDHS             | DGND             | AGND             | RES7    | RES17             | RES16            | RES15             | 19 |

|             |                                          | 18 | LOS_C            | LOS_B              | P_S01            | EQ1_D             |          |                  |        |         |                  |         |                  |                  |                   |                  |         |                   |                  |                  | RES21   | RES23             | PSEL0_D          | PSEL1_D           | 18 |

|             |                                          | 17 | RES3             | AGND               | EN_CDET          | LOS_D             |          |                  |        |         |                  |         |                  |                  |                   |                  |         |                   |                  |                  | PSEL0_C | V <sub>DDQ</sub>  | PSEL 1_C         | PSEL0_B           | 17 |

|             |                                          | 16 | EN_RAC           | VDDHS              | EN_HDR           | EN_RBC            |          |                  |        |         |                  |         |                  |                  |                   |                  |         |                   |                  |                  | PSEL1_B | DGND              | PSEL 1_A         | ER_D              | 16 |

|             | (Mé                                      | 15 | REFCLK+          | EN_PTN0            | EN_PTN1          | EN_ERR            |          |                  |        |         |                  |         |                  |                  |                   |                  |         |                   |                  |                  | PSEL0_A | ER_C              | ER_A             | RES 1             | 15 |

|             | ⊺op Vi€                                  | 14 | REFCLK-          | AGND               | EN_PLB           | EN_10B            |          |                  |        |         | AGND             | AGND    | AGND             | AGND             | AGND              | AGND             |         |                   |                  |                  | ER_B    | RBIASTX           | DGND             | RBIAS_<br>RTN     | 14 |

|             | BGA (1                                   | 13 | VDDHS            | RES12              | EN_SLB           | RES2              |          |                  |        |         | AGND             | AGND    | AGND             | AGND             | AGND              | AGND             |         |                   |                  |                  | RBIASRX | VDDB              | V <sub>DDQ</sub> | RTERM_<br>RTN     | 13 |

|             | I TE-PI                                  | 12 | AGND             | RES 13             | EN_LOS           | AGND              |          |                  |        |         | AGND             | AGND    | AGND             | AGND             | AGND              | AGND             |         |                   |                  |                  | RTERM   | DGND              | PD0              | DGND              | 12 |

|             | 324-bal                                  | 11 | $TD_A(3)$        | $TD_A(2)$          | TD_A(1)          | TD_A(0)           |          |                  |        |         | DGND             | DGND    | DGND             | DGND             | DGND              | DGND             |         |                   |                  |                  | PD1     | V <sub>DDQ</sub>  | TD_D[0]          | TD_D[1]           | 11 |

|             | DS25C400TUT: 324-ball TE-PBGA (Top View) | 10 | V <sub>DDQ</sub> | TDA(4)             | DGND             | V <sub>DDIO</sub> |          |                  |        |         | DGND             | DGND    | DGND             | DGND             | DGND              | DGND             |         |                   |                  |                  | TD_D[2] | TD_D[3]           | TD_D[4]          | DGND              | 10 |

|             | 25C400                                   | 6  | DGND             | TD_A(6)            | DGND             | TD_A(5)           |          |                  |        |         | DGND             | DGND    | DGND             | DGND             | DGND              | DGND             |         |                   |                  |                  | DGND    | V <sub>DDIO</sub> | TD_D[5]          | V <sub>DDQ</sub>  | 6  |

|             | DS                                       | 8  | TBC_A            | TD_A(9)            | TD_A(8)          | TD_A(7)           |          |                  |        |         |                  |         |                  |                  |                   |                  |         |                   |                  |                  | TD_D[6] | TD_D[7]           | TD_D[8]          | TD_D[9]           | ø  |

|             |                                          | 7  | RBC0_A           | CDET_A             | V <sub>DDQ</sub> | RBC 1_A           |          |                  |        |         |                  |         |                  |                  |                   |                  |         |                   |                  |                  | TBC_D   | DGND              | CDET_D           | RBC1_D            | 7  |

|             |                                          | 9  | RD_A[2]          | RD_A[1]            | DGND             | RD_A[0]           |          |                  |        |         |                  |         |                  |                  |                   |                  |         |                   |                  |                  | RD_D[0] | V <sub>DDQ</sub>  | RBC0_D           | RD_D[1]           | 9  |

|             |                                          | 5  | V <sub>DDQ</sub> | RD_A[5]            | RD_A[4]          | RD_A[3]           |          |                  |        |         |                  |         |                  |                  |                   |                  |         |                   |                  |                  | RD_D[2] | RD_D[3]           | RD_D[4]          | DGND              | 5  |

|             |                                          | 4  | DGND             | RD_A[8]            | RD_A[7]          | RD_A[6]           | RD_B[3]  | RD_B[0]          | RBC1_B | TD_B[7] | DGND             | TD_B[2] | DGND             | V <sub>DDQ</sub> | VDDIO             | DGND             | TD_C[7] | RBC1_C            | RD_C[0]          | RD_C[2]          | RD_C[5] | RD_D[5]           | RD_D[6]          | V <sub>DDQ</sub>  | 4  |

|             |                                          | 3  | RD_A(9)          | V <sub>REF 1</sub> | V <sub>DDQ</sub> | RD_B[6]           | RD_B[4]  | RD_B[1]          | CDET_B | DGND    | V <sub>DDQ</sub> | TD_B[3] | TD_B[0]          | TD_C[0]          | TD_C[2]           | V <sub>DDQ</sub> | DGND    | CDET_C            | RD_C[1]          | V <sub>DDQ</sub> | DGND    | RD_C[7]           | RD_D[7]          | RD_D[8]           | ×  |

|             |                                          | 2  | DGND             | V <sub>DDQ</sub>   | RD_B[8]          | RD_B[7]           | DGND     | V <sub>DDQ</sub> | TBC_B  | TD_B[8] | TD_B[5]          | TD_B[4] | TD_B[1]          | TD_C[1]          | TD_C[3]           | TD_C[5]          | TD_C[8] | TBC_C             | RBC0_C           | RD_C[3]          | RD_C[6] | RD_C[8]           | RD_D[9]          | V <sub>REF2</sub> | 2  |

| am          |                                          | 1  | DGND             | DGND               | RD_B[9]          | V <sub>DDQ</sub>  | RD_B[5]  | RD_B[2]          | RBC0_B | TD_B[9] | TD_B[6]          | VDDIO   | V <sub>DDQ</sub> | DGND             | TD_C[4]           | TD_C[6]          | TD_C[9] | V <sub>DDQ</sub>  | DGND             | RD_C[4]          | DGND    | RD_C[9]           | V <sub>DDQ</sub> | DGND              | -  |

| iagr        |                                          | I  | A                | -                  | U                | 0                 | ш        | Ŀ                | G      | т       | ~                | ¥       |                  | Σ                | z                 | ۵.               | ч       | -                 | D                | >                | ≥       | ~                 | AA               | AB                |    |

| Pin Diagram |                                          |    |                  |                    |                  |                   |          |                  |        |         |                  |         |                  |                  |                   |                  |         |                   |                  |                  |         |                   |                  |                   |    |

|             |                                          |    |                  |                    |                  |                   |          |                  |        |         |                  |         |                  |                  |                   |                  |         |                   |                  |                  |         |                   |                  |                   |    |

20030103

www.DataSheet4U.com

| Pin                | Pin #     | I/O,                    | Description                                                                                                        |

|--------------------|-----------|-------------------------|--------------------------------------------------------------------------------------------------------------------|

| Name               |           | Туре                    | Description                                                                                                        |

| HIGH SPEED D       |           |                         |                                                                                                                    |

| DO_A+              | D20       | O, CML                  | Inverting and non-inverting high speed CML differential outputs of the                                             |

| DO_A-              | E20       |                         | serializer, channel A. On-chip termination resistors connect from DO_A+ and                                        |

|                    |           |                         | DO_A- to V <sub>DDHS</sub> .                                                                                       |

| DO_B+              | L20       | O, CML                  | Inverting and non-inverting high speed CML differential outputs of the                                             |

| DO_B-              | K20       |                         | serializer, channel B. On-chip termination resistors connect from DO_B+ and DO_B- to $V_{DDHS}$ .                  |

| DO_C+              | M20       | O, CML                  | Inverting and non-inverting high speed CML differential outputs of the                                             |

| DO_C-              | N20       |                         | serializer, channel C. On-chip termination resistors connect from DO_C+ and DO_C- to $V_{DDHS}$ .                  |

| DO_D+              | W20       | O, CML                  | Inverting and non-inverting high speed CML differential outputs of the                                             |

| DO_D-              | V20       |                         | serializer, channel D. On-chip termination resistors connect from DO_D+ and                                        |

|                    |           |                         | DO_D- to V <sub>DDHS</sub> .                                                                                       |

|                    | Eoo       |                         | Investing and non-investing bick around differential investor of the start of the                                  |

| RI_A+              | E22       | I, CML                  | Inverting and non-inverting high speed differential inputs of the deserializer,                                    |

| RI_A–              | F22       |                         | channel A. On-chip termination resistors connect from RI_A+ and RI_A– to $V_{\text{DDHS}}$ .                       |

| RI_B+              | J22       | I, CML                  | Inverting and non-inverting high speed differential inputs of the deserializer,                                    |

| RI_B-              | H22       |                         | channel B. On-chip termination resistors connect from RI_B+ and RI_B- to                                           |

|                    |           |                         | V <sub>DDHS</sub> .                                                                                                |

| RI_C+              | P22       | I, CML                  | Inverting and non-inverting high speed differential inputs of the deserializer,                                    |

| RI_C-              | R22       |                         | channel C. On-chip termination resistors connect from RI_C+ and RI_C- to                                           |

|                    |           |                         | V <sub>DDHS</sub> .                                                                                                |

| RI_D+              | V22       | I, CML                  | Inverting and non-inverting high speed differential inputs of the deserializer,                                    |

| RI_D-              | U22       |                         | channel D. On-chip termination resistors connect from RI_D+ and RI_D- to $V_{\mbox{\scriptsize DDHS}}.$            |

| DIFFERENTIAL       | REFERENCE | CLOCK                   |                                                                                                                    |

| REFCLK+            | A15       | I, CML or AC            | Inverting and non-inverting differential reference clock to the clock                                              |

| REFCLK-            | A14       | coupled inputs          | synthesizers for clock generation. A low jitter clock source should be                                             |

|                    |           |                         | connected to REFCLK±. The REFCLK± is shared by all four channels.                                                  |

| PARALLEL I/O       | DATA      |                         |                                                                                                                    |

| TD_A[0]            | D11       | I, SSTL_18,             | Transmit data word for channel A.                                                                                  |

| TD_A[1]            | C11       | Pull-Low                | In the 10-bit mode, the 10-bit code-group at TD_A[0-9] is serialized with the                                      |

| TD_A[2]            | B11       |                         | internal 8b/10b encoder disabled. Bit 9 is the MSB.                                                                |

| TD_A[3]            | A11       |                         | In the 8-bit mode, TD_A[0–7] is first converted into 10-bit code-group by the                                      |

| TD_A[4]            | B10       |                         | internal 8b/10b encoder before it is serialized. Bit 7 is the MSB. TD_A[8] is                                      |

| TD_A[5]            | D9        |                         | used as K-code select pin. When TD_A[8] is low, TD_A[0-7] is mapped to                                             |

| TD_A[6]            | B9        |                         | the corresponding 10-bit D-group. When TD_A[8] is high, TD_A[0–7] is                                               |

| TD_A[7]            | D8        |                         | mapped to the corresponding 10-bit K-group. The 8b/10b code group                                                  |

| TD_A[8]            | C8<br>B8  |                         | conversion is implemented in according to 802.3z standard.                                                         |

| TD_A[9]            |           |                         | Transmit data word for channel R                                                                                   |

| TD_B[0]<br>TD_B[1] | L3<br>L2  | I, SSTL_18,<br>Pull-Low | Transmit data word for channel B.<br>In the 10-bit mode, the 10-bit code-group at TD_B[0-9] is serialized with the |

| TD_B[1]<br>TD_B[2] | K4        |                         | internal 8b/10b encoder disabled. Bit 9 is the MSB.                                                                |

| TD_B[3]            | K3        |                         | In the 8-bit mode, TD_B[0–7] is first converted into 10-bit code-group by the                                      |

| TD_B[4]            | K2        |                         | internal 8b/10b encoder before it is serialized. Bit 7 is the MSB. TD_B[8] is                                      |

| TD_B[5]            | J2        |                         | used as K-code select pin. When TD_B[8] is low, TD_B[0–7] is mapped to                                             |

| TD_B[6]            | J1        |                         | the corresponding 10-bit D-group. When TD_B[8] is high, TD_B[0–7] is                                               |

| TD_B[7]            | H4        |                         | mapped to the corresponding 10-bit K-group.                                                                        |

| TD_B[8]            | H2        |                         |                                                                                                                    |

| TD_B[9]            | H1        |                         |                                                                                                                    |

| Pin Desc                            | riptions | (Continued)                             |                                                                                                                    |

|-------------------------------------|----------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| Pin Desc<br>Pin Desc<br>Pin<br>Name | Pin #    | l/O,<br>Type                            | Description                                                                                                        |

| PARALLEL I/O                        | DATA     | .,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |                                                                                                                    |

| TD_C[0]                             | M3       | I, SSTL_18,                             | Transmit data word for channel C.                                                                                  |

| TD_C[1]                             | M2       | Pull-Low                                | In the 10-bit mode, the 10-bit code-group at TD_C[0–9] is serialized with                                          |

| TD_C[2]                             | N3       |                                         | internal 8b/10b encoder disabled. Bit 9 is the MSB.                                                                |

| TD_C[3]                             | N2       |                                         | In the 8-bit mode, $TD_C[0-7]$ is first converted into 10-bit code-group by                                        |

| TD_C[4]                             | N1       |                                         | internal 8b/10b encoder before it is serialized. Bit 7 is the MSB. TD_C[8]                                         |

| TD_C[5]                             | P2       |                                         | used as K-code select pin. When TD_C[8] is low, TD_C[0–7] is mapped                                                |

| TD_C[6]                             | P1       |                                         | the corresponding 10-bit D-group. When TD_C[8] is high, TD_C[0–7] is                                               |

| TD_C[7]                             | R4       |                                         | mapped to the corresponding 10-bit K-group.                                                                        |

| TD_C[8]                             | R2       |                                         |                                                                                                                    |

| TD_C[9]                             | R1       |                                         |                                                                                                                    |

| TD_D[0]                             | AA11     | I, SSTL_18,                             | Transmit data word for channel D.                                                                                  |

| TD_D[1]                             | AB11     | Pull-Low                                | In the 10-bit mode, the 10-bit code-group at TD_D[0-9] is serialized with                                          |

| TD_D[2]                             | W10      |                                         | internal 8b/10b encoder disabled. Bit 9 is the MSB.                                                                |

| TD_D[3]                             | Y10      |                                         | In the 8-bit mode, $TD_D[0-7]$ is first converted into 10-bit code-group by                                        |

| TD_D[4]                             | AA10     |                                         | internal 8b/10b encoder before it is serialized. Bit 7 is the MSB. TD_D[8]                                         |

| TD_D[5]                             | AA9      |                                         | used as K-code select pin. When TD_D[8] is low, TD_D[0-7] is mapped                                                |

| TD_D[6]                             | W8       |                                         | the corresponding 10-bit D-group. When TD_D[8] is high, TD_D[0–7] is                                               |

| TD_D[7]                             | Y8       |                                         | mapped to the corresponding 10-bit K-group.                                                                        |

| TD_D[8]                             | AA8      |                                         |                                                                                                                    |

| TD_D[9]                             | AB8      |                                         |                                                                                                                    |

| TBC_A                               | A8       | I, SSTL_18,                             | Transmit byte clock for channel A.                                                                                 |

|                                     |          | Pull-Low                                |                                                                                                                    |

| TBC_B                               | G2       | I, SSTL_18,                             | Transmit byte clock for channel B.                                                                                 |

|                                     |          | Pull-Low                                |                                                                                                                    |

| TBC_C                               | T2       | I, SSTL_18,                             | Transmit byte clock for channel C.                                                                                 |

|                                     |          | Pull-Low                                |                                                                                                                    |

| TBC_D                               | W7       | I, SSTL_18,                             | Transmit byte clock for channel D.                                                                                 |

|                                     |          | Pull-Low                                | Descriptional respire data word for sharped A                                                                      |

| RD_A[0]                             | D6<br>B6 | O, SSTL_18                              | Deserialized receive data word for channel A.                                                                      |

| RD_A[1]                             |          |                                         | In the 10-bit mode, RD_A[0–9] is the deserialized received data word in                                            |

| RD_A[2]<br>RD_A[3]                  | A6<br>D5 |                                         | 10-bit code group. Bit 9 is the MSB.<br>In the 8-bit mode, RD_A[0-7] is the deserialized received data byte. Bit 7 |

| RD_A[3]<br>RD_A[4]                  | D5<br>C5 |                                         | the MSB. RD_A[9] is the 8b/10b error monitor. RD_A[8] is the K-group                                               |

| RD_A[4]<br>RD_A[5]                  | B5       |                                         | indicator. A low at RD_A[8] indicates RD_A[0–7] belongs to the D-group,                                            |

| RD_A[5]<br>RD_A[6]                  | D4       |                                         | while a high indicates it belongs to the K-group.                                                                  |

| RD_A[0]<br>RD_A[7]                  | C4       |                                         |                                                                                                                    |

| RD_A[8]                             | B4       |                                         |                                                                                                                    |

| RD_A[0]<br>RD_A[9]                  | A3       |                                         |                                                                                                                    |

| RD_B[0]                             | F4       | O, SSTL_18                              | Deserialized receive data word for channel B.                                                                      |

| RD_B[1]                             | F3       | 0,0012_10                               | In the 10-bit mode, RD_B[0–9] is the deserialized received data word in                                            |

| RD_B[2]                             | F1       |                                         | 10-bit code group. Bit 9 is the MSB.                                                                               |

| RD_B[3]                             | E4       |                                         | In the 8-bit mode, $RD_B[0-7]$ is the deserialized received data byte. Bit 7                                       |

| RD_B[4]                             | E3       |                                         | the MSB. RD_B[9] is the 8b/10b error monitor. RD_B[8] is the K-group                                               |

| RD_B[5]                             | E1       |                                         | indicator. A low at RD_B[8] indicates RD_B[0–7] belongs to the D-group,                                            |

| RD_B[6]                             | D3       |                                         | while a high indicates it belongs to the K-group.                                                                  |

| RD_B[7]                             | D2       |                                         |                                                                                                                    |

| RD_B[8]                             | C2       |                                         |                                                                                                                    |

| RD_B[9]                             | C1       |                                         |                                                                                                                    |

| Pin<br>Name       | Pin # | I/O,<br>Type | Description                                                                                                                                                                       |

|-------------------|-------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PARALLEL I/O      | DATA  |              |                                                                                                                                                                                   |

| RD_C[0]           | U4    | O, SSTL_18   | Deserialized receive data word for channel C.                                                                                                                                     |

| RD_C[1]           | U3    |              | In the 10-bit mode, RD_C[0-9] is the deserialized received data word in                                                                                                           |

| RD_C[2]           | V4    |              | 10-bit code group. Bit 9 is the MSB.                                                                                                                                              |

| RD_C[3]           | V2    |              | In the 8-bit mode, RD_C[0-7] is the deserialized received data byte. Bit 7 is                                                                                                     |

| RD_C[4]           | V1    |              | the MSB. RD_C[9] is the 8b/10b error monitor. RD_C[8] is the K-group                                                                                                              |