# DRPIC166X

# High Performance Configurable 8-bit RISC Microcontroller ver 2.15

#### OVERVIEW

The DRPIC166X is a low-cost, high performance, 8-bit, fully static soft IP Core, dedicated for operation with **fast** (typically onchip) dual ported **memory**. The core has been designed with a special concern about **low power consumption**.

DRPIC166X soft softwarecore is compatible with the industry standard PIC16C6X. It implements an enhanced Harvard architecture (i.e. separate instruction and data memories) with independent address and data buses. The 14 bit program memory and 8-bit dual port data memory allow instruction fetch and data operations to occur simultaneously. The advantage of this architecture is instruction fetch and memory transfers can be overlapped by multi stage pipeline, so that the next instruction can be fetched from program memory while the current instruction is executed with data from the data memory. The DRPIC166X architecture is 4 times faster compared to standard architecture. So most instructions are executed within 1 system clock period, except the instructions which directly operates on program counter PC (GOTO, CALL, RETURN), this situation require the pipeline to be cleared and subsequently refilled. This operation takes additional one clock cycle.

The DRPIC166X Microcontroller fits perfectly in applications ranging from high-

All trademarks mentioned in this document are trademarks of their respective owners.

speed automotive and appliance motor control to low-power remote transmitters/receivers, pointing devices and telecom processors. Built-in power save mode make this IP perfect for applications where power consumption is critical.

DRPIC166X is delivered with fully automated testbench and complete set of tests allowing easy package validation at each stage of SoC design flow

#### **CPU FEATURES**

- Software compatible with industry standard PIC16C6X

- Pipelined Harvard architecture 4 times faster compared to original implementation

- 35 14 bit wide instructions

- Up to 512 bytes of internal Data Memory

- Up to 64K bytes of Program Memory

- Configurable hardware stack

- Power saving SLEEP mode

- Fully synthesizable, static synchronous design with no internal tri-states

- Technology independent HDL Source Code

- 1.4 GHz virtual clock frequency in a 0.18u technological process

## www.DataSheet4U PERALS

- Four 8 bit I/O ports

- Four 8-bit corresponding TRIS registers

- o Interrupt feature on PORTB(7:4) change

- Timer 0

- 8-bit timer/counter

- o Readable and Writable

- 8-bit software programmable prescaler

- Internal or external clock select

- Interrupt generation on timer overflow

- Edge select for external clock

- Timer 1

- o 16-bit timer/counter

- o 3-bit prescaler

- Internal or external clock select

- Interrupt generation on timer overflow

- Timer 2

- o 8-bit timer with prescaler

- CCP Compare-Capture-PWM

- 16 Bit Compare/Capture operations

- o 10-bit resolution PWM output

- USART

- Asynchronous full duplex

- Synchronous half duplex Master/Slave

- Watchdog Timer

- Configurable Time out period

- 7-bit software programmable prescaler

- Dedicated independent Watchdog Clock input

- Interrupt Controller

- Seven individually maskable Interrupt sources

- Two external interrupts INT Port B[7:4] change

- Five internal interrupts TIMERS 0, 1, 2, USART

- DoCD™ debug unit

- o Processor execution control

- o Run

- Halt

- Step into instruction

- Skip instruction

- o Read-write all processor contents

All trademarks mentioned in this document are trademarks of their respective owners.

- Program Counter (PC)

- o Program Memory

- Data Memory

- Special Function Registers (SFRs)

- o Hardware Stack and Stack Pointer

- Hardware execution breakpoints

- o Program Memory

- Data Memory

- Special Function Registers (SFRs)

- o Hardware breakpoints activated at a certain

- Program address (PC)

- Address by any write into memory

- o Address by any read from memory

- Address by write into memory a required data

- Address by read from memory a required data

- o Three wire communication interface

#### LICENSING

Comprehensible and clearly defined licensing methods without royalty fees make using of IP Core easy and simply.

<u>Single Design</u> license allows use IP Core in single FPGA bitstream and ASIC implementation.

<u>Unlimited Designs</u>, <u>One Year</u> licenses allow use IP Core in unlimited number of FPGA bitstreams and ASIC implementations.

In all cases number of IP Core instantiations within a design, and number of manufactured chips are unlimited. There is no time restriction except <u>One Year</u> license where time of use is limited to 12 months.

- Single Design license for

- VHDL, Verilog source code called <u>HDL</u> <u>Source</u>

- Encrypted, or plain text EDIF called <u>Netlist</u>

- One Year license for

- Encrypted Netlist only

- Unlimited Designs license for

- HDL Source

- Netlist

- Upgrade from

- Single Design to Unlimited Designs

- HDL Source to Netlist

## www.DataSheet4LLcom

- Source code:

- ◊ VHDL Source Code or/and

- ♦ VERILOG Source Code or/and

- ♦ Encrypted, or plain text EDIF netlist

- VHDL & VERILOG test bench environment

- Active-HDL automatic simulation macros

- ModelSim automatic simulation macros

- ♦ Tests with reference responses

- Technical documentation

- Installation notes

- ♦ HDL core specification

- ◊ Datasheet

- Synthesis scripts

- Example application

- Technical support

- ◊ IP Core implementation support

- ◊ 3 months maintenance

- Delivery the IP Core updates, minor and major versions changes

- Delivery the documentation updates

- · Phone & email support

#### CONFIGURATION

The following parameters of the DRPIC166X core can be easy adjusted to requirements of dedicated application and technology. Configuration of the core can be prepared by effortless changing appropriate constants in package file. There is no need to change any parts of the code.

Number of hardware stack - 1-16 levels - default 8

Memories type

- synchronous

- asynchronous

• SLEEP mode - used - unused

• WATCHDOG Timer - used / width - unused

• Timer 0, 1, 2 system - used - unused

Compare Capture PWMusedunused

- USADT - used

• USART - unused

PORTS A,B,C,Dusedunused

DoCD<sup>™</sup> Debug Unit

used

unused

All trademarks mentioned in this document are trademarks of their respective owners.

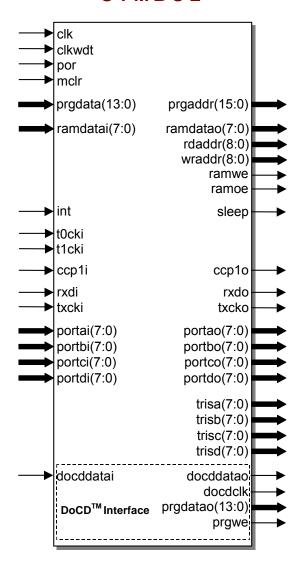

#### SYMBOL

#### PINS DESCRIPTION

| PIN           | TYPE  | DESCRIPTION                      |  |  |  |  |  |  |

|---------------|-------|----------------------------------|--|--|--|--|--|--|

| clk           | input | Global clock                     |  |  |  |  |  |  |

| clkwdt        | input | Watchdog clock                   |  |  |  |  |  |  |

| por           | input | Global reset Power On Reset      |  |  |  |  |  |  |

| mclr          | input | User reset                       |  |  |  |  |  |  |

| prgdata[13:0] | input | Data bus from program memory     |  |  |  |  |  |  |

| ramdati[7:0]  | input | Data bus from int. data memory   |  |  |  |  |  |  |

| Int           | input | External interrupt               |  |  |  |  |  |  |

| t0cki         | input | Timer 0 input                    |  |  |  |  |  |  |

| t1cki         | input | Timer 1 input                    |  |  |  |  |  |  |

| ccp1i         | input | Compare Capture channel input    |  |  |  |  |  |  |

| rxdti         | input | USART serial data input          |  |  |  |  |  |  |

| txcki         | input | USART serial clock input         |  |  |  |  |  |  |

| portxi[7:0]   | input | Port A, B, C, D input            |  |  |  |  |  |  |

| docddatai     | input | DoCD <sup>™</sup> Debugger input |  |  |  |  |  |  |

/brgatedr/15:01.0 output Program memory address bus ramdatao[7:0] output Data bus for internal data memory rdaddr[8:0] output RAM read address bus wraddr[8:0] output RAM write address bus ramwe output Data memory write ramoe output Data memory output enable Output sleep Sleep signal ccp1o Output Compare Capture channel output Output USART serial clock output txcko rxdto Output USART serial data output portxo[7:0] Output Port A, B, C, D outputs trisx[7:0] Output Ports A, B, C, D data direction pins DoCD<sup>™</sup> Debugger data output docddatao Output DoCD<sup>TM</sup> Clock line docdclk Output prgdatao[13:0] Output Program Memory data output Output Program Memory write enable prgwe

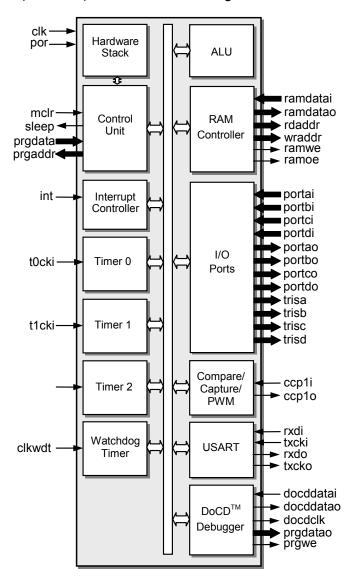

#### **BLOCK DIAGRAM**

**ALU** – Arithmetic Logic Unit performs arithmetic and logic operations during execution of an instruction. This module contains work register (W) and Status register.

**Control Unit** – It performs the core synchronization and data flow control. This module manages execution of all instructions. Performs decode and control functions for all other blocks. It contains program counter (PC) and hardware stack.

Hardware Stack – it's a configurable hardware stack. The stack space is not a part of either program or data space and the stack pointer is not readable or writable. The PC is pushed onto the stack when CALL instruction is executed or an interrupt causes a branch. The stack is popped while RETURN, RETFIE and RETLW instruction execution. The stack operates as a circular buffer. This means that after the stack has been pushed eight times, the ninth push overwrites the value that was stored from the first push.

**RAM Controller** – It performs interface functions between Data memory and DRPIC166X internal logic. It assures correct Data Memory addressing and data transfers. The DRPIC166X supports two addressing modes: direct or indirect. In Direct Addressing the 9-bit direct address is computed from RP(1:0) bits (STATUS) and 7 least significant bits of instruction word.

All trademarks mentioned in this document are trademarks of their respective owners.

Indirect addressing is possible by using the INDF register. Any instruction using INDF register actually accesses data pointed to by the file select register FSR. Reading INDF register indirectly will produce 00h. Writing to the INDF register indirectly results in a no-operation. An effective 9-bit address is obtained by concatenating the IRP bit (STATUS) and the 8-bit FSR register.

**Timer 0** – Main system's timer and prescaler. This timer operates in two modes: 8-bit timer or 8-bit counter. In the "timer mode", timer registers are incremented every 4 CLK periods. When the prescaler is assigned into the TIMER prescale ration can be divided by 2, 4 .. 256. In the "counter mode" the timer register is incremented every falling or rising edge of TOCKI pin, dependent on TOSE bit in OPTION register.

of two 8-bit registers (TMR1H and TMR1L). Timer 1 can operate either as a 16 bit timer incremented every CLK clock period or as a Counter incremented by rising edge on the T1CKI input pin. The Timer1 interrupt is generated by the timer overflow.

**Timer 2** – Is a 8-bit Timer with a prescaler and postscaler. Timer2 is suitable as PWM time-base. The Timer2 module has an 8-bit period register, PR2. Timer2 is incremented until it matches PR2 and then resets on the next increment cycle. The match output of the TMR2 register goes through a 4-bit postscaler to generate a TMR2 interrupt.

Interrupt Controller – Interrupt Controller module is responsible for interrupt manage system for the external and internal interrupt sources. It contains interrupt related registers called INTCON, PIE1, PIR1. There are seven individually maskable interrupt sources:

- ◆ Two external interrupts INT pin, PORTB change (pins B7:B4)

- ◆ Five internal interrupts Timers 0, 1, 2, USART, CCP1

The interrupt control register INTCON and PIR1 records individual interrupt requests in flag bits. A global interrupt enable bit, GIE and Peripheral interrupts enable bit, PIE enables all unmasked interrupts. Each interrupt source has an individual enable bit, which can enable or disable corresponding interrupt. When an interrupt is responded to, the GIE is cleared to disable any further interrupt, the return address is pushed into the stack and the PC is loaded with 0004h. The interrupt flag bits must be cleared in software before re-enabling interrupts.

I/O Ports - Block contains DRPIC166X's general purpose I/O ports and data direction registers (TRIS). The DRPIC166X has four 8bit full bi-directional ports PORT A, PORT B, PORT C, PORT D. Each port's bit can be individually accessed by bit addressable instructions. Read and write accesses to the I/O port are performed via their corresponding SFR's PORTA, PORTB, PORTC, PORTD. The reading instruction always reads the status of Port pins. Writing instructions always write into the Port latches. Each port's pin has an corresponding bit in TRISA, B, C and D registers. When the bit of TRIS register is set this means that the corresponding bit of port is All trademarks mentioned in this document

are trademarks of their respective owners.

configured as an input (output drivers are set into the High Impedance).

**CCP/PWM** – The CCP module contains a 16-bit register which can operate as a 16-bit capture register, 16-bit compare register, or as a PWM master/slave duty cycle register.

Watchdog Timer— it's a free running timer. WDT has own clock input separate from system clock. It means that the WDT will run even if the system clock is stopped by execution of SLEEP instruction. During normal operation, a WDT time-out generates a Watchdog reset. If the device is in SLEEP mode the WDT time-out causes the device to wake-up and continue with normal operation.

USART – The Universal Synchronous Asynchronous Receiver Transmitter module is also known as a Serial Communication Interface (SCI). The USART can be configured as a full duplex asynchronous system that can communicate with peripheral devices or it can be configured as a half duplex synchronous system (Master or Slave).

**DoCD™ Debug Unit** – it's a real-time hardware debugger provides debugging capability of a whole SoC system. In contrast to other on-chip debuggers DoCD™ provides non-intrusive debugging of running application. It can halt, run, step into or skip an instruction, read/write any contents of microcontroller including all registers, internal, program memories, all SFRs external. including user defined peripherals. Hardware breakpoints can be set and controlled on program memory, internal and external data memories, as well as on SFRs. Hardware breakpoint is executed if any write/read occurred at particular address with certain data pattern or without pattern. The DoCD™ system includes three-wire interface and complete set of tools to communicate and work with core in real time debugging. It is built as scalable unit and some features can be turned off to save silicon and reduce power consumption. A special care on power consumption has been taken, and when debugger is not used it is automatically switched in power save mode. Finally whole debugger is turned off when debug option is no longer used.

# WWW.DataSheet4U.com OPTIONAL PERIPHERALS

There are also available an optional peripherals, not included in presented DRPIC166X Microcontroller Core. The optional peripherals, can be implemented in microcontroller core upon customer request.

- SPI Master and Slave Serial Peripheral Interface

- Supports speeds up ¼ of system clock

- Mode fault error

- Write collision error

- Software selectable polarity and phase of serial clock SCK

- o System errors detection

- Allows operation from a wide range of system clock frequencies (build-in 5-bit timer)

- Interrupt generation

- I2C bus controller Master

- 7-bit and 10-bit addressing modes

- o NORMAL, FAST, HIGH speeds

- Multi-master systems supported

- Clock arbitration and synchronization

- User defined timings on I2C lines

- Wide range of system clock frequencies

- Interrupt generation

- I2C bus controller Slave

- o NORMAL speed 100 kbs

- o FAST speed 400 kbs

- o HIGH speed 3400 kbs

- Wide range of system clock frequencies

- User defined data setup time on I2C lines

- o Interrupt generation

#### PERFORMANCE

The following table gives a survey about the Core area and performance in the ALTERA® devices after Place & Route:

| Device     | Speed grade | Logic Cells | F <sub>max</sub> |  |  |  |  |

|------------|-------------|-------------|------------------|--|--|--|--|

| CYCLONE    | -6          | 1654        | 81 MHz           |  |  |  |  |

| CYCLONE II | -6          | 1654        | 72 MHz           |  |  |  |  |

| STRATIX    | -5          | 1655        | 86 MHz           |  |  |  |  |

| STRATIX II | -3          | 1401        | 166 MHz          |  |  |  |  |

| STRATIX GX | -5          | 1655        | 84 MHz           |  |  |  |  |

| APEX II    | -7          | 1695        | 74 MHz           |  |  |  |  |

| APEX20KC   | -7          | 1695        | 64 MHz           |  |  |  |  |

| APEX20KE   | -1          | 1695        | 54 MHz           |  |  |  |  |

| APEX20K    | -1          | 1695        | 50 MHz           |  |  |  |  |

| ACEX1K     | -1          | 1695        | 52 MHz           |  |  |  |  |

| FLEX10KE   | -1          | 1695        | 54 MHz           |  |  |  |  |

Core performance in ALTERA® devices

Area utilized by the each unit of DRPIC166X core in vendor specific technologies is summarized in table below.

| Component      | Area  |       |  |  |  |  |  |

|----------------|-------|-------|--|--|--|--|--|

|                | [LC]  | [FFs] |  |  |  |  |  |

| CPU*           | 904   | 296   |  |  |  |  |  |

| Timer 0        | 60    | 29    |  |  |  |  |  |

| Timer 1        | 81    | 30    |  |  |  |  |  |

| Timer 2        | 90    | 34    |  |  |  |  |  |

| USART          | 257   | 100   |  |  |  |  |  |

| CCP1           | 111   | 32    |  |  |  |  |  |

| Watchdog Timer | 55    | 38    |  |  |  |  |  |

| I/O Ports      | 96    | 64    |  |  |  |  |  |

| Total area     | 1 654 | 625   |  |  |  |  |  |

\*CPU – consisted of ALU, Control Unit, Bus Controller, Hardware Stack, External INT pin Interrupt Controller, Extended interrupt controller,(512 Bytes RAM and 8kW of program memory)

Core components area utilization

### www.DataSheet4U CAM PROVEMENT

Most instruction of DRPIC166X is executed within 1 CLK period, except program branches that require 2 CLK periods. The table below shows sample instructions execution times:

| Mnemonic operands | DRPIC166X<br>(CLK cycles) | PIC16C6X<br>(CLK cycles) | Impr. |

|-------------------|---------------------------|--------------------------|-------|

| ADDWF             | 1                         | 4                        | 4     |

| ANDWF             | 1                         | 4                        | 4     |

| RLF               | 1                         | 4                        | 4     |

| BCF               | 1                         | 4                        | 4     |

| DECFSZ            | 1(2) <sup>1</sup>         | 4(8) <sup>1</sup>        | 4     |

| INCFSZ            | 1(2) <sup>1</sup>         | 4(8) <sup>1</sup>        | 4     |

| BTFSC             | 1(2) <sup>1</sup>         | 4(8) <sup>1</sup>        | 4     |

| BTFSS             | 1(2) <sup>1</sup>         | 4(8) <sup>1</sup>        | 4     |

| CALL              | 2                         | 8                        | 4     |

| GOTO              | 2                         | 8                        | 4     |

| RETFIE            | 2                         | 8                        | 4     |

| RETLW             | 2                         | 8                        | 4     |

| RETURN            | 2                         | 8                        | 4     |

<sup>-</sup> number of clock in case that result of operation is 0.

#### DFPIC&DRPIC FAMILY OVERVIEW

The family of DCD DFPICXX & DRPICXX IP Cores combine a high–performance, low cost, and small compact size, offering the best price/performance ratio in the IP Market. The DCD's Cores are dedicated for use in cost-sensitive consumer products, computer peripherals, office automation, automotive control systems, security and telecommunication applications.

DCD's DFPICXX & DRPICXX IP Cores family contains four 8-bit microcontroller Cores to best meet your needs: DFPIC165X 12-bit program word, DFPIC1655X 14-bit program word, and DRPIC1655X and DRPIC166X single cycle microcontrollers with 14-bit program word. All three microcontroller cores are binary compatible with widely accepted PIC16C5X and PIC16CXXX. They employ a modified RISC architecture two or four times faster than the original ones.

The DFPICXXX & DRPICXX IP Cores are written in pure VHDL/VERILOG HDL languages which make them technologically independent. All of the DFPICXX & DRPICXX family members supports a power saving SLEEP mode and allows the user to configure the watchdog time-out period and a number of hardware stack levels. DFPICXX & DRPICXX can be fully customized according to customer needs.

| Design     | Program Memory space | Data Memory space | Program word length | Number of instructions | ort | Timer 0      | Timer 1 | Timer 2 | Watchdog Timer | CCP1 | USART | Sleep Mode   | External interrupts | Internal<br>Interrupts | Levels of hardware stack | Wake up on port pin change | Speed rate | DoCD <sup>™</sup><br>Debugger | Size (gate) |

|------------|----------------------|-------------------|---------------------|------------------------|-----|--------------|---------|---------|----------------|------|-------|--------------|---------------------|------------------------|--------------------------|----------------------------|------------|-------------------------------|-------------|

| DFPIC165X  | 2k                   | 128               | 12                  | 33                     | 24  | ✓            | -       | -       | ✓              | -    | -     | ✓            | -                   | -                      | 2                        | -                          | 2          |                               | 2 700       |

| DFPIC1655X | 64k                  | 512               | 14                  | 35                     | 16  | ✓            | -       | -       | $\checkmark$   | -    | -     | $\checkmark$ | 5                   | 1                      | 8                        | $\checkmark$               | 2          | <b>√</b> *                    | 3 900       |

| DRPIC1655X | 64k                  | 512               | 14                  | 35                     | 32  | $\checkmark$ | -       | -       | ✓              | -    | -     | ✓            | 5                   | 1                      | 8                        | ✓                          | 4          | <b>√</b> *                    | 4 800       |

| DRPIC166X  | 64k                  | 512               | 14                  | 35                     | 32  | ✓            | ✓       | ✓       | ✓              | ✓    | ✓     | ✓            | 5                   | 5                      | 8                        | ✓                          | 4          | <b>√</b> *                    | 6 700       |

<sup>\*</sup> Optional

DFPIC & DRPIC family of High Performance Microcontroller Cores

## www.DataSheet4U.com CONTACTS

For any modification or special request please contact to Digital Core Design or local distributors.

#### **Headquarters:**

Wroclawska 94

41-902 Bytom, POLAND

e-mail: info@dcd.pl

tel. : +48 32 282 82 66 fax : +48 32 282 74 37

#### **Distributors:**

Please check http://www.dcd.pl/apartn.php