# **DP8350 Series Programmable CRT Controllers**

# National Semiconductor

# **DP8350 Series Programmable CRT Controllers**

# **General Description**

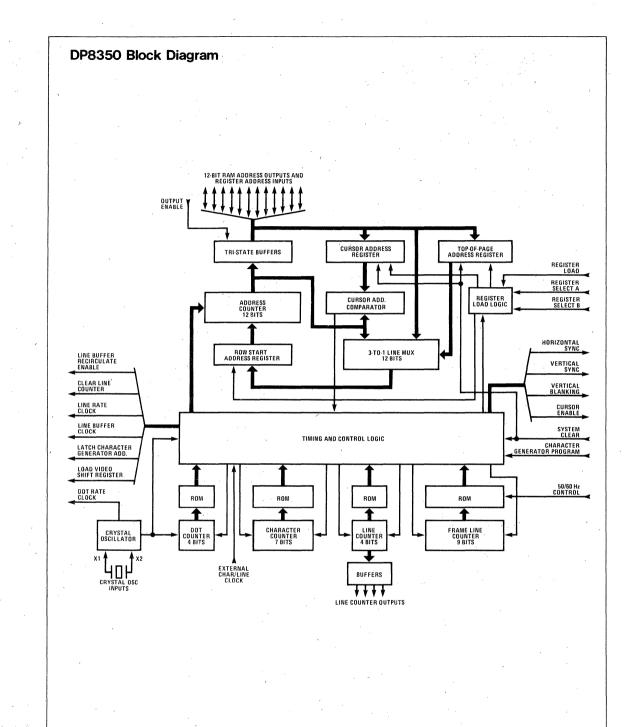

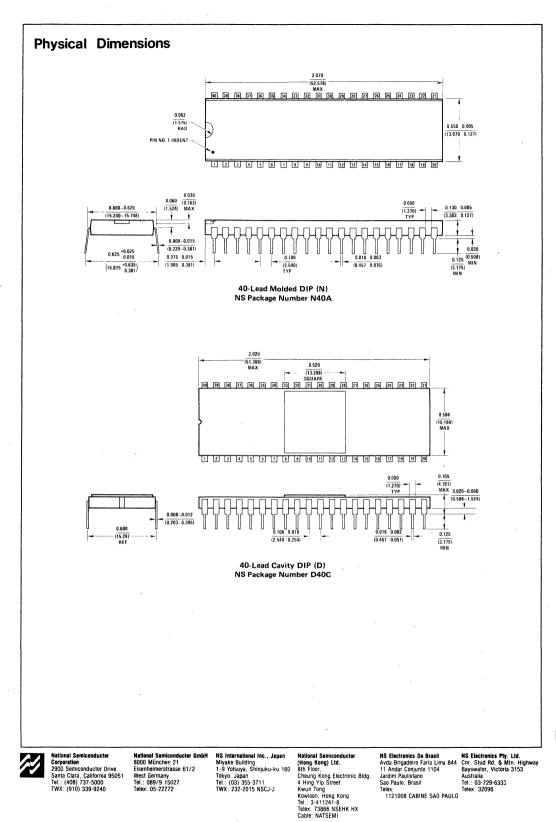

The DP8350 Series of CRT Controllers are single-chip bipolar ( $1^2$ L technology) circuits in a 40-pin package. They are designed to be dedicated CRT display refresh circuits.

The CRT Controller (CRTC) provides an internal dot rate crystal controlled oscillator for ease of system design. For systems where a dot rate clock is already provided, an external clock input may be used by the CRTC. In either case system synchronization is made possible with the use of the buffered Dot Rate Clock Output.

The DP8350 Series has 11 character generation related timing outputs. These outputs are compatible for systems with or without line buffers, using character ROMS, or DM8678-type latch/ROM/shift register circuits.

12 bits (4k) of bidirectional TRI-STATE  $^{\textcircled{B}}$  character memory addresses are provided by the CRTC for direct interface to character memory.

Three on-chip registers provide for external loading of the row starting address, cursor address, and top-of-page address.

A complete set of video outputs is available including cursor enable, programmable vertical blanking, programmable horizontal sync, and programmable vertical sync.

The DP8350 Series CRTC provides for a wide range of programmability using internal mask programmable ROMs:

- Character Field (both number of dots/character and number of scan lines/character)

- Characters per Row

- Character Rows per Video Frame

The CRTC also provides system sync and program inputs including 50/60 Hz control, system clear, external character/line rate clock, and character generator program.

The DP8350 Series operates on a single +5 V power supply. Outputs and inputs are TTL compatible.

# Features

- Internal crystal controlled dot rate oscillator

- External dot rate clock input

- Buffered dot rate clock output

- Timing pulses for character generation

- Character memory address outputs (12 bits)

- Internal cursor address register

- Internal row starting address register

- Top-of-page address register (for scrolling)

- Programmable horizontal and vertical sync outputs

- Programmable cursor enable output

- Programmable vertical blanking output

- 50/60 Hz refresh rate

- Programmable characters/row (5 to 110)

- Programmable character field size (up to 16 dots x 16 scan line field size)

- Programmable character rows/frame (1 to 64)

- Single +5 V power supply

- Inputs and outputs TTL compatible

- Ease of system design/application

© 1978 National Semiconductor Corp

D-60

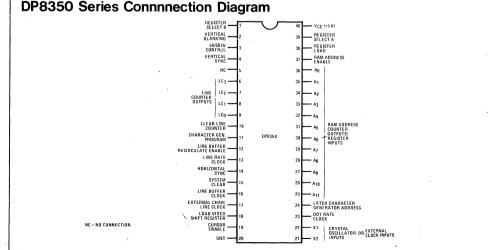

## **DP8350 Functional Pin Description**

### CHARACTER GENERATION/TIMING OUTPUTS

The CRTC provides 11 interface timing outputs for line buffers, character generator ROM, DM8678-type latch/ ROM/shift register combination character generators, and system status timing. All outputs are TTL compatible and directly interface to popular system circuits, including:

- DM8678 Series Character Generators

- MM52157, MM52179 Character ROMs

- DM74166 Dot Shift Register

- MK1007P, 33571/2, 2532 80-Bit Shift Registers (Line Buffers)

**Dot Rate Clock:** This output is buffered for use in system synchronization and interface to dot shift register. Positive edge clock at crystal oscillator frequency.

Load Video Shift Register: Buffered output at character rate frequency. Used for direct interface to dot shift register. This output is active only during video time and therefore performs both the horizontal and vertical blanking functions. Low level active.

Latch Character Generator Address: Buffered output at character rate frequency. Active at all times. Positive edge clock.

Line Buffer Clock: This output directly interfaces to line buffers. Output operates at character rate. Negative edge clock. Not active during horizontal blanking. The number of clocks per scan line is equivalent to the number of video characters per row.

Line Rate Clock: Line rate frequency output for use with DM8678-type character generator.

Line Counter Outputs (LC0 to LC3): Buffered outputs at line rate frequency for use with character ROMs without internal line counter. These outputs are also useful for system decode of present line position in character row. Outputs clock in sync with Line Rate Clock at start of horizontal blanking. Outputs are always active.

**Clear Line Counter:** Row rate clock – occurs in sync with Line Rate Clock during horizontal blanking between last line of any row and first line of a new row. This output is always active and is a negative edge clock – direct interface to the DM8678.

Line Buffer Recirculate Enable: This output interfaces to a line buffer and becomes inactive (logic "0" state) during the last line or the first line of a character row, depending on the state of the character generator program input. A low level on this output indicates (in line buffer applications) the time during which the line buffer is loaded with the next row of character codes.

### Table 1. Character Generator Program Truth Table

| Character Generator<br>Program Input | Recirculate Enable Output<br>Low Level and New Row<br>Address at Address Outputs |  |

|--------------------------------------|----------------------------------------------------------------------------------|--|

| "0"                                  | Last line of character row                                                       |  |

| "1"                                  | First line of character row                                                      |  |

The pulse appears at the start of horizontal blanking prior to when the memory address bus must be transferred to the CRTC, then returns to the high state at the next horizontal blanking interval.

### MEMORY ADDRESS OUTPUTS/INPUTS AND REGISTERS

**CRT Character Address Outputs (TRI-STATE)** – A<sub>0</sub> to A<sub>11</sub>: 12 bits of bidirectional CRT character address counter outputs are provided by the CRTC. These outputs directly interface to the system RAM memory address bus.

Within a scan line the counter is pre-set to the address contained within the Row Start Register (RSR) three character times before the start of video time. The counter is then advanced sequentially at character rate to the max video character address plus 1 for the present scan line. This address is then held during the horizontal blanking interval up to three character times before video start for the next scan line. At this point the counter is again pre-set to the contents of the RSR and the above sequence is repeated. This sequence provides scan line address repetition for every scan line of a character location within a row. Row-to-row start address modifications are accomplished by updating the contents of the RSR.

During vertical blanking the address counter operation is modified by stopping the pre-set load of the contents of the RSR into the address counter, thereby allowing the address outputs to free run during vertical blanking. This allows minimum access time to the CRTC when the CRTC address counter outputs are being used for dynamic RAM refresh.

**RAM Address Enable Input:** At all times the status of the address counter outputs is controlled externally by the Enable Input. Logic "0" = TRI-STATE, Logic "1" = Active.

Internal Top-of-Page, Row Start, and Cursor Registers: Control pins are provided for loading the top-of-page, row start, and cursor address into three 12-bit CRTC registers from the bidirectional memory address pins.

The Top-of-Page Register (TOPR) holds the address of the first character of the first video row. This register allows display scroll with the CRTC without the use of external memory address adders. If the TOPR is not loaded after a system clear its contents will be zero and the address outputs will be sequential from zero at the top-of-page.

The Cursor Register (CR) holds the present address of the cursor and is cleared to zero after a system clear. Once the TOPR and CR registers have been loaded they need not be accessed again until modification of their contents is required. These registers may be loaded at any time, but to cause minimum display distortion it is recommended that they be loaded only during blanking intervals. The Row Start Register (RSR) is the working register for the CRTC address counter. It determines the first video character address on a scan line to scan line basis.

Modification of this register after the start of video in a scan line will modify the address counter outputs at the start of video on the next scan line. (See address output description.) If the RSR is never externally loaded, the CRTC address outputs will be sequential on a row-to-row basis from the TOPR contents at the start of the video page. With external loading, row-to-row non-sequential operation of the CRTC address outputs is possible, thus row-to-row edit capability. When used in this mode the RSR should be loaded after the start of video time of the last scan line of the previous row. A load to the RSR during vertical blanking will also load the TOPR.

### Table 2. Register Load Truth Table

| Register<br>Select<br>A | Register<br>Select<br>B | Register<br>Load<br>Input | Register<br>Access |

|-------------------------|-------------------------|---------------------------|--------------------|

| 0                       | 0                       | 0 ·                       | No Select          |

| 0                       | 1                       | 0                         | Top-of-Page        |

| 1                       | 0                       | Ó                         | Row Start*         |

| 1                       | 1                       | 0                         | Cursor             |

| х                       | X                       | 1                         | No Select          |

\*During vertical blanking a load to this register will also load the top-of-page register.

### VIDEO RELATED OUTPUTS

Horizontal Sync: This output provides the necessary line (scan) rate sync to either three-terminal or composite sync monitors. The pulse is programmable in position and width at character time increments. This output may also be programmed to have RS-170 compatible serration pulses during the vertical sync interval. The active logic state of this output is also programmable.

Vertical Sync: This output provides the necessary frame rate sync consistent with either three-terminal or composite type monitors. The pulse is programmable in position and width at line (scan) time increments. The active logic state of this output is also programmable.

**Cursor Enable:** When a match with the CRTC cursor address register and address counter occurs a pulse will appear at this output at that video character time (character field width) for every line in that row. This output may also be programmed to appear on only one line of a character row. With the character generator program pin in a logic "O" position the cursor enable output will not be valid on the last line of a character row for that row. Like the Load Video Shift Register Output, this output is not active during horizontal or vertical blanking. High level active output.

### CRT SYSTEM CONTROL FUNCTIONS

50/60 Hz Control Input: This input controls the CRT system refresh rate. The CRTC may also be programmed for refresh rates other than 50 and 60 Hz.

| 50/60 Hz<br>Control | Refresh<br>Rate         |

|---------------------|-------------------------|

| 1.                  | 60 Hz (f <sub>1</sub> ) |

| 0                   | 50 Hz (f <sub>0</sub> ) |

Vertical Blanking Output: This output becomes active (logic "1") at the start of vertical blanking and may be programmed to stop at the end of any line of the character row before the start of the first video row. This output is useful for flag applications to other elements in the CRT system. Its active level is also programmable.

System Clear Input: This input when low sets and holds the CRTC at the start of vertical blanking for system sync and test. It also clears to zero the cursor and topof-page registers. The input has hysteresis and may be connected to a resistor to  $V_{CC}$  and a capacitor to ground to provide power-up system clear.

Character Generator Program Input: This input modifies both the position of the recirculate enable output low level and the time at which the address outputs change to a new row address. It is intended to provide optimum use of the CRTC with character generator/ROMs programmed with or without active video on the first or last line of a character row. (See Recirculate Enable for truth table.)

External Character/Line Rate Clock: This input is intended to aid testing of the CRTC and is not meant to be used as an active input in a CRT system. When this input is left open it is guaranteed not to interfere with normal operation.

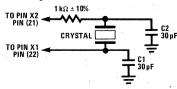

**Crystal Inputs X1 and X2:** The oscillator is controlled by an external, parallel resonant crystal connected between the X1 and X2 pins. Normally, a fundamental mode crystal is used to determine the operating frequency of the oscillator; however, overtone mode crystals may be used.

### Crystal Specifications (parallel resonant):

| Type                                                                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------|

| Tolerance 0.005% at 25°C                                                                                                      |

| Stability $\dots \dots \dots$ |

| Resonance Fundamental (parallel)                                                                                              |

| Maximum Series Resistance Dependent on                                                                                        |

| frequency                                                                                                                     |

| (for 10.92 MHz, 50 Ω)                                                                                                         |

| Load Capacitance                                                                                                              |

**Connection Diagram**

If the DP8350 series is clocked at dot rate by a system clock, pin 22 (X1 input) should be clocked directly using a Schottky series circuit. Pin 21 (X2 input) may be left open.

D-63

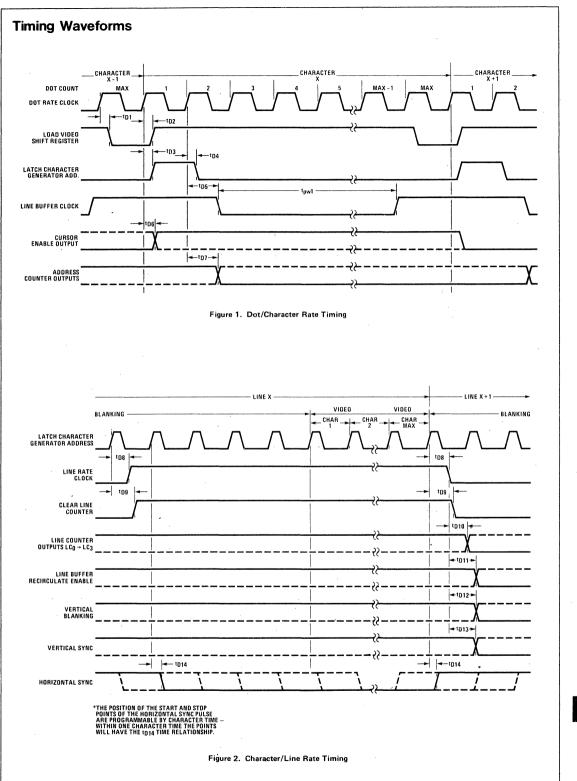

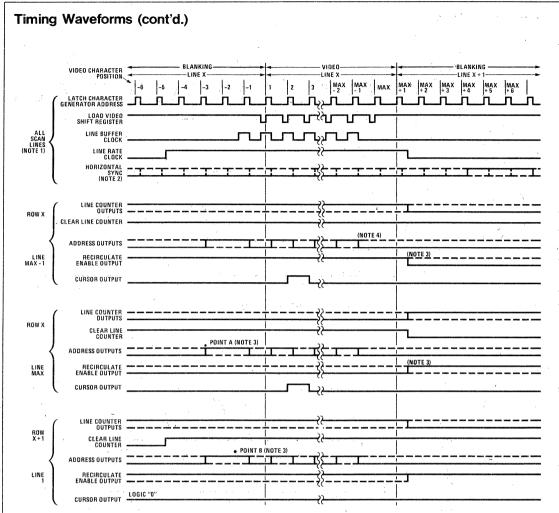

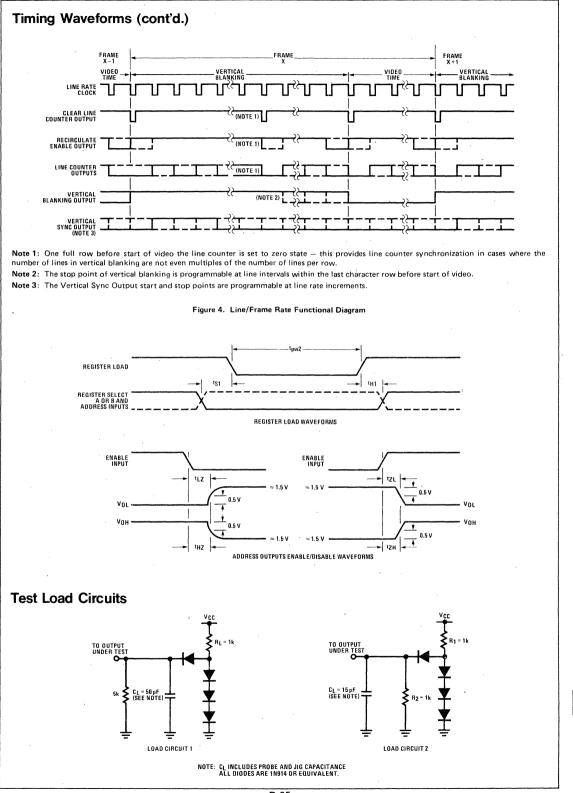

Note 1: The load video shift register output is not active during vertical or horizontal blanking (remains in the logic "1" state during these intervals.

Note 2: The horizontal sync output start and stop point positions are user-programmable at character width intervals.

Note 3: The position of the recirculate enable output logic "0" level is dependent on the state of the character generator program input (CGPI). With CGPI = "0," recirculate enable occurs on the max line of a character row (solid line) and the address counter outputs roll over to the new row address at point A. With CGPI = "1," recirculate enable occurs on the first line of a character row (dashed line) and the address counter outputs roll over to the new row address at point B.

Note 4: The address counter outputs clock to the address of the last character of a video row plus 1. This address is then held during the horizontal blanking interval until video minus three character times. At this point the outputs are modified to the contents of the Row Start Register (RSR). With no external loading of the RSR the contents will be either the character address of the first character in the present row or the character address of the first character address of the first character of the next video row (depending on the state of the Character Generator Program input) which will be sequential from the last character address of the last chara

Figure 3. Character/Line Rate Functional Diagram

D-65

$\mathcal{R}$

# Absolute Maximum Ratings (Note 1)

# **Operating Conditions**

| Supply Voltage, VCC          | 7.0 V             |

|------------------------------|-------------------|

| Input Voltage                | –1 V to +5.5 V    |

| Output Voltage               | 5.5 V             |

| Storage Temperature Range    | -65°C to +150°C   |

| Lead Temperature (soldering, | 10 seconds) 300°C |

MinMaxUnitsV<sub>CC</sub>, Supply Voltage4.755.25VTA, Ambient Temperature0+70°C

# **Electrical Characteristics** $V_{CC} = 5 V \pm 5\%$ , $T_A = 0^{\circ}C$ to +70°C (Notes 2 and 3)

| Parameter          |                                                                              | Conditions                                                               | Min  | Тур  | Max | Units |

|--------------------|------------------------------------------------------------------------------|--------------------------------------------------------------------------|------|------|-----|-------|

| VIH                | Logic "1" Input Voltage<br>(System Clear)                                    |                                                                          | 2.6  |      |     | v     |

|                    | (All Other Inputs Except X1, X2)                                             |                                                                          | 2.0  |      |     | V     |

| VIL                | Logic "O" Input Voltage<br>(System Clear)                                    |                                                                          |      |      | 0.8 | v     |

|                    | (All Other Inputs Except X1, X2)                                             |                                                                          |      |      | 0.8 | v     |

| VIH-VIL            | System Clear Input Hysteresis                                                |                                                                          |      | 0.4  |     | v     |

| V <sub>clamp</sub> | Input Clamp Voltage<br>(All Inputs Except X1, X2, &<br>Char/Line Rate Clock) | I <sub>IN</sub> = −12 mA                                                 |      | -0.8 |     | V     |

| IH.                | Logic "1" Input Current<br>(Address Outputs)                                 | Enable Input = 0 V,<br>V <sub>CC</sub> = 5.25 V, V <sub>R</sub> = 5.25 V |      | 10   |     | μA    |

|                    | (All Other Inputs Except X1, X2)                                             | V <sub>CC</sub> = 5.25 V, V <sub>R</sub> = 5.25 V                        |      | 2    |     | μA    |

| ΙIL                | Input Current<br>(Address Outputs)                                           | Enable Input = 0 V,<br>V <sub>CC</sub> = 5.25 V, V <sub>IN</sub> = 0.5 V |      | -20  |     | μΑ    |

|                    | (All Other Inputs Except X1, X2)                                             | V <sub>CC</sub> = 5.25 V, V <sub>IN</sub> = 0.5 V                        |      | -20  |     | μA    |

| Vон                | Logic "1" Output Voltage                                                     | I <sub>OH</sub> = -100 μA                                                | 3.2  | 4.1  |     | V     |

|                    | · · · · · · · · · · · · · · · · · · ·                                        | I <sub>OH</sub> = -1 mA                                                  | 2.5  | 3.3  |     | , V   |

| VOL                | Logic "0" Output Voltage                                                     | IOL = 5 mA                                                               |      | 0.35 | 0.5 | V     |

| Ios                | Output Short Circuit Current                                                 | V <sub>CC</sub> = 5 V, V <sub>OUT</sub> = 0 V,<br>(Note 4)               | <br> | -40  |     | mA    |

| lcc                | Power Supply Current                                                         | V <sub>CC</sub> = 5.25 V                                                 |      | 170  |     | mA    |

Note 1: "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. They are not meant to imply that the device should be operated at these limits. The table of "Electrical Characteristics" provides conditions for actual device operation. Note 2: Unless otherwise specified, min/max limits apply across the 0°C to  $+70^{\circ}$ C temperature range and the 4.75 V to 5.25 V power supply range. All typical values are for T<sub>A</sub> = 25°C and V<sub>CC</sub> = 5.0 V.

Note 3: All currents into device pins are shown as positive; all currents out of device pins are shown as negative; all voltages are referenced to ground, unless otherwise specified. All values shown as max or min are so classified on absolute value basis.

Note 4: Only one output at a time should be shorted.

|                                   | Parameter                                                                            | Conditions                                                              | Min | Тур     | Max | Unit |

|-----------------------------------|--------------------------------------------------------------------------------------|-------------------------------------------------------------------------|-----|---------|-----|------|

| <sup>t</sup> D1                   | Dot Clock to Load Video Shift<br>Register Negative Edge                              | C <sub>L</sub> = <b>50</b> pF, R <sub>L</sub> = 1 kΩ,<br>Load Circuit 1 |     | 5       |     | ns   |

| <sup>t</sup> D2                   | Dot Clock to Load Video Shift<br>Register Positive Edge                              | $C_L = 50 pF, R_L = 1 k\Omega,$<br>Load Circuit 1                       |     | 11      |     | ns   |

| tD3                               | Dot Clock to Latch Character<br>Generator Positive Edge                              | $C_L = 50 pF, R_L = 1 k\Omega,$<br>Load Circuit 1                       |     | 11      |     | ns   |

| <sup>t</sup> D4                   | Dot Clock to Latch Character<br>Generator Negative Edge                              | $C_L = 50 pF, R_L = 1 k\Omega,$<br>Load Circuit 1                       |     | 4       |     | ns   |

| <sup>t</sup> D5                   | Dot Clock to Line Buffer<br>Clock Negative Edge                                      | C <sub>L</sub> = <b>50</b> pF, R <sub>L</sub> = 1 kΩ,<br>Load Circuit 1 |     | 20      |     | ns   |

| <sup>t</sup> PW1                  | Line Buffer Clock Pulse Width                                                        | $C_L = 50 pF, R_L = 1 k\Omega,$<br>Load Circuit 1                       |     | N (DT)* |     | ns   |

| <sup>t</sup> D6                   | Dot Clock to Cursor Enable<br>Output Transition                                      | C <b>L = 50</b> pF, R <b>L =</b> 1 kΩ,<br>Load Circuit 1                |     | 25      |     | ns   |

| tD7                               | Dot Clock to Valid Address<br>Output                                                 | $C_L = 50 pF, R_L = 1 k\Omega,$<br>Load Circuit 1                       |     | 20      |     | ns   |

| tD8                               | Latch Character Generator to<br>Line Rate Clock Transition                           | $C_L = 50 pF, R_L = 1 k\Omega,$<br>Load Circuit 1                       |     | 300+2DT |     | ns   |

| tD9                               | Latch Character Generator to<br>Clear Line Counter Transition                        | CL = <b>50</b> pF, RL = 1 kΩ,<br>Load Circuit 1                         |     | 400+2DT |     | ns   |

| <sup>t</sup> D10                  | Line Rate Clock to Line<br>Counter Output Transition                                 | C <b>L = 50</b> pF, R <b>L =</b> 1 kΩ,<br>Load Circuit 1                |     | 180     |     | ns   |

| <sup>t</sup> D11                  | Line Rate Clock to Line Buffer<br>Recirculate Enable Transition                      | CL = <b>50</b> pF, RL = 1 kΩ,<br>Load Circuit 1                         |     | 200     |     | ns   |

| <sup>t</sup> D12                  | Line Rate Clock to Vertical<br>Blanking Transition                                   | C <sub>L</sub> = <b>50</b> pF, R <sub>L</sub> = 1 kΩ,<br>Load Circuit 1 |     | 200     |     | ns   |

| <sup>t</sup> D13                  | Line Rate Clock to Vertical Sync Transition                                          | CL= <b>50</b> pF, RL=1kΩ,<br>Load Circuit 1                             |     | 200     |     | ns   |

| <sup>t</sup> D14                  | Latch Character Generator to<br>Horizontal Sync Transition                           | $C_L = 50 pF, R_L = 1 k\Omega,$<br>Load Circuit 1                       |     | 100     |     | ns   |

| tSI                               | Register Select/Memory<br>Address Setup Time Prior to<br>Register Load Negative Edge |                                                                         |     | 100     |     | ns   |

| tHI                               | Register Select Memory Hold<br>Time After Register Load<br>Positive Edge             |                                                                         |     | 0       |     | ns   |

| tPW2                              | Register Load Pulse Width                                                            |                                                                         |     | 150     |     | ns   |

| fMAXdot                           | Maximum Dot Rate Frequency                                                           | 1                                                                       |     | 25      |     | MHẓ  |

| fMAXchar                          | Maximum Character Rate<br>Frequency                                                  |                                                                         |     | 2.5     |     | MHz  |

| <sup>t</sup> LZ <sup>, t</sup> HZ | Delay from Enable Input to<br>High Impedance State from<br>Logic "0" and Logic "1"   | CL = 15 pF, Load Circuit 2                                              | •   | 25      | ÷   | ns   |

| <sup>t</sup> ZL <sup>, t</sup> ZH | Delay from Enable Input to<br>Logic "0" and Logic "1" from<br>High Impedance State   | CL = 15 pF, Load Circuit 2                                              |     | 25      |     | ns   |

Note 1: Unless otherwise specified, all AC measurements are referenced to the 1.5 V level of the input to 1.5 V of the output.

Note 2: When external clock inputs are used, the input characteristics are Z<sub>OUT</sub> = 50  $\Omega$  and t<sub>R</sub>  $\leq$  10 ns, t<sub>F</sub>  $\leq$  10 ns.

\*"DT" is defined as the duration (in ns) of one full cycle of the Dot Rate Clock (Item 20 of the ROM Program Table). "N" denotes the number of DTs per definition in Item 24 of the ROM Program Table.

# DP8350 Series Option Program Table (Notes 1, 2, and 3)

| Item<br>No. |                                                                                                             | Parameter                                                     |      | Value<br>• |  |

|-------------|-------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|------|------------|--|

| 1           | Ohanatan (Earth Siza)                                                                                       | Dots per Character                                            |      |            |  |

| 2           | Character (Font Size)                                                                                       | Scan Lines per Character                                      | 5    |            |  |

| 3           |                                                                                                             | Dots per Character                                            |      |            |  |

| 4           | Character Field (Block Size)                                                                                | Scan Lines per Character                                      |      |            |  |

| 5           | Number of Video Characters p                                                                                | er Row                                                        |      |            |  |

| 6           | Number of Video Character R                                                                                 | ows per Frame                                                 | j.   |            |  |

| 7           | Number of Video Scan Lines (                                                                                | Item 4 x Item 6)                                              |      |            |  |

| 8           | Frame Refresh Rate (Hz) (two                                                                                | frequencies allowed)                                          | f1 = | f0 =       |  |

| 9           | Delay after/before Vertical Bla                                                                             | nk start to start of Vertical Sync (+/- Number of Scan Lines) |      |            |  |

| 10          | Vertical Sync Width (Number                                                                                 | of Scan Lines)                                                |      |            |  |

| 11          | Delay after Vertical Blank star                                                                             | t to start of Video (Number of Scan Lines)                    |      |            |  |

| 12          | Total Scan Lines per Frame (I                                                                               | tem 7 + Item 11 = Item 13 ÷ Item 8)                           |      |            |  |

| 13          | Horizontal Scan Frequency (Line Rate) (kHz) Item 8 x Item 12)                                               |                                                               |      |            |  |

| 14          | Number of Character Times per Scan Line                                                                     |                                                               |      |            |  |

| 15          | Character Clock Rate (MHz) Item 13 x Item 14)                                                               |                                                               |      |            |  |

| 16          | Character Time (ns) (1 ÷ Item 15)                                                                           |                                                               |      |            |  |

| 17          | Delay after/before Horizontal Blank start to Horizontal Sync Start (+/- Character Times)                    |                                                               |      |            |  |

| 18          | Horizontal Sync Width (Character Times)                                                                     |                                                               |      |            |  |

| 19          | Dot Frequency (MHz) (Item 3 x Item 15)                                                                      |                                                               |      |            |  |

| 20          | Dot Time (ns) (1 ÷ Item 19)                                                                                 |                                                               |      |            |  |

| 21          | Vertical Blanking Stop before start of Video (Number of Scan Lines)<br>(Range = Item 4 - 1 line to 0 lines) |                                                               |      |            |  |

| 22          |                                                                                                             | s of a Row? (Yes or No) If not, which Line?                   |      |            |  |

| 23          | Does the Horizontal Sync Pulse have Serrations during Vertical Sync? (Yes or No)                            |                                                               |      | 2° 19      |  |

| 24          | Width of Line Buffer Clock logic "O" state within a Character Time<br>(Number of Dot Time increments)       |                                                               |      |            |  |

| 25          | Serration Pulse Width, if used (Character Times)                                                            |                                                               |      | r          |  |

| 26          | Horizontal Sync Pulse Active s                                                                              | tate logic level (1 or 0)                                     |      | 1          |  |

| 27          | Vertical Sync Pulse Active stat                                                                             | e logic level (1 or 0)                                        |      |            |  |

| 28          | Vertical Blanking Pulse Active                                                                              |                                                               |      |            |  |

Note 1: If the Cursor Enable, Item 22, is active on only one line of a character row, then Item 21 must be either "1" or "0" unless it is the same as the line selected for Cursor Enable.

Note 2: Item 24 x Item 20 should be > 250 ns.

Note 3: Item 11 must be greater than Item 4 + 1.

# **DP8350 Series Option Program Table**

### DP8350 Option: 80 Characters x 24 Rows, 5 x 7 Character Font, 7 x 10 Character Field

| ltem<br>No. |                                                                                                               | Value                                                          |            |            |  |

|-------------|---------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|------------|------------|--|

| 1           | Character (Font Size)                                                                                         | Dots per Character                                             | 5          |            |  |

| 2           | Character (Font Size)                                                                                         | Scan Lines per Character                                       |            |            |  |

| 3           |                                                                                                               | Dots per Character                                             | 7 10       |            |  |

| 4           | Character Field (Block Size)                                                                                  | Scan Lines per Character                                       |            |            |  |

| 5           | Number of Video Characters                                                                                    | per Row                                                        | 80         |            |  |

| 6           | Number of Video Character R                                                                                   | ows per Frame                                                  |            | 24         |  |

| 7           | Number of Video Scan Lines                                                                                    | (Item 4 x Item 6)                                              |            | 240        |  |

| 8           | Frame Refresh Rate (Hz) (two                                                                                  | o frequencies allowed)                                         | f1 = 60 Hz | f0 = 50 Hz |  |

| 9           | Delay after/before Vertical Bl                                                                                | ank start to start of Vertical Sync (+/- Number of Scan Lines) | 4          | 30         |  |

| 10          | Vertical Sync Width (Number                                                                                   | of Scan Lines)                                                 | 10         | 10         |  |

| 11          | Delay after Vertical Blank sta                                                                                | 20                                                             | 72         |            |  |

| 12          | Total Scan Lines per Frame (I                                                                                 | 260                                                            | 312        |            |  |

| 13          | Horizontal Scan Frequency (L                                                                                  | 15.6 kHz                                                       |            |            |  |

| 14          | Number of Character Times p                                                                                   | er Scan Line                                                   | 100        |            |  |

| 15          | Character Clock Rate (MHz) I                                                                                  | tem 13 x Item 14)                                              | 1.56 MHz   |            |  |

| 16          | Character Time (ns) (1 ÷ Item 15)                                                                             |                                                                |            | 1 ns       |  |

| 17          | Delay after/before Horizontal Blank start to Horizontal Sync Start (+/- Character Times)                      |                                                                |            | 0          |  |

| 18          | Horizontal Sync Width (Character Times)                                                                       |                                                                |            | 43         |  |

| 19          | Dot Frequency (MHz) (Item 3 x Item 15)                                                                        |                                                                |            | 10.920 MHz |  |

| 20          | Dot Time (ns) (1 ÷ Item 19)                                                                                   |                                                                |            | .6 ns      |  |

| 21          | Vertical Blanking Stop before start of Video (Number of Scan Lines)<br>(Range = Item 4 – 1 line to 0 lines) 1 |                                                                |            |            |  |

| 22          | Cursor Enable on all Scan Lin                                                                                 | Y                                                              | ′es        |            |  |

| 23          | Does the Horizontal Sync Pulse have Serrations during Vertical Sync? (Yes or No)                              |                                                                |            | No .       |  |

| 24          | Width of Line Buffer Clock logic "O" state within a Character Time<br>(Number of Dot Time increments)         |                                                                |            | 4          |  |

| 25          | Serration Pulse Width, if used (Character Times)                                                              |                                                                |            | — ,        |  |

| 26          | Horizontal Sync Pulse Active state logic level (1 or 0)                                                       |                                                                | 1          |            |  |

| 27          | Vertical Sync Pulse Active state logic level (1 or 0) 0                                                       |                                                                |            | 0          |  |

| 28          | Vertical Blanking Pulse Active state logic level (1 or 0)                                                     |                                                                |            | 1          |  |

### FULL/HALF ROW CONTROL (PIN 5)

Device pin 5 converts the DP8350 programmed display from 80 characters by 24 rows to 80 characters by 12 rows.

| Full/Half<br>Row (Pin 5)<br>Logic State | Display<br>Size |  |

|-----------------------------------------|-----------------|--|

| 1                                       | 80 by 24        |  |

| 0                                       | 80 by 12        |  |

|                                         |                 |  |

With pin 5 in logic "0" state, the 12 character rows are equally spaced vertically on the CRT. Each row is spaced by one full row of blanked video.

Also in this mode the address counter outputs address the same memory space for two rows – the video row and the blanked row. Thus one half of the CRT memory space is addressed with pin 5 in logic. "0" state as compared to pin 5 in logic "1" state.

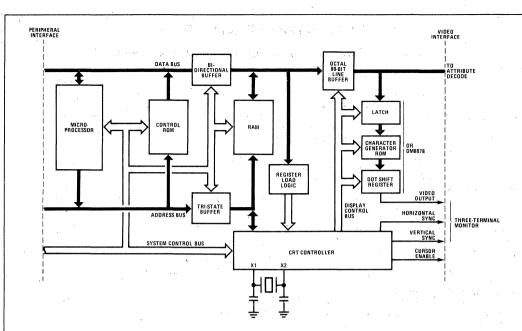

Figure 6. System Diagram Using a Line Buffer

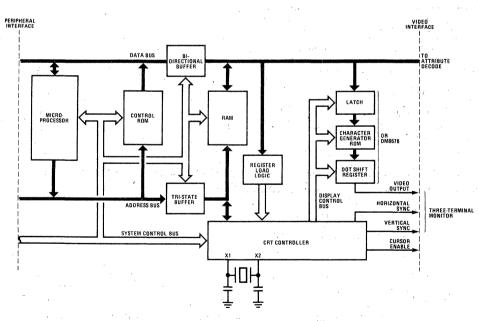

Figure 7. System Diagram with no Line Buffer

Note 1: If the Cursor Enable, Item 22, is active on only one line of a character row, then Item 21 must be either "1" or "0" unless it is the same as the line selected for Cursor Enable.

Note 2: Item 24 x Item 20 should be > 250 ns.

Note 3: Item 11 must be greater than Item 4 + 1.

National does not assume any responsibility for use of any circuitry described; no circuit patent licenses are implied, and National reserves the right, at any time without notice, to change said circuitry.