National Semiconductor

# DP83261 BMAC<sup>™</sup> Device (FDDI Media Access Controller)

### **General Description**

The DP83261 BMAC device implements the Media Access Control (MAC) protocol for operation in an FDDI token ring. The BMAC device provides a flexible interface to the BSI-2TM device. The BMAC device offers the capabilities described in the ANSI X3T9.5 MAC Standard and several functional enhancements allowed by the Standard.

The BMAC device transmits, receives, repeats, and strips tokens and frames. It uses a full duplex architecture that allows diagnostic transmission and self testing for error isolation. The duplex architecture also allows full duplex data service on point-to-point connections. Management software is also aided by an array of on chip statistical counters, and the ability to internally generate Claim and Beacon frames without program intervention. A multi-frame streaming interface is provided to the system interface device.

### Features

- Full duplex operation with through parity

- Supports all FDDI ring scheduling classes (asynchronous, synchronous, restricted asynchronous, and immediate)

- Supports individual, group, short, long and external addressing

- Generates Beacon, Claim and Void frames without intervention

- Provides extensive ring and station statistics

- Provides extensions for MAC level bridging

- Provides separate management interface

- Uses low power microCMOS

DP83265A BSI-2 (SYSTEM INTERFACE) DP83261 BMAC CONTROL (MEDIA ACCESS CONTROLLER) DP83256/56-AP/57 PLAYER+ (PHYSICAL LAYER CONTROLLER) TO FIBER OPTIC TRANSCEIVER PAIR TL/F/10387-1 FIGURE 1-1. FDDI Chip Set Block Diagram

TO HOST SYSTEM

TRI-STATE®is a registered trademark of National Semiconductor Corporation. BSI-2TM, BMACTM, PLAYER+TM, CDDTM and CRDTM are trademarks of National Semiconductor Corporation.

© 1995 National Semiconductor Corporation TL/F/10387

RRD-B30M105/Printed in U. S. A.

October 1994

### 1.0 FDDI CHIP SET OVERVIEW

### 2.0 ARCHITECTURAL DESCRIPTION

2.1 Ring Engine 2.2 Interfaces

### **3.0 FEATURE OVERVIEW**

### 4.0 FDDI MAC FACILITIES

- 4.1 Symbol Set

- 4.2 Protocol Data Units

- 4.3 Frame Counts

- 4.4 Timers

- 4.5 Ring Scheduling

### **5.0 FUNCTIONAL DESCRIPTION**

- 5.1 Token Handling

- 5.2 Servicing Transmission Requests

- 5.3 Request Service Parameters

- 5.4 Frame Validity Processing

- 5.5 Frame Status Processing

- 5.6 SMT Frame Processing

- 5.7 MAC Frame Processing

- 5.8 Receive Batching Support

- 5.9 Immediate Frame Transmission

- 5.10 Full Duplex Operation

- 5.11 Parity Processing

# **Table of Contents**

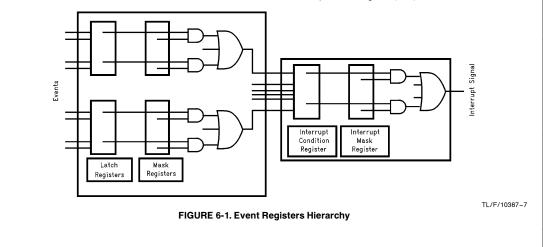

### 6.0 CONTROL INFORMATION

- 6.1 Conventions

- 6.2 Access Rules

- 6.3 Operation Registers

- 6.4 Event Registers

- 6.5 MAC Parameters

- 6.6 Timer Thresholds

- 6.7 Event Counters

### 7.0 SIGNAL DESCRIPTIONS

- 7.1 Control Interface

- 7.2 PHY Interface

- 7.3 MAC Indication Interface

- 7.4 MAC Request Interface

- 7.5 Electrical Interface

- 7.6 Pinout Summary

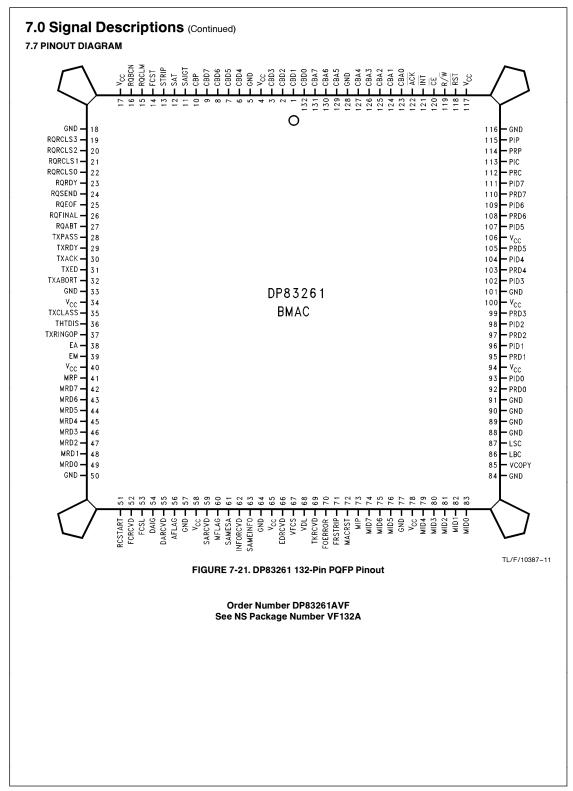

- 7.7 Pinout Diagram

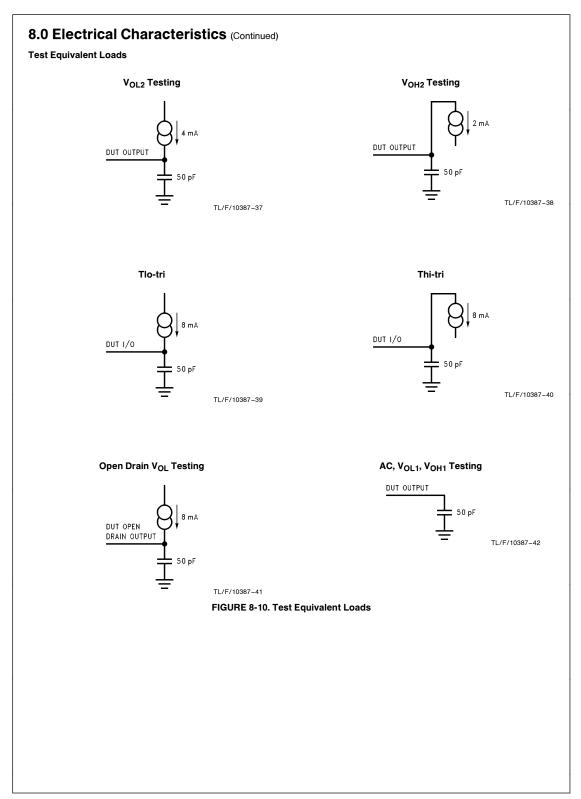

### 8.0 ELECTRICAL CHARACTERISTICS

- 8.1 Absolute Maximum Ratings

- 8.2 Recommended Operating Conditions

- 8.3 DC Electrical Characteristics

- 8.4 AC Electrical Characteristics

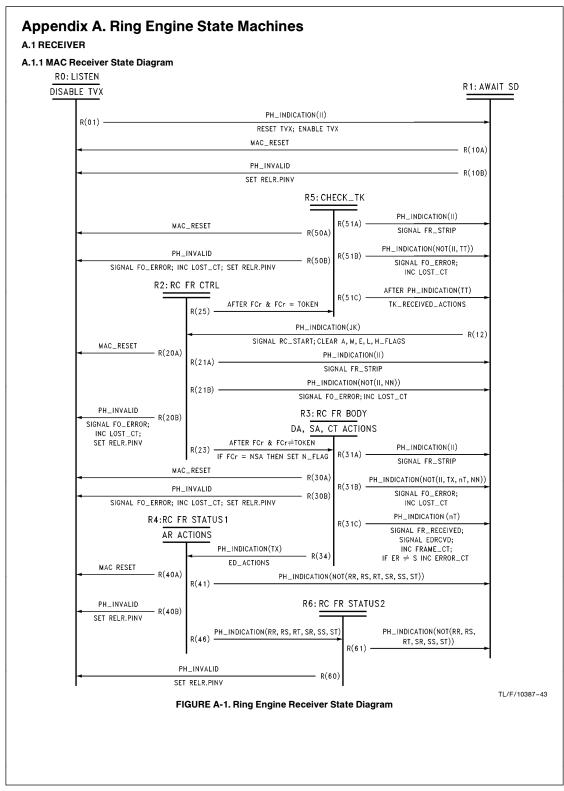

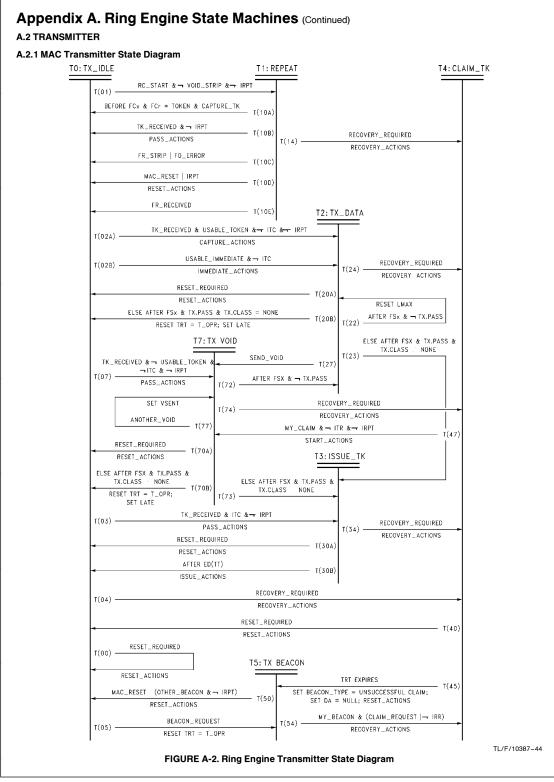

### APPENDIX A. RING ENGINE STATE MACHINES

- A.1 Receiver

- A.2 Transmitter

# 1.0 FDDI Chip Set Overview

National Semiconductor's DP83200 FDDI chip set consists of five components as shown in *Figure 1-1*. For more information on the other devices of the chip set, consult the appropriate datasheets and application notes.

# DP83256/56-AP/57 PLAYER + ™ Device Physical Layer Controller

The PLAYER+ device implements the Physical Layer (PHY) protocol as defined by the ANSI FDDI PHY X3T9.5 Standard, along with all the necessary clock recovery and clock regeneration functions.

## Features

- Single chip FDDI Physical Layer (PHY) solution

- Integrated Digital Clock Recovery Module provides enhanced tracking and greater lock acquisition range

- Integrated Clock Generation Module provides all necessary clock signals for an FDDI system from an external 12.5 MHz reference

- Alternate PMD Interface (DP83256-AP/57) supports UTP twisted pair FDDI PMDs with no external clock recovery or clock generation functions required

- No External Filter Components

- Connection Management (CMT) Support (LEM, TNE, PC\_React, CF\_React, Auto Scrubbing)

- · Full on-chip configuration switch

- Low Power CMOS-BIPOLAR design using a single 5V supply

- Full duplex operation with through parity

- · Separate management interface (Control Bus)

- Selectable Parity on PHY-MAC Interface and Control Bus Interface

- Two levels of on-chip loopback

- 4B/5B encoder/decoder

- Framing logic

- · Elasticity Buffer, Repeat Filter and Smoother

- Line state detector/generator

- Supports single attach stations, dual attach stations and concentrators with no external logic

- DP83256/56-AP for SAS/DAS single path stations

- P83257 for SAS/DAS single/dual path stations

In addition, the DP83257 contains an additional PHY\_Data.request and PHY\_Data.indicate port required for concentrators and dual attach stations.

# DP83261 BMAC<sup>™</sup> Device Media Access Controller

The BMAC device implements the Timed Token Media Access Control protocol defined by the ANSI X3T9.5 FDDI MAC Standard.

# Features

- All of the standard defined ring service options

- Full duplex operation with through parity

- Supports all FDDI Ring Scheduling Classes (Synchronous, Asynchronous, etc.)

- Supports Individual, Group, Short, Long, and External Addressing

- Generates Beacon, Claim, and Void frames internally

- Extensive ring and station statistic gathering

- Extensions for MAC level bridging

- Separate management port that is used to configure and control operation

- Multi-frame streaming interface

# DP83265A BSI-2 Device System Interface

The BSI-2 device implements an interface between the BMAC device and a host system.

### Features

- Fully software and pin compatible with the original BSI device

- Over 2 kbytes of on-chip FIFO

- Operates from 12.5 MHz to 33 MHz synchronously with host system

- Provides Address bit swapping capability

- Reduces interface logic for SBus adapters

- · 32-bit wide Address/Data path with byte parity

- Programmable transfer burst sizes of 4 or 8 32-bit words

- · Interfaces to DRAMs or directly to system bus

- 2 Output and 3 Input Channels

- Supports Header/Info splitting

- · Bridging support

- · Programmable Big or Little Endian alignment

- · Full duplex data path

- · Receive frame filtering services

# 2.0 Architectural Description

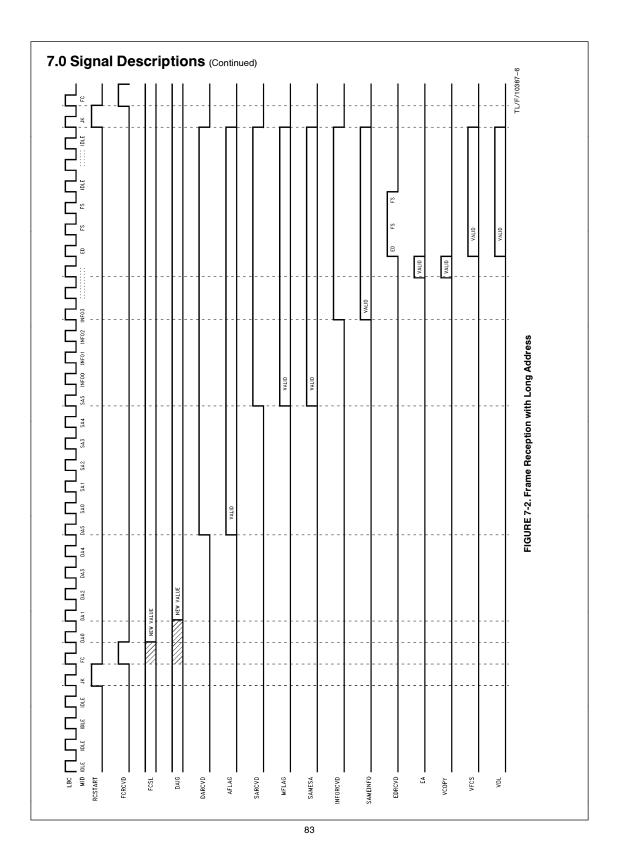

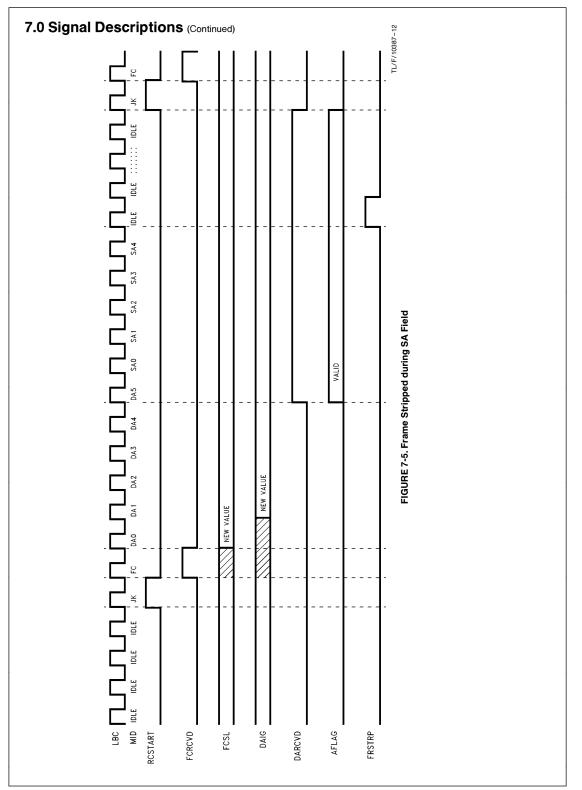

The BMAC device receivers, transmits, and strips or repeats Protocol Data Units (PDUs, i.e., Tokens and Frames) and handles the token management functions required by the timed token protocol in accordance with the FDDI MAC Standard.

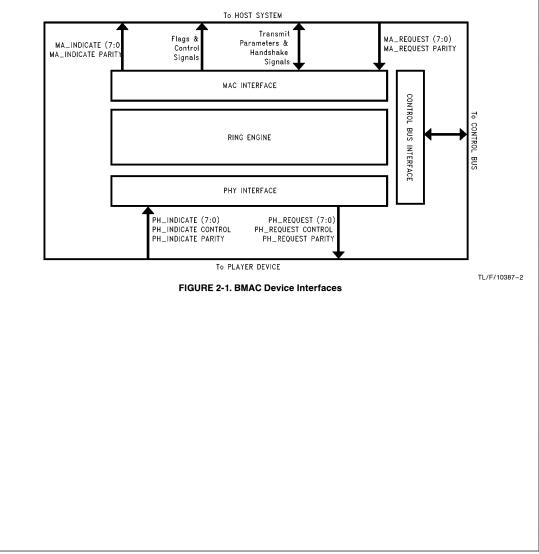

The BMAC device is comprised of the Ring Engine (RE) and interfaces to the Control Bus (Control Interface), the PLAYER device (PHY Interface) and a System Interface such as the BSI device (MAC Interface) as shown in *Figure 2-1*.

On transmission, the system interface prepares one or more frames for transmission and requests a service opportunity. Based on the requested service class and requested token type, the Ring Engine waits for a token meeting the request ed criteria. When a token is captured, the Ring Engine signals the interface and soon thereafter transmission begins. After traversing the ring, frames are stripped based on the Source Address. Frames with a Source Address matching one of the station individual addresses are stripped by the Ring Engine. Status is available at the MAC interface for every transmitted frame.

For reception, the Ring Engine sequences through the incoming byte stream, comparing received destination addresses against the station's short or long address. The results of these comparisons are made available at the MAC interface. The System Interface then decides how to handle the frame. In the normal case, a frame with a Destination Address matching one of the station addresses is copied and passed to the system.

The BMAC device utilizes a full duplex, byte-wide (symbol pair) architecture. There are two bytes of delay in the Transmit path, three bytes of delay in Receive and Repeat paths, and two bytes of delay in the Loopback path.

# 2.0 Architectural Description (Continued)

### 2.1 RING ENGINE

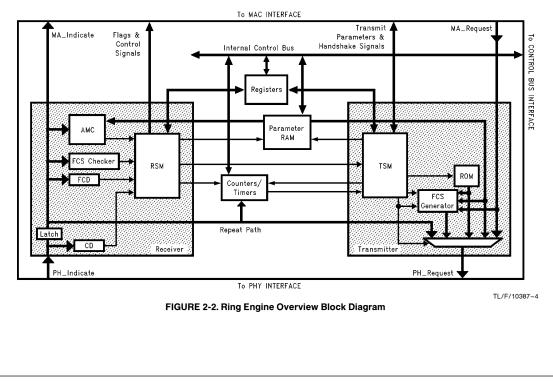

The BMAC device is operated by the Ring Engine which is comprised of four blocks: Receiver, Transmitter, MAC Parameter RAM, and Counters/Timers as shown in *Figure 2-2*.

### 2.1.1 Receiver

The Receiver Block accepts data from the PLAYER device in the byte stream format (PH\_Indicate).

Upon receiving the data, the Receiver Block performs the following functions:

- Determines the beginning and ending of a Protocol Data Unit (PDU)

- Decodes the Frame Control field to determine the PDU type (frame or token)

- Compares the received Destination and Source Addresses with the internal addresses

- · Processes data within the frame

- Calculates and checks the Frame Check Sequence at the end of the frame

- Checks the Frame Status field

And finally, the Receiver Block presents the data to the MAC Interface along with the appropriate control signals (MA\_Indicate).

### 2.1.2 Transmitter

The Transmitter Block inserts frames from this station into the ring in accordance with the FDDI Timed Token MAC protocol. It also repeats frames from other stations in the ring. The Transmitter block multiplexes data from the MA\_\_\_\_\_ Request Interface and data from the Receiver Block. During Frame Transmission, data from the Request Interface is selected. During Frame Repeating, data from the Receiver Block is selected.

During Frame Transmission, the Transmitter Block performs the following functions:

- Captures a token to gain the right to transmit

- Transmits one or more frames

- Generates the Frame Check Sequence during transmission and appends it at the end of the frame

- Generates the Frame Status field that is transmitted at the end of the frame

- Issues the token at the end of frame transmission

During Frame Repeating, the Transmitter Block performs the following functions:

• Repeats the received frame and modifies the Frame Status field at the end of the frame as specified by the standard

Whether transmitting or repeating frames, the Transmitter Block also performs the following functions:

• Strips the frame(s) that are transmitted by this station

Generates Idle symbols between frames

Data is presented from the Transmitter Block to the PLAYER device in the byte stream format (PH\_Request).

### 2.1.3 MAC Parameter RAM

The MAC Parameter RAM block is a dual port RAM that contains MAC parameters such as the station's short and long addresses. These parameters are initialized via the Control Interface. Both the Receiver and Transmitter Blocks may access the RAM.

### 2.0 Architectural Description (Continued)

The Receiver uses these parameters to compare addresses in incoming frames with its addresses stored in the Parameter RAM.

The Transmitter uses the Parameter RAM for generating the Source Address for all frames (except when Source Address Transparency is enabled) and for the Destination Address and Information fields in Claim and Beacon frames.

The MAC Parameter RAM block is described in greater details in Section 6.5.

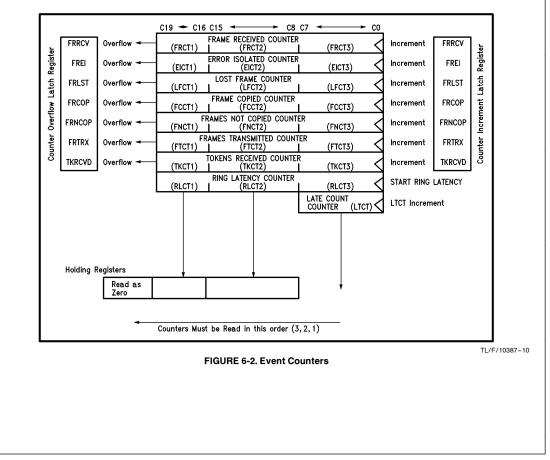

### 2.1.4 Counter/Timer

The Counter/Timer block maintains all of the Counters and Timers required by the Standard.

Events which occur too rapidly for software to count, such as the various Frame Counts, are included in the Event Counters. The size of the wrap around counters has been chosen to require minimal software intervention even under marginal operating conditions. Most of the Counters increment in response to events detected by the Receiver. The Counters are readable via the Control Interface.

The Token Rotation and Token Holding Timers which are used to implement the Timed Token Protocol are contained within the Timer Block.

The Counters and Timers are described in detail in Sections 6.6 and 6.7.

### 2.2 INTERFACES

### 2.2.1 PHY Interface

The PHY Intreface is a synchronous interface that provides an encoded byte stream to the PLAYER + device (the PHY Request byte stream), and receives an encoded byte stream from the PLAYER + device (the PHY Indication byte stream).

The BMAC device connects to one or two PLAYER + devices via the PH\_Indicate and PH\_Request Interfaces.

Data is transferred from the PLAYER+ device to the Ring Engine via the PH\_Indicate Interface. Data is transferred from the Ring Engine to the PLAYER+ device via the PH\_ Request Interface.

The 10-bit byte transferred in both directions across the PH\_Indicate and PH\_Request interfaces consists of one parity bit (Odd parity), one Control bit, and 8 bits of data. The Control Bit determines if the 8 data bits are a data symbol pair or a control symbol pair.

### 2.2.2 MAC Interface

The MAC Interface provides the required information and handshakes to allow a system interface (such as the DP83265A BSI-2) to exploit the capabilities of the Ring Engine.

The MAC Interface is synchronous and is divided into separate MAC Request and MAC Indication interfaces.

Data is transferred from the system interface to the Ring Engine via the MAC Request Interface. The MA\_Request Interface consists of a parity bit (Odd parity) and byte-wide data along with the transmit parameters and handshake signals. The MAC Request Interface utilizes a handshake that separates token capture from data transmisson. A captured token may be held until it is no longer usable. Void frames are automatically generated to allow data interface logic as much time as it needs to prepare a transmission.

Data is transferred from the Ring Engine to the system interface via the MAC Indication Interface. The MA\_Indicate Interface consists of a parity bit (Odd parity) and byte-wide data along with Addressing Flags and Frame Sequencing signals. The Addressing Flags give the result of the address comparisons performed by the Ring Engine. These are used to decide whether to continue to copy or to reject frames. The MAC Indication Interface also accepts inputs to determine how to set the control indicators and increment the statistical counters based on external address comparison logic and frame copying logic. Frames may also be stripped based on external comparisons.

### 2.2.3 Control Bus Interface

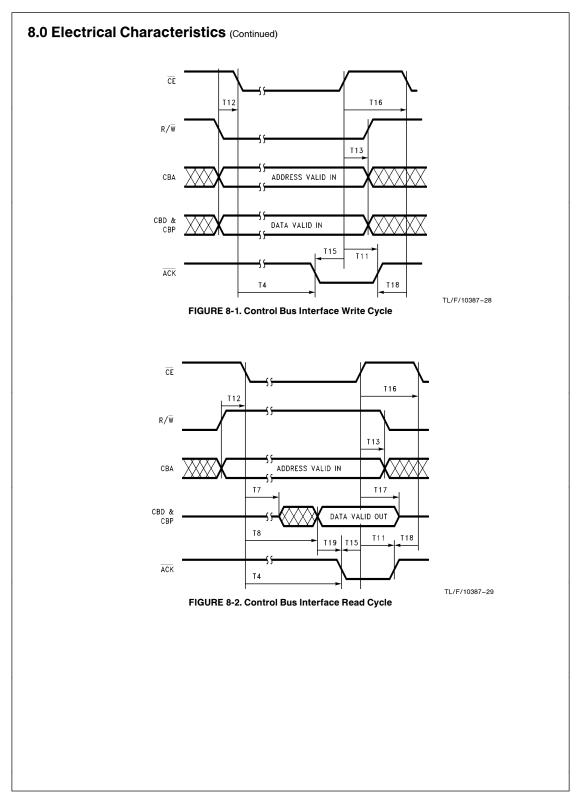

The Control Interface implements the interface to the Control Bus by which to initialize, monitor and diagnose the operation of the BMAC device. The Control Interface is an 8-bit asynchronous interface in order to minimize pinout and layout. All information that must be synchronized with the data stream crosses the MAC Interface.

The Control bus is separated completely from the MAC and PHY Interfaces in order to allow independent operation of the processor on the Control Bus. The Control Interface provides the synchronization between the Control Bus and the Ring Engine.

### **3.0 Feature Overview**

The BMAC device implements the standard FDDI MAC protocol. It also provides additional addressing, bridging, and service class functions to allow maximal flexibility in designing an FDDI station.

The BMAC device offers extensive diagnostic features including a number of diagnostic counters, a dedicated interface for control and configuration, and a capability to perform Self Testing. Furthermore, the BMAC device allows the tuning of certain parameters to increase the performance of the network.

### 3.0 Feature Overview (Continued) 3.1 FDDI MAC SUPPORT

The BMAC device implements the Standard ANSI X3T9.5 FDDI MAC protocol for transmitting, receiving, repeating and stripping frames. Many of the capabilities defined in MAC-2 are included in the BMAC device such as bridging end station support for setting the control indicators, and the statistic counters. The BMAC device provides all of the information necessary to implement the service primitives defined in the standard.

The BMAC device also implements many of the permitted extensions to the FDDI-MAC standard as captured in the FDDI MAC-2 document. These include the extensions for MAC level bridging, Group Addressing support that can be used for SMT, reporting of additional events to aid the ring management processes and enhanced versions of the state machines.

### 3.2 MAC ADDRESSING SUPPORT

Both long (48-bit) and short (16-bit) addressing are supported simultaneously, for both Individual and Group addresses.

Up to 128 contiguous programmable group addresses and up to 15 Fixed Group Addresses plus the universal/broadcast address are recognized. Limited operation with null addresses is supported. An interface to external address matching logic is provided to augment the Ring Engine's addressing capabilities.

### 3.3 MAC BRIDGING SUPPORT

Several features are provided to aid in Bridging applications. On the receive side, external address matching logic can be used to examine the PH\_Indicate byte stream to decide whether to copy a frame, how to set the control indicators and how to increment the counters.

On the transmit side, transparency options are provided on the Source Address, the most significant bit of the Source Address, and the FCS.

In addition, support for an alternate Void stripping mechanism provides maximal flexibility in the generation of frames.

### 3.4 MAC SERVICE CLASS SUPPORT

All of the FDDI MAC service classes are supported by the BMAC device. These include the Synchronous, Asynchronous, Restricted Asynchronous, and Immediate service classes.

For Synchronous transmission, one or more frames are transmitted in accordance with the station's synchronous bandwidth allocation.

For Asynchronous transmission, one programmable asynchronous priority threshold is supported in addition to the threshold at the Negotiated Target Token Rotation time.

For Restricted Asynchronous transmission, support is provided to begin, continue and end restricted dialogues.

For Immediate transmissions, support is provided to send frames from either the Data, Beacon or Claim states and either ignore or respond to the received byte stream. After an immediate transmission a token may optionally be issued.

### 3.5 DIAGNOSTIC COUNTERS

The BMAC device includes a number of diagnostic counters that monitor ring and station performance.

These counters allow measurement of the following:

- Number of frames transmitted and received by the station

- Number of frames copied as well as frames not copied because of insufficient buffering

- Frame error rate of an incoming physical connection to the MAC

- Load on the ring based on the number of tokens received and the ring latency

- Ring latency

- Lost frames

The size of these counters has been selected to keep the frequency of overflow small, even under worst case operating conditions.

### 3.6 MANAGEMENT SERVICES

The BMAC device provides management services to the Host System via the Control Bus Interface. This interface allows access to internal registers to control and configure the BMAC device.

### **3.7 RING PARAMETER TUNING**

The BMAC device includes settable parameters to allow tuning of the network to increase performance over a large range of network sizes.

The BMAC device supports systems of two stations with little cable between them to ring configurations much larger than the 1000 physical attachments and/or 200 km distance that are specified as the default values in the standard.

The BMAC device also handles frames larger than the 4500 byte default maximum frame size as specified in the Standard.

### 3.8 MULTI-FRAME STREAMING INTERFACE

The BMAC device provides an interface to support a multiframe streaming interface. Multiple frames can be transmitted after a token is captured within the limits of the token timer thresholds.

### 3.9 GENERATES BEACON, CLAIM, AND VOID FRAMES INTERNALLY

For purposes of transient token and ring recovery, no processor intervention is required. The BMAC device automatically generates the appropriate MAC frames.

### 3.10 SELF TESTING

Because the BMAC device is full duplex, loopback testing is possible before entering the ring and during normal ring operation.

There are several posible loopback paths:

- internal to the BMAC device

- through the PLAYER device(s) using the PLAYER device configuration switch

- through the CRD device.

These paths allow error isolation down to the device level. The BMAC device also supports through parity.

# **4.0 FDDI MAC Facilities**

# 4.1 SYMBOL SET

The Ring Engine recognizes and generates a set of symbols. These symbols are used to convey Line States (such as the Idle Line State), Control Sequences (such as the Starting and Ending Delimiters) and Data.

Additional information regarding the symbol set can be found in the FDDI PHY Standard.

The Ring Engine expects that the Starting Delimiter will always be conveyed on an even symbol pair boundary. Following the starting delimiter, data symbols should always come in matched pairs. Similarly the Ending Delimiter should always come in one or more matched symbol pairs. The symbol pairs conveyed at the PHY Interface are shown in Table 4-1.

### **4.2 PROTOCOL DATA UNITS**

The Ring Engine recognizes and generates two types of Protocol Data Units (PDUs): Tokens and Frames.

The Token is used to control access to the ring. Only the station that has captured the token has the right to transmit new information. The format of a token is shown in Figure 4-1.

| SI                       | ⁼s |    | EFS |  |

|--------------------------|----|----|-----|--|

| PA                       | SD | FC | ED  |  |

| FIGURE 4-1. Token Format |    |    |     |  |

Frames are used to pass information between stations. The format of a frame is shown in Figure 4-2 with the field definitions in Table 4-2.

| SI                       | FS |    | EF | -s |    |  |  |

|--------------------------|----|----|----|----|----|--|--|

| PA                       | SD | FC | DA | ED | FS |  |  |

| FIGURE 4-2. Frame Format |    |    |    |    |    |  |  |

TABLE 4-1. Symbol Pair Set

| Туре               | Symbols              |

|--------------------|----------------------|

| Starting Delimiter | JK                   |

| Ending Delimiter   | TT or TR or TS or nT |

| Frame Status       | RR or RS or SR or SS |

| ldle               | ll or nl             |

| Data Pair          | nn                   |

Note : n represents any data symbol (0-F).

Symbol pairs others than the defined symbols are treated as code violations. Section 7.2 has additional information on the symbol pairs generated and interpreted by the Ring Engine.

| TABLE 4-2. PD0 Tielus |                         |                                                                  |  |  |  |  |

|-----------------------|-------------------------|------------------------------------------------------------------|--|--|--|--|

| Name                  | Description             | Size                                                             |  |  |  |  |

| SFS                   | Start of Frame Sequence |                                                                  |  |  |  |  |

| PA                    | Preamble                | 8 or More Idle Symbol Pairs                                      |  |  |  |  |

| SD                    | Starting Delimiter      | JK Symbol Pair                                                   |  |  |  |  |

| FC                    | Frame Control Field     | 1 Data Symbol Pair                                               |  |  |  |  |

| DA                    | Destination Address     | 2 or 6 Symbol Pairs                                              |  |  |  |  |

| SA                    | Source Address          | 2 or 6 Symbol Pairs                                              |  |  |  |  |

| INFO                  | Information Field       |                                                                  |  |  |  |  |

| FCS                   | Frame Check Sequence    | 4 Symbol Pairs                                                   |  |  |  |  |

| EFS                   | End of Frame Sequence   |                                                                  |  |  |  |  |

| ED                    | Ending Delimiter        | At Least 1T Symbol for Frames;<br>At Least 2T Symbols for Tokens |  |  |  |  |

| FS                    | Frame Status            | 3 or More R or S Symbols                                         |  |  |  |  |

# TABLE 4-2. PDU Fields

4.2.1 PDU Fields

#### Start of Frame Sequence

The Start of Frame Sequence (SFS) consists of the Preamble (PA) followed by the Starting Delimiter (SD).

The Preamble is a sequence of zero or more Idle symbols that is used to separate the PDUs. The Ring Engine Receiver can process and repeat a frame or token with no preamble. The Ring Engine Transmitter generates frames with at least 8 bytes of preamble. The Ring Engine Transmitter also guarantees that valid FDDI frames will never be transmitted with more than 40 bytes of preamble.

The Starting Delimiter is used to indicate the start of a new PDU. The Starting Delimiter is the JK symbol pair.

The Ring Engine expects the Starting Delimiter to be conveyed across the PH\_Indication Interface as a single byte. Similarly, the Ring Engine only generates Starting Delimiters aligned to the byte boundary.

### Frame Control

The Frame Control (FC) field is used to discriminate PDUs. For tokens, the FC field identifies Restricted and Non-restricted tokens. For frames, the FC field identifies the frame types and format and how the frame is to be processed. The one byte FC field is formatted as shown in *Figure 4-3*.

The C (Class) bit specifies the MAC Service Class as Asynchronous (C = 0) or Synchronous (C = 1).

The L (Length) bit specifies the length of the MAC Address as Short (L = 0) or Long (L = 1). A Short Address is a 16-bit address. A Long Address is a 48-bit address.

The FF (Format) bits specify the PDU types as shown in Table 4-3.

The r (Reserved) bit is currently not specified and should always be transmitted as Zero (Exception: SMT NSA Frames).

The ZZZ (Control) bits are used in conjunction with the C and FF bits to specify the type of PDUs. These bits may be used to affect protocol processing criteria such as the Priority, Protocol Class, Status Handling, etc.

| TABLE 4-3. | Frame | Control | Format | Bits |

|------------|-------|---------|--------|------|

|------------|-------|---------|--------|------|

| FC | .FF | PDU Types                           |

|----|-----|-------------------------------------|

| 0  | 0   | SMT/MAC                             |

| 0  | 1   | LLC                                 |

| 1  | 0   | Reserved for Implementer            |

| 1  | 1   | Reserved for Future Standardization |

When the Frame Control Format bits (FC.FF) indicate a SMT or MAC PDU, the frame type is identified as shown in Table 4-4.

### TABLE 4-4. MAC/SMT Frames Types

| TADLE 4-4. MAC/SMITTAILes Types |                 |                                      |  |  |  |  |

|---------------------------------|-----------------|--------------------------------------|--|--|--|--|

| CLFF                            | rZZZ            | PDU Type                             |  |  |  |  |

| 1000                            | 0000            | Non-Restricted Token                 |  |  |  |  |

| 1100                            | 0000            | Restricted Token                     |  |  |  |  |

| 0L00                            | 0000            | Void Frame                           |  |  |  |  |

| 0L00                            | 0001 to<br>1110 | SMT Frame                            |  |  |  |  |

| 0L00                            | 1111            | SMT Next Station<br>Addressing Frame |  |  |  |  |

| 1L00                            | 0001            | Other MAC Frame                      |  |  |  |  |

| 1L00                            | 0010            | MAC Beacon Frame                     |  |  |  |  |

| 1L00                            | 0011            | MAC Claim Frame                      |  |  |  |  |

| 1L00                            | 0100 to<br>1111 | Other MAC Frame                      |  |  |  |  |

### Destination Address

The Destination Address (DA) field is used to specify the station(s) that should receive and process the frame.

The DA can be an Individual or Group address. This is determined by the Most Significant Bit of the DA (DA.IG). When DA.IG is 0 the DA is an Individual Address, when DA.IG is 1 the DA is a Group Address. The Broadcast/Universal address is a Group Address.

The DA field can be a Long or Short Address. This is determined by the L bit in the FC field (FC.L). If FC.L is 1, the DA is a 48-bit Long Address. If FC.L is 0, the DA is a 16-bit Short Address.

The Ring Engine maintains both a 16-bit Individual Address, My Short Address (MSA) and a 48-bit Individual Address, My Long Address (MLA).

On the receive side, if DA.IG is 0 the incoming DA is compared with MLA (if FC.L = 1) or MSA (if FC.L = 0). If the received DA matches MLA or MSA the frame is intended for this station and the address recognized flag (A\_Flag) is set. If DA.IG is 1, the DA is a Group Addresse and is compared with the set of Group Addresses recognized by the Ring Engine. If a match occurs the address recognized flag (A\_Flag) is set. The A\_Flag is used by system interface logic as part of the criteria (with FC.L, DA.IG and M\_Flag) to determine whether or not to copy the frame. If the A\_flag is set, the system interface will normally attempt to copy the frame.

On the transmit side, the DA is provided by the system interface logic as part of the data stream. The length of the address to be transmitted is determined by the L bit of the FC field. (The FC field is also passed in the data stream.) The Destination Address can be an Individual, Group, or Broadcast Address.

#### Source Address

The Source Address (SA) field is used to specify the address of the station that originally transmitted the frame.

The Source Address has the same length as the Destination Address (i.e., if the DA is a 16-bit Address, the SA is a 16-bit Address; if the DA is a 48-bit Address, the SA is a 48-bit Address).

On the receive side, the incoming SA is compared with either MSA or MLA. If a match occurs between the incoming SA and this station's MLA or MSA, the M\_Flag is set. This flag is used to indicate that the frame is recognized as having been transmitted by this station and is stripped. The most significant bit of the SA (SA.IG) is not evaluated in the comparison.

On the transmit side, the station's individual address is transmitted as the SA. Since the SA field is normally used for stripping frames from the ring, the SA stored by the Ring Engine normally replaces the SA from the data stream. The length of the address to be transmitted is determined by the L bit of the FC field. (The FC field is passed in the data stream.) The most significant bit of the SA (SA.IG) is normally transmitted as 0, independent of the value passed through the data stream.

As a transmission option, the SA may also be transmitted transparently from the data stream. When the SA Transparency option is used, an alternate stripping mechanism is necessary to remove these frames from the ring. (The Ring Engine provides a Void Stripping Option. See Section 7.4.2.4 for futher information.)

As a separate and independent transmission option, the MSB of the SA may also be transmitted transparently from the data stream. This is useful for end stations participating in the Source Routing protocol.

### Information

The Information field (Info) contains the Service Data Unit (SDU). A SDU is the unit of data transfer between peer users of the MAC data service (SMT, LLC, etc). There is no INFO field in a Token.

The INFO field contains zero or more bytes.

On the receive side, the INFO field is checked to ensure that it has at least the minimum length for the frame type and contains an even number of symbols, as required by the Standard.

The first 4 bytes of the INFO field of MAC frames (e.g., MAC Beacon or MAC Claim) are stored in an internal register and compared against the INFO field of the next MAC frame. If the data of the two frames match, the SameInfo signal is generated. This signal may be used to copy MAC frames only when new information is present.

On the transmit side, the Ring Engine does not limit the maximum size of the INFO field, but it does insure that frames are transmitted with a valid DA and SA.

### Frame Check Sequence

The Frame Check Sequence (FCS) is a 32-bit Cyclic Redundancy Check that is used to check for data corruption in frames. There is no FCS field in a Token.

On the receive side, the Ring Engine checks the FCS to determine whether the frame is valid or corrupted.

On the transmit side, the FCS field is appended to the end of the INFO field. As a transmission option, appending the FCS to the frame can be inhibited (FCS Transparency).

### **End of Frame Sequence**

The End of Frame Sequence (EFS) always begins with a T symbol and should always contain an even number of symbols. For Tokens an additional T symbol is added. For frames the *Ending Delimiter* (ED) is followed by one or more *Frame Status* Indicators (FS).

The Frame Status (FS) field is used to indicate the status of the frame. The FS field consists of three Indicators: Error Detected (E), Address Recognized (A), and Frame Copied (C). These Indicators are created and modified as specified in the Standard.

For frames transmitted by the Ring Engine, the E, A and C Indicators are appended to all frames and are transmitted as R symbols. No provisions are made to generate additional trailing control indicators.

For frames repeated by the Ring Engine, the E, A and C Indicators are handled as specified in the Standard. Additional trailing control indicators are repeated unmodified provided they are properly aligned. See Section 5.5 for details on Frame Status Processing.

### 4.2.2 Token Formats

The Ring Engine supports non-restricted and restricted Tokens. See *Figures 4-4* and *4-5*.

| SFS | FC | EFS |

|-----|----|-----|

| SD  | 80 | ED  |

FIGURE 4-4. Non-Restricted Token Format

| SFS  | FC | ED |

|------|----|----|

| SD   | C0 | ED |

| <br> |    |    |

FIGURE 4-5. Restricted Token Format

### Non-Restricted

A non-restricted token is used for synchronous and non-restricted asynchronous transmissions.

Each time the non-restricted token arrives, a station is permitted to transmit one or more frames in accordance with its synchronous bandwidth allocation regardless of the status of the token (late or early).

Asynchronous transmissions occur only if the token is early (usable token) and the Token Holding Timer has not reached the selected threshold.

#### Restricted

A restricted token is used for synchronous and restricted asynchronous transmissions only.

A station which initiates the restricted dialogue captures a non-restricted token and releases a restricted token. Stations that participate in the restricted dialogue are allowed to capture the restricted token. A station ends the restricted dialogue by capturing the restricted token and releasing a non-restricted token.

### 4.2.3 Frame Formats

The Ring Engine supports all of the frame formats permitted by the FDDI standard. All frame types may be created external to the BMAC device and be passed through the MAC Request Interface to the Ring. The BMAC device also has the ability to generate Void, Beacon and Claim frames internally.

### **Frames Generated Externally**

The Ring Engine transmits frames passed to it from the System Interface. The data portion of the frame is created by the System Interface. This begins with the FC field and ends with the last byte of the INFO field. The FC field is passed transparently to the ring. The length bit in the FC field is used to determine the length of the transmitted addresses. The data is passed as a byte stream across the MAC Request Interface as shown in Table 4-5.

Before the frame is transmitted, the Ring Engine inserts the Start of Frame Sequence with at least 8 bytes of Preamble but no more than 40 bytes of Preamble. The starting delimiter is transmitted as a JK symbol pair. The Source Address is normally transmitted by the Ring Engine since it uses the Source Address to strip the frame from the ring. This can be overridden by using the Source Address transparency capability. Similarly, the Frame Check Sequence (4 bytes) is normally transmitted by the Ring Engine. This can be overridden with the FCS transparency capability. With FCS transparency, the FCS is transmitted from the data stream. The End of Frame Sequence is always transmitted by the Ring Engine as TR RR.

Frames transmitted by the Ring Engine must have a valid DA and SA field. If the end of a frame is reached before a valid length is transmitted, the frame will be aborted and a Void frame will be transmitted.

TABLE 4-5. Frame Formats

| Field | Size         | MA_Request | PHRequest          |

|-------|--------------|------------|--------------------|

| PA    | ≥8; ≤40      |            | Idle Pairs         |

| SD    | 1            |            | JK                 |

| FC    | 1            | FC         | FC                 |

| DA    | 2 or 6       | DA         | DA                 |

| SA    | 2 or 6       | SA         | MSA, MLA,<br>or SA |

| INFO  | ≥ 0          | INFO       | INFO               |

| FCS   | 4 if Present | FCS        | FCS                |

| ED    | 1            |            | TR                 |

| FS    | 1            |            | RR                 |

My\_Claim

ELA

### Frames Generated by the Ring Engine

The Ring Engine generates and detects several frames in order to attain and maintain an operational ring.

### Void Frames

Void frames are used during normal operation. The Ring Engine generates two types of void frames: regular Void frames and My\_Void frames. See Table 4-6.

If short addressing is enabled, Void frames with the short address are transmitted, otherwise Void frames with the long address are transmitted.

Void frames are transmitted in order to reset the Valid Transmission timers (TVX) in other stations in order to eliminate an unnecessary entry to the Claim state. Stations are not required to copy Void frames. Void frames are transmitted by the Ring Engine in two situations:

- While holding a token when no data is ready to be transmitted.

- 2. After a frame transmission is aborted.

My\_Void frames are transmitted by the Ring Engine in three situations:

- 1. After a request to measure the Ring Latency has been made when the next early token is captured.

- After this station wins the Claim Process before the token is issued.

- After a frame has been transmitted with the STRIP option before the token for that service opportunity is issued.

Void frames are also detected by the Ring Engine. A Void frame with a Source Address other than MSA or MLA is considered an Other\_Void frame.

### **Claim Frames**

Claim frames are generated continuously with minimum preamble while the Ring Engine is in the Transmit Claim state. The format of Claim frames generated by the Ring Engine is shown in Table 4-7. When long addressing is enabled, frames with the long address are transmitted, otherwise frames with the short address are transmitted.

The Ring Engine detects reception of valid Claim frames. A comparison is performed between the (first) four bytes of the received INFO field and TREQ in order to distinguish Higher\_Claim, Lower\_Claim, and My\_Claim. Details are given in Appendix A.

TREQ

FCS

TRRR

| Туре                    | Enable  | Size  |    | SFS |    | FC | DA    | SA   | FCS | EFS  |

|-------------------------|---------|-------|----|-----|----|----|-------|------|-----|------|

| Void                    | ESA     | Short | P  | A : | SD | 00 | Null  | MSA  | FCS | TRRR |

| Void                    | Not ESA | Long  | P  | A : | SD | 40 | Null  | MLA  | FCS | TRRR |

| MyVoid                  | ESA     | Short | P  | A : | SD | 00 | MSA   | MSA  | FCS | TRRR |

| MyVoid                  | Not ESA | Long  | P  | A : | SD | 40 | MLA   | MLA  | FCS | TRRR |

| TABLE 4-7. Claim Frames |         |       |    |     |    |    |       |      |     |      |

| Туре                    | Enable  | Size  | S  | FS  | FC | DA | SA    | INFO | FCS | EFS  |

| My_Claim                | Not ELA | Short | PA | SD  | 83 | MS | A MSA | TREQ | FCS | TRRR |

|                         |         |       |    |     |    |    |       |      |     |      |

### TABLE 4-6. Void Frames

C3

MLA

MLA

PA

SD

Long

### 4.0 FDDI MAC Facilities (Continued) Beacon Frames

Beacon frames are transmitted continuously with minimum preamble when the Ring Engine is in the Transmit Beacon state. The format of Beacon frames generated by the Ring Engine is shown in Table 4-8. When long addressing is enabled, frames with the long address are transmitted, otherwise frames with the short address are transmitted.

When the Transmit Beacon State is entered from the Transmit Claim State the first byte of the 4 byte TBT Field is transmitted as Zero.

Beacon frames that require alternative formats such as Directed Beacons must be generated externally.

The Ring Engine detects reception of valid Beacon frames and distinguishes between Beacon frames transmitted by this MAC (My\_Beacon) and Beacon frames transmitted by other stations (Other\_Beacon). Details are given in Appendix A.

### **4.3 FRAME COUNTS**

To aid in fault isolation and to enhance the management capabilities of a ring, the Ring Engine maintains several frame counts. The Error and Isolated frame counts increment when a frame is received with one or more errors that were previously undetected. The Ring Engine then corrects the error such that a downstream station will not increment its count.

The size of the counters has been chosen such that minimal software intervention is required, even under marginal operating conditions.

The following counts are maintained by the Ring Engine:

| FRCT | Frame Received     |

|------|--------------------|

| EICT | Error Isolated     |

| LFCT | Lost Frame         |

| FCCT | Frames Copied      |

| FNCT | Frames Not Copied  |

| FTCT | Frames Transmitted |

|      |                    |

### 4.3.1 Frame Received Count

The Frame Received Count (FRCT) is specified in the FDDI MAC Standard, and is the count of all complete frames received. This count includes frames stripped by this station.

### 4.3.2 Error Isolated Count

The Error Isolated Count (EICT) is specified in the FDDI MAC Standard, and is the count of error frames detected by this station and no previous station. It increments when:

- 1. An FCS error is detected and the received Error Indicator (Er) is not equal to S.

- 2. A frame of invalid length (i.e., off boundary T) is received and Er is not equal to S.

3. Er is not R or S.

### 4.3.3 Lost Frame Count

The Lost Frame Count (LFCT) is specified in the FDDI MAC Standard, and is the count of all instances where a format error is detected in a frame or token such that the credibility of PDU reception is placed in doubt. The Lost Frame Count is incremented when any symbol other than data or Idle symbols are received between the Starting and Ending Delimiters of a PDU (this includes parity errors).

### 4.3.4 Frame Copied Count

The Frames Copied Count (FCCT) is specified in the FDDI MAC-2 Standard, and is the count of the number of frames copied by this station. The count is incremented when an internal or external match occurs (when Option.EMIND is enabled) on the Destination Address, no errors were detected in the frame and the frame was successfully copied (VCOPY = 1). This can be used to accumulate station performance statistics. Frames copied promiscuously, MAC frames, Void frames and NSA frames received with the A indicator set are not included in this count.

### 4.3.5 Frames Not Copied Count

The Frames Not Copied Count (FNCT) is specified in the FDDI MAC-2 Standard, and is the count of frames intended for this station that were not successfully copied by this station. The count is incremented when an internal or external (when Option.EMIND is enabled) Destination Address match occurs, no errors were detected in the frame, and the frame was not successfully copied (VCOPY = 0). This count is an indication of insufficient buffering or frame processing capability for frames addressed to the station. MAC frames, Void frames and NSA frames received with the A indicator set are not included in this count.

### 4.3.6 Frames Transmitted Count

The Frames Transmitted Count (FTCT) is specified in the FDDI MAC-2 Standard, and is incremented every time a complete frame is transmitted from the MAC Request Interface. The count is provided as an aid to accumulate station performance statistics. Void and MAC frames generated by the Ring Engine are not included in the count.

### 4.4 TIMERS

### 4.4.1 Token Rotation Timer

The Token Rotation Timer (TRT) times token rotations from arrival to arrival. TRT is used to control ring scheduling during normal operation and to detect and recover from serious ring error situations.

TRT is loaded with the maximum token rotation time, TMAX, when the ring is not operational. TRT is loaded with the negotiated Target Token Rotation Time, TNEG, when the ring is operational.

| ГΑ | BLE | 4-8. | Beacon | Frames |

|----|-----|------|--------|--------|

|    |     |      |        |        |

| Туре      | Enable  | Size  | S  | FS | FC | DA   | SA  | INFO | FCS | EFS  |  |

|-----------|---------|-------|----|----|----|------|-----|------|-----|------|--|

| My_Beacon | Not ELA | Short | PA | SD | 82 | Null | MSA | TBT  | FCS | TRRR |  |

| My_Beacon | ELA     | Long  | PA | SD | C2 | Null | MLA | TBT  | FCS | TRRR |  |

### 4.4.2 Token Holding Timer

The Token Holding timer (THT) is used to limit the amount of ring bandwidth used by a station for asynchronous traffic once the token is captured. THT is used to determine if the captured token is (still) usable for asynchronous transmission. A token is usable for asynchronous traffic if THT has not reached the selected threshold. Two asynchronous thresholds are supported; one that is fixed at the Negotiated Target Token Rotation Time (TNEG), and one that is programmable at one of 16 Asynchronous Priority Thresholds. Requests to transmit frames at one of the priority thresholds are serviced when the Token Holding Timer (THT) has not reached the selected threshold.

### 4.4.3 Late Count

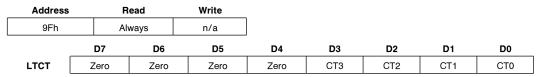

The Late Count (LTCT) is implemented differently than suggested by the Standard, but provides similar information. The function of the Late Count is divided beween the Late\_\_\_\_\_ Flag that is equivalent to the standard Late Count with a non-zero value and a separate counter. Late Flag is maintained by the Ring Engine to indicate if it is possible to send asynchronous traffic. When the ring is operational, Late Count indicates the time it took the ring to recover the last time the ring went non-operational. When the ring is non-operational, Late Count indicates the time it has taken (so far) to recover the ring.

The Late Count is incremented every time TRT expires while the ring is non-operational and Late\_Flag is set (once every TMAX).

The Late Count is provided to assist Station Management, SMT, in the isolation of serious ring errors. In many situations the ring will recover very quickly and late count will be of marginal utility. However in the case of serious ring errors, it is helpful for SMT to know how long it has been since the ring went non-operational (with TMAX resolution) in order to determine if it is necessary to invoke recovery procedures. When the ring goes no operational there is no way to know how long it will stay non-operational, therefore a timer is necessary. If the Late Count were not provided, SMT would be forced to start a timer every time the ring goes non-operational even though it may seldom be used. By using the provided Late Count, an SMT implementation may be able to alleviate this additional overhead.

### 4.4.4 Valid Transmission Timer

The Valid Transmission Timer (TVX) is reset every time a valid PDU is received. TVX is used to increase the responsiveness of the ring to errors. Expiration of the TVX indicates that no PDU has been received within the timeout period and causes the Transmitter to invoke the recovery Claim Process.

### 4.4.5 Token Received Count

The Token Received Count (TKCT) is incremented every time a valid token arrives. The Token Count can be used with the Ring Latency Count to calculate the average network load over a period of time. The frequency of token arrival is inversely related to the network load.

### 4.4.6 Ring Latency Count

The Ring Latency Count (RLCT) is a measurement of time for PDUs to propagate around the ring. This counter contains the last measured ring latency whenever the Ring Latency Valid bit of the Token Event Register (TELR.RLVLD) is one. The Latency Counter increments every 16 byte times (1.28  $\mu$ s) and is used to measure ring latencies up to 1.3421772 seconds directly with an accuracy of 1.2  $\mu$ s. No overflow or increment event is provided with this counter.

### 4.5 RING SCHEDULING

FDDI uses a timed token protocol to schedule the use of the ring. The protocol measures load on the network by timing the rotation of the token. The longer the token rotation time the greater the instantaneous load on the network. By limiting the transmission of data when the token rotation time exceeds a target rotation time, a maximum average token rotation time is realized. The protocol is used to provide different classes of service.

Multiple classes of service can be accommodated by setting different target token rotation times for each class of service.

The Ring Engine supports Synchronous, Non-Restricted Asynchronous, Restricted Asynchronous, and Immediate service classes. The Immediate service class is supported when the ring is non-operational; the other classes are supported when the ring is operational.

### 4.5.1 Synchronous Service Class

The Synchronous service class may be used to guarantee a maximum response time (2 times TTRT), minimum bandwidth, or both.

Each time the token arrives, a station is permitted to transmit one or more frames in accordance with its synchronous bandwidth allocation regardless of the status of the token (late or early; Restricted or Non-Restricted).

Since the Ring Engine does not provide a mechanism for monitoring a station's synchronous bandwidth utilization, the user must insure that no synchronous request requires more than the allocated bandwidth.

To help ensure that synchronous bandwidth is properly allocated after ring configuration, synchronous requests are not serviced after a Beacon frame is received. After a major reconfiguration has occurred, management software must intervene to verify or modify the current synchronous bandwidth allocation.

### 4.5.2 Non-Restricted Asynchronous Service Class

The Non-Restricted Asynchronous service class is typically used with interactive and background traffic. Non-restricted Asynchronous requests are serviced only if the token is early and the Token Holding Timer has not reached the selected threshold.

Asynchronous service is available at two priority thresholds, the Negotiated Target Token Rotation Time plus one programmable threshold. Management software may use the priority thresholds to discriminate additional classes of traffic based on current loading characteristics of the ring. The priority thresholds may be determined using the current TTRT and the Ring Latency. In this case, application software is only concerned with the priority level of a request.

As an option, Asynchronous Requests may be serviced with THT disabled. This is useful when it is necessary to guarantee that a multi-frame request will be serviced on a single token opportunity. Because of the possibility of causing late tokens, this capability should be used with caution, and should only be allowed when absolutely necessary.

### 4.5.3 Restricted Asynchronous Service Class

The Restricted Asynchronous service class is useful for large transfers requiring all of the available Asynchronous bandwidth. The Restricted Token service is useful for large transfers requiring all of the available (remaining) asynchronous bandwidth.

The Restricted Token service may also be used for operations requiring instantaneous allocation of the remaining synchronous bandwidth when Restricted Requests are serviced with THT disabled. This is useful when it is necessary to guarantee atomicity, i.e., that a multi-frame request will be serviced on a single token opportunity.

A Restricted dialogue consists of three phases:

- 1. Initiation of a Restricted dialogue:

- Capture a Non-Restricted Token

- Transmit zero or more frames to establish a Restricted dialogue with other stations

- Issue a Restricted Token to allow other stations in the dialogue to transmit frames

2. Continuation of a Restricted dialogue:

- Capture a Restricted Token

- Transmit zero or more frames to continue the Restricted dialogue

- Issue a Restricted Token to allow other stations in the dialogue to transmit frames

- 3. Termination of a Restricted dialogue:

- Capture a Restricted Token

- Transmit zero or more frames to continue the Restricted dialogue

- Issue a Non-restricted Token to return to the Non-restricted service class

Initiation of a Restricted dialogue will prevent all Non-restricted Asynchronous traffic throughout the ring for the duration of the dialogue, but will not affect Synchronous traffic. To ensure that the Restricted traffic is operating properly, it is possible to monitor the use of Restricted Tokens on the ring. When a Restricted Token is received, the event is latched and under program control may generate an interrupt. In addition, a request to begin a Restricted dialogue will only be honored if both the previous transmitted Token and the current received Token were Non-restricted tokens. This is to ensure that the upper bound on the presence of a Restricted dialogue in the ring is limited to a single dialogue.

As suggested by the MAC-2 Draft standard, to help ensure that only one Restricted dialogue will be in progress at any given time, Restricted Requests are not serviced after a MAC frame is received until Restricted Requests are explicitly enabled by management software. Since the Claim Process results in the generation of a Non-restricted Token, this prevents stations from initiating another restricted dialogue without the intervention of management software.

### 4.5.4 Immediate Service Class

The Immediate service class facilitates several non-standard applications and is useful in ring failure recovery (e.g., Transmission of Directed Beacons). Certain ring failures may cause the ring to be unusable for normal traffic, until the failure is remedied. Immediate requests are only serviced when the ring is nonoperational. Immediate requests may be serviced from the Transmitter Data, Claim, and Beacon states Options are available to force the Ring Engine to enter the Claim or Beacon state, to prohibit it from entering the Claim state, or to remain in the Claim state when receiving My\_Claim.

On the completion of an Immediate request, a Token (Nonrestricted or Restricted) may optionally be issued. Immediate requests may also be used in non-standard applications such as a full duplex point to point link.

## **5.0 Functional Description**

### 5.1 TOKEN HANDLING

### 5.1.1 Token Timing Logic

The FDDI Ring operates based on the Timed Token Rotation protocol where all stations on the ring negotiate on the maximum time that the stations have to wait before being able to transmit frames. This value is termed the Negotiated Target Token Rotation Time (TTRT). The TTRT value is stored in the TNEG Register.

Stations negotiate for TTRT based on their TREQ that is assigned to them upon initialization.

Each station keeps track of the token arrival by setting the Token Rotation Timer (TRT) to the TTRT value. If the token is not received within TTRT (the token is late), the event is recorded by setting the Late\_Flag. If the token is not received within twice TTRT (TRT expires and Late\_Flag is set), there is a potential problem in the ring and the recovery process is invoked.

Furthermore, the Token Holding Timer (THT) is used to limit the amount of ring bandwidth used by a station for Asynchronous traffic once the token is captured. Asynchronous traffic is prioritized based on the Late\_Flag which denotes a threshold at TTRT and an additional Asynchronous Priority Threshold (THSH). The Asynchronous Threshold comparison (Apri 1) is pipelined, so a threshold crossing may not be detected immediately; however, the possible error is a fraction of the precision of the threshold values.

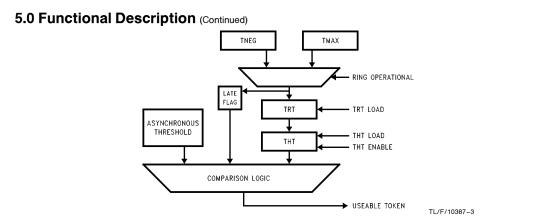

The Token Timing Logic consists of two Timers, TRT and THT, in addition to the TMAX and TNEG values loaded into these counters (See *Figure 5-1*).

The Timers are implemented as count-up counters that increment every 80 ns. The Timers are reset by loading TNEG or TMAX into the counters where TNEG and TMAX are unsigned twos complement numbers. This allows a Carry flag to denote timer expiration.

On an early token arrival (Late\_Flag is not set), TRT is loaded with TNEG and counts up. On a late token arrival (Late\_Flag is set), Late\_Flag is cleared and TRT continues to count. When TRT expires and Late\_Flag is not set, Late\_Flag is set and TRT is loaded with TNEG.

THT follows the value of TRT until a token is captured. When a token is captured, TRT may be reloaded with TNEG while THT continues to count from its previous value (THT does not wrap around). THT increments when enabled. THT is disabled during synchronous transmission and a special class of asynchronous transmission. THT is used to determine if the token is usable for asynchronous requests.

FIGURE 5-1. Token Timing Logic

If TRT expires while Late\_Flag is set, TRT is loaded with TMAX and the recovery process (Claim) is invoked. When TRT expires and the ring is not operational, TRT is loaded with TMAX. TRT is also loaded with TMAX on a MAC Reset.

#### 5.1.2 Token Recovery

While the ring is operational, every station in the ring uses the Negotiated Target Token Rotation Time, TNEG. The MAC implements the protocol for negotiation of this target token rotation time (TTRT) through the Claim Process. The shortest requested Token Rotation Time is used by all of the stations in the ring as the TNEG.

If TRT expires with Late\_Flag set, a token has not been received within twice TTRT (Target Token Rotation Time). If TVX (Valid Transmission Time) expires, the station has not received a valid token within TVX Max. Both these events require token recovery and cause the Ring Engine to enter the Claim Process.

In the Claim Process a MAC continuously transmits Claim frames containing TREQ. Should the MAC receive a Claim frame with a shorter TREQ (larger value—Higher\_Claim) it leaves the Claim State. A station that receives its own Claim frame gains the right to send the first token and make the ring operational again. If the Claim Process does not complete successfully, TRT will expire and the Beacon Process is invoked.

The Beacon Process is used for fault isolation. A station may invoke the Beacon Process through an SM\_Control.request(Beacon). When a station enters the Beacon Process, it continuously sends out Beacon frames. The Beacon Process is complete when a station receives its

own Beacon frame. That station then enters the Claim Process, to re-initialize the ring.

### 5.2 SERVICING TRANSMISSION REQUESTS

A Request to transmit one or more frames is serviced by the Ring Engine. After a Request is submitted to the Ring Engine, the Ring Engine awaits an appropriate Service Opportunity in which to service the Request. Frames associated with the Request are transmitted during the Service Opportunity. The definition of a Service Opportunity is different depending on the operational state of the ring.

A Service Opportunity begins when the criteria presented to the Ring Engine are met. This criteria contains the requested service class (synch, asynch, asynch priority, immediate) and the type of token to capture (restricted, non-restricted, any, none).

During a service opportunity, the Ring Engine guarantees that a valid frame is sent with at most 40 bytes of preamble. When data is not ready to be transmitted, Void frames are transmitted to reset the TVX timers in all stations. During an immediate request while in the Claim or Beacon States, when no Claim or Beacon frames are ready to be transmitted, the internally generated Claim or Beacon frames are transmitted.

### 5.2.1 Service Opportunity While Ring Operational

### **Beginning of Service Opportunity**

Table 5-1 shows the conditions that must be true when a valid token is received in order to begin a Service Opportunity when the ring is operational.

| Requested<br>Service Class | Requested Token<br>Capture Class | Criteria                                 | Received<br>Token Class |

|----------------------------|----------------------------------|------------------------------------------|-------------------------|

| Asynchronous Priority      | non-restricted                   | THT > THSH<br>LateFlag = 0<br>RingOp = 1 | non-restricted          |

| Asynchronous               | non-restricted                   | Late_Flag = 0<br>Ring_Op = 1             | non-restricted          |

| Asynchronous               | restricted                       | Late_Flag = 0<br>Ring_Op = 1             | restricted              |

| Synchronous                | any                              | Ring_Op = 1                              | any                     |

### TABLE 5-1. Beginning of Service Opportunity

In addition to the criteria mentioned above, additional criteria apply to the servicing of Synchronous and Restricted Requests.

- Synchronous Requests are not serviced if RELR.BCNR is set (See Section 4.5.1).

- Restricted requests are not serviced when RELR.BCNR, RELR.CLMR, or RELR.OTRMAC are set. (See Section 4.5.3).

- Restricted Dialogues may only begin when a non-restricted token has been received and transmitted (See Section 4.5.3).

### **End of Service Opportunity**

The Service Opportunity continues until either a token is issued or the ring becomes non-operational.

A token is issued after the current frame, if any, is transmitted when:

- 1. It is no longer necessary to hold the token

- All frames of all active requests have been transmitted

- 2. The token became unusable while servicing a request

- Asynchronous Priority threshold reached (If an Asynch Priority Request is being serviced)

- THT expired (if enabled)

When the ring becomes non-operational the current frame transmission is aborted. The ring may go non-operational while holding a token as a result of any one of the following conditions:

- A MAC Reset

- · Reception of a valid MAC frame

- TRT expiration, (TRT was reset when the token was captured)

### **Issue Token Type**

The criteria presented to the Ring Engine to begin a Service Opportunity, also contains the Issue Token Class. The Issue Token Class is used if servicing of that request was completed (the last frame of that request was transmitted), otherwise a token of the Capture Token Class is issued.

When servicing multiple requests on a single service opportunity, the Issue Token Class of the previous class becomes the capture class for the next request for purposes of determining usability.

The type of token issued depends on the service class and the type of token captured as shown in Table 5-2.

### 5.2.2 Service Opportunity while

### Ring Not Operational

While the ring is not operational, a service opportunity occurs if an immediate transmission is requested from the transmitter Data, Claim or Beacon State, and the transmitter is in the appropriate state.

The service opportunity continues until any one of the following conditions exist:

- 1. No (additional) frames are to be sent

- 2. TMAX of time elapses on this request

- 3. The transmitter exits the requested state

- 4. The ring becomes operational while servicing an immediate request

### 5.2.3 Frame Transmission

Frames associated with the current request may be transmitted at any time during a Service Opportunity. In many applications, data is ready to be transmitted when the request is presented to the interface. Soon after the Service Opportunity begins, frame transmission begins. In other applications in order to minimize the effects of ring latency it is desirable to capture the token when no data is ready to be transmitted. This capability results in wasted ring bandwidth and should be used judiciously.

During transmission, a byte stream is passed from the System Interface to the MAC Request Interface. The data is passed through the Ring Engine and appears at the PHY Request Interface two byte times later.

While a frame is being transmitted, the request parameters for the next request (if different) may be presented to the interface. At the end of the current frame transmission, a decision is made to continue or cancel the current service opportunity based on the new request parameters.

During a transmission several errors can occur. A transmission may be terminated unsuccessfully because of external buffering or interface parity errors, internal Ring Engine errors, a MAC reset, or reception of a MAC frame. When a transmission is aborted due to an external error (and Option.IRPT is not set), a Void frame is transmitted to reset the TVX timers in all stations in the ring. When a frame is aborted due to a transmission error, the Service Opportunity is not automatically ended.

### **5.3 REQUEST SERVICE PARAMETERS**

### 5.3.1 Request Service Class

The Request Service corresponds to the Request Service Class and the token class parameters of the (SM\_)MA\_DATA.request and (SM\_)MA\_Token.request primitives as specified in the Standard.

14 useful combinations of the Requested Service Class (Non-Restricted Asynchronous, Restricted Asynchronous, Synchronous, Immediate), the Token Capture and Issue Class, and THT Enable are supported by the Ring Engine as shown in Table 5-3.

| TABLE 5-2. Token | Transmissior | n Type |

|------------------|--------------|--------|

|------------------|--------------|--------|

| TABLE V LI I             | eken manenneelen ij | P0             |

|--------------------------|---------------------|----------------|

| Service Class            | Token Captured      | Token Issued   |

| Non-Restricted           | Non-Restricted      | Non-Restricted |

| Begin Restricted         | Non-Restricted      | Restricted     |

| Continue Restricted      | Restricted          | Restricted     |

| End Restricted           | Restricted          | Non-Restricted |

| Immediate                | None                | None           |

| Immediate Non-Restricted | None                | Non-Restricted |

| Immediate Restricted     | None                | Restricted     |

| TABLE 5-3. Request Service Classes |          |                |          |                  |                |       |  |  |  |

|------------------------------------|----------|----------------|----------|------------------|----------------|-------|--|--|--|

| RQRCLS                             | Name     | Class          | тнт      | Token<br>Capture | Token<br>Issue | Notes |  |  |  |

| 0000                               | None     | None           |          |                  |                |       |  |  |  |

| 0001                               | Apri_1   | Async<br>THSH1 | Enabled  | Non-rstr         | Non-rstr       |       |  |  |  |

| 0010                               | Reserved | Reserved       |          |                  |                |       |  |  |  |

| 0011                               | Reserved | Reserved       |          |                  |                |       |  |  |  |

| 0100                               | Syn      | Synch          | Disabled | Any              | Captured       | 1     |  |  |  |

| 0101                               | Imm      | Immediate      | Disabled | None             | None           | 4     |  |  |  |

| 0110                               | ImmN     | Immediate      | Disabled | None             | Non-rstr       | 4     |  |  |  |

| 0111                               | ImmR     | Immediate      | Disabled | None             | Rstr           | 4     |  |  |  |

| 1000                               | Asyn     | Asynch         | Enabled  | Non-rstr         | Non-rstr       |       |  |  |  |

| 1001                               | Rbeg     | Restricted     | Enabled  | Non-rstr         | Rstr           | 2, 3  |  |  |  |

| 1010                               | Rend     | Restricted     | Enabled  | Rstr             | Non-rstr       | 2     |  |  |  |

| 1011                               | Rcnt     | Restricted     | Enabled  | Rstr             | Rstr           | 2     |  |  |  |

| 1100                               | AsynD    | Asynch         | Disabled | Non-rstr         | Non-rstr       |       |  |  |  |

| 1101                               | RbeginD  | Restricted     | Disabled | Non-rstr         | Rstr           | 2, 3  |  |  |  |

| 1110                               | RenD     | Restricted     | Disabled | Rstr             | Non-rstr       | 2     |  |  |  |

| 1111                               | RcntD    | Restricted     | Disabled | Rstr             | Rstr           | 2     |  |  |  |

Note 1: Synchronous Requests are not serviced when bit BCNR of the Ring Event Latch Register is set.

Note 2: Restricted Requests are not serviced when bit BCNR, CLMR, or OTRMAC of the Ring Event Latch Register is set.

Note 3: Restricted Dialogues only begin when a Non-Restricted token has been received and transmitted.

Note 4: Immediate Requests are serviced when the ring is Non-Operational. These requests are serviced from the Data state if neither signal RQCLM nor RQBCN is asserted. If signal RQCLM is asserted, Immediate Requests are serviced from the Claim State. If signal RQBCN is asserted, Immediate Requests are serviced from the Beacon State. RQCLM and RQBCN do not cause transitions to the Claim and Beacon States.

Requests are serviced on a Service Opportunity meeting the requested criteria.

External support is required to limit the requests presented to the MAC Interface by different MAC Users (SMT, LLC, etc.).

A Token Capture Class of **non-rstr** indicates that the Transmitter Token Class must be Non-Restricted to begin servicing the request. A Token Capture Class of **rstr** indicates that the Transmitter Token Class must be Restricted to begin servicing the Request. A Token Issue Class of **non-rstr** means that the Transmitter Token Class will be Non-Restricted upon completion of the request. A Token Issue Class of **rstr** means that the Transmitter Token Class will be Restricted upon completion of the request.

### 5.3.2 Request Options

The Request Options provide the ability for Source Address Transparency (SAT) and FCS Transparency (FCST). In both cases, data from the request stream is transmitted in place of data from either the Ring Engine. The use of Source Address transparency has no effect on the sequencing of the interface. When Source Address transparency is not used, the SA from the internal parameter RAM is substituted for the SA bytes in the request stream, which must still be present. Since the FCS is appended to the frame, when FCS transparency is not used, no FCS bytes are present in the request stream.

#### Source Address Transparency

Normally the SA field in a frame is generated by the BMAC device, using either the MSA or MLA. When the SA Transparency option is selected, the SA from the data stream is transmitted in place of the MSA or MLA. The SAT option can be invoked on a per frame basis upon the assertion of the SAT signal (Pin 12).

When the SA Transparency option is selected, it is necessary to rely on an alternate stripping mechanism because stripping based on the returning SA only guarantees that frames with MSA or MLA will be stripped. Either the Void Stripping option (described below) may be invoked, or external hardware that forces stripping using the EM (External M\_Flag) signal is required.

The MSB of the SA is not controlled by this option. It is normally forced to Zero. It can be controlled using the Source Address MSB Transparency option described below.

SA Transparency is possible for all frames (including MAC frames). External support is required to limit the use of SA Transparency to certain MAC Users. SA Transparency should not be used with externally generated MAC Frames in order to maintain accountability, but this is not enforced by the Ring Engine.

SA Transparency also overrides the Long and Short Addressing enables. For example, if Long Addressing is not enabled, it is still possible to transmit frames with Long Addresses. Similarly, if Short Addressing is not enabled, it is still possible to transmit Frames with Short Addresses. This may be useful in full duplex point to point applications and for diagnostic purposes.

### Source Address Most Significant Bit Transparency

With the Source Address MSB Transparency option, the MSB of the SA is sourced from the data stream, as opposed to being transmitted as Zero. The SA MSB Transparency option is selected by asserting signal SAIGT (Pin 11).

Unless the Source Address Transparency option is also selected, the rest of the SA is generated by the Ring Engine.

The MSB of the SA is used to denote the presence of the Routing Information Field used in Source Routing algorithms (as in the IEEE 802.5 protocol). This option is useful for stations that utilize Source Routing. In these applications, the SA can still be generated by the Ring Engine, even when routing information is inserted into the data stream.

### Void Stripping

This option is useful for removing bridged and ownerless frames and remnants (fragments) from the ring.

In the Void Stripping protocol, two My\_Void frames are transmitted at the end of a service opportunity. Stripping continues until one of the following conditions occur:

- One My\_Void frames returns (The Second My\_Void will be stripped on the basis of the SA)

- · A Token is received

- An Other\_Void is received

- A MAC frame other than My\_Claim is received

- A MAC Reset occurs

If any frame of a Service Opportunity requests this option, then all frames on that service opportunity will be stripped using this method. Void Stripping is invoked upon the assertion of the STRIP signal (Pin 13) at the beginning of a frame transmission. Void Stripping is also automatically invoked by this station if it wins the Claim Process before the initial token is issued. This removes all fragments and ownerless frames from the ring when the ring becomes operational.

### FCS Transparency

Normally, the BMAC device generates and transmits the FCS. When the Frame Check Sequence Transparency option is selected, the Ring Engine device does not append the FCS to the end of the Information field. This option is selected by asserting signal FCST (Pin 14).

The receiving stations treat the last four bytes of the data stream as the FCS.

This option may be useful for end to end FCS coverage when crossing FDDI bridges, for diagnostic purposes, or in Implementer frames.

#### 5.4 FRAME VALIDITY PROCESSING

A valid frame is a frame that meets the minimum length criteria and contains an integral number of data symbol pairs between the Starting and Ending Delimiters as shown in Table 5-4.

On the Transmit side, frames are checked to see that they are of a minimum length. If the end of a frame is reached before a valid length is transmitted, the frame will be aborted and a Void frame will be transmitted (as with all aborted frames). A MAC frame with a zero length INFO field will not be aborted even though the Receiver will not recognize it as a valid frame. Frame lengths are not checked for the maximum allowable length (4500 bytes).