## **General Description**

DA9063 is a high current system PMIC suitable for dual- and quad-core processors used in smartphones, tablets, ultra-books, and other handheld and automotive applications that require up to 5 A core processor supply.

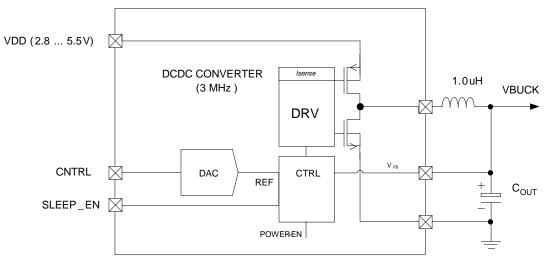

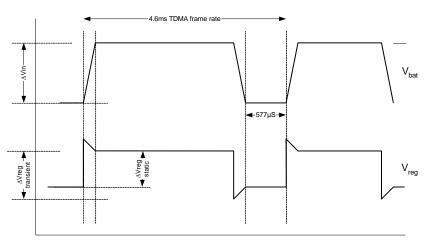

DA9063 contains six DC-DC buck converters designed for small external 1 µH inductors capable of supplying in total up to 12 A continuous output (0.3 V to 3.3 V). The buck converters do not require external Schottky diodes. They dynamically optimize their efficiency depending on the load current using an Automatic Sleep mode. The bucks incorporate pin and s/w controlled Dynamic Voltage Control (DVC) to support processor load adaptive adjustment of the supply voltage. One buck can also be used in a DDR memory termination mode.

Eleven SmartMirror<sup>™</sup> programmable LDO regulators are incorporated, rated up to 300 mA. All support remote capacitor placement and can support operation from a low 1.5 V/1.8 V input voltage: this allows the linear regulators to be cascaded with a suitable buck supply to improve overall system efficiency.

Processor core leakage can be minimized by using the integrated rail switch controller for ultra-fast power domain isolation/reconnection while current limited switches provide support for external peripherals such as external accessory or memory cards.

There are five distinct operating modes consuming < 20  $\mu$ A including a 1.5  $\mu$ A RTC mode with alarm and wake-up. A system monitor watchdog can be enabled in ACTIVE mode.

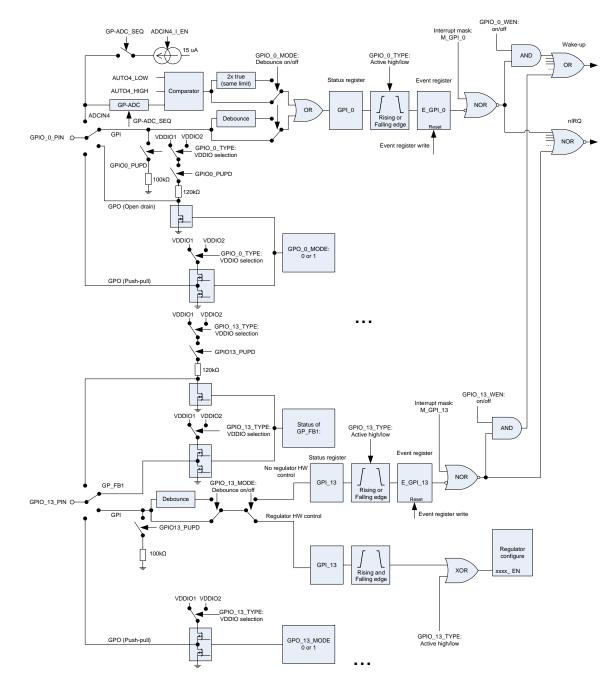

The DA9063 provides an OTP start-up sequencing engine that offers autonomous hardware system start-up or software controlled start-up and configurable power modes. The on key detects the button press time and offers configurable key lock and application shutdown functions. Up to 16 freely configurable GPIO pins can perform system functions, including: keypad supervision, application wake-up, and timing controlled external regulator, power switch, or other IC enable.

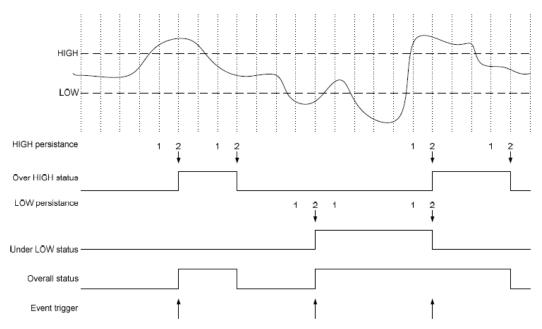

An integrated 10-channel ADC includes advanced voltage monitoring, internal temperature supervision, three general-purpose channels with programmable high/low thresholds, an integrated current source for resistive measurements, and system voltage monitoring with a programmable low-voltage warning. The ADC has 8-bit resolution in AUTO mode and 10-bit resolution in manual conversion mode.

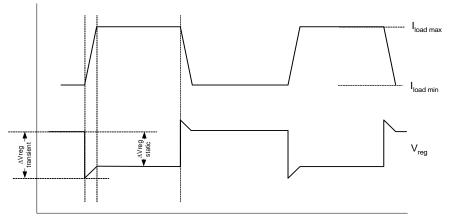

Three RGB-LED driver pins are provided with PWM control.

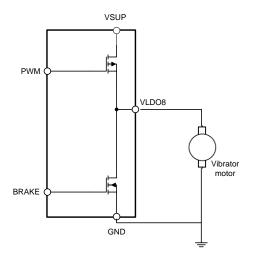

LDO8 can be configured as a 6-bit, PWM-controlled, vibration motor driver with automatic battery voltage correction.

| _ |    |            |   |   |   |     |

|---|----|------------|---|---|---|-----|

| D | -  | •          | _ | - | - | ٤.  |

|   | 21 | <b>r</b> 2 | 9 |   | - | r – |

|   | a  | LCI        | - | 6 |   |     |

### System PMIC for Mobile and Automotive Applications

## **Key Features**

- 6 DC-DC buck converters with DVC

- □ 2.5 A BuckCore1 5 A in dual phase

- □ 2.5 A BuckCore2 └ mode

- □ 2.5 A BuckPro

- □ 1.5 A BuckPeri

- 3 A in merged □ 1.5 A BuckMem mode

- 1.5 A BuckIO

- 3 MHz switching frequency (±10 %) (allows use of low profile [1 mm] 1 µH inductors)

- 11 programmable LDO regulators:

- □ 3 low noise, 4 with DVC, 5 with current limited switch mode

- Two rail switches

- Power Manager with programmable . regulators, rail switch start-up, and configurable low power modes

- Multiple master application support via two independent control interfaces

- System monitor with watchdog timer

- Up to 16 flexible GPIO pins for enhanced wake-up and peripheral control

# **Applications**

- Smartphones .

- Ultrabooks

- Tablets, e-books .

- Car infotainment and ADAS

- RGB-LED driver with autonomous flashing

- PWM vibration motor driver

- 10-bit ADC with nine channels and configurable alarm thresholds

- Regulator supervision with automatic under-/over-voltage protection

- Coin cell/super-capacitor backup charger

- Ultra-low power, 1.5 µA RTC with alarm and oscillator circuitry with crystal frequency adjustment

- -40 °C to +125 °C junction temperature operation

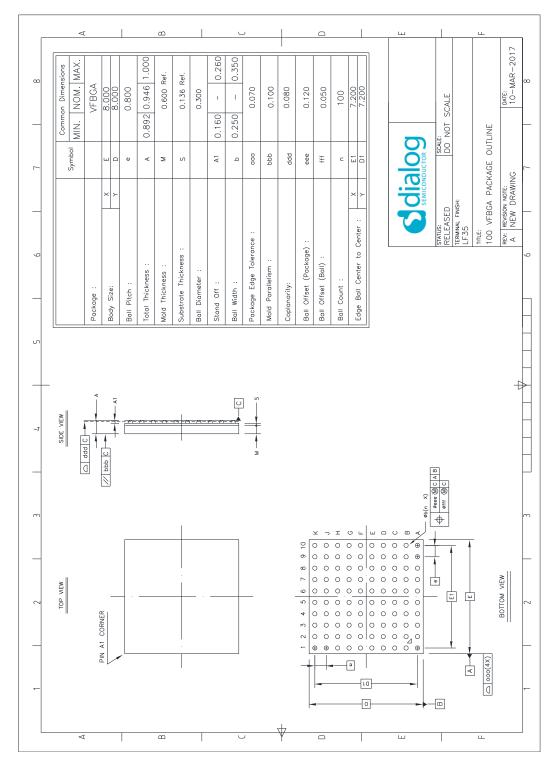

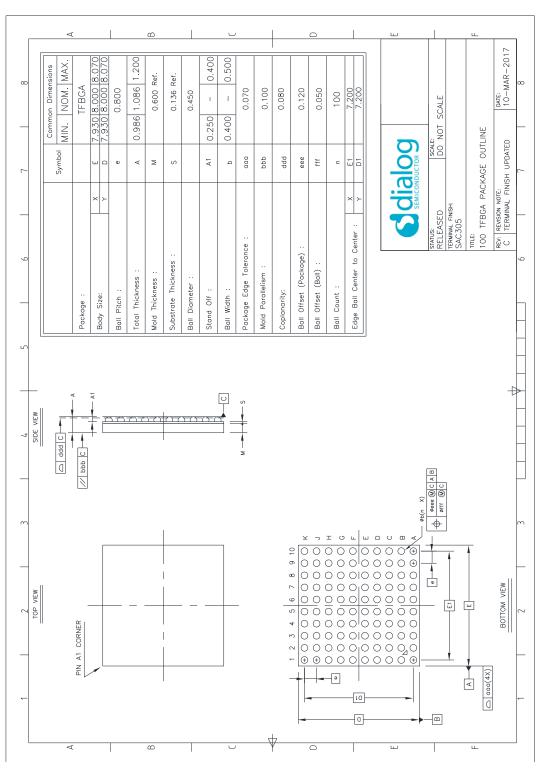

- Two package variants:

- □ 100 VFBGA 8.0 mm x 8.0 mm x 1.0 mm, 0.8 mm pitch, 0.30 mm balls

- 100 TFBGA 8.0 mm x 8.0 mm x 1.2 mm П 0.8 mm pitch, 0.45 mm balls

- Automotive AEC-Q100 Grade 2 available (DA9063L-A)

- Navigation devices

- Set-top boxes, TV, and media players

- Portable industrial and medical devices

- IoT devices

# System PMIC for Mobile and Automotive Applications

## Contents

| Ge | neral [       | Descriptio  | on                               | . 1 |  |  |  |  |  |

|----|---------------|-------------|----------------------------------|-----|--|--|--|--|--|

| Ke | y Feat        | ures        |                                  | . 2 |  |  |  |  |  |

| Ар | plicati       | ons         |                                  | . 2 |  |  |  |  |  |

| Со | ntents        |             |                                  | . 3 |  |  |  |  |  |

| 1  | Block Diagram |             |                                  |     |  |  |  |  |  |

| 2  |               | •           | rview                            |     |  |  |  |  |  |

| 3  | -             |             | nation                           |     |  |  |  |  |  |

| •  | 3.1           | -           | Outlines                         |     |  |  |  |  |  |

|    | 3.2           | •           |                                  |     |  |  |  |  |  |

| 4  | Elect         | rical Chai  | racteristics                     | 18  |  |  |  |  |  |

| -  | 4.1           |             | Maximum Ratings                  |     |  |  |  |  |  |

|    | 4.2           |             | ended Operating Conditions       |     |  |  |  |  |  |

|    |               | 4.2.1       | Power Derating Curves            |     |  |  |  |  |  |

|    | 4.3           | Typical C   | Current Consumption              | 22  |  |  |  |  |  |

|    | 4.4           | Digital I/C | D Characteristics                | 23  |  |  |  |  |  |

|    | 4.5           | Watchdo     | g                                | 25  |  |  |  |  |  |

|    | 4.6           | Power M     | anager and HS-2-Wire Control Bus | 25  |  |  |  |  |  |

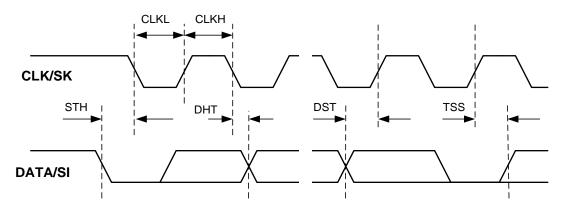

|    | 4.7           | 4-Wire C    | ontrol Bus                       | 26  |  |  |  |  |  |

|    | 4.8           | LDO Volt    | age Regulators                   | 28  |  |  |  |  |  |

|    |               | 4.8.1       | LDO1                             | 28  |  |  |  |  |  |

|    |               | 4.8.2       | LDO2                             | 29  |  |  |  |  |  |

|    |               | 4.8.3       | LDO3                             |     |  |  |  |  |  |

|    |               | 4.8.4       | LDO4                             |     |  |  |  |  |  |

|    |               | 4.8.5       | LDO5                             |     |  |  |  |  |  |

|    |               | 4.8.6       | LDO6                             |     |  |  |  |  |  |

|    |               | 4.8.7       | LD07                             |     |  |  |  |  |  |

|    |               | 4.8.8       | LDO8                             |     |  |  |  |  |  |

|    |               | 4.8.9       | LDO9                             |     |  |  |  |  |  |

|    |               | 4.8.10      | LDO10                            |     |  |  |  |  |  |

|    |               |             |                                  |     |  |  |  |  |  |

|    | 4.0           | 4.8.12      |                                  |     |  |  |  |  |  |

|    | 4.9           | 4.9.1       | Buck ConvertersBuckCORE2         |     |  |  |  |  |  |

|    |               | 4.9.1       | BUCKPRO                          |     |  |  |  |  |  |

|    |               | 4.9.2       | BUCKMEM                          |     |  |  |  |  |  |

|    |               | 4.9.3       | BUCKIO                           |     |  |  |  |  |  |

|    |               | 4.9.4       | BUCKPERI                         |     |  |  |  |  |  |

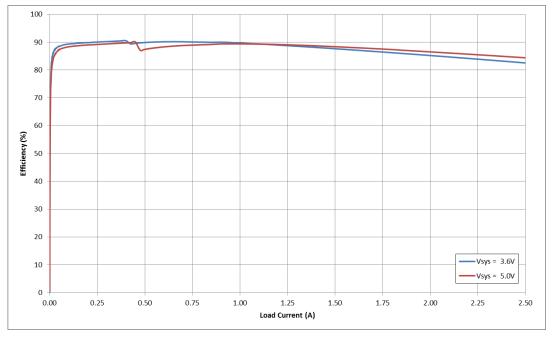

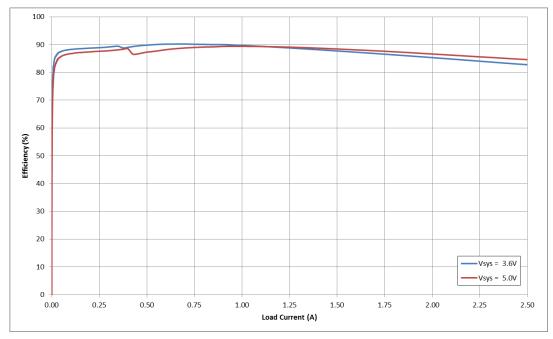

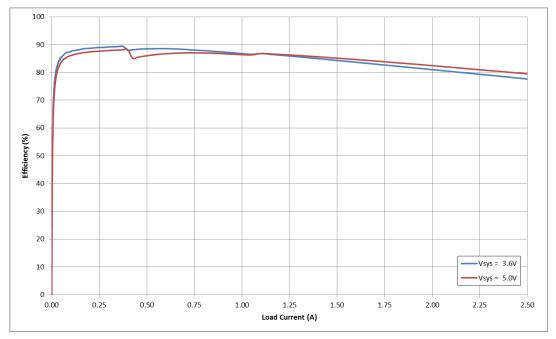

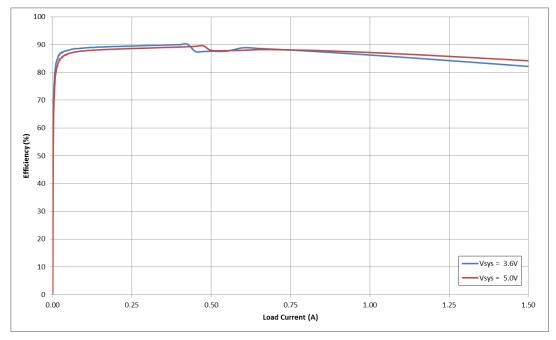

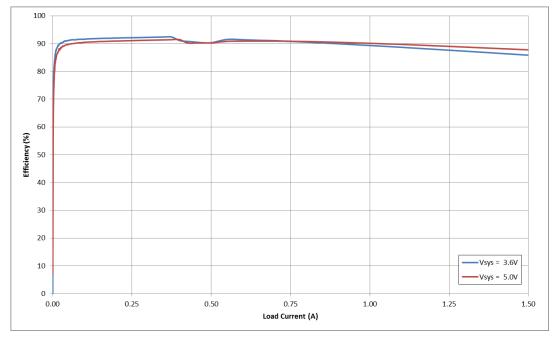

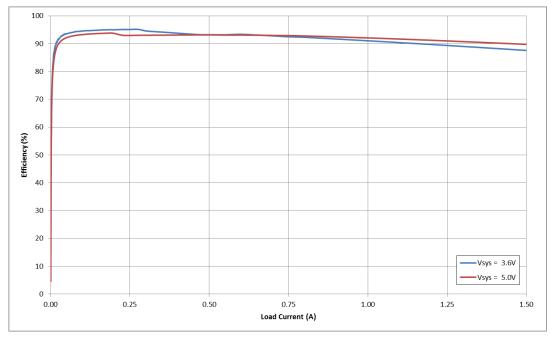

|    |               | 4.9.6       | Typical Characteristics          |     |  |  |  |  |  |

|    | 4.10          |             | I Switches                       |     |  |  |  |  |  |

# System PMIC for Mobile and Automotive Applications

|    | 4.11  | Backup Battery Charger |                                                                      |             |  |  |  |

|----|-------|------------------------|----------------------------------------------------------------------|-------------|--|--|--|

|    | 4.12  | General                | Purpose ADC                                                          | 64          |  |  |  |

|    | 4.13  | 32 kHz (               | Oscillator                                                           | 65          |  |  |  |

|    | 4.14  | Internal               | Oscillator                                                           | 66          |  |  |  |

|    | 4.15  | POR, R                 | eference Generation, and Voltage Supervision                         |             |  |  |  |

|    | 4.16  | Therma                 | I Supervision                                                        | 67          |  |  |  |

| 5  | Func  | tional De              | escription                                                           | 68          |  |  |  |

|    | 5.1   | Power N                | /anager IO Ports                                                     | 69          |  |  |  |

|    |       | 5.1.1                  | On/Off Port (nONKEY)                                                 | 69          |  |  |  |

|    |       | 5.1.2                  | Wake-up Port (CHG_WAKE)                                              | 70          |  |  |  |

|    |       | 5.1.3                  | Hardware Reset (nOFF, nSHUTDOWN, nONKEY, GPIO14, GPIO15<br>WATCHDOG) |             |  |  |  |

|    |       | 5.1.4                  | Reset Output (nRESET)                                                | 70          |  |  |  |

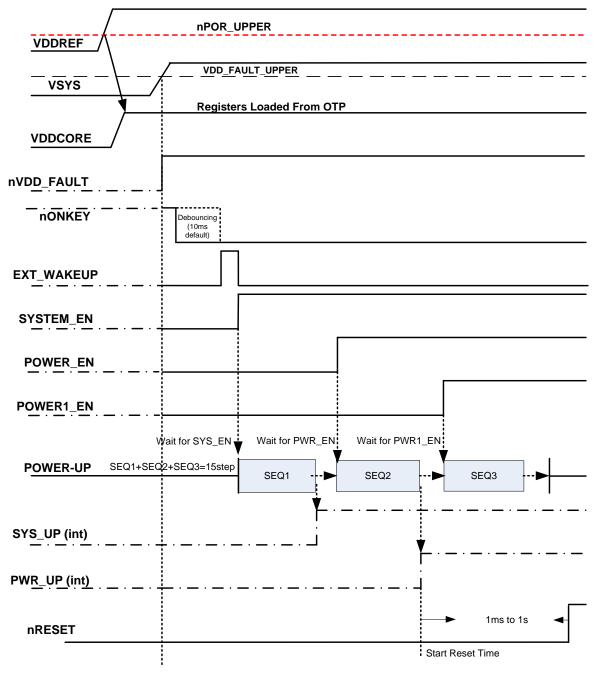

|    |       | 5.1.5                  | System Enable (SYS_EN)                                               | 71          |  |  |  |

|    |       | 5.1.6                  | Power Enable (PWR_EN)                                                | 71          |  |  |  |

|    |       | 5.1.7                  | Power1 Enable (PWR1_EN)                                              | 71          |  |  |  |

|    |       | 5.1.8                  | GP_FB1, General Purpose Signal 1 (EXT_WAKEUP/READY)                  | 71          |  |  |  |

|    |       | 5.1.9                  | GP_FB2, General Purpose Signal 2 (PWR_OK/KEEP_ACT)                   | 72          |  |  |  |

|    |       | 5.1.10                 | GP_FB3, General Purpose Signal 3 (OUT32K_2/nVIB_BRAKE)               |             |  |  |  |

|    |       | 5.1.11                 | Supply Rail Fault (nVDD_FAULT)                                       | 73          |  |  |  |

|    |       | 5.1.12                 | Interrupt Request (nIRQ)                                             |             |  |  |  |

|    |       | 5.1.13                 | Real Time Clock Output (OUT_32K)                                     |             |  |  |  |

|    |       | 5.1.14                 | IO Supply Voltage (VDD_IO1 and VDD_IO2)                              |             |  |  |  |

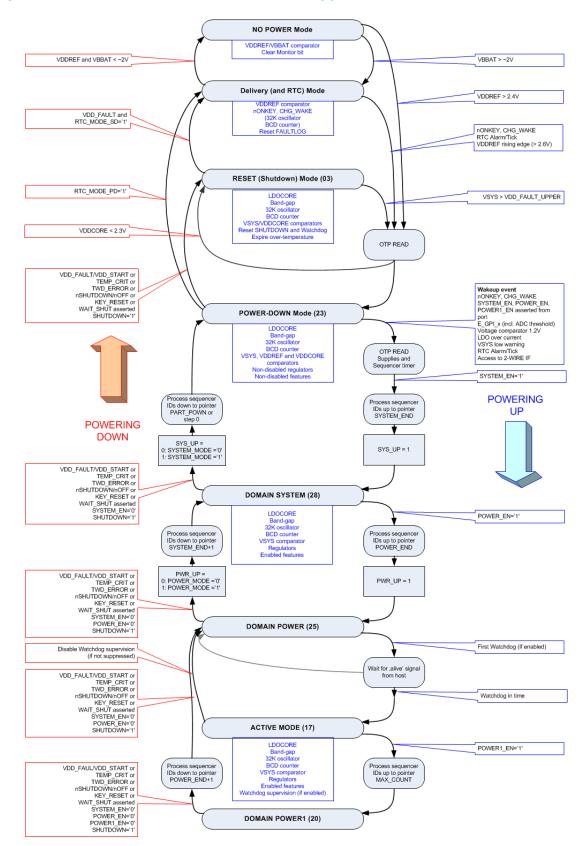

|    | 5.2   | Operatir               | ng Modes                                                             | 74          |  |  |  |

|    |       | 5.2.1                  | ACTIVE Mode                                                          |             |  |  |  |

|    |       | 5.2.2                  | POWERDOWN Mode                                                       |             |  |  |  |

|    |       | 5.2.3                  | RESET Mode                                                           |             |  |  |  |

|    |       | 5.2.4                  | RTC Mode                                                             |             |  |  |  |

|    |       | 5.2.5                  | DELIVERY Mode                                                        |             |  |  |  |

|    |       | 5.2.6                  | NO-POWER Mode                                                        |             |  |  |  |

|    |       | 5.2.7                  | Power Commander Mode                                                 |             |  |  |  |

|    | 5.3   | •                      | o from NO-POWER Mode                                                 |             |  |  |  |

|    |       | 5.3.1                  | Power-On-Reset (nPOR)                                                |             |  |  |  |

|    | 5.4   | -                      | Reset Mode and Application Wake-up                                   |             |  |  |  |

|    |       | 5.4.1                  | VDD_START                                                            |             |  |  |  |

|    |       | 5.4.2                  | Wake-Up Events                                                       |             |  |  |  |

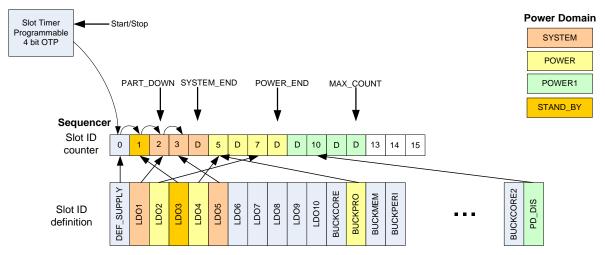

|    | 5.5   |                        | Supply Sequencer                                                     |             |  |  |  |

|    |       | 5.5.1                  | Powering Up                                                          |             |  |  |  |

|    |       | 5.5.2                  | Power-Up Timing                                                      |             |  |  |  |

|    |       | 5.5.3                  | Programmable Slot Delays                                             |             |  |  |  |

|    |       | 5.5.4                  | Powering Down                                                        |             |  |  |  |

|    | E C   | 5.5.5                  | User Programmable Delay                                              |             |  |  |  |

|    | 5.6   | •                      | Monitor (Watchdog)                                                   |             |  |  |  |

|    | 5.7   | GPIU E                 | xtender                                                              | 88          |  |  |  |

| Da | tashe | et                     | Revision 2.2                                                         | 12-Mar-2019 |  |  |  |

# System PMIC for Mobile and Automotive Applications

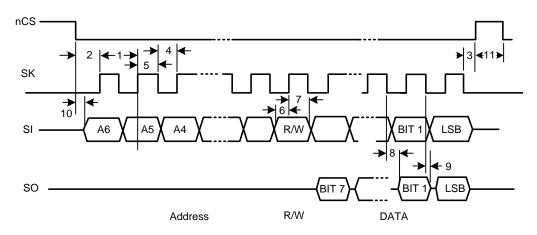

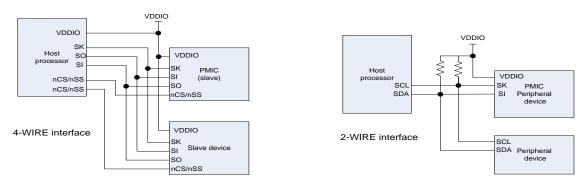

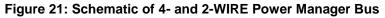

|   | 5.8   | Control    | Interfaces                                          |     |

|---|-------|------------|-----------------------------------------------------|-----|

|   |       | 5.8.1      | Power Manager Interface (4- and 2-WIRE Control Bus) |     |

|   |       | 5.8.2      | High Speed 2-WIRE Interface                         | 100 |

|   | 5.9   | Voltage    | Regulators                                          | 100 |

|   |       | 5.9.1      | Regulators Controlled by Software                   | 101 |

|   |       | 5.9.2      | Regulators Controlled by Hardware                   | 101 |

|   |       | 5.9.3      | Power Sequencer Control of LDOs                     | 102 |

|   |       | 5.9.4      | Dynamic Voltage Control                             | 103 |

|   |       | 5.9.5      | Voltage Tracking Mode LDO1                          | 103 |

|   |       | 5.9.6      | Pull-Down Resistor                                  | 103 |

|   |       | 5.9.7      | Bypass Mode and Current Limit                       |     |

|   |       | 5.9.8      | LDO Supply from Buck Converter                      |     |

|   |       | 5.9.9      | LDO Sleep Mode for Reduced IOUT                     |     |

|   |       | 5.9.10     | Vibration Motor Driver                              | 105 |

|   |       | 5.9.11     | Core Regulator LDOCORE                              | 105 |

|   | 5.10  | DC/DC      | Buck Converters                                     | 106 |

|   |       | 5.10.1     | Active Discharge                                    | 108 |

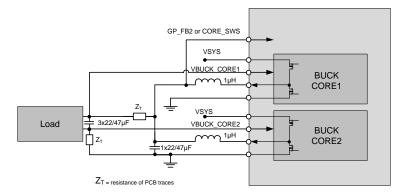

|   |       | 5.10.2     | BUCKCORE1, BUCKCORE2, and BUCKPRO                   | 108 |

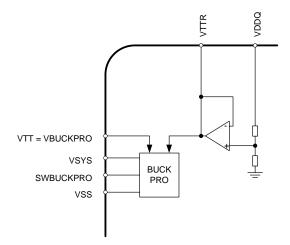

|   |       | 5.10.3     | BUCKPRO in DDR Memory Bus Termination Mode          | 109 |

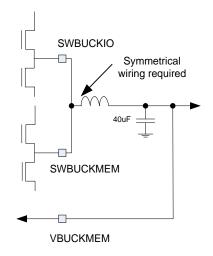

|   |       | 5.10.4     | BUCKMEM and BUCKIO in Merged Mode                   | 110 |

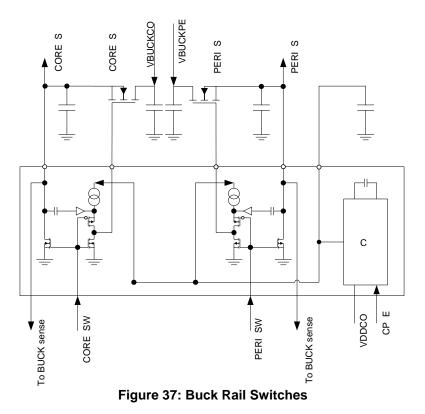

|   | 5.11  | Buck Ra    | ail Switches                                        | 111 |

|   | 5.12  | Backup     | Battery Charger/RTC Supply Rail Generator           | 112 |

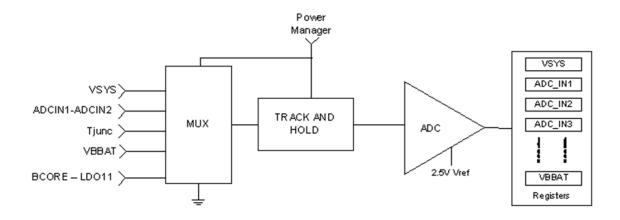

|   | 5.13  | Genera     | I Purpose ADC                                       | 113 |

|   |       | 5.13.1     | ADC Overview                                        | 113 |

|   |       | 5.13.2     | ADC Input MUX                                       | 113 |

|   |       | 5.13.3     | Manual Conversion Mode                              | 114 |

|   |       | 5.13.4     | Automatic Measurements Scheduler                    | 114 |

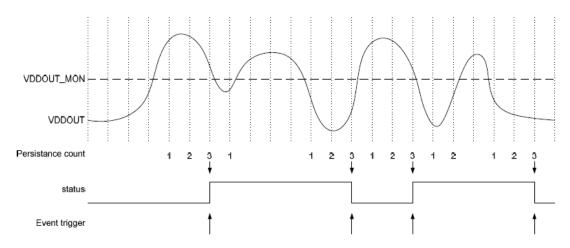

|   |       | 5.13.5     | Fixed Threshold Comparator                          | 118 |

|   | 5.14  | Real Tir   | me Clock                                            | 119 |

|   |       | 5.14.1     | 32 kHz Oscillator                                   | 119 |

|   |       | 5.14.2     | RTC Counter and Alarm                               | 121 |

|   | 5.15  | Adjusta    | ble Frequency Internal Oscillator                   | 122 |

|   | 5.16  | Referen    | nce Voltage Generation: VREF, VLNREF                | 122 |

|   | 5.17  | Therma     | Il Supervision                                      | 122 |

|   | 5.18  | Main Sy    | ystem Rail Voltage Supervision                      | 123 |

| 6 | Regis | ster Map   | )                                                   |     |

| 7 | Appli | ication li | nformation                                          |     |

| - | 7.1   |            | or Selection                                        |     |

|   | 7.2   | •          | Device                                              |     |

|   | 7.3   | •          | r Selection                                         |     |

|   | 7.4   |            | rs                                                  |     |

|   | 7.5   |            | I Pass Transistors                                  |     |

|   | 7.6   |            |                                                     |     |

| D | - | -  | ~ | h | ~ | ~ | ¢. |

|---|---|----|---|---|---|---|----|

| υ | a | La | Э |   | e | e | L  |

**Revision 2.2**

## System PMIC for Mobile and Automotive Applications

|    | 7.7   | Layout G   | Guidelines                                       | . 140 |

|----|-------|------------|--------------------------------------------------|-------|

|    |       | 7.7.1      | General Recommendations                          | . 140 |

|    |       | 7.7.2      | LDOs and Switched Mode Supplies                  | . 140 |

|    |       | 7.7.3      | Crystal Oscillator                               | . 140 |

|    |       | 7.7.4      | Thermal Connection, Land Pad, and Stencil Design | . 140 |

| 8  | Defin | itions     |                                                  | . 141 |

|    | 8.1   | Power D    | issipation and Thermal Design                    | . 141 |

|    | 8.2   | Regulato   | pr Parameter - Dropout Voltage                   | . 142 |

|    | 8.3   | Regulato   | or Parameter - Power Supply Rejection            | . 142 |

|    | 8.4   | Regulato   | or Parameter - Line Regulation                   | . 142 |

|    | 8.5   | Regulato   | or Parameter - Load Regulation                   | . 143 |

| 9  | Furth | er Applic  | ation Information                                | . 143 |

| 10 | Orde  | rina Infor | mation                                           | . 144 |

|    |       | -          | Ordering Information                             |       |

| Ap |       |            | ster Descriptions                                |       |

|    | A.1   | -          | Page Control                                     |       |

|    | A.2   | •          | Page 0                                           |       |

|    |       | A.2.1      | Power Manager Control and Monitoring             |       |

|    |       | A.2.2      | GPIO Control                                     |       |

|    |       | A.2.3      | Regulator Control                                | . 161 |

|    |       | A.2.4      | GPADC                                            | . 171 |

|    |       | A.2.5      | ADC Results                                      | . 172 |

|    |       | A.2.6      | RTC Calendar and Alarm                           | . 174 |

|    | A.3   | Register   | Page 1                                           | . 176 |

|    |       | A.3.1      | Power Sequencer                                  | . 177 |

|    |       | A.3.2      | Regulator Settings                               | . 182 |

|    |       | A.3.3      | Backup Battery Charger                           | . 217 |

|    |       | A.3.4      | High Power GPO PWM                               | . 218 |

|    |       | A.3.5      | GPADC Thresholds                                 | . 220 |

|    | A.4   | Register   | Page 2                                           | . 222 |

|    |       | A.4.1      | OTP                                              | . 222 |

|    |       | A.4.2      | Customer Trim and Configuration                  | . 223 |

|    | A.5   | Register   | Page 3                                           | . 237 |

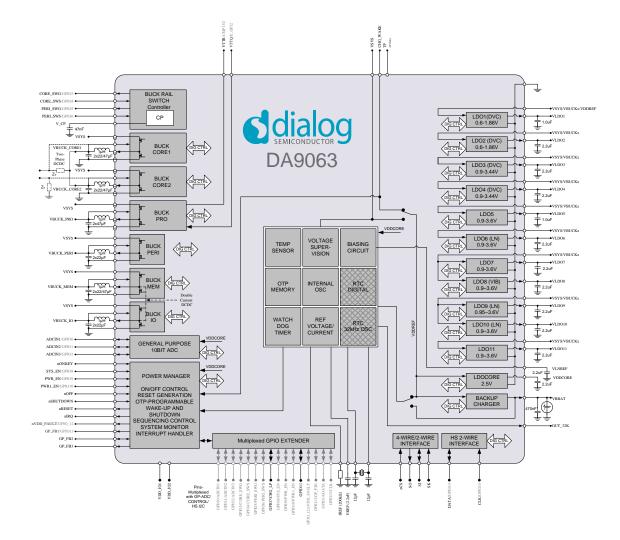

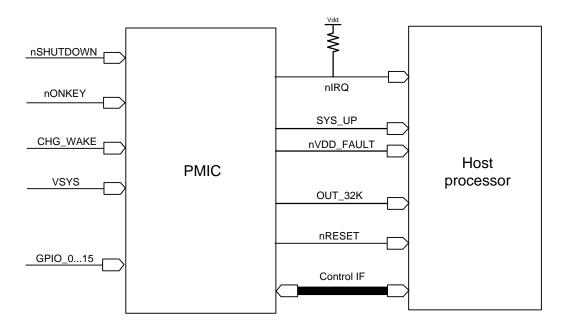

## 1 Block Diagram

Figure 1: Block Diagram

| Dat | tas | heet |

|-----|-----|------|

| _   |     |      |

# 2 Regulator Overview

### Table 1: Regulators

| Regulator | Supplied Pins | Supplied<br>Voltage<br>(V) | Supplied<br>Max.<br>Current<br>(mA)     | External<br>Component       | Notes                                                                                                                                                                                                                                                                                                                                                              |

|-----------|---------------|----------------------------|-----------------------------------------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BUCKCORE1 | VBUCKCORE1    | 0.3 to<br>1.57             | 1250/<br>2500<br>(full-current<br>mode) | 1.0 μΗ/<br>44 μF /<br>88 μF | <ul> <li>GPIO and host interface-<br/>controlled DVC with<br/>variable slew rate (10 mV<br/>in [0.5, 1.0, 2.0, 4.0] µs)</li> <li>10 mV steps</li> <li>&lt; 0.7 V PFM mode only</li> <li>2500 mA in full-current<br/>mode (double pass device<br/>and current limit)</li> <li>Provides dual-phase buck<br/>with up to 5 A if combined<br/>with BUCKCORE2</li> </ul> |

| BUCKCORE2 | VBUCKCORE2    | 0.3 to<br>1.57             | 1250/<br>2500<br>(full-current<br>mode) | 1.0 μH/<br>44/88 μF         | <ul> <li>GPIO and host interface-<br/>controlled DVC with<br/>variable slew rate (10 mV<br/>in [0.5/1.0/2.0/4.0] µs)</li> <li>10 mV steps</li> <li>&lt; 0.7 V PFM mode only</li> <li>2500 mA in full-current<br/>mode (double pass device<br/>and current limit)</li> <li>Provides dual-phase Buck<br/>if combined with<br/>BUCKCORE1</li> </ul>                   |

| BUCKPRO   | VBUCKPRO      | 0.53 to<br>1.80            | 1250/<br>2500<br>(full-current<br>mode) | 1.0 μΗ/<br>44/88 μF         | <ul> <li>GPIO and host interface-<br/>controlled DVC with<br/>variable slew rate, (10 mV<br/>in [0.5/1.0/2.0/4.0] μs)</li> <li>10 mV steps and VTT<br/>regulator mode</li> <li>&lt; 0.7 V PFM mode only</li> <li>2500 mA in full-current<br/>mode (double pass device<br/>and current limit)</li> </ul>                                                            |

| BUCKMEM   | VBUCKMEM      | 0.8 to<br>3.34             | 1500                                    | 1.0 μΗ/<br>44 μF            | <ul> <li>GPIO and host interface-controlled DVC with variable slew rate (10 mV in [0.5/1.0/2.0/4.0] µs)</li> <li>20 mV steps</li> <li>Can be merged with BUCK_IO towards single buck with up to 3 A output current</li> </ul>                                                                                                                                      |

# System PMIC for Mobile and Automotive Applications

| Regulator | Supplied Pins | Supplied<br>Voltage<br>(V) | Supplied<br>Max.<br>Current<br>(mA) | External<br>Component | Notes                                                                                                                                                                                                                                   |

|-----------|---------------|----------------------------|-------------------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| вискіо    | VBUCKIO       | 0.8 to<br>3.34             | 1500                                | 1.0 μH/<br>44 μF      | <ul> <li>GPIO and host interface-<br/>controlled DVC with<br/>variable slew rate (10 mV<br/>in [0.5/1.0/2.0/4.0] µs)</li> </ul>                                                                                                         |

|           |               |                            |                                     |                       | <ul> <li>20 mV steps, can be<br/>merged with BUCK_MEM</li> </ul>                                                                                                                                                                        |

| BUCKPERI  | VBUCKPERI     | 0.8 to<br>3.34             | 1500                                | 1.0 μΗ/<br>44 μF      | <ul> <li>GPIO and host interface-<br/>controlled DVC with<br/>variable slew rate (10 mV<br/>in [0.5/1.0/2.0/4.0] µs)</li> <li>20 mV steps</li> </ul>                                                                                    |

| LDO1      | VLDO1         | 0.6 to<br>1.86             | 100                                 | 1.0 µF                | <ul> <li>20 mV steps</li> <li>GPIO and host interface-<br/>controlled DVC with<br/>variable slew rate (10 mV<br/>in [0.5/1.0/2.0/4.0] µs)</li> <li>20 mV steps</li> <li>Optional voltage tracking of<br/>BUCKCORE or BUCKPRO</li> </ul> |

| LDO2      | VLDO2         | 0.6 to<br>1.86             | 200                                 | 2.2 µF                | <ul> <li>GPIO and host interface-<br/>controlled DVC with<br/>variable slew rate (10 mV<br/>in [0.5/1.0/2.0/4.0] µs)</li> <li>20 mV steps</li> </ul>                                                                                    |

| LDO3      | VLDO3         | 0.9 to<br>3.44             | 200                                 | 2.2 µF                | <ul> <li>Bypass mode</li> <li>GPIO and host interface-<br/>controlled DVC with<br/>variable slew rate (10 mV<br/>in [0.5/1.0/2.0/4.0] µs)</li> <li>20 mV steps</li> </ul>                                                               |

| LDO4      | VLDO4         | 0.9 to<br>3.44             | 200                                 | 2.2 µF                | <ul> <li>Bypass mode</li> <li>GPIO and host interface-<br/>controlled DVC with<br/>variable slew rate (10 mV<br/>in [0.5/1.0/2.0/4.0] µs)</li> <li>20 mV steps</li> </ul>                                                               |

| LDO5      | VLDO5         | 0.9 to 3.6                 | 100                                 | 1.0 µF                | 50 mV steps                                                                                                                                                                                                                             |

| LDO6      | VLDO6         | 0.9 to 3.6                 | 200                                 | 2.2 µF                | <ul><li>Low noise</li><li>50 mV steps</li></ul>                                                                                                                                                                                         |

| LDO7      | VLDO7         | 0.9 to 3.6                 | 200                                 | 2.2 µF                | <ul> <li>Bypass mode</li> <li>50 mV steps</li> <li>Common supply with LDO8</li> </ul>                                                                                                                                                   |

Datasheet

**Revision 2.2**

# System PMIC for Mobile and Automotive Applications

| Regulator | Supplied Pins           | Supplied<br>Voltage<br>(V) | Supplied<br>Max.<br>Current<br>(mA) | External<br>Component | Notes                                                                                                                                          |

|-----------|-------------------------|----------------------------|-------------------------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| LDO8      | VLDO8                   | 0.9 to 3.6                 | 200                                 | 2.2 µF                | <ul> <li>Bypass and switching<br/>vibration motor driver<br/>mode</li> <li>50 mV steps</li> <li>Common supply with<br/>LDO7</li> </ul>         |

| LDO9      | VLDO9                   | 0.95 to<br>3.6             | 200                                 | 2.2 µF                | <ul> <li>Low noise</li> <li>50 mV steps</li> <li>OTP trimmed</li> <li>Common supply with<br/>LDO10</li> </ul>                                  |

| LDO10     | VLDO10                  | 0.9 to 3.6                 | 300                                 | 2.2 µF                | <ul> <li>Low noise LDO</li> <li>50 mV steps</li> <li>Common supply with LDO9</li> </ul>                                                        |

| LDO11     | VLDO11                  | 0.9 to 3.6                 | 300                                 | 2.2 µF                | <ul><li>Bypass mode</li><li>50 mV steps</li></ul>                                                                                              |

| BACKUP    | VBBAT                   | 1.1 to 3.1                 | 6                                   | 470 nF                | <ul> <li>100/200 mV steps</li> <li>Configurable charge current between 100 μA and 6000 μA</li> <li>Reverse current protection (RCP)</li> </ul> |

| LDOCORE   | Internal PMIC<br>supply | 2.5 ± 2 %<br>accuracy      | 4                                   | 2.2 µF                | <ul><li>Internal LDO</li><li>OTP trimmed</li></ul>                                                                                             |

### **System PMIC for Mobile and Automotive Applications**

## **3** Package Information

### 3.1 Package Outlines

Datasheet

**Revision 2.2**

#### 12-Mar-2019

#### Figure 2: Package Outline Drawing 100 VFBGA 0.3 mm Ball Diameter

| Da | tas | he | et |

|----|-----|----|----|

|    |     |    |    |

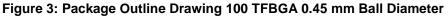

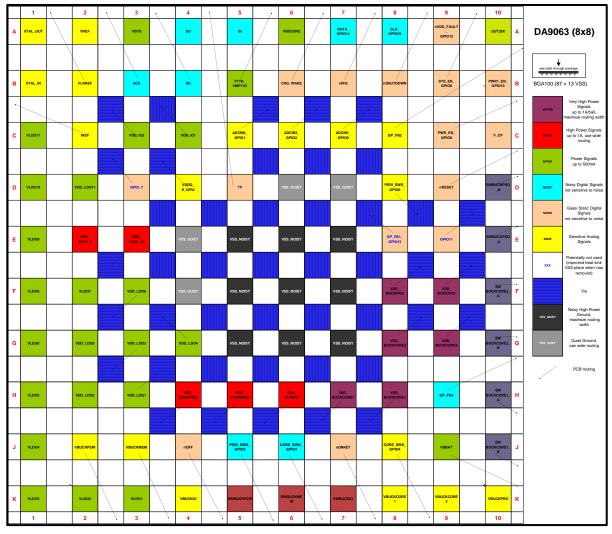

### 3.2 Pinout

### Figure 4: Connection Diagram

### Table 2: Pin Type Definition

| Pin Type | Description          | Pin Type | Description         |

|----------|----------------------|----------|---------------------|

| DI       | Digital input        | AI       | Analog input        |

| DO       | Digital output       | AO       | Analog output       |

| DIO      | Digital input/output | AIO      | Analog input/output |

| PWR      | Power supply         | GND      | Ground connection   |

| _ |   |    |   |   |   |   |  |

|---|---|----|---|---|---|---|--|

| n | - | •  | - | b | - | - |  |

| L |   | ta |   |   | е | - |  |

|   |   |    |   |   |   |   |  |

### **Table 3: Pin Description**

| Pin     | Pin Name   | Alternate<br>Function | Type<br>(Table 2) | Description                                                                                                                                                                                                                 |

|---------|------------|-----------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power N | lanager    |                       |                   |                                                                                                                                                                                                                             |

| A9      | nVDD_FAULT | GPIO12                | DO/DIO            | Indication for low supply voltage / GPIO12 / VDD_MON controlled GPO                                                                                                                                                         |

| B6      | CHG_WAKE   |                       | DI/PWR            | Wake-up signal from companion charger to trigger a start-up and temporary supply voltage for PMIC (VBUS_PROT in case of an inserted supply until charger Buck provides power to $V_{SYS}$ ).<br>Connect to GND if not used. |

| B7      | nIRQ       |                       | DO                | IRQ line for host                                                                                                                                                                                                           |

| B8      | nSHUTDOWN  |                       | DI                | Active-low input from switch or host to initiate shutdown                                                                                                                                                                   |

| B9      | SYS_EN     | GPIO8                 | DI/DIO            | Hardware enable of power domain<br>SYSTEM/GPIO8                                                                                                                                                                             |

| B10     | PWR1_EN    | GPIO10                | DI/DIO            | Hardware enable of power domain<br>POWER1/GPIO10 with high power output / input<br>for power sequencer WAIT ID                                                                                                              |

| C3      | VDD_IO2    |                       | PWR               | Alternate supply I/O voltage                                                                                                                                                                                                |

| C4      | VDD_IO1    |                       | PWR               | First supply I/O voltage rail                                                                                                                                                                                               |

| C8      | GP_FB2     |                       | DO/DI             | PWR_OK status indicator: all supervised<br>regulators are in-range / HW input for watchdog<br>supervision / dual-phase BUCKCORE voltage<br>sense at output capacitor                                                        |

| C9      | PWR_EN     | GPIO9                 | DI/DIO            | Hardware enable of power domain power / sequencer controlled GPO                                                                                                                                                            |

| D3      | GPIO7      |                       | DIO               | Sequencer controlled GPO                                                                                                                                                                                                    |

| D5      | ТР         |                       | DIO               | Test pin: enables power commander boot mode<br>and supply pin for OTP fusing voltage                                                                                                                                        |

| D9      | nRESET     |                       | DO                | Active low reset for host                                                                                                                                                                                                   |

| E8      | GP_FB1     | GPIO13                | DO/DIO            | Status indication for host of a valid wake-up<br>event (EXT_WAKEUP) / indicator for on-going<br>power mode transition (READY) / GPIO13,<br>regulator HW control                                                             |

| E9      | GPIO11     |                       | DIO               | GPIO11 with high power output and blinking feature                                                                                                                                                                          |

| H9      | GP_FB3     |                       | DO/DO             | Second 32 kHz oscillator output: OUT32_2 /<br>VIB_BREAK control signal for vibration motor<br>driver (LDO8)                                                                                                                 |

| J4      | nOFF       |                       | DI                | Active-low input from error indication line to initiate fast emergency shutdown                                                                                                                                             |

| J7      | nONKEY     |                       | DI                | On/off key with optional long press shutdown                                                                                                                                                                                |

**Revision 2.2**

| Pin      | Pin Name          | Alternate<br>Function | Type<br>(Table 2) | Description                                                                                                                      |

|----------|-------------------|-----------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------|

| 4-Wire/2 | 2-Wire Interfaces |                       | ·                 | ·                                                                                                                                |

| A4       | SO                |                       | DO                | 4-wire data output                                                                                                               |

| A5       | SI                |                       | DIO               | 4-wire data input / 2-wire data                                                                                                  |

| A7       | DATA              | GPIO14                | DIO               | HS-2-WIRE data / GPIO14 (optional reset if long<br>press in parallel with GPI15) with high power<br>output and blinking feature  |

| A8       | CLK               | GPIO15                | DI                | HS-2-WIRE clock / GPIO15 (optional reset if<br>long press in parallel with GPI14) with high<br>power output and blinking feature |

| B3       | nCS               |                       | DI                | 4-wire (active low) chip select                                                                                                  |

| B4       | SK                |                       | DI                | 4-wire/2-wire clock                                                                                                              |

| Voltage  | Regulators        |                       |                   |                                                                                                                                  |

| A3       | VSYS              |                       | PWR               | Supply voltage for PMIC and input for voltage supervision (decouple with 1.0 μF)                                                 |

| A6       | VDDCORE           |                       | AO                | Regulated supply for internal circuitry<br>(2.2 V/2.5 V)<br>(decouple with 2.2 μF)                                               |

| C1       | VLDO11            |                       | AO                | Output voltage from LDO11                                                                                                        |

| D1       | VLDO10            |                       | AO                | Output voltage from LDO10                                                                                                        |

| D2       | VDD_LDO11         |                       | PWR               | Supply voltage for LDO11                                                                                                         |

| E1       | VLDO9             |                       | AO                | Output voltage from LDO9                                                                                                         |

| E2       | VDD_LDO7_8        |                       | PWR               | Supply voltage for LDO7 and LDO8                                                                                                 |

| E3       | VDD_LDO9_10       |                       | PWR               | Supply voltage for LDO9 and LDO10                                                                                                |

| F1       | VLDO8             |                       | AO                | Output voltage from LDO8                                                                                                         |

| F2       | VLDO7             |                       | AO                | Output voltage from LDO7                                                                                                         |

| F3       | VDD_LDO6          |                       | PWR               | Supply voltage for LDO6                                                                                                          |

| G1       | VLDO6             |                       | AO                | Output voltage from LDO6                                                                                                         |

| G2       | VDD_LDO5          |                       | PWR               | Supply voltage for LDO5                                                                                                          |

| G3       | VDD_LDO3          |                       | PWR               | Supply voltage for LDO3                                                                                                          |

| G4       | VDD_LDO4          |                       | PWR               | Supply voltage for LDO4                                                                                                          |

| H1       | VLDO5             |                       | AO                | Output voltage from LDO5                                                                                                         |

| H2       | VDD_LDO2          |                       | PWR               | Supply voltage for LDO2                                                                                                          |

| H3       | VDD_LDO1          |                       | PWR               | Supply voltage for LDO1                                                                                                          |

| J1       | VLDO4             |                       | AO                | Output voltage from LDO4                                                                                                         |

| K1       | VLDO3             |                       | AO                | Output voltage from LDO3                                                                                                         |

| K2       | VLDO2             |                       | AO                | Output voltage from LDO2                                                                                                         |

| K3       | VLDO1             |                       | AO                | Output voltage from LDO1                                                                                                         |

Datasheet

**Revision 2.2**

| Pin     | Pin Name        | Alternate<br>Function | Type<br>(Table 2) | Description                                                                                       |

|---------|-----------------|-----------------------|-------------------|---------------------------------------------------------------------------------------------------|

| DC/DC E | Buck Converters |                       |                   |                                                                                                   |

| A1      | XTAL_OUT        |                       | AIO               | 32 kHz crystal connection<br>(adjust with 10 pF)                                                  |

| A2      | VREF            |                       | AIO               | Filter node for internal reference voltage (decouple with 0.22 $\mu\text{F})$                     |

| A10     | OUT_32K         |                       | DO                | 32 kHz oscillator buffer                                                                          |

| B1      | XTAL_IN         |                       | AIO               | 32 kHz crystal connection<br>(adjust with 10 pF)                                                  |

| B2      | VLNREF          |                       |                   | Filter node for LN (low noise)<br>(decouple with 0.22 μF)                                         |

| B5      | VTTR            | CMP1V2                | AO/DO             | Memory bus termination reference voltage (50 % of VDDQ), COMP1V2 controlled GPO                   |

| C2      | IREF            |                       | AO                | Connection for bias setting (configure with high precision 200 $k\Omega$ resistor)                |

| C5      | ADCIN2          | GPIO1                 | AI/DIO            | Connection to GPADC channel 2 with 1.2 V HW comparator IRQ/GPIO1, regulator HW control            |

| C6      | ADCIN3          | GPIO2                 | AI/DIO            | Connection to GPADC channel 3/GPIO2, regulator HW control                                         |

| C7      | ADCIN1          | GPIO0                 | AI/DIO            | Connection to GPADC auto channel 1 with<br>threshold IRQ and resistor measurement<br>option/GPIO0 |

| C10     | V_CP            |                       | AIO               | Charge pump output bypass<br>(decouple with 10 nF)                                                |

| D4      | VDDQ            | E_GPI2                | AI/DO             | BUCKPRO target voltage sense port / state of<br>E_GPI2 controlled GPO                             |

| D8      | PERI_SWS        | GPIO6                 | AI/DO             | BUCKPERI sense node from rail switch output/<br>GPIO6<br>Pulled down when switch is open          |

| D10     | SWBUCKPRO_B     |                       | AO                | Switching node for BUCKPRO (full-current)                                                         |

| E10     | SWBUCKPRO_A     |                       | AO                | Switching node for BUCKPRO (half-current)                                                         |

| F8, F9  | VDD_BUCKPRO     |                       | PWR               | Supply voltage for buck<br>To be connected to VSYS                                                |

| F10     | SWBUCKCORE2_A   |                       | AO                | Switching node for BUCKCORE2 (half-current)                                                       |

| G8, G9  | VDD_BUCKCORE2   |                       | PWR               | Supply voltage for buck<br>To be connected to VSYS                                                |

| G10     | SWBUCKCORE2_B   |                       | AO                | Switching node for BUCKCORE2 (full-current)                                                       |

| H4      | VDD_BUCKPERI    |                       | PWR               | Supply voltage for buck<br>To be connected to VSYS                                                |

| H5      | VDD_BUCKMEM     |                       | PWR               | Supply voltage for buck<br>To be connected to VSYS                                                |

| H6      | VDD_BUCKIO      |                       | PWR               | Supply voltage for buck<br>To be connected to VSYS                                                |

Datasheet

**Revision 2.2**

12-Mar-2019

# System PMIC for Mobile and Automotive Applications

| Pin                    | Pin Name        | Alternate<br>Function | Type<br>(Table 2) | Description                                                                                                                                                                                   |

|------------------------|-----------------|-----------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| H7, H8                 | VDD_BUCKCORE1   |                       | PWR               | Supply voltage for buck<br>To be connected to VSYS                                                                                                                                            |

| H10                    | SWBUCKCORE1_A   |                       | AO                | Switching node for BUCKCORE1 (half-current)                                                                                                                                                   |

| J2                     | VBUCKPERI       |                       | AI                | Sense node for BUCKPERI                                                                                                                                                                       |

| J3                     | VBUCKMEM        |                       | AI                | Sense node for DC/DC BUCKMEM                                                                                                                                                                  |

| J5                     | PERI_SWG        | GPIO5                 | AIO/DIO           | NMOS gate driver for buck rail switch/GPIO5                                                                                                                                                   |

| J6                     | CORE_SWG        | GPIO3                 | AIO/DIO           | NMOS gate driver for buck rail switch/GPIO3                                                                                                                                                   |

| J8                     | CORE_SWS        | GPIO4                 | AI/DO             | BUCKCORE sense node from rail switch output<br>or output capacitor of dual-phase BUCKCORE/<br>connection of internal switch to the output of<br>LDO1/GPIO4<br>Pulled down when switch is open |

| J10                    | SWBUCKCORE1_B   |                       | AO                | Switching node for BUCKCORE1 (full-current)                                                                                                                                                   |

| K4                     | VBUCKIO         |                       | AI                | Sense node for BUCKIO                                                                                                                                                                         |

| K5                     | SWBUCKPERI      |                       | AO                | Switching node for BUCKPERI                                                                                                                                                                   |

| K6                     | SWBUCKMEM       |                       | AO                | Switching node for BUCKMEM                                                                                                                                                                    |

| K7                     | SWBUCKIO        |                       | AO                | Switching node for BUCKIO<br>To be connected to SWBUCKMEM for buck<br>merge                                                                                                                   |

| K8                     | VBUCKCORE1      |                       | AI                | Sense node for BUCKCORE1                                                                                                                                                                      |

| K9                     | VBUCKCORE2      |                       | AI                | Sense node for BUCKCORE2                                                                                                                                                                      |

| K10                    | VBUCKPRO        |                       | AI                | Sense node for BUCKPRO                                                                                                                                                                        |

| Backup                 | Battery Charger |                       |                   |                                                                                                                                                                                               |

| J9                     | VBBAT           |                       | AIO               | Backup battery connection<br>Coin-cell or super-cap (decouple with 470 nF)                                                                                                                    |

| Vss                    |                 |                       |                   |                                                                                                                                                                                               |

| D6-7,<br>E4, F4        | GND             |                       | GND               | VSS_LDO, VSS_ADC, VSS_CORE, VSUB                                                                                                                                                              |

| E5-7,<br>F5-7,<br>G5-7 | GND             |                       | GND               | VSS_BUCKCORE1_A, VSS_BUCKCORE1_B,<br>VSS_BUCKCORE2_A, VSS_BUCKCORE2_B,<br>VSS_BUCK_PRO_A, VSS_BUCK_PRO_B,<br>VSS_BUCK_IO, VSS_BUCK_MEM,<br>VSS_BUCK_PERI                                      |

Datasheet

## **4** Electrical Characteristics

### 4.1 Absolute Maximum Ratings

Table 4 lists the absolute maximum ratings of the device. Exceeding these ratings may cause permanent damage to the device. Device functionality is only guaranteed under the conditions listed in Sections 4.1 and 4.2. Operating the device in conditions exceeding those listed in Table 5 but compliant with the absolute maximum ratings listed in Table 4, for extended periods of time may affect device reliability.

| Parameter          | Description                                   | Conditions     | Min  | Тур | Max                      | Unit |

|--------------------|-----------------------------------------------|----------------|------|-----|--------------------------|------|

| T <sub>STG</sub>   | Storage temperature                           |                | -65  |     | +150                     | °C   |

| TJ                 | Junction temperature                          | Note 1         | -40  |     | +150                     | °C   |

| Vsys,<br>Vchg_wake |                                               |                | -0.3 |     | 6.0                      | V    |

| VBBAT              | Cumplus stars                                 |                | -0.3 |     | 3.25                     | V    |

| VTP                | Supply voltage                                | Note 3         | -0.3 |     | 8.0                      | V    |

| All other<br>pins  |                                               | Note 2         | -0.3 |     | V <sub>DDREF</sub> + 0.3 | V    |

| Vesd_hbm           | ESD protection -<br>Human Body Model<br>(HBM) |                | 2000 |     |                          | V    |

|                    | ESD protection -                              | Corner pins    | 750  |     |                          |      |

| Vesd_cdm           | Charged Device Model<br>(CDM)                 | All other pins | 500  |     |                          | V    |

#### Table 4: Absolute Maximum Ratings

**Note 1** See Section 4.16 and Section 5.17.

**Note 2** Maximum 6.0 V. An internal node V<sub>DDREF</sub> is defined as the higher rail of CHG\_WAKE and VSYS.

**Note 3** Voltage on TP pin should be 0 V except during in-circuit programming.

### 4.2 Recommended Operating Conditions

All voltages are referenced to VSS unless otherwise stated. Currents flowing into DA9063 are deemed positive; currents flowing out are deemed negative. All parameters are valid over the recommended temperature range and power supply range unless otherwise stated. Please note that the power dissipation must be limited to avoid overheating of DA9063.

| Table 5: Recommended | Operating | Conditions |

|----------------------|-----------|------------|

|----------------------|-----------|------------|

| Parameter                      | Description              | Conditions | Min  | Тур | Max  | Unit |

|--------------------------------|--------------------------|------------|------|-----|------|------|

| TJ                             | Junction temperature     |            | -40  |     | +125 | °C   |

| Vsys,<br>V <sub>CHG_WAKE</sub> | Supply voltage           |            | 0    |     | 5.5  | V    |

| VBBAT                          | Backup supply voltage    |            | 0    |     | 3.15 | V    |

| VDD_IO1/2                      | Supply voltage IO        | Note 1     | 1.2  |     | 3.6  | V    |

| V <sub>TP</sub>                | TP programming<br>supply | Note 4     | 7.25 | 7.5 | 7.75 | V    |

**Datasheet**

**Revision 2.2**

12-Mar-2019

### System PMIC for Mobile and Automotive Applications

| Parameter | Description                         | Conditions                                                                                       | Min  | Тур   | Max  | Unit |

|-----------|-------------------------------------|--------------------------------------------------------------------------------------------------|------|-------|------|------|

| Іоит      | BUCKCORE1,<br>BUCKCORE2,<br>BUCKPRO | Note 2                                                                                           |      |       | 2500 | mA   |

| lout      | BUCKMEM,<br>BUCKIO,<br>BUCKPERI     | Note 2                                                                                           |      |       | 1500 | mA   |

|           | Thermal resistance                  | 100 VFBGA package<br>Note 3                                                                      |      | 27.7  |      | °C/W |

| θја       | junction to ambient                 | 100 TFBGA package<br>Note 3                                                                      |      | 26.1  |      | °C/W |

| өлс       | Thermal resistance junction to case | 100 TFBGA package<br>Note 3                                                                      |      | 10.67 |      | °C/W |

| De        | Maximum power<br>dissipation, see   | 100 VFBGA<br>Derating factor above<br>T <sub>A</sub> = 70 °C:<br>36.1 mW/°C (1/θ <sub>JA</sub> ) | 2000 |       |      | mW   |

| PD        | Section<br>4.2.1                    | 100 TFBGA<br>Derating factor above<br>$T_A = 70 \text{ °C:}$<br>38.3 mW/°C (1/ $\theta_{JA}$ )   | 2100 |       |      | mW   |

Note 1 VDDIO1/2 must not exceed VDDREF.

**Note 2** For short durations to meet peak current requirements I<sub>OUT</sub> can be operated at up to 10 % higher than the specified maximum operating condition. The part should not be operated in this mode for extended periods and is not guaranteed for continuous operation.

- **Note 3** Obtained from package thermal simulations, JEDEC 2S2P four layer board (76.2 mm x 114 mm x 1.6 mm), 70 μm (2 oz) copper thickness power planes, 35 μm (1 oz) copper thickness signal layer traces, natural convection (still air), see Section 3.13.1.

- **Note 4** Voltage on TP pin should be 0 V except during in-circuit programming.

| Datasheet |

|-----------|

|-----------|

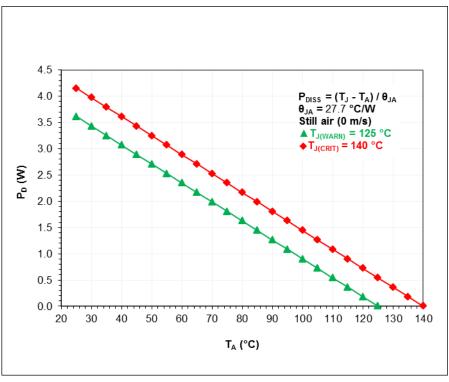

### 4.2.1 Power Derating Curves

#### **Table 6: Typical Temperatures**

|                     | T <sub>A</sub> = 70 °C  | T <sub>A</sub> = 85 °C  | T <sub>A</sub> = 105 °C |

|---------------------|-------------------------|-------------------------|-------------------------|

| Tj_warn             | P <sub>D</sub> = 1.99 W | P <sub>D</sub> = 1.44 W | P <sub>D</sub> = 0.72 W |

| T <sub>J_CRIT</sub> | P <sub>D</sub> = 2.53 W | P <sub>D</sub> = 1.99 W | P <sub>D</sub> = 1.26 W |

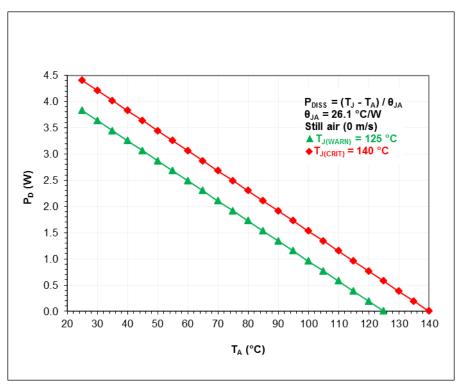

Figure 6:100 TFBGA Power Derating Curve

| Table | 7: | Typical | Temperatures |

|-------|----|---------|--------------|

|-------|----|---------|--------------|

|                     | T <sub>A</sub> = 70 °C  | T <sub>A</sub> = 85 °C  | T <sub>A</sub> = 105 °C  |

|---------------------|-------------------------|-------------------------|--------------------------|

| Tj_warn             | P <sub>D</sub> = 2.11 W | P <sub>D</sub> = 1.53 W | $P_{D} = 0.77 \text{ W}$ |

| T <sub>J_CRIT</sub> | P <sub>D</sub> = 2.68 W | P <sub>D</sub> = 2.11 W | P <sub>D</sub> = 1.34 W  |

| D | a | ta | S | h | e | et |

|---|---|----|---|---|---|----|

|   | a |    | 9 |   | C | Cι |

### 4.3 **Typical Current Consumption**

#### **Table 8: Typical Current Consumption**

| Operating Mode                | Conditions (Note 1)                                                                                                                                                              | Backup<br>Device | Battery        | Unit |  |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------|------|--|

| NO-POWER mode (POR)           | 2.4 V > V <sub>DDREF</sub> > V <sub>BBAT</sub> > 1.5 V                                                                                                                           | 0                | 16             | μA   |  |

| DELIVERY mode Note 2          | VBBAT > VDDREF > 1.5 V                                                                                                                                                           | 0.5              | 0.4<br>Note 3  | μA   |  |

|                               | VDDREF > VBBAT > 1.5 V                                                                                                                                                           | 0                | 1.5            |      |  |

| RTC mode Note 2               | $V_{BBAT} > V_{DDREF} > 2.0 V$                                                                                                                                                   | 1.4              | 1.06<br>Note 3 | μA   |  |

|                               | V <sub>DDREF</sub> > V <sub>BBAT</sub> > 2.0 V                                                                                                                                   | 0.05             | 7              | -    |  |

|                               | V <sub>DDREF</sub> > 2.2 V, supplies off (except LDOCORE), RTC on, pulsed mode:                                                                                                  |                  |                |      |  |

| RESET mode                    | VBBAT > VDDREF                                                                                                                                                                   | 1.6              | 11             | μA   |  |

|                               | Vbbat < Vddref                                                                                                                                                                   | 0.05             | 18             |      |  |

| LOW-POWER mode                | V <sub>SYS</sub> > V <sub>DD_FAULT_LOWER</sub> , supplies off<br>(except LDOCORE), all blocks in<br>POWERDOWN mode, RTC on,<br>pulsed mode with limited parametric<br>compliance |                  | 18             | μA   |  |

| POWERDOWN mode<br>(Hibernate) | V <sub>SYS</sub> > V <sub>DD_FAULT_LOWER</sub> , supplies off<br>(except LDOCORE), all blocks in<br>POWERDOWN mode, RTC on                                                       |                  | 40             | μA   |  |

| POWERDOWN mode (Standby)      | BUCKCORE, LDOCORE, LDO2, 4, 5 enabled, RTC and GPIO unit on                                                                                                                      |                  | 65<br>Note 4   | μA   |  |

| ACTIVE mode                   | All supplies, GPIO, RTC and GPADC on                                                                                                                                             |                  | 320            | μA   |  |

**Note 1** nONKEY/CHG\_WAKE/V<sub>DDREF</sub> detection circuit is enabled in all modes.

**Note 2** See V<sub>BBAT</sub> current in RTC or DELIVERY modes [1]

**Note 3** 0 µA if no main battery available.

**Note 4** Regulators are running in SLEEP mode.

| _    |     | _   |                        |   |

|------|-----|-----|------------------------|---|

| n.   | ata |     |                        | 4 |

| 1 12 |     | en  | 00                     |   |

|      | λια | 311 | $\mathbf{c}\mathbf{c}$ | • |

### 4.4 Digital I/O Characteristics

### Table 9: Digital I/O Electrical Characteristics, T<sub>J</sub> = -40 °C to +125 °C

| Parameter                                           | Description                                                                                                         | Conditions                                                  | Min         | Тур | Max         | Unit |  |

|-----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|-------------|-----|-------------|------|--|

| Mar                                                 | GPI0 to GPI15, nOFF,<br>nSHUTDOWN                                                                                   | VDDCORE mode                                                | 1.0         |     | Vsys        | Ň    |  |

| Vih                                                 | SYS_EN, PWR_EN,<br>PWR1_EN<br>Input High Voltage                                                                    | VDD_IO2 mode                                                | 0.7*VDD_IO2 |     | Vsys        | V    |  |

| Vu                                                  | GPI0 to GPI15, nOFF,<br>nSHUTDOWN<br>SYS_EN, PWR_EN,                                                                | VDDCORE mode                                                | -0.3        |     | 0.4         | V    |  |

| VIL SYS_EN, PWR_EN,<br>PWR1_EN<br>Input Low Voltage | PWR1_EN                                                                                                             | VDD_IO2 mode<br>VDD_IO2 ≥ 1.5V                              | -0.3        |     | 0.3*VDD_IO2 | v    |  |

| VIH                                                 | nONKEY, CHG_WAKE<br>Input High Voltage                                                                              |                                                             | 1.0         |     | Vsys        | V    |  |

| VIL                                                 | nONKEY, CHG_WAKE<br>Input Low Voltage                                                                               |                                                             | -0.3        |     | 0.4         | V    |  |

| VIH (2-WIRE mod                                     | CLK, DATA, SK, SI                                                                                                   | VDDCORE mode                                                | 1.0         |     |             | .,   |  |

|                                                     | (2-WIRE mode)<br>Input High Voltage                                                                                 | VDD_IO2 mode                                                | 0.7*VDD_IO2 |     |             | V    |  |

|                                                     | CLK, DATA, SK, SI                                                                                                   | VDDCORE mode                                                |             |     | 0.4         |      |  |

| VIL                                                 | (2-WIRE mode)<br>Input Low Voltage                                                                                  | VDD_IO2 mode<br>VDD_IO2 ≥ 1.5V                              |             |     | 0.3*VDD_IO2 | V    |  |

| Vih                                                 | SK, nCS, SI<br>(4-WIRE mode)<br>Input High Voltage                                                                  |                                                             | 0.7*VDD_IOx |     |             | V    |  |

| VIL                                                 | SK, nCS, SI<br>(4-WIRE mode)<br>Input Low Voltage                                                                   |                                                             |             |     | 0.3*VDD_IOx | V    |  |

| Mau                                                 | GPO0 to GPO15,<br>nVDD_FAULT, SO,<br>nRESET, nIRQ,<br>E_GPI_2, COMP1V2,                                             | lou⊤ = -1 mA<br>VDD_IO1 ≥ 1.5 V<br>VDD_IO1 mode             | 0.8*VDD_IO1 |     |             | V    |  |

| Vон                                                 | OUT_32K,<br>OUT_32K_2<br>Output High Voltage                                                                        | I <sub>OUT</sub> = -1 mA<br>VDD_IO2 ≥ 1.5 V<br>VDD_IO2 mode | 0.8*VDD_IO2 |     |             |      |  |

| Vон                                                 | GPO1, 3 to 6, 10, and<br>12 to 15, DATA, SI (2-<br>WIRE mode) SO,<br>nRESET, nIRQ,<br>GP_FB2<br>Output High Voltage | Open drain                                                  |             |     | Vddref      | V    |  |

### **System PMIC for Mobile and Automotive Applications**

| Parameter        | Description                                                                                                                                          | Conditions                                     | Min         | Тур | Мах  | Unit |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|-------------|-----|------|------|

| Vol              | GPO0 to GPO15, SO,<br>nVDD_FAULT,<br>nRESET (Note 1),<br>nIRQ (Note 1),<br>GP_FB2, E_GPI_2,<br>COMP1V2, OUT_32K,<br>OUT_32K_2,<br>Output Low Voltage | lout = 1 mA                                    |             |     | 0.3  | v    |

| Vol              | DATA, SI (2-WIRE<br>mode)<br>Output Low Voltage                                                                                                      | I <sub>OUT</sub> = 3 mA                        |             |     | 0.24 | V    |

| Vol              | SI (2-WIRE mode)<br>Output Low Voltage                                                                                                               | Iout = 8 mA                                    |             |     | 0.4  | V    |

| C <sub>IN</sub>  | CLK, DATA, SK, SI<br>Input Capacitance                                                                                                               |                                                |             |     | 10   | pF   |

|                  |                                                                                                                                                      | Fast<br>C <sub>B</sub> < 550 pF                | 20 + 0.1 Cb |     | 120  |      |

| t <sub>fDA</sub> | SI (2-WIRE MODE)<br>Data Fall Time                                                                                                                   | HS<br>10 < С <sub>в</sub> < 100 pF             | 10          |     | 40   | ns   |

|                  |                                                                                                                                                      | НЅ<br>С <sub>в</sub> < 400 рF                  | 20          |     | 80   |      |

|                  | Sink current capability GPO 10, 11, 14, 15                                                                                                           | V <sub>GPIO</sub> = 0.4 V<br>Note 2            |             | 11  |      | mA   |

|                  | Source current<br>capability<br>GPO 10, 11,14,15                                                                                                     | V <sub>GPIO</sub> =<br>0.8*VDD_IO1/2<br>Note 2 |             | -4  |      | mA   |

|                  | Sink current capability GPO 0 to 9, 12, 13                                                                                                           | $V_{GPIO} = 0.3 V$                             |             | 1   |      | mA   |

|                  | Source current<br>capability<br>GPO 0 to 9, 12, 13                                                                                                   | V <sub>GPIO</sub> =<br>0.8*VDD_IO1/2<br>Note 3 |             | -1  |      | mA   |

|                  | GPI pull-down resistor                                                                                                                               |                                                | 50          | 100 | 250  | kΩ   |

|                  |                                                                                                                                                      | VDD_IO1/2 = 1.5 V                              | 60          | 180 | 310  |      |

|                  | GPO pull-up resistor<br>Note 4                                                                                                                       | VDD_IO1/2 = 1.8 V                              | 45          | 120 | 190  | kΩ   |

|                  |                                                                                                                                                      | VDD_IO1/2 = 3.3 V                              | 20          | 40  | 60   |      |

**Note 1** Electrical characteristics are guaranteed down to V<sub>DDREF</sub> = 2.0 V (V<sub>POR\_LOWER</sub>). For lower voltages the port continues operating with reduced performance.

Note 2 At low V<sub>DDREF</sub> values and high temperatures, the sink current capability is reduced.

**Note 3** For VDD\_IO1/2 < 1.5 V the source current capability is reduced.

**Note 4** V(PAD) = 0 V.

### **System PMIC for Mobile and Automotive Applications**

### 4.5 Watchdog

### Table 10: Watchdog, $T_J = -40$ °C to +125 °C

| Parameter           | Description           | Conditions                 | Min | Тур | Max  | Unit |

|---------------------|-----------------------|----------------------------|-----|-----|------|------|

| Twd_min             | Minimum Watchdog time | External 32 kHz oscillator |     |     | 0.11 | S    |

|                     | Minimum Watchdog time | Internal 25 kHz oscillator |     |     | 0.2  | S    |

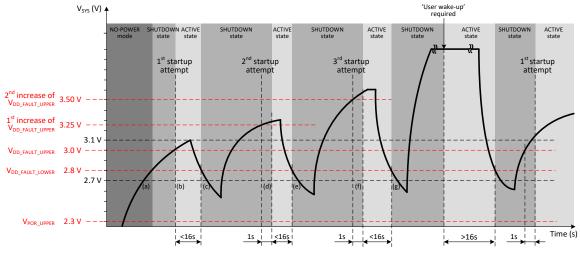

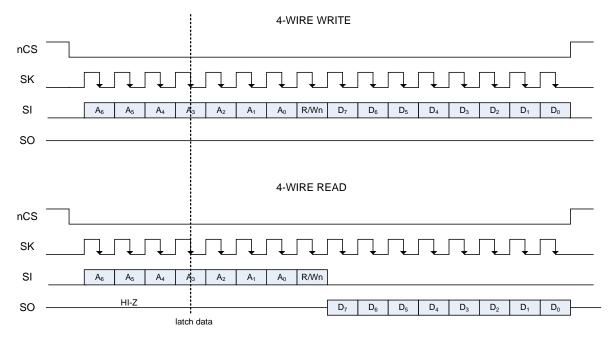

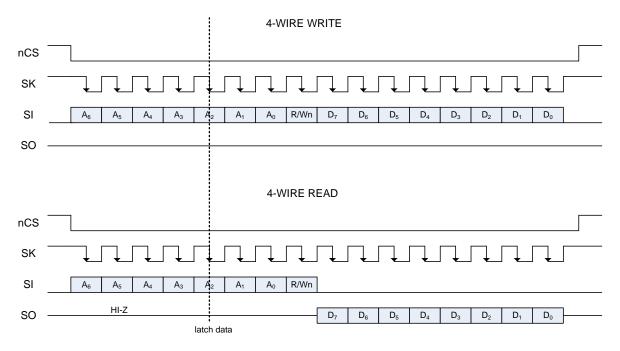

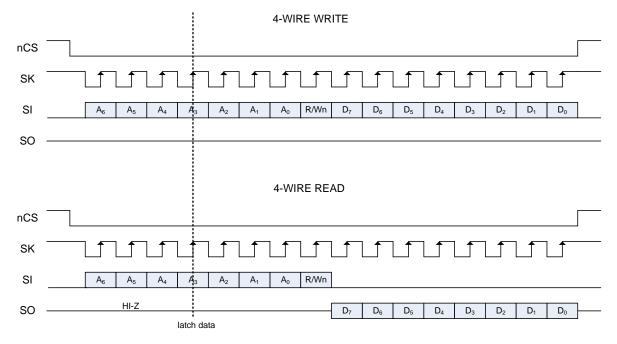

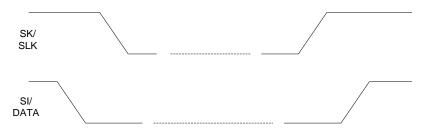

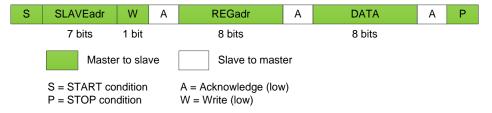

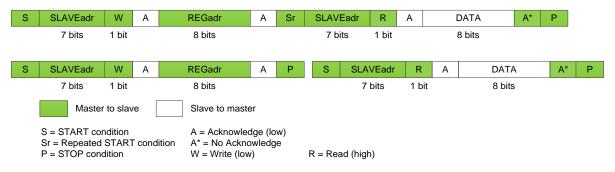

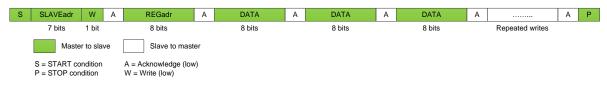

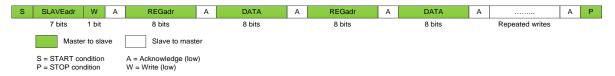

| T <sub>WD_MAX</sub> | Maximum Watchdog time | External 32 kHz oscillator | 2   |     |      | s    |