# M2147H HIGH SPEED 4096 x 1-BIT STATIC RAM

Military

|                           | M2147H-2 | M2147H-3 | M2147H |

|---------------------------|----------|----------|--------|

| Max. Access Time (ns)     | 45       | 55       | 70     |

| Max. Active Current (mA)  | 180      | 180      | 180    |

| Max. Standby Current (mA) | 30       | 30       | 30     |

- Pinout, Function, and Power Compatible to Industry Standard M2147

- HMOS\* II Technology

- Completely Static Memory—No Clock or Timing Strobe Required

- Equal Access and Cycle Times

- Single +5V Supply

- Direct Performance Upgrade for M2147

- Power-Down

- High Density 18-Pin Package

- Separate Data Input and Output

- **■** Three-State Output

- Military Temperature Range: -55°C to +125°C (T<sub>C</sub>)

The Intel M2147H is a 4096-bit static Random Access Memory organized as 4096 words by 1-bit using HMOS II, Intel's next generation high-performance MOS technology. It uses a uniquely innovative design approach which provides the ease-of-use features associated with non-clocked static memories and the reduced standby power dissipation associated with clocked static memories. To the user this means low standby power dissipation without the need for clocks, address setup and hold times, nor reduced data rates due to cycle times that are longer than access times.

CS controls the power-down feature. In less than a cycle time after CS goes high—deselecting the M2147H—the part automatically reduces its power requirements and remains in this low power standby mode as long as CS remains high. This device feature results in system power savings as great as 85% in larger systems, where the majority of devices are deselected.

The M2147H is placed in an 18-pin package configured with the industry standard pinout. It is directly  $\overline{\text{TTL}}$  compatible in all respects: inputs, output, and a single +5V supply. The data is read out nondestructively and has the same polarity as the input data. A data input and a separate three-state output are used.

\*HMOS is a patented process of Intel Corporation.

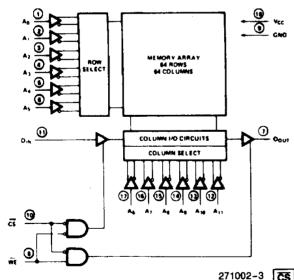

Figure 1. Block Diagram

Diagrams are for pin reference only.

Package sizes are not to scale.

Figure 2.

Pin Configuration

**Truth Table**

| CS WE |   | S WE Mode Out |                  | Power   |  |  |

|-------|---|---------------|------------------|---------|--|--|

| Н     | Х | Not Selected  | High Z           | Standby |  |  |

| L     | L | Write         | High Z           | Active  |  |  |

| L     | Н | Read          | D <sub>OUT</sub> | Active  |  |  |

Figure 3. Logic Symbol

Pin Names

| Address Inputs |

|----------------|

| Write Enable   |

| Chip Select    |

| Data Input     |

| Data Output    |

| Power (+5V)    |

| Ground         |

|                |

### ABSOLUTE MAXIMUM RATINGS\*

Case Temperature Under Bias... - 65°C to +135°C Storage Temperature .....-65°C to +150°C Voltage on Any Pin with Respect to Ground......... -3.5V to +7V Power Dissipation.....1.2W

NOTICE: This is a production data sheet. The specifications are subject to change without notice.

\*WARNING: Stressing the device beyond the "Absolute Maximum Ratings" may cause permanent damage. These are stress ratings only. Operation beyond the "Operating Conditions" is not recommended and extended exposure beyond the "Operating Conditions" may affect device reliability.

### **Operating Conditions**

| Symbol          | Description                   | Min  | Max   | Units |

|-----------------|-------------------------------|------|-------|-------|

| T <sub>C</sub>  | Case Temperature (Instant On) | -55  | + 125 | •C    |

| V <sub>CC</sub> | Digital Supply Voltage        | 4.50 | 5.50  | ٧     |

### D.C. CHARACTERISTICS (Over Specified Operating Conditions)

| Symbol              | Parameter                           | M2147H-2<br>M2147H-3, M2147H |        |       | Unit   | Test Conditions                                                                                                                 |                                                         |  |

|---------------------|-------------------------------------|------------------------------|--------|-------|--------|---------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|--|

| Oymbo.              | rarameter                           | Min                          | Typ(1) | Max   |        | i est Coliditions                                                                                                               |                                                         |  |

| lu                  | Input Load Current (All Input Pins) |                              | 0.01   | 10    | μΑ     | V <sub>CC</sub> = Max., V                                                                                                       | $V_{IN} = GND \text{ to } V_{CC}$                       |  |

| lıol                | Output Leakage Current              | ,                            | 0.1    | 50    | μА     | $\overline{\text{CS}} = \text{V}_{\text{IH}}, \text{V}_{\text{CC}} = \text{Max.},$ $\text{V}_{\text{OUT}} = \text{GND to 4.5V}$ |                                                         |  |

| lcc                 | Operating Current                   |                              | 120    | 170   | mA     | T <sub>C</sub> = 25°C                                                                                                           | V <sub>CC</sub> = Max., <del>CS</del> = V <sub>IL</sub> |  |

|                     |                                     |                              |        | 180   | mA     | T <sub>C</sub> = -55°C                                                                                                          | Outputs Open                                            |  |

| I <sub>SB</sub>     | Standby Current                     |                              | 18     | 30    | mA     | V <sub>CC</sub> = Min. to Max., CS = V <sub>IH</sub>                                                                            |                                                         |  |

| I <sub>PO</sub> (2) | Peak Power-On Current               |                              | 35     | 70    | mA<br> | V <sub>CC</sub> = GND to V <sub>CC</sub> Min.  CS = Lower of V <sub>CC</sub> of V <sub>IH</sub> Min.                            |                                                         |  |

| V <sub>IL</sub>     | Input Low Voltage                   | -3.0                         |        | 8.0   | V      |                                                                                                                                 |                                                         |  |

| V <sub>IH</sub>     | Input High Voltage                  | 2.0                          |        | 6.0   | V      |                                                                                                                                 |                                                         |  |

| VOL                 | Output Low Voltage                  |                              |        | 0.4   | ٧      | I <sub>OL</sub> = 8 mA                                                                                                          |                                                         |  |

| V <sub>OH</sub>     | Output High Voltage                 | 2.4                          |        |       | ٧      | I <sub>OH</sub> = -4.0 mA                                                                                                       |                                                         |  |

| los                 | Output Short Circuit Current        | -275                         |        | + 275 | mA     | V <sub>OUT</sub> = GND to V <sub>CC</sub> , T <sub>C</sub> = 0°C                                                                |                                                         |  |

1. Typical limits at  $V_{CC} = 5V$ ,  $T_{C} = \pm 25^{\circ}C$ , and Load A. 2. A pull-up resistor to  $V_{CC}$  on the  $\overline{CS}$  input is required to keep the device deselected; otherwise, power-on current approaches I<sub>CC</sub> active.

### **CAPACITANCE** $T_C = 25^{\circ}C$ , F = 1.0 MHz

| Symbol           | Parameter             | Max | Unit | Conditions            |  |  |  |  |  |  |

|------------------|-----------------------|-----|------|-----------------------|--|--|--|--|--|--|

| C <sub>IN</sub>  | Input<br>Capacitance  | 5   | pF   | V <sub>IN</sub> = 0V  |  |  |  |  |  |  |

| C <sub>OUT</sub> | Output<br>Capacitance | 6   | рF   | V <sub>OUT</sub> = 0V |  |  |  |  |  |  |

# 271002-4

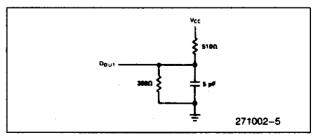

### A.C. TEST CONDITIONS

| Input Pulse Levels             | GND to 3.0V |

|--------------------------------|-------------|

| Input Rise and Fall Times      | 5 ns        |

| Input Timing Reference Levels  | 1.5V        |

| Output Timing Reference Levels | 0.8V-2.0V   |

| Output Load                    | See Load A  |

Load B

Load A www.DataSheet4

### A.C. CHARACTERISTICS (Over Specified Operating Conditions)

# **READ CYCLE**

| Symbol              | Parameter                            | M2147H-2 |     | M2147H-3 |     | M2147H |     | Unit | Co       |

|---------------------|--------------------------------------|----------|-----|----------|-----|--------|-----|------|----------|

|                     |                                      | Min      | Max | Min      | Max | Min    | Max | OTHE | Comments |

| t <sub>RC</sub> (1) | Read Cycle Time                      | 45       |     | 55       |     | 70     |     | ns   |          |

| t <sub>AA</sub>     | Address Access Time                  |          | 45  |          | 55  |        | 70  | ns   |          |

| t <sub>ACS1</sub>   | Chip Select Access Time              |          | 45  |          | 55  |        | 70  | ns   | (Note 7) |

| t <sub>ACS2</sub>   | Chip Select Access Time              |          | 45  |          | 65  |        | 80  | ns   | (Note 8) |

| t <sub>OH</sub>     | Output Hold from Address Change      | 5        |     | 5        |     | 5      |     | ns   |          |

| t <sub>LZ</sub> (2) | Chip Selection to Output in Low Z    | 5        |     | 10       |     | 10     |     | ns   | (Note 3) |

| t <sub>HZ</sub> (2) | Chip Deselection to Output in High Z | 0        | 30  | 0        | 30  | 0      | 40  | ns   | (Note 3) |

| tpU                 | Chip Selection to Power Up Time      | 0        |     | 0        |     | 0      |     | ns   |          |

| t <sub>PD</sub>     | Chip Deselection to Power Down Time  |          | 20  |          | 20  |        | 30  | ns   |          |

### **WAVEFORMS**

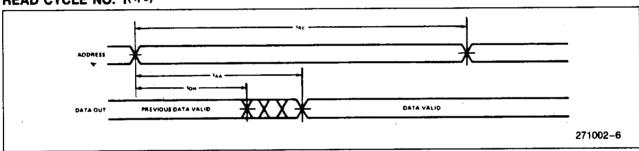

### READ CYCLE NO. 1(4,5)

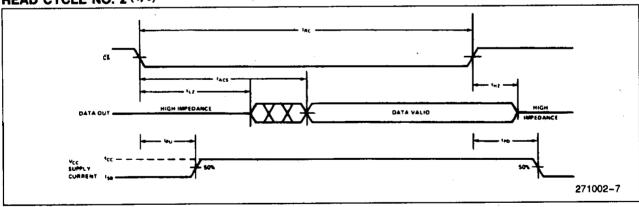

### READ CYCLE NO. 2 (4,6)

- 1. All Read Cycle timings are referenced from the last valid address to the first transitioning address.

- 2. At any given temperature and voltage condition, tHZ max, is less than tLZ min, both for a given device and from device to

- 3. Transition is measured  $\pm 500$  mV from steady state voltage with Load B.

- 4. WE is high for Read Cycles.

- 5. Device is continuously selected, S = V<sub>IL</sub>.

6. Addresses valid prior to or coincident with S transition low.

- 7. Chip deselected for greater than 55 ns prior to selection.

- 8. Chip deselected for a finite time that is less than 55 ns prior to selection. (If the deselect time is 0 ns, the chip is by definition selected and access occurs according to Read Cycle No. 1.)

# A.C. CHARACTERISTICS (Continued)

# WRITE CYCLE

| Symbol              | Parameter                        | M2147H-2 |     | M2147H-3 |     | M2147H |     |      |          |

|---------------------|----------------------------------|----------|-----|----------|-----|--------|-----|------|----------|

|                     | rarameter                        | Min      | Max | Min      | Max | Min    | Max | Unit | Comments |

| t <sub>WC</sub> (2) | Write Cycle Time                 | 45       |     | 55       |     | 70     |     | ns   |          |

| tcw                 | Chip Selection to End of Write   | 45       |     | 45       |     | 55     |     | ns   |          |

| t <sub>AW</sub>     | Address Valid to End of Write    | 45       |     | 45       |     | 55     |     | ns   | -        |

| tas                 | Address Setup Time               | 0        |     | 0        |     | 0      |     | ns   |          |

| t <sub>WP</sub>     | Write Pulse Width                | 25       |     | 25       |     | 40     |     | ns   |          |

| twR                 | Write Recovery Time              | 0        |     | 10       |     | 15     |     | ns   |          |

| t <sub>DW</sub>     | Data Valid to End of Write       | 25       |     | 25       |     | 30     |     | ns   |          |

| t <sub>DH</sub>     | Data Hold Time                   | 10       |     | 10       |     | 10     |     | ns   |          |

| twz                 | Write Enable to Output in High Z | 0        | 25  | 0        | 25  | 0      | 35  | ns   | (Note 3) |

| tow                 | Ouput Active from End of Write   | 0        |     | 0        |     | 0      |     | ns   | (Note 3) |

### **WAVEFORMS**

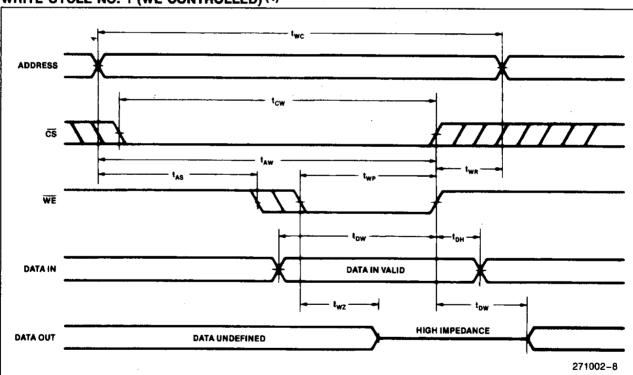

# WRITE CYCLE NO. 1 (WE CONTROLLED) (4)

# **WAVEFORMS** (Continued)

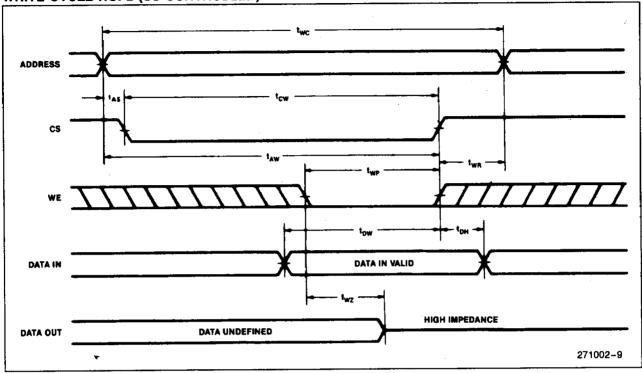

WRITE CYCLE NO. 2 (CS CONTROLLED) (4)

- 1. If CS goes high simultaneously with WE high, the output remains in a high impedance state.

2. All Write Cycle timings are referenced from the last valid address to the first transitioning address.

3. Transition is measured ±500 mV from steady state voltage with Load B.

- 4. CS or WE must be high during address transitions.