# CY8C201A0

# CapSense Express<sup>™</sup> -10 Configurable IOs with Slider

## Features

- 10 configurable IOs supporting

- CapSense slider

- □ LED drive

- Interrupt outputs

- WAKE on interrupt input

- $\square$  User defined input or output

- 2.4V to 5.25V operating voltage

- Industrial temperature range: -40°C to +85°C

- I<sup>2</sup>C slave interface for configuration

Selectable to 50 kHz,100 kHz and 400 kHz.

- Reduce BOM cost

Internal oscillator no external oscillators or crystal

- □ Free development tool no external tuning components

- Low operating current

- □ Active current: continuous sensor scan: 1.5 mA

□ Sleep current: no scan, continuous sleep: 2.6 uA

- Available in 16-pin COL and 16-pin SOIC packages

### Overview

The CapSense Express<sup>TM</sup> controller allows the control of 10 IOs configurable as capacitive sensing buttons or as GPIOs for driving LEDs or interrupt signals based on various button conditions. The GPIOs are also configurable for waking up the device from sleep based on an interrupt input.

The user has the ability to configure buttons, outputs, and parameters, through specific commands sent to the I<sup>2</sup>C port. The IOs have the flexibility in mapping to capacitive buttons and as standard GPIO functions such as interrupt output or input, LED drive and digital mapping of input to output using simple logical operations. This enables easy PCB trace routing and reduces the PCB size and stack up. CapSense Express products are designed for easy integration into complex products.

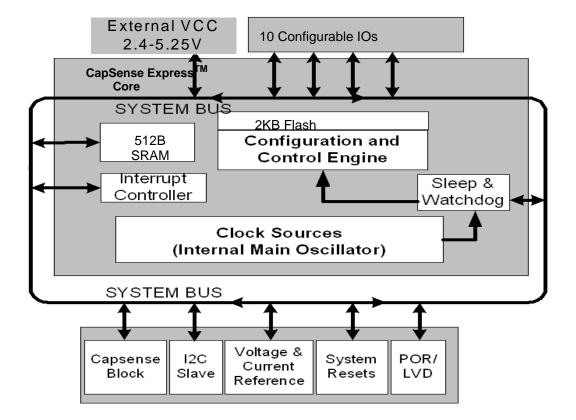

## Architecture

The logic block diagram shows the internal architecture of CY8C201A0.

The user can configure registers with parameters needed to adjust the operation and sensitivity of the CapSense system. CY8C201A0 supports a standard  $I^2C$  serial communication interface that allows the host to configure the device and to read sensor information in real time through easy register access.

## The CapSense Express Core

The CapSense Express Core has a powerful configuration and control block. It encompasses SRAM for data storage, an interrupt controller, sleep and watchdog timers. System resources provide additional capability, such as a configurable  $I^2C$  slave communication interface and various system resets. The Analog System is composed of the CapSense PSoC block which supports capacitive sensing of up to 10 inputs.

San Jose, CA 95134-1709 WWW Data Sheet 4U.com Revised March 11, 2008

# Logic Block Diagram

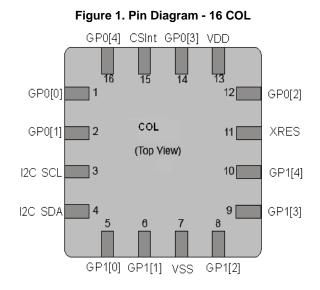

## Pinouts

### Table 1. Pin Definitions - 16 COL

| Pin Number | Name                 | Description                                                                                                                 |

|------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------|

| 1          | GP0[0]               | Configurable as CapSense or GPIO                                                                                            |

| 2          | GP0[1]               | Configurable as CapSense or GPIO                                                                                            |

| 3          | I <sup>2</sup> C SCL | l <sup>2</sup> C clock                                                                                                      |

| 4          | I <sup>2</sup> C SDA | l <sup>2</sup> C data                                                                                                       |

| 5          | GP1[0]               | Configurable as CapSense or GPIO                                                                                            |

| 6          | GP1[1]               | Configurable as CapSense or GPIO                                                                                            |

| 7          | VSS                  | Ground connection                                                                                                           |

| 8          | GP1[2]               | Configurable as CapSense or GPIO                                                                                            |

| 9          | GP1[3]               | Configurable as CapSense or GPIO                                                                                            |

| 10         | GP1[4]               | Configurable as CapSense or GPIO                                                                                            |

| 11         | XRES                 | Active HIGH external reset with internal pull down                                                                          |

| 12         | GP0[2]               | Configurable as CapSense or GPIO                                                                                            |

| 13         | V <sub>DD</sub>      | Supply voltage                                                                                                              |

| 14         | GP0[3]               | Configurable as CapSense or GPIO                                                                                            |

| 15         | CSInt                | Integrating Input. The external capacitor is required only if 5:1 SNR cannot be achieved. Typical range is 10 nf to 100 nf. |

| 16         | GP0[4]               | Configurable as CapSense or GPIO                                                                                            |

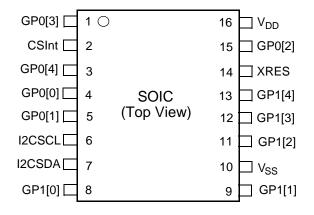

### Figure 2. Pin Diagram - 16 SOIC

#### Table 2. Pin Definitions - 16 SOIC

| Pin Number | Name                 | Description                                                                                                               |

|------------|----------------------|---------------------------------------------------------------------------------------------------------------------------|

| 1          | GP0[3]               | Configurable as CapSense or GPIO                                                                                          |

| 2          | CSInt                | Integrating Input. The external capacitor is required only if 5:1 SNR cannot be achieved. Typical range is 10nf to 100nf. |

| 3          | GP0[4]               | Configurable as CapSense or GPIO                                                                                          |

| 4          | GP0[0]               | Configurable as CapSense or GPIO                                                                                          |

| 5          | GP0[1]               | Configurable as CapSense or GPIO                                                                                          |

| 6          | I <sup>2</sup> C SCL | I <sup>2</sup> C clock                                                                                                    |

| 7          | I <sup>2</sup> C SDA | I <sup>2</sup> C data                                                                                                     |

| 8          | GP1[0]               | Configurable as CapSense or GPIO                                                                                          |

| 9          | GP1[1]               | Configurable as CapSense or GPIO                                                                                          |

| 10         | VSS                  | Ground connection                                                                                                         |

| 11         | GP1[2]               | Configurable as CapSense or GPIO                                                                                          |

| 12         | GP1[3]               | Configurable as CapSense or GPIO                                                                                          |

| 13         | GP1[4]               | Configurable as CapSense or GPIO                                                                                          |

| 14         | XRES                 | Active HIGH external reset with internal pull down.                                                                       |

| 15         | GP0[2]               | Configurable as CapSense or GPIO                                                                                          |

| 16         | V <sub>DD</sub>      | Supply voltage                                                                                                            |

www.DataSheet4U.com

## The CapSense Analog System

The CapSense analog system contains the capacitive sensing hardware which supports the CapSense Successive Approximation (CSA) algorithm. This hardware performs capacitive sensing and scanning without external components. Capacitive sensing is configurable on each pin.

### Additional System Resources

System resources provide additional capability useful to complete systems. Additional resources are low voltage detection and power on reset. Brief statements describing the merits of each system resource are:

- The I<sup>2</sup>C slave provides 50, 100, or 400 kHz communication over two wires.

- Low Voltage Detection (LVD) interrupts can signal the application of falling voltage levels and the advanced POR (Power On Reset) circuit eliminates the need for a system supervisor.

An internal 1.8V reference provides a stable internal reference so that capacitive sensing functionality is not affected by minor  $V_{\text{DD}}$  changes.

## **Electrical Specifications**

## I<sup>2</sup>C Interface

The two modes of operation for the I<sup>2</sup>C interface are:

- Device register configuration and status read or write for controller

- Command execution

The  $I^2C$  address is programmable during configuration. It can be locked to prevent accidental change by setting a flag in a configuration register.

## CapSense Express Software Tool

An easy to use software tool integrated with PSoC Express is available for configuring and tuning CapSense Express devices.Refer to the Application Note AN42137 for details of the software tool.

## CapSense Express Register Map

CapSense Express supports user configurable registers through which the device functionality and parameters are configured. For details, refer to CY8C201xx Register Reference document.

| Parameter        | Description                                                                           | Min            | Тур | Max                   | Unit | Notes                                                                                                                                                                                                                          |

|------------------|---------------------------------------------------------------------------------------|----------------|-----|-----------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T <sub>STG</sub> | Storage temperature                                                                   | -55            | 25  | +100                  | °C   | Higher storage temperatures reduce<br>data retention time. Recommended<br>storage temperature is $+25^{\circ}C \pm 25^{\circ}C$<br>(0°C to 50°C). Extended duration<br>storage temperatures above 65°C<br>degrade reliability. |

| T <sub>A</sub>   | Ambient temperature with power applied                                                | -40            | _   | +85                   | °C   |                                                                                                                                                                                                                                |

| V <sub>DD</sub>  | Supply voltage on $V_{\mbox{\scriptsize DD}}$ relative to $V_{\mbox{\scriptsize SS}}$ | -0.5           | -   | +6.0                  | V    |                                                                                                                                                                                                                                |

| V <sub>IO</sub>  | DC input voltage                                                                      | $V_{SS} - 0.5$ | _   | V <sub>DD</sub> + 0.5 | V    |                                                                                                                                                                                                                                |

| V <sub>IOZ</sub> | DC voltage applied to tri-state                                                       | $V_{SS} - 0.5$ | _   | $V_{DD} + 0.5$        | V    |                                                                                                                                                                                                                                |

| I <sub>MIO</sub> | Maximum current into any GPIO pin                                                     | -25            | _   | +50                   | mA   |                                                                                                                                                                                                                                |

| ESD              | Electro static discharge voltage                                                      | 2000           | _   | -                     | V    | Human body model ESD                                                                                                                                                                                                           |

| LU               | Latch up current                                                                      | -              | -   | 200                   | mA   |                                                                                                                                                                                                                                |

### **Absolute Maximum Ratings**

### **Operating Temperature**

| Parameter      | Description          | Min | Тур | Max  | Unit | Notes |

|----------------|----------------------|-----|-----|------|------|-------|

| T <sub>A</sub> | Ambient temperature  | -40 | -   | +85  | °C   |       |

| TJ             | Junction temperature | -40 | -   | +100 | °C   |       |

## **DC Electrical Characteristics**

### **DC Chip Level Specifications**

| Parameter       | Description                                                       | Min  | Тур | Max  | Unit | Notes                                                   |

|-----------------|-------------------------------------------------------------------|------|-----|------|------|---------------------------------------------------------|

| V <sub>DD</sub> | Supply voltage                                                    | 2.40 | -   | 5.25 | V    |                                                         |

| I <sub>DD</sub> | Supply current                                                    | -    | 1.5 | 2.5  | mA   | Conditions are $V_{DD} = 3.0V$ , $T_A = 25^{\circ}C$    |

| I <sub>SB</sub> | Sleep mode current with POR and LVD active. Mid temperature range | -    | 2.6 | 4    | μA   | $V_{DD} = 2.55V, 0^{\circ}C \le T_{A} \le 40^{\circ}C$  |

| I <sub>SB</sub> | Sleep mode current with POR and LVD active.                       | -    | 2.8 | 5    | μA   | $V_{DD} = 3.3V, -40^{\circ}C \le T_{A} \le 85^{\circ}C$ |

| I <sub>SB</sub> | Sleep mode current with POR and LVD active.                       | -    | 5.2 | 6.4  | μA   | $V_{DD} = 5.25V, -40^{\circ}C \le T_A \le 85^{\circ}C$  |

### 5V and 3.3V DC General Purpose IO Specifications

This table lists guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75V to 5.25Vand  $-40C \le TA \le 85^{\circ}C$ . Typical parameters apply to 5v and 3.3V at 25°C and are for design guidance only.

| Parameter        | Description                                                           | Min                   | Тур | Max  | Unit | Notes                                                                                                                        |

|------------------|-----------------------------------------------------------------------|-----------------------|-----|------|------|------------------------------------------------------------------------------------------------------------------------------|

| R <sub>PU</sub>  | Pull up resistor                                                      | 4                     | 5.6 | 8    | kΩ   |                                                                                                                              |

| V <sub>OH1</sub> | High output voltage<br>Port 0 pins                                    | V <sub>DD</sub> - 0.2 | Ι   | -    | V    | IOH $\leq$ 10 µA, V <sub>DD</sub> $\geq$ 3.0V, maximum of 20 mA source current in all IOs.                                   |

| V <sub>OH2</sub> | High output voltage<br>Port 0 pins                                    | V <sub>DD</sub> – 0.9 | Ι   | -    | V    | IOH = 1 mA, $V_{DD} \ge 3.0V$ , maximum of 20 mA source current in all IOs.                                                  |

| V <sub>OH3</sub> | High output voltage<br>Port 1 pins                                    | V <sub>DD</sub> – 0.2 | _   | _    | V    | IOH < 10 $\mu$ A, V <sub>DD</sub> $\geq$ 3.0V, maximum of 10 mA source current in all IOs.                                   |

| V <sub>OH4</sub> | High output voltage<br>Port 1 pins                                    | V <sub>DD</sub> – 0.9 | _   | -    | V    | IOH = 5 mA, $V_{DD} \ge 3.0V$ , maximum of 20 mA source current in all IOs.                                                  |

| V <sub>OH5</sub> | High output voltage<br>Port 1 pins with 3.0V LDO regulator<br>enabled | 2.75                  | 3.0 | 3.2  | V    | IOH < 10 $\mu$ A, V <sub>DD</sub> $\ge$ 3.1V, maximum of 4 IOs all sourcing 5mA.                                             |

| V <sub>OH6</sub> | High Output Voltage<br>Port 1 pins with 3.0V LDO regulator            | 2.2                   | _   | -    | V    | IOH = 5 mA, $V_{DD} \ge 3.1V$ , maximum of 20 mA source current in all IOs.                                                  |

| V <sub>OH7</sub> | High Output Voltage<br>Port 1 pins with 2.4V LDO regulator            | 2.1                   | 2.4 | 2.5  | V    | IOH < 10 $\mu$ A, V <sub>DD</sub> $\geq$ 3.0V, maximum of 20 mA source current in all IOs.                                   |

| V <sub>OH8</sub> | High Output Voltage<br>Port 1 pins with 2.4V LDO regulator            | 2                     | -   | -    | V    | IOH < 200 $\mu$ A, V <sub>DD</sub> $\geq$ 3.0V, maximum of 20 mA source current in all IOs.                                  |

| V <sub>OL</sub>  | Low output voltage                                                    | -                     | -   | 0.75 | V    | $IOL = 20 \text{ mA}, V_{DD} > 3V$ , maximum of 60 mA sink current on even port pins and 60 mA sink current on odd port pins |

| V <sub>IL</sub>  | Input low voltage                                                     | -                     | -   | .75  | V    | V <sub>DD</sub> 3.0 to 3.6V                                                                                                  |

| Viн              | Input high voltage                                                    | 1.6                   |     |      | V    | V <sub>DD</sub> 3.0 to 3.6V                                                                                                  |

| V <sub>IL</sub>  | Input low voltage                                                     | -                     | -   | 0.8  | V    | V <sub>DD</sub> = 3.6 to 5.25V.                                                                                              |

| V <sub>IH</sub>  | Input high voltage                                                    | 2.0                   | -   | -    | V    | V <sub>DD</sub> = 3.6 to 5.25V.                                                                                              |

| V <sub>H</sub>   | Input hysteresis voltage                                              | -                     | 140 | -    | mV   |                                                                                                                              |

| IIL              | Input leakage                                                         | -                     | 1   | -    | nA   | Gross tested to 1 µA.                                                                                                        |

| C <sub>IN</sub>  | Capacitive load on pins as input                                      | 0.5                   | 1.7 | 5    | pF   | Package and pin dependent.<br>Temp = 25°C.                                                                                   |

| C <sub>OUT</sub> | Capacitive load on pins as output                                     | 0.5                   | 1.7 | 5    | pF   | Package and pin dependent.<br>Temp = 25°C.                                                                                   |

www.DataSheet4U.com

### 2.7 DC General Purpose IO Specifications

This table lists guaranteed maximum and minimum specifications for the voltage and temperature ranges: 2.4V to 3.0V and -40°C<T<sub>A</sub><85°C, respectively. Typical parameters apply to 2.7V at 25°C and are for design guidance only.

| Parameter         | Description                        | Min                   | Тур | Max  | Unit | Notes                                                                                                                            |  |

|-------------------|------------------------------------|-----------------------|-----|------|------|----------------------------------------------------------------------------------------------------------------------------------|--|

| R <sub>PU</sub>   | Pull up resistor                   | 4                     | 5.6 | 8    | kΩ   |                                                                                                                                  |  |

| V <sub>OH1</sub>  | High output voltage<br>Port 0 pins | V <sub>DD</sub> - 0.2 | -   | -    | V    | IOH $\leq$ 10 µA, maximum of 10 mA source current in all IOs.                                                                    |  |

| V <sub>OH2</sub>  | High output voltage<br>Port 0 pins | V <sub>DD</sub> - 0.5 | _   | -    | V    | IOH = 0.2 mA, maximum of 10 mA source current in all IOs.                                                                        |  |

| V <sub>OH3</sub>  | High output voltage<br>Port 1 pins | V <sub>DD</sub> - 0.2 | -   | -    | V    | IOH < 10 μA, maximum of 10 mA<br>source current in all IOs.                                                                      |  |

| V <sub>OH4</sub>  | High output voltage<br>Port 1 pins | V <sub>DD</sub> – 0.5 | _   | -    | V    | IOH = 2 mA, maximum of 10 mA source current in all IOs.                                                                          |  |

| V <sub>OL</sub>   | Low output voltage                 | -                     | -   | 0.75 | V    | IOL = 10 mA, maximum of 30 mA sink<br>current on even port pins and 30 mA<br>sink current on odd port pins                       |  |

| V <sub>OLP1</sub> | Low output voltage port 1 pins     | -                     | -   | 0.4  | V    | IOL=5mA Maximum of 50mA sink<br>current on even port pins and 50mA<br>sink current on odd port pins<br>$2.4 \le V_{DD} \le 3.6V$ |  |

| V <sub>IL</sub>   | Input low voltage                  | -                     | -   | 0.75 | V    | V <sub>DD</sub> = 3.0 to 3.6V                                                                                                    |  |

| V <sub>IH</sub>   | Input high voltage                 | 1.6                   | -   | -    | V    | V <sub>DD</sub> = 3.0 to 3.6V                                                                                                    |  |

| V <sub>IL</sub>   | Input low voltage                  | -                     | -   | 0.75 | V    | V <sub>DD</sub> = 2.4 to 3.6V.                                                                                                   |  |

| V <sub>IH1</sub>  | Input high voltage                 | 1.4                   | -   | -    | V    | V <sub>DD</sub> = 2.4 to 2.7V.                                                                                                   |  |

| V <sub>IH2</sub>  | Input high voltage                 | 1.6                   | -   | -    | V    | V <sub>DD</sub> = 2.7 to 3.6V                                                                                                    |  |

| V <sub>H</sub>    | Input hysteresis voltage           | -                     | 60  | -    | mV   |                                                                                                                                  |  |

| IIL               | Input leakage                      | -                     | 1   | -    | nA   | Gross tested to 1 µA.                                                                                                            |  |

| C <sub>IN</sub>   | Capacitive load on pins as input   | 0.5                   | 1.7 | 5    | pF   | Package and pin dependent.<br>Temp = 25°C.                                                                                       |  |

| C <sub>OUT</sub>  | Capacitive load on pins as output  | 0.5                   | 1.7 | 5    | pF   | Package and pin dependent.<br>Temp = 25°C.                                                                                       |  |

### **DC POR and LVD Specifications**

| Parameter                                | Description                                                                                                    | Min                  | Тур                  | Мах                  | Unit        | Notes                                                                                                                  |

|------------------------------------------|----------------------------------------------------------------------------------------------------------------|----------------------|----------------------|----------------------|-------------|------------------------------------------------------------------------------------------------------------------------|

| V <sub>PPOR0</sub><br>V <sub>PPOR1</sub> | V <sub>DD</sub> Value PPOR Trip<br>V <sub>DD</sub> = 2.7V<br>V <sub>DD</sub> = 3.3V,5V                         | -                    | 2.36<br>2.60         | 2.40<br>2.65         |             | V <sub>DD</sub> must be greater than or equal to 2.5V during startup, reset from the XRES pin, or reset from Watchdog. |

| VLVD0<br>VLVD2<br>VLVD6                  | V <sub>DD</sub> Value for LVD trip<br>V <sub>DD</sub> = 2.7V<br>V <sub>DD</sub> = 3.3V<br>V <sub>DD</sub> = 5V | 2.39<br>2.75<br>3.98 | 2.45<br>2.92<br>4.05 | 2.51<br>2.99<br>4.12 | V<br>V<br>V |                                                                                                                        |

## **AC Electrical Characteristics**

### 5.0V and 3.3V AC General Purpose IO Specifications

| Parameter | Description                                        | Min | Max | Unit | Notes                                                           |

|-----------|----------------------------------------------------|-----|-----|------|-----------------------------------------------------------------|

| TRise0    | Rise time, strong mode,<br>Cload = 50pF, Port 0    | 15  | 80  | ns   | $V_{DD}$ = 3.0V to 3.6V and 4.75V to 5.25V, 10% - 90%           |

| TRise1    | Rise time, strong mode,<br>Cload = 50pF, Port 1    | 10  | 50  | ns   | V <sub>DD</sub> = 3.0V to 3.6V, 10% - 90%                       |

| TFall     | Fall time, strong mode,<br>Cload = 50pF, all ports | 10  | 50  | ns   | V <sub>DD</sub> = 3.0V to 3.6V and 4.75V to 5.25V,<br>10% - 90% |

#### 2.7V AC General Purpose IO Specifications

| Parameter | Description                                        | Min | Max | Unit | Notes                                     |

|-----------|----------------------------------------------------|-----|-----|------|-------------------------------------------|

| TRise0    | Rise time, strong mode,<br>Cload = 50pF, Port 0    | 15  | 100 | ns   | V <sub>DD</sub> = 2.4V to 3.0V, 10% - 90% |

| TRise1    | Rise time, strong mode,<br>Cload = 50pF, Port 1    | 10  | 70  | ns   | V <sub>DD</sub> = 2.4V to 3.0V, 10% - 90% |

| TFall     | Fall time, strong mode,<br>Cload = 50pF, all ports | 10  | 70  | ns   | V <sub>DD</sub> = 2.4V to 3.0V, 10% - 90% |

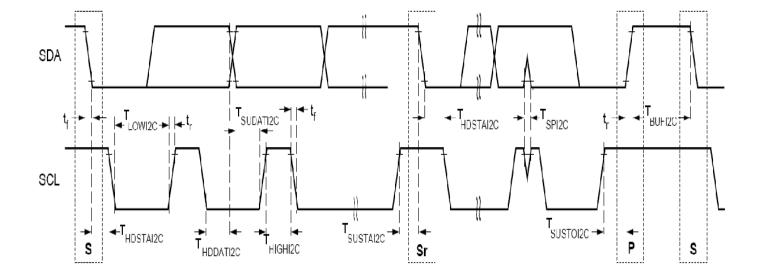

## AC I<sup>2</sup>C Specifications

| Parameter                           | Description                                                                                  |     | dard<br>de | Fast | Mode | Units | Notes                                                 |

|-------------------------------------|----------------------------------------------------------------------------------------------|-----|------------|------|------|-------|-------------------------------------------------------|

|                                     |                                                                                              | Min | Max        | Min  | Max  |       |                                                       |

| F <sub>SCL</sub> I <sup>2</sup> C   | SCL clock frequency                                                                          | 0   | 100        | 0    | 400  | kbps  | Fast mode not supported for<br>V <sub>DD</sub> < 3.0V |

| T <sub>HDSTA</sub> I <sup>2</sup> C | Hold time (repeated) START condition. After this period, the first clock pulse is generated. | 4.0 | -          | 0.6  | -    | μs    |                                                       |

| T <sub>LOW</sub> I <sup>2</sup> C   | LOW period of the SCL clock                                                                  | 4.7 | -          | 1.3  | -    | μs    |                                                       |

| T <sub>HIGH</sub> I <sup>2</sup> C  | HIGH period of the SCL clock                                                                 | 4.0 | —          | 0.6  | -    | μs    |                                                       |

| T <sub>SUSTA</sub> I <sup>2</sup> C | Setup time for a repeated START condition                                                    | 4.7 | -          | 0.6  | -    | μs    |                                                       |

| T <sub>HDDAT</sub> I <sup>2</sup> C | Data hold time                                                                               | 0   | -          | 0    | _    | μs    |                                                       |

| T <sub>SUDAT</sub> I <sup>2</sup> C | Data setup time                                                                              | 250 | -          | 100  | _    | ns    |                                                       |

| T <sub>SUSTO</sub> I <sup>2</sup> C | Setup time for STOP condition                                                                | 4.0 | -          | 0.6  | _    | μs    |                                                       |

| T <sub>BUF</sub> I <sup>2</sup> C   | BUS free time between a STOP and START condition                                             | 4.7 | -          | 1.3  | -    | μs    |                                                       |

| T <sub>SP</sub> I <sup>2</sup> C    | Pulse width of spikes suppressed by the input filter                                         | _   | -          | 0    | 50   | ns    |                                                       |

### Figure 3. Definition for Timing for Fast/Standard Mode on the I2C Bus

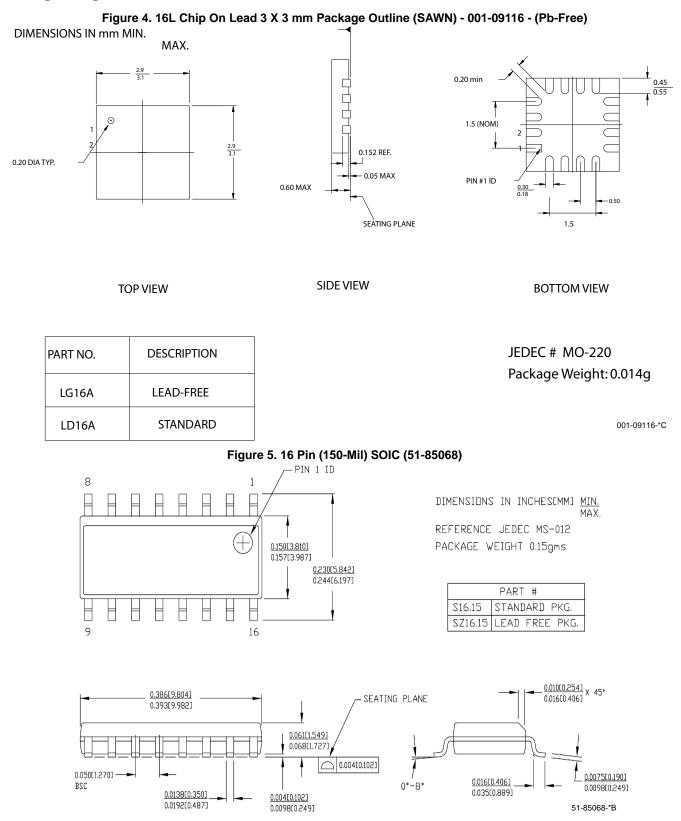

## **Ordering Information**

| Ordering Code   | Package Diagram | Package Type          | Operating<br>Temperature |

|-----------------|-----------------|-----------------------|--------------------------|

| CY8C201A0-LDX2I | 001-09116       | 16 COL <sup>[3]</sup> | Industrial               |

| CY8C201A0-SX2I  | 51-85068        | 16 SOIC               | Industrial               |

## **Thermal Impedances by Package**

| Package               | Typical θ <sub>JA</sub> <sup>[1]</sup> |

|-----------------------|----------------------------------------|

| 16 COL <sup>[3]</sup> | 46 °C                                  |

| 16 SOIC               | 79.96 °C                               |

## **Solder Reflow Peak Temperature**

| Package               | Minimum Peak Temperature <sup>[2]</sup> | Maximum Peak Temperature |

|-----------------------|-----------------------------------------|--------------------------|

| 16 COL <sup>[3]</sup> | 240 °C                                  | 260 °C                   |

| 16 SOIC               | 240 °C                                  | 260 °C                   |

Notes

T<sub>J</sub> = T<sub>A</sub> + Power x θ<sub>JA</sub>.

Higher temperatures may be required based on the solder melting point. Typical temperatures for solder are 220 ± 5°C with Sn-Pb or 245 ± 5°C with Sn-Ag-Cu paste. Refer to the solder manufacturer specifications.

Earlier termed as QFN package.

Page 10 of 12 www.DataSheet4U.com

## Package Diagram

www.DataSheet4U.com

### **Document History Page**

| Document Title: CY8C201A0 CapSense Express™ -10 Configurable IOs with Slider<br>Document Number: 001-17349 |         |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|------------------------------------------------------------------------------------------------------------|---------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| REV.                                                                                                       | ECN.    | Orig. of<br>Change | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| **                                                                                                         | 1494145 | TUP/AESA           | New Datasheet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| *A                                                                                                         | 1773608 | TUP/AESA           | Removed table - 3V DC General Purpose IO Specifications<br>Updated Logic Block Diagram<br>Updated table - DC POR and LVD Specifications<br>Updated table - DC Chip Level Specifications<br>Updated table - 5V and 3.3V DC General Purpose IO Specifications<br>Updated table - 2.7V DC General Purpose IO Specifications<br>Updated table - AC GPIO Specifications and split it into two tables for 5V/3.3V and 2.7V<br>Added section on CapSense Express <sup>TM</sup> Software tool<br>Updated 16-QFN Package Diagram |  |

| *В                                                                                                         | 2091026 | DZU/MOHD<br>/AESA  | Updated table-DC Chip Level Specifications<br>Updated table-Pin Definitions 16 pin COL<br>Updated table-Pin Definitions 16 pin SOIC<br>Updated table-5V and 3.3V DC General Purpose IO Specifications<br>Updated table - 2.7V DC General Purpose IO Specifications<br>Changed definition for Timing for Fast/Standard Mode on the I2C Bus diagram                                                                                                                                                                       |  |

© Cypress Semiconductor Corporation, 2007-2008. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress product. Nor does it convey or imply any license under patent or other rights. Cypress products are not warranted nor intended to be used for medical, life support, life saving, critical control or safety applications, unless pursuant to an express written agreement with Cypress. Furthermore, Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Any Source Code (software and/or firmware) is owned by Cypress Semiconductor Corporation (Cypress) and is protected by and subject to worldwide patent protection (United States and foreign), United States copyright laws and international treaty provisions. Cypress hereby grants to licensee a personal, non-exclusive, non-transferable license to copy, use, modify, create derivative works of, and compile the Cypress Source Code and derivative works for the sole purpose of creating custom software and or firmware in support of licensee product to be used only in conjunction with a Cypress integrated circuit as specified in the applicable agreement. Any reproduction, modification, translation, compilation, or representation of this Source Code except as specified above is prohibited without the express written permission of Cypress.

Disclaimer: CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Cypress reserves the right to make changes without further notice to the materials described herein. Cypress does not assume any liability arising out of the application or use of any product or circuit described herein. Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress' product in a life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Use may be limited by and subject to the applicable Cypress software license agreement.

#### Document Number: 001-17349 Rev. \*B

#### Revised March 11, 2008

Page 12 of 12

PSoC Designer™, Programmable System-on-Chip™, and PSoC Express™ are trademarks and PSoC® is a registered trademark of Cypress Semiconductor Corp. All other trademarks or registered trademarks referenced herein are property of the respective corporations. Purchase of I<sup>°</sup>C components from Cypress or one of its sublicensed Associated Companies conveys a license under the Philips I<sup>°</sup>C Patent Rights to use these components in an I<sup>°</sup>C system, provided that the system conforms to the I<sup>°</sup>C Standard Specification as defined by Philips. All www.DataSheet400.com mentioned in this document may be the trademarks of their respective holders.