# 13 Output, 3.3V SDRAM Buffer for Desktop PCs with 3 DIMMs

#### **Features**

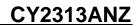

- One input to 13 output buffer/driver

- Supports up to three SDRAM DIMMs

- · One additional outputs for feedback

- · Serial interface for output control

- · Low skew outputs

- Up to 100-MHz operation

- Multiple V<sub>DD</sub> and V<sub>SS</sub> pins for noise reduction

- Low EMI outputs

- 28-pin SOIC (300-mil) package

- 3.3V operation

### **Functional Description**

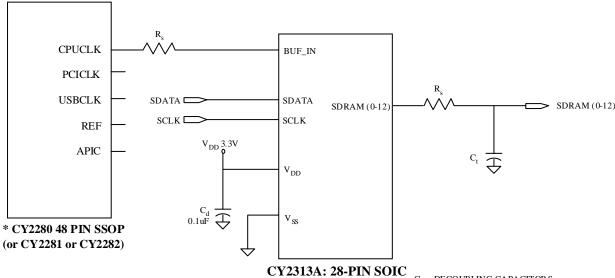

The CY2313ANZ is a 3.3V buffer designed to distribute high-speed clocks in desktop PC applications. The part has 13 outputs, 12 of which can be used to drive up to three SDRAM DIMMs, and the remaining can be used for external feedback to a PLL. The device operates at 3.3V and outputs can run up to 100 MHz, thus making it compatible with Pentium® II processors. The CY2313ANZ can be used in conjunction with the CY2280, CY2281, CY2282 or similar clock synthesizer for a complete Pentium II motherboard solution.

The CY2313ANZ also includes a serial interface which can enable or disable each output clock. On power-up, all output clocks are enabled.

Pentium is a registered trademark of Intel Corporation.

www.DataSheet4U.com

www.DataSheet4U.com

### **Pin Summary**

| Name                  | Pins                                           | Description                                             |  |

|-----------------------|------------------------------------------------|---------------------------------------------------------|--|

| V <sub>DD</sub>       | 1, 5, 20, 24, 28                               | 3.3V Digital voltage supply                             |  |

| $V_{SS}$              | 4, 8, 17, 21, 25                               | Ground                                                  |  |

| V <sub>DDIIC</sub>    | 13                                             | Serial interface voltage supply                         |  |

| V <sub>SSIIC</sub> 16 |                                                | Ground for serial interface                             |  |

| BUF_IN                | 9                                              | Input clock                                             |  |

| SDATA 14              |                                                | Serial data input, internal pull-up to V <sub>DD</sub>  |  |

| SCLK 15               |                                                | Serial clock input, internal pull-up to V <sub>DD</sub> |  |

| SDRAM [0-12]          | 2, 3, 6, 7, 10, 11, 12, 18, 19, 22, 23, 26, 27 | SDRAM clock outputs                                     |  |

## **Serial Configuration Map**

The Serial bits will be read by the clock driver in the following order:

Byte 0 - Bits 7, 6, 5, 4, 3, 2, 1, 0 Byte 1 - Bits 7, 6, 5, 4, 3, 2, 1, 0

Byte N - Bits 7, 6, 5, 4, 3, 2, 1, 0

- Reserved and unused bits should be programmed to "0"

- Serial interface address for the CY2313ANZ is:

| A6 | A5 | A4 | А3 | A2 | A1 | A0 | R/W |

|----|----|----|----|----|----|----|-----|

| 1  | 1  | 0  | 1  | 0  | 0  | 1  |     |

# Byte 0:SDRAM Active/Inactive Register (1 = Enable, 0 = Disable), Default = Enabled

| Bit   | Pin# | Description              |  |  |

|-------|------|--------------------------|--|--|

| Bit 7 | 11   | SDRAM5 (Active/Inactive) |  |  |

| Bit 6 | 10   | SDRAM4 (Active/Inactive) |  |  |

| Bit 5 |      | Reserved, drive to 0     |  |  |

| Bit 4 |      | Reserved, drive to 0     |  |  |

| Bit 3 | 7    | SDRAM3 (Active/Inactive) |  |  |

| Bit 2 | 6    | SDRAM2 (Active/Inactive) |  |  |

| Bit 1 | 3    | SDRAM1 (Active/Inactive) |  |  |

| Bit 0 | 2    | SDRAM0 (Active/Inactive) |  |  |

# Byte 1: SDRAM Active/Inactive Register (1 = Active, 0 = Inactive), Default = Active

| Bit   | Pin# | Description               |  |

|-------|------|---------------------------|--|

| Bit 7 | 27   | SDRAM11 (Active/Inactive) |  |

| Bit 6 | 26   | SDRAM10 (Active/Inactive) |  |

| Bit 5 | 23   | SDRAM9 (Active/Inactive)  |  |

| Bit 4 | 22   | SDRAM8 (Active/Inactive)  |  |

| Bit 3 |      | Reserved, drive to 0      |  |

| Bit 2 |      | Reserved, drive to 0      |  |

| Bit 1 | 19   | SDRAM7 (Active/Inactive)  |  |

| Bit 0 | 18   | SDRAM6 (Active/Inactive)  |  |

# Byte 2: SDRAM Active/Inactive Register (1 = Active, 0 = Inactive), Default = Active

| Bit   | Pin # Description |                           |

|-------|-------------------|---------------------------|

| Bit 7 |                   | Reserved, drive to 0      |

| Bit 6 | 12                | SDRAM12 (Active/Inactive) |

| Bit 5 |                   | Reserved, drive to 0      |

| Bit 4 |                   | Reserved, drive to 0      |

| Bit 3 |                   | Reserved, drive to 0      |

| Bit 2 |                   | Reserved, drive to 0      |

| Bit 1 |                   | Reserved, drive to 0      |

| Bit 0 |                   | Reserved, drive to 0      |

www.DataSheet4U.com

Document #: 38-07144 Rev. \*A Page 2 of 8

# **Maximum Ratings**

| Supply Voltage to Ground Potential | –0.5V to +7.0V                 |

|------------------------------------|--------------------------------|

| DC Input Voltage (Except BUF_IN)   | 0.5V to V <sub>DD</sub> + 0.5V |

| DC Input Voltage (BUF_IN)          | –0.5V to +7.0V                 |

| Storage Temperature            | 65°C to +150°C |

|--------------------------------|----------------|

| Junction Temperature           | 150°C          |

| Static Discharge Voltage       |                |

| (per MIL-STD-883, Method 3015) | >2000V         |

# Operating Conditions<sup>[1]</sup>

| Parameter       | Description                                                                                    | Min.  | Max.  | Unit |

|-----------------|------------------------------------------------------------------------------------------------|-------|-------|------|

| $V_{DD}$        | Supply Voltage                                                                                 | 3.135 | 3.465 | V    |

| T <sub>A</sub>  | Operating Temperature (Ambient Temperature)                                                    | 0     | 70    | °C   |

| C <sub>L</sub>  | Load Capacitance                                                                               |       | 30    | pF   |

| C <sub>IN</sub> | Input Capacitance                                                                              |       | 7     | pF   |

| t <sub>PU</sub> | Power-up time for all VDD's to reach minimum specified voltage (power ramps must be monotonic) | 0.05  | 50    | ms   |

## **Electrical Characteristics** Over the Operating Range

| Parameter          | Description                              | Test Conditions                                                                  | Min. | Max. | Unit |

|--------------------|------------------------------------------|----------------------------------------------------------------------------------|------|------|------|

| V <sub>IL</sub>    | Input LOW Voltage <sup>[2]</sup>         | Except serial interface pins                                                     |      | 0.8  | V    |

| V <sub>ILiic</sub> | Input LOW Voltage                        | For serial interface pins only                                                   |      | 0.7  | V    |

| V <sub>IH</sub>    | Input HIGH Voltage <sup>[2]</sup>        |                                                                                  | 2.0  |      | V    |

| I <sub>IL</sub>    | Input LOW Current (BUF_IN input)         | V <sub>IN</sub> = 0V                                                             | -10  | 10   | μΑ   |

| I <sub>IL</sub>    | Input LOW Current<br>(Except BUF_IN Pin) | V <sub>IN</sub> = 0V                                                             |      | 100  | μΑ   |

| I <sub>IH</sub>    | Input HIGH Current                       | $V_{IN} = V_{DD}$                                                                | -10  | 10   | μΑ   |

| V <sub>OL</sub>    | Output LOW Voltage <sup>[3]</sup>        | I <sub>OL</sub> = 25 mA                                                          |      | 0.4  | V    |

| V <sub>OH</sub>    | Output HIGH Voltage <sup>[3]</sup>       | I <sub>OH</sub> = -36 mA                                                         | 2.4  |      | V    |

| I <sub>DD</sub>    | Supply Current <sup>[3]</sup>            | Unloaded outputs, 100 MHz                                                        |      | 200  | mA   |

| I <sub>DD</sub>    | Supply Current <sup>[3]</sup>            | Loaded outputs, 100 MHz                                                          |      | 290  | mA   |

| I <sub>DD</sub>    | Supply Current <sup>[3]</sup>            | Unloaded outputs, 66.67 MHz                                                      |      | 150  | mA   |

| I <sub>DD</sub>    | Supply Current <sup>[3]</sup>            | Loaded outputs, 66.67 MHz                                                        |      | 185  | mA   |

| I <sub>DDS</sub>   | Supply Current                           | BUF_IN=V <sub>DD</sub> or V <sub>SS</sub><br>All other inputs at V <sub>DD</sub> |      | 500  | μΑ   |

#### Notes:

www.DataSheet4U.com

Document #: 38-07144 Rev. \*A Page 3 of 8

Electrical parameters are guaranteed under the operating conditions specified.

BUF\_IN input has a threshold voltage of V<sub>DD</sub>/2.

Parameter is guaranteed by design and characterization. Not 100% tested in production.

# Switching Characteristics<sup>[4]</sup> Over the Operating Range

| Parameter      | Name                                         | Test Conditions                | Min. | Тур. | Max. | Unit |

|----------------|----------------------------------------------|--------------------------------|------|------|------|------|

|                | Maximum Operating Frequency                  |                                |      |      | 100  | MHz  |

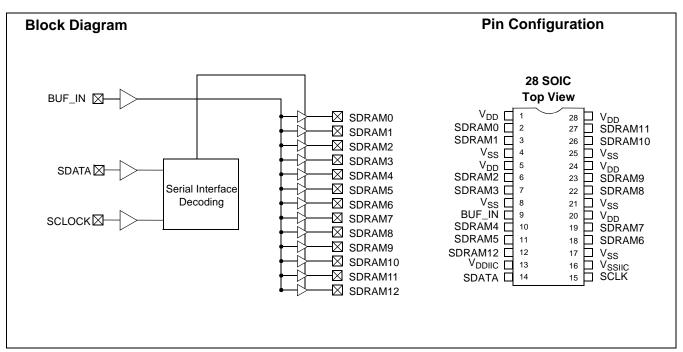

|                | Duty Cycle <sup>[3,5]</sup> = $t_2 \div t_1$ | Measured at 1.5V               | 45.0 | 50.0 | 55.0 | %    |

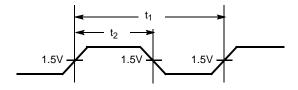

| t <sub>3</sub> | Rising Edge Rate <sup>[3]</sup>              | Measured between 0.4V and 2.4V | 0.9  | 1.5  | 4.0  | V/ns |

| t <sub>4</sub> | Falling Edge Rate <sup>[3]</sup>             | Measured between 2.4V and 0.4V | 0.9  | 1.5  | 4.0  | V/ns |

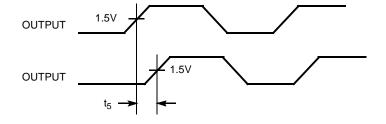

| t <sub>5</sub> | Output to Output Skew <sup>[3]</sup>         | All outputs equally loaded     | -250 |      | +250 | ps   |

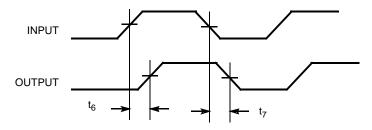

| t <sub>6</sub> | SDRAM Buffer LH Prop. Delay <sup>[3]</sup>   | Input edge greater than 1 V/ns | 1.0  | 3.5  | 5.0  | ns   |

| t <sub>7</sub> | SDRAM Buffer HL Prop. Delay <sup>[3]</sup>   | Input edge greater than 1 V/ns | 1.0  | 3.5  | 5.0  | ns   |

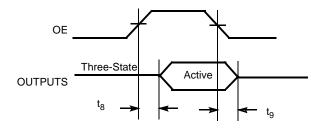

| t <sub>8</sub> | SDRAM Buffer Enable Delay <sup>[3]</sup>     | Input edge greater than 1 V/ns | 1.0  | 5    | 12   | ns   |

| t <sub>9</sub> | SDRAM Buffer Disable Delay <sup>[3]</sup>    | Input edge greater than 1 V/ns | 1.0  | 20   | 30   | ns   |

#### Notes:

- 4. All parameters specified with loaded outputs.

5. Duty cycle of input clock is 50%. Rising and falling edge rate of the input clock is greater than 1 V/ns.

### **Switching Waveforms**

### **Duty Cycle Timing**

#### All Outputs Rise/Fall Time

### **Output-Output Skew**

www.DataSheet4U.com

Document #: 38-07144 Rev. \*A Page 4 of 8

## Switching Waveforms (continued)

## SDRAM Buffer LH and HL Propagation Delay

#### **SDRAM Buffer Enable and Disable Times**

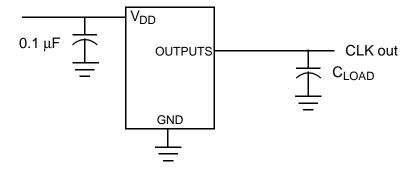

## **Test Circuit**

www.DataSheet4U.com

www.DataSheet4U.com

CY2313ANZ

### **Application Information**

Clock traces must be terminated with either series or parallel termination, as is normally done.

### **Application Circuit**

\* THIS FREQUENCY SYNTHESIZER IS USED TO GENER ATE CPU, PCI, USB, REF, AND APIC CLOCKS.

$\begin{aligned} & \mathbf{C_d} = \mathbf{DECOUPLING} \ \mathbf{CAPACITOR} \, \mathbf{S} \\ & \mathbf{C_t} = \mathbf{OPTIONAL} \ \mathbf{EMI-REDUCING} \ \mathbf{CAPACITOR} \\ & \mathbf{R_s} = \mathbf{SERIES} \ \mathbf{TERMINATING} \ \mathbf{RESISTORS} \end{aligned}$

### Summary

- Surface mount, low-ESR, ceramic capacitors should be used for filtering. Typically, these capacitors have a value of 0.1 μF.

In some cases, smaller value capacitors may be required.

- The value of the series terminating resistor satisfies the following equation, where Rtrace is the loaded characteristic impedance

of the trace, Rout is the output impedance of the buffer (typically 25Ω), and Rseries is the series terminating resistor.

Rseries > Rtrace Rout

- Footprints must be laid out for optional EMI-reducing capacitors, which should be placed as close to the terminating resistor as is physically possible. Typical values of these capacitors range from 4.7 pF to 22 pF.

- A Ferrite Bead  $\mathbf{may}$  be used to isolate the Board  $V_{DD}$  from the clock generator  $V_{DD}$  island. Ensure that the Ferrite Bead offers greater than  $50\Omega$  impedance at the clock frequency, under loaded DC conditions. Please refer to the application note "Layout and Termination Techniques for Cypress Clock Generators" for more details.

- If a Ferrite Bead is used, a 10 μF–22 μF tantalum bypass capacitor should be placed close to the Ferrite Bead. This capacitor prevents power supply droop during current surges.

#### Ordering Information

| Ordering Code | Package<br>Name | Package Type | Operating<br>Range |

|---------------|-----------------|--------------|--------------------|

| CY2313ANZSC-1 | S21             | 28-Pin SOIC  | Commercial         |

www.DataSheet4U.com

Document #: 38-07144 Rev. \*A Page 6 of 8

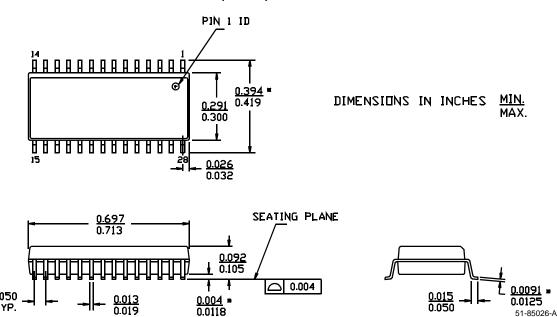

51-85026-A

## **Package Diagram**

#### 28-Lead (300-Mil) Molded SOIC S21

| Document Title: CY2313ANZ 13 Output, 3.3V SDRAM Buffer for Desktop PCs with 3 DIMMs Document Number: 38-07144 |        |          |     |                                                                 |  |  |  |

|---------------------------------------------------------------------------------------------------------------|--------|----------|-----|-----------------------------------------------------------------|--|--|--|

| REV. ECN NO. Date Change Description of Change                                                                |        |          |     |                                                                 |  |  |  |

| **                                                                                                            | 110253 | 11/18/01 | DSG | Change from Spec number: 38-00692 to 38-07144                   |  |  |  |

| *A                                                                                                            | 121831 | 12/14/02 | RBI | Power up requirements added to Operating Conditions Information |  |  |  |