SONY

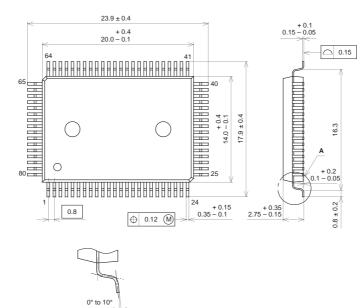

# CXD1186CQ/CR

# **CD-ROM Decoder**

#### Description

The CXD1186C is a CD-ROM decoder LSI.

#### Features

- Corresponds to CD-ROM, CD-I and CD-ROM XA formats.

- Real time error correction. (Erasure correction using C2 pointer from CD player.)

- Double speed playback.

- Connection to standard SRAM up to 64 K bytes, as buffer memory, possible.

#### Applications

**CD-ROM** driver

#### Structure

Silicon gate CMOS IC

### Absolute Maximum Ratings (Ta=25 °C)

| <ul> <li>Supply voltage</li> </ul>      | VDD -0.5 to +7.0    | V  |

|-----------------------------------------|---------------------|----|

| <ul> <li>Input voltage</li> </ul>       | VI -0.5 to VDD +0.5 | V  |

| <ul> <li>Output voltage</li> </ul>      | Vo -0.5 to VDD +0.5 | V  |

| Operating temperature                   | Topr -20 to +75     | °C |

| <ul> <li>Storage temperature</li> </ul> | Tstg -55 to +150    | °C |

#### **Recommended Operating Conditions**

| <ul> <li>Supply voltage</li> </ul> | Vdd | +4.5 to +5.5    | V |

|------------------------------------|-----|-----------------|---|

|                                    |     | (standard +5.0) |   |

• Operating temperature Topr -20 to +75 °C

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

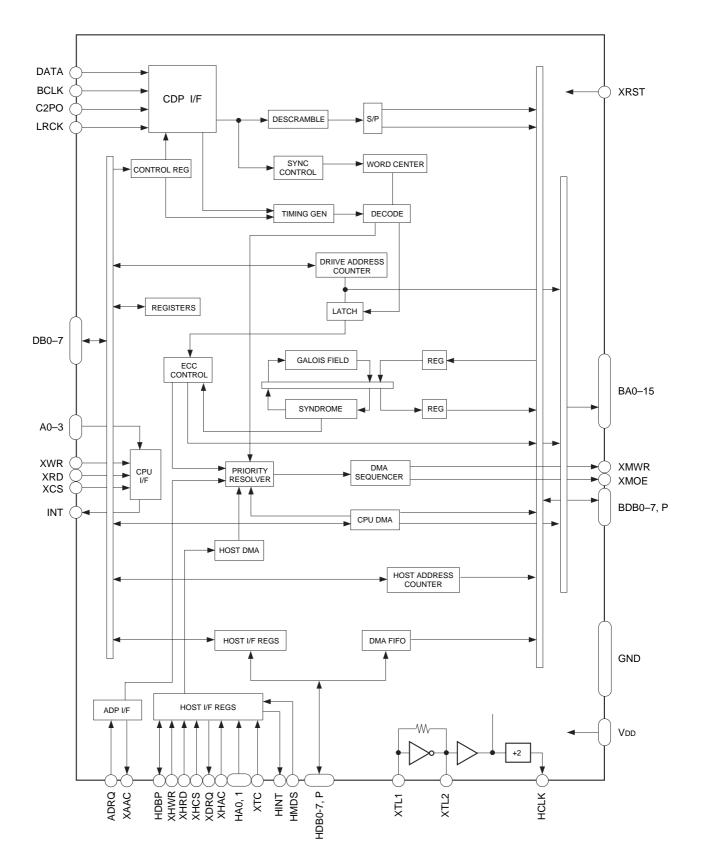

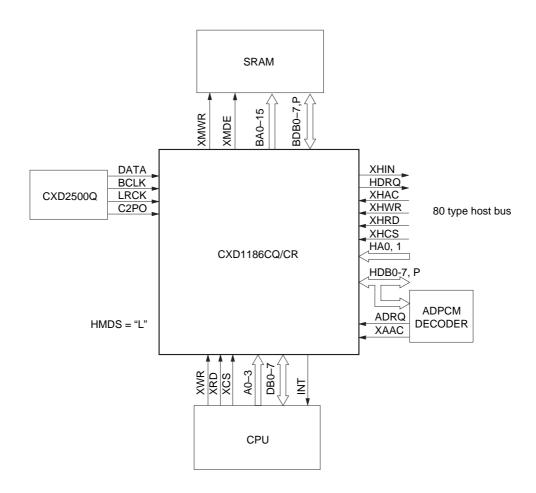

#### **Block Diagram**

—2—

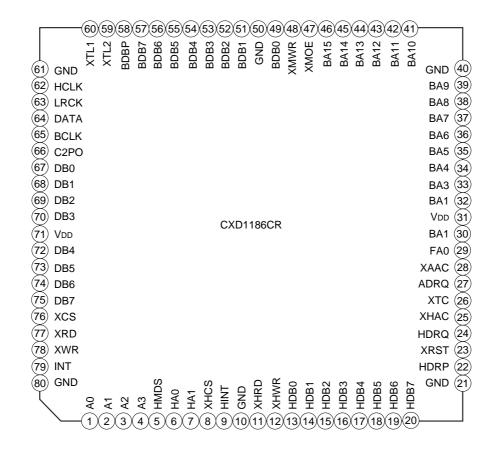

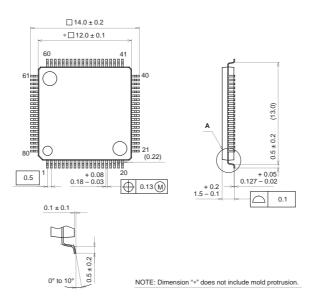

#### **Pin Configuration**

| 64/63/62/61/60/59/58/57/56/55/54/53/52/51/50/49/48/47/46/45/44/43/42/41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HCLK<br>GND<br>GND<br>GND<br>GND<br>GND<br>BDB3<br>BDB3<br>BDB3<br>BDB3<br>BDB3<br>BDB3<br>BDB3<br>BD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| (65) LRCK BA8 (40)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 66 DATA BA7 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 67 BCLK BA6 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 68 C2PO         BA5 (37)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 69 DB0 BA4 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| (70) DB1 BA3 (35)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| (71) DB2 BA2 (34)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| (72) DB3 VDD (33)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| T         CXD1186CQ         BA1 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| (74) DB4 BA0 (31)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| (75) DB5 XAAC (30)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| (76) DB6         ADRQ (29)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 77 DB7 XTC 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 78 XCS XHAC 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| (79) XRDHDRQ (26)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 80 XWR XRST (25)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| (1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000)<br>(1000) |

| -123456789101112131415161718192021222324                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

# **Pin Description**

| Pin No.   |           | <u> </u> |     |                                                            |

|-----------|-----------|----------|-----|------------------------------------------------------------|

| CXD1186CQ | CXD1186CR | Symbol   | I/O | Description                                                |

| 1         | 79        | INT      | 0   | Interrupt request signal to CPU                            |

| 2         | 80        | GND      | —   | GND pin                                                    |

| 3         | 1         | A0       | I   | CPU address signal                                         |

| 4         | 2         | A1       | I   | CPU address signal                                         |

| 5         | 3         | A2       | I   | CPU address signal                                         |

| 6         | 4         | A3       | I   | CPU address signal                                         |

| 7         | 5         | HMDS     | I   | Host mode select signal                                    |

| 8         | 6         | HA0      | I   | Host address signal                                        |

| 9         | 7         | HA1      | I   | Host address signal                                        |

| 10        | 8         | XHCS     | I   | Chip select negative logic signal from host                |

| 11        | 9         | HINT     | 0   | Interrupt request negative logic signal to host            |

| 12        | 10        | GND      | —   | GND pin                                                    |

| 13        | 11        | XHRD     | I/O | Data read strobe signal from host or to SCSI control IC    |

| 14        | 12        | XHWR     | I/O | Data write strobe signal from host or to SCSI control IC   |

| 15        | 13        | HDB0     | I/O | Host data bus                                              |

| 16        | 14        | HDB1     | I/O | Host data bus                                              |

| 17        | 15        | HDB2     | I/O | Host data bus                                              |

| 18        | 16        | HDB3     | I/O | Host data bus                                              |

| 19        | 17        | HDB4     | I/O | Host data bus                                              |

| 20        | 18        | HDB5     | I/O | Host data bus                                              |

| 21        | 19        | HDB6     | I/O | Host data bus                                              |

| 22        | 20        | HDB7     | I/O | Host data bus                                              |

| 23        | 21        | GND      | —   | GND pin                                                    |

| 24        | 22        | HDBP     | I/O | Error flag, Host data bus                                  |

| 25        | 23        | XRST     | I   | Reset negative logic signal                                |

| 26        | 24        | HDRQ     | 0   | Data request positive logic signal to host. Or DMA         |

| 20        | 24        | TIDING   |     | acknowledge negative logic signal to SCSI control IC       |

| 27        | 25        | XHAC     |     | DMA acknowledge negative logic signal from host.           |

| 21        | 25        | AHAO     | 1   | Or data request positive logic signal from SCSI control IC |

| 28        | 26        | XTC      | I   | Terminal count negative logic signal                       |

| 29        | 27        | ADRQ     | I   | DMA request positive logic signal from ADP                 |

| 30        | 28        | XAAC     | 0   | DMA acknowledge negative logic signal to ADP               |

| 31        | 29        | BA0      | 0   | Buffer memory address                                      |

| 32        | 30        | BA1      | 0   | Buffer memory address                                      |

| 33        | 31        | Vdd      | —   | Power (+5 V) supply pin                                    |

| 34        | 32        | BA2      | 0   | Buffer memory address                                      |

| 35        | 33        | BA3      | 0   | Buffer memory address                                      |

| 36        | 34        | BA4      | 0   | Buffer memory address                                      |

| 37        | 35        | BA5      | 0   | Buffer memory address                                      |

| 38        | 36        | BA8      | 0   | Buffer memory address                                      |

| 39        | 37        | BA7      | 0   | Buffer memory address                                      |

| Pin       | No.       | Sumbol | I/O | Description                                                   |

|-----------|-----------|--------|-----|---------------------------------------------------------------|

| CXD1186CQ | CXD1186CR | Symbol | 1/0 | Description                                                   |

| 40        | 38        | BA8    | 0   | Buffer memory address                                         |

| 41        | 39        | BA9    | 0   | Buffer memory address                                         |

| 42        | 40        | GND    | —   | GND pin                                                       |

| 43        | 41        | BA10   | 0   | Buffer memory address                                         |

| 44        | 42        | BA11   | 0   | Buffer memory address                                         |

| 45        | 43        | BA12   | 0   | Buffer memory address                                         |

| 46        | 44        | BA13   | 0   | Buffer memory address                                         |

| 47        | 45        | BA14   | 0   | Buffer memory address                                         |

| 48        | 46        | BA15   | 0   | Buffer memory address                                         |

| 49        | 47        | XMOE   | 0   | Buffer memory output enable negative logic signal             |

| 50        | 48        | XMWR   | 0   | Buffer memory write negative logic signal                     |

| 51        | 49        | BDB0   | I/O | Buffer memory data bus                                        |

| 52        | 50        | GND    | _   | GND pin                                                       |

| 53        | 51        | BDB1   | I/O | Buffer memory data bus                                        |

| 54        | 52        | BDB2   | I/O | Buffer memory data bus                                        |

| 55        | 53        | BDB3   | I/O | Buffer memory data bus                                        |

| 56        | 54        | BDB4   | I/O | Buffer memory data bus                                        |

| 57        | 55        | BDB5   | I/O | Buffer memory data bus                                        |

| 58        | 56        | BDB6   | I/O | Buffer memory data bus                                        |

| 59        | 57        | BDB7   | I/O | Buffer memory data bus                                        |

| 60        | 58        | BDBP   | I/O | Buffer memory pointer data bus                                |

| 61        | 59        | XTL2   | 0   | Crystal oscillation circuit output pin                        |

| 62        | 60        | XTL1   | I   | Crystal oscillation circuit input pin                         |

| 63        | 61        | GND    | _   | GND pin                                                       |

| 64        | 62        | HCLK   | 0   | 1/2 frequency divided clock signal of XTL1                    |

| 65        | 63        | LRCK   | I   | LR clock from CD player                                       |

| 66        | 64        | DATA   | I   | Serial data from CD player                                    |

| 67        | 65        | BCLK   | I   | Bit clock from CD player                                      |

| 68        | 66        | C2PO   | I   | C2 pointer from CD player                                     |

| 69        | 67        | DB0    | I/O | CPU data bus                                                  |

| 70        | 68        | DB1    | I/O | CPU data bus                                                  |

| 71        | 69        | DB2    | I/O | CPU data bus                                                  |

| 72        | 70        | DB3    | I/O | CPU data bus                                                  |

| 73        | 71        | Vdd    |     | Power (+5 V) supply pin                                       |

| 74        | 72        | DB4    | I/O | CPU data bus                                                  |

| 75        | 73        | DB5    | I/O | CPU data bus                                                  |

| 76        | 74        | DB6    | I/O | CPU data bus                                                  |

| 77        | 75        | DB7    | I/O | CPU data bus                                                  |

| 78        | 76        | XCS    | I   | Chip select negative logic signal from CPU                    |

| 79        | 77        | XRD    | I   | CPU strobe negative logic signal to read out this IC internal |

|           |           |        |     | register                                                      |

| 80        | 78        | XWR    | 1   | CPU strobe negative logic signal to write in this IC internal |

|           |           |        |     |                                                               |

# **Electrical Characteristics**

#### **DC** characteristics

### (VDD=5 V±10 %, Vss=0 V, Topr=-20 to +75 °C)

| Item                         |         | Symbol      | Conditions     | Min.    | Тур.  | Max.    | Unit |

|------------------------------|---------|-------------|----------------|---------|-------|---------|------|

|                              | H level | VIH1        |                | 2.2     |       |         | V    |

| Input voltage                | L level | VIL1        |                |         |       | 0.8     | V    |

| TTL Schmitt hysterisis       |         | (Vt+)-(Vt-) |                | 0.2     | 0.4   |         | V    |

| Input current of pull up inp | out     | lı∟         | VIL=0 V        | -40     | -100  | -240    | μA   |

| Input current of pull down   | input   | Ін          | Vih=Vdd        | 40      | 100   | 240     | μA   |

|                              | H level | Vон1        | Іон=–2 mA      | Vdd-0.8 |       |         | V    |

| Output voltage               | L level | Vol1        | lo∟=4 mA       |         |       | 0.4     | V    |

| Open drain output L level    |         | Vol2        | lo∟=4 mA       |         |       | 0.4     | V    |

| Oscillation cell             | H level | Viн         |                | 0.7 Vdd |       |         | V    |

| input voltage                | L level | VIL         |                |         |       | 0.3 Vdd | V    |

| Logic threshold value        |         | LVth        |                |         | Vdd/2 |         | V    |

| Feedback resistance          |         | Rfb         | VIN=Vss or VDD | 250 k   | 1 M   | 2.5 M   | Ω    |

|                              | H level | Vон         | Іон=–1 mA      | Vdd/2   |       |         | V    |

| Output voltage               | L level | Vol         | lo∟=1 mA       |         |       | Vdd/2   | V    |

| <ul> <li>Input pin with pull up resistance</li> </ul> | : XHCS, HA0, HA1, XTC |

|-------------------------------------------------------|-----------------------|

| Input pin with pull down resistance                   | : C2PO, HMDS, ADRQ    |

| <ul> <li>Input pin with pull down resistance</li> </ul> | : | C2PO, HMDS, ADR |

|---------------------------------------------------------|---|-----------------|

• TTL Schmitt input pin

• Open drain output pin

: XRST : HINT

- Two-way data bus always pulled up.

- Oscillation cell

| Input  | : | XTL1 |

|--------|---|------|

| Output | : | XTL2 |

### I/O capacitance

VDD=VI=0 V, f=1 MHz

| Item       | Symbol | Min. | Тур. | Max. | Unit |

|------------|--------|------|------|------|------|

| Input pin  | CIN    |      |      | 9    | pF   |

| Output pin | Соит   |      |      | 11   | pF   |

| I/O pin    | Ci/o   |      |      | 11   | pF   |

# **AC characteristics**

(Ta=-20 to +75 °C, Vdd=5 V $\pm$ 10 %, Output Load=50 pF, f $\leq$  24.576 MHz)

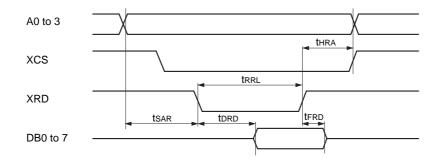

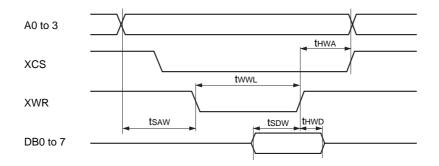

# 1. CPU interface

(1) Read

| Item                                             | Symbol | Min. | Тур. | Max. | Unit |

|--------------------------------------------------|--------|------|------|------|------|

| Address setup time (vs. XCS & XRD $\downarrow$ ) | tsar   | 30   |      |      | n    |

| Address hold time (vs. XCS & XRD ↑)              | thra   | 20   |      |      | n    |

| Data delay time (vs. XCS & XRD $\downarrow$ )    | tdrd   |      |      | 60   | n    |

| Data float time (vs. XCS & XRD ↑)                | tfrd   | 0    |      | 10   | n    |

| Low level XRD pulse width                        | trrl   | 100  |      |      | n    |

(2) Write

| Item                                             | Symbol | Min. | Тур. | Max. | Unit |

|--------------------------------------------------|--------|------|------|------|------|

| Address setup time (vs. XCS & XWR $\downarrow$ ) | tsaw   | 30   |      |      | n    |

| Address hold time (vs. XCS & XWR ↑)              | thwa   | 20   |      |      | n    |

| Data setup time (vs. XCS & XWR ↑)                | tsow   | 40   |      |      | n    |

| Data hold time (vs. XCS & XWR ↑)                 | thwd   | 10   |      |      | n    |

| Low level XWR pulse width                        | twwL   | 50   |      |      | n    |

Where & in the chart indicates logical multiplication.

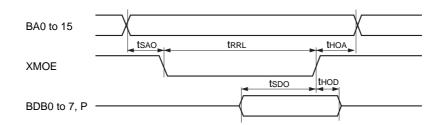

# 2. Memory interface

(1) Read

| Item                                        | Symbol | Min.   | Тур. | Max.    | Unit |

|---------------------------------------------|--------|--------|------|---------|------|

| Address setup time (vs. XMOE $\downarrow$ ) | tsao   | Tw-22  |      |         | n    |

| Address hold time (vs. XMOE ↑)              | tноа   | Tw–9   |      |         | n    |

| Data setup time (vs. XMOE ↑)                | tsdo   | 45     |      |         | n    |

| Data hold time (vs. XMOE ↑)                 | thod   | 0      |      |         | n    |

| Low level XMOE pulse width                  | trrl   | 2 • Tw |      | 2•Tw+16 | n    |

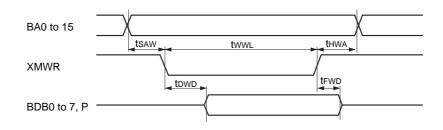

(2) Write

| Item                                        | Symbol | Min.   | Тур. | Max. | Unit |

|---------------------------------------------|--------|--------|------|------|------|

| Address setup time (vs. XMWR $\downarrow$ ) | tsaw   | Tw–29  |      |      | n    |

| Address hold time (vs. XMWR ↑)              | thwa   | Tw–9   |      |      | n    |

| Data delay time (vs. XMWR $\downarrow$ )    | towd   |        |      | 0    | n    |

| Data float time (vs. XMWR ↑)                | tFWD   | 10     |      |      | n    |

| Low level XMWR pulse width                  | tww∟   | 2 • Tw |      |      | n    |

Where Tw=1/f.

Usually, when f=16.9344 MHz, use a RAM with access time within 120 ns.

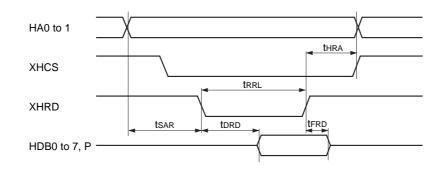

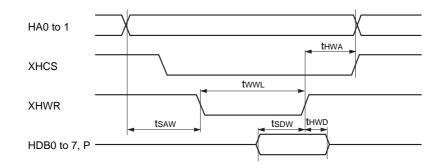

# 3. Host interface

(1) Read

| Item                                               | Symbol | Min. | Тур. | Max. | Unit |

|----------------------------------------------------|--------|------|------|------|------|

| Address setup time (vs. XHCS & XHRD $\downarrow$ ) | tsar   | 30   |      |      | n    |

| Address hold time (vs. XHCS & XHRD ↑)              | thra   | 20   |      |      | n    |

| Data delay time (vs. XHCS & XHRD $\downarrow$ )    | tdrd   |      |      | 60   | n    |

| Data float time (vs. XHCS & XHRD ↑)                | tfrd   | 0    |      | 10   | n    |

| Low level XHRD pulse width                         | trrl   | 100  |      |      | n    |

(2) Write

| Item                                               | Symbol | Min. | Тур. | Max. | Unit |

|----------------------------------------------------|--------|------|------|------|------|

| Address setup time (vs. XHCS & XHWR $\downarrow$ ) | tsaw   | 30   |      |      | n    |

| Address hold time (vs. XHCS & XHWR ↑)              | thwa   | 20   |      |      | n    |

| Data setup time (vs. XHCS & XHWR ↑)                | tsow   | 40   |      |      | n    |

| Data hold time (vs. XHCS & XHWR ↑)                 | thwd   | 10   |      |      | n    |

| Low level XHWR pulse width                         | twwL   | 50   |      |      | n    |

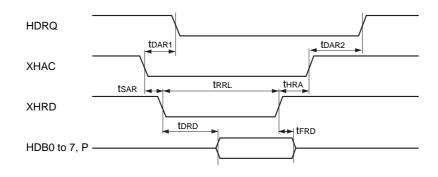

# 4. HOST DMA cycle (80 type bus)

(1) Read

| Item                                     | Symbol | Min. | Тур. | Max. | Unit |

|------------------------------------------|--------|------|------|------|------|

| HDRQ fall time (vs. XHAC $\downarrow$ )  | tDAR1  |      |      | 35   | n    |

| HDRQ rise time (vs. XHAC ↑)              | tDAR2  |      |      | 48   | n    |

| XHAC setup time (vs. XHRD $\downarrow$ ) | tsar   | 5    |      |      | n    |

| XHAC hold time (vs. XHRD ↑)              | thra   | 0    |      |      | n    |

| Low level XHRD pulse width               | trrl   | 100  |      |      | n    |

| Data delay time (vs. XHRD $\downarrow$ ) | tdrd   |      |      | 60   | n    |

| Data float time (vs. XHRD ↑)             | tfrd   | 0    |      | 10   | n    |

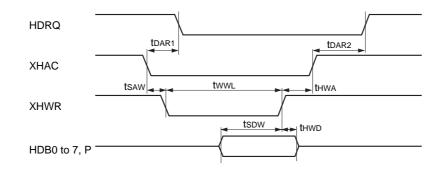

### (2) Write

| Item                                     | Symbol | Min. | Тур. | Max. | Unit |

|------------------------------------------|--------|------|------|------|------|

| HDRQ fall time (vs. XHAC $\downarrow$ )  | tDAR1  |      |      | 35   | n    |

| HDRQ rise time (vs. XHAC ↑)              | tdar2  |      |      | 48   | n    |

| XHAC setup time (vs. XHWR $\downarrow$ ) | tsaw   | 5    |      |      | n    |

| XHAC hold time (vs. XHWR ↑)              | thwa   | 0    |      |      | n    |

| Low level XHWR pulse width               | twwL   | 50   |      |      | n    |

| Data setup time (vs. XHWR ↑)             | tsow   | 40   |      |      | n    |

| Data hold time (vs. XHWR ↑)              | thwd   | 10   |      |      | n    |

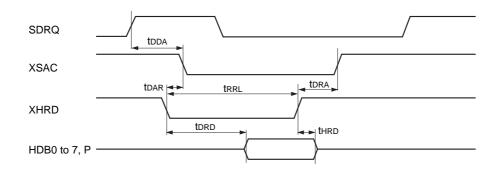

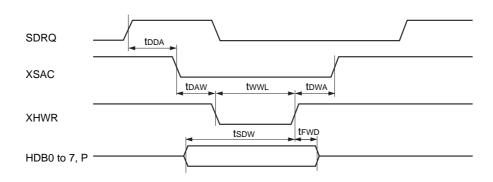

# 5. HOST DMA cycle (SCSI bus)

(1) Read

| Item                                     | Symbol       | Min. | Тур. | Max. | Unit |

|------------------------------------------|--------------|------|------|------|------|

| XSAC fall time (vs. SDRQ ↑)              | tdda         |      |      | Tw   | n    |

| XSAC delay time (vs. XHRD $\downarrow$ ) | tdar         | 0    |      |      | n    |

| XSAC delay time (vs. XHRD ↑)             | <b>t</b> dra |      |      | Tw   | n    |

| Low level XHRD pulse width               | trrl         | T+59 |      |      | n    |

| Data delay time (vs. XHRD $\downarrow$ ) | tdrd         |      |      | 90   | n    |

| Data hold time (vs. XHRD ↑)              | thrd         | 0    |      |      | n    |

(2) Write

| Item                                     | Symbol | Min. | Тур. | Max. | Unit |

|------------------------------------------|--------|------|------|------|------|

| XSAC fall time (vs. SDRQ ↑)              | tdda   |      |      | Tw   | n    |

| XHWR delay time (vs. XSAC $\downarrow$ ) | tdaw   |      |      | Tw   | n    |

| XSAC delay time (vs. XHWR ↑)             | tdwa   |      |      | Tw   | n    |

| Low level XHWR pulse width               | tww∟   | Т    |      |      | n    |

| Data setup time (vs. XHWR $\downarrow$ ) | tsow   | T+24 |      |      | n    |

| Data float time (vs. XHWR $\downarrow$ ) | tfwd   | 27   |      |      | n    |

Where T in the chart indicates :

Tw for 3 cycle mode

2 • Tw for 4 cycle mode

3 • Tw for 5 cycle mode

Here Tw=1/f

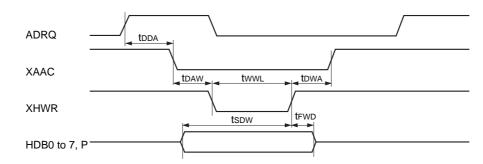

### 6. ADPCM DMA cycle

| Item                                     | Symbol       | Min. | Тур. | Max. | Unit |

|------------------------------------------|--------------|------|------|------|------|

| XAAC fall time (vs. ADRQ ↑)              | <b>t</b> dda |      |      | Tw   | n    |

| XHWR delay time (vs. XAAC $\downarrow$ ) | tdaw         |      |      | Tw   | n    |

| XAAC delay time (vs. XHWR ↑)             | tdwa         |      |      | Tw   | n    |

| Low level XHWR pulse width               | tww∟         | Т    |      |      | n    |

| Data setup time (vs. XHWR $\downarrow$ ) | tsow         | T+24 |      |      | n    |

| Data float time (vs. XHWR $\downarrow$ ) | tFWD         | 27   |      |      | n    |

Where T in the chart indicates :

Tw for 3 cycle mode

2 • Tw for 4 cycle mode

3 • Tw for 5 cycle mode

Here Tw=1/f

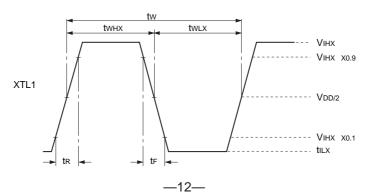

### 7. XTL1 and XTL2 pins

(1) For self oscillation

#### (Topr=-20 to +75 °C, VDD=5.0 V±10 %)

| Item                  | Symbol | Min.    | Тур. | Max.   | Unit |

|-----------------------|--------|---------|------|--------|------|

| Oscillation frequency | fмах   | 16.9344 |      | 24.576 | MHz  |

(2) When a pulse is input to XTL1

(Topr=-20 to +75 °C, VDD=5.0 V±10 %)

| Item                  | Symbol | Min.    | Тур. | Max. | Unit |

|-----------------------|--------|---------|------|------|------|

| "H" level pulse width | twнx   | 15      |      |      | ns   |

| "L" level pulse width | twLx   | 15      |      |      | ns   |

| Pulse period          | tw     | 40.7    |      |      | ns   |

| Input "H" level       | Vihx   | Vdd—1.0 |      |      | V    |

| Input "L" level       | VILX   |         |      | 0.8  | V    |

| Rise time, Fall time  | tr, tr |         |      | 15   | ns   |

# **Description of Function**

1. Pin description

Below is a description of pins by function.

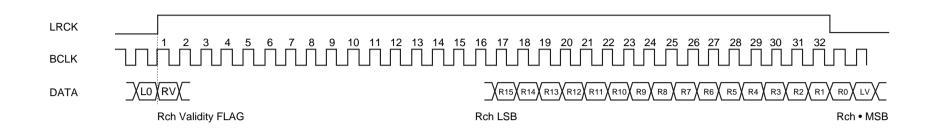

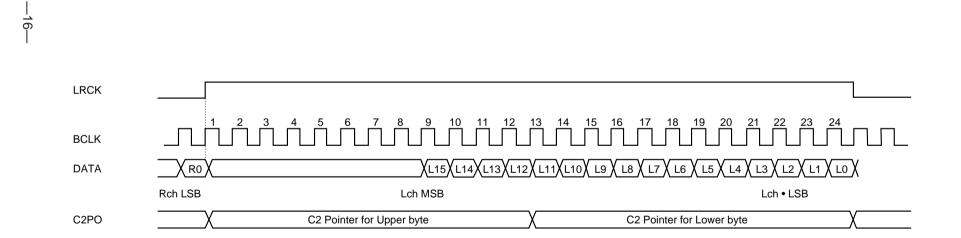

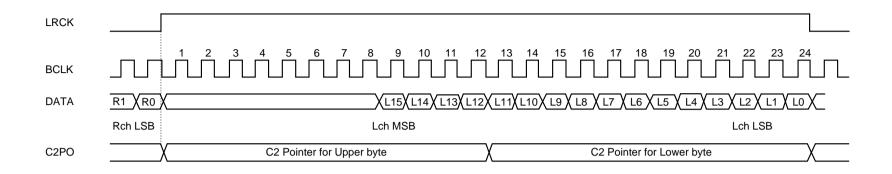

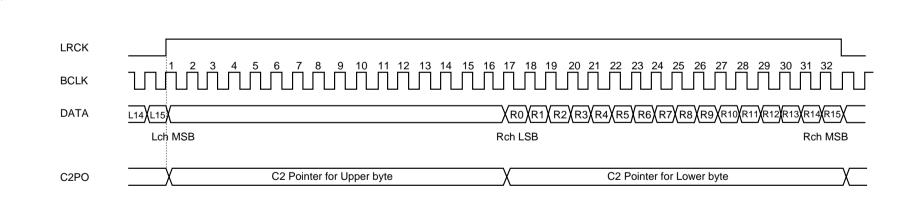

- 1.1 CD player interface (4 pins)

- DATA (input) Serial data from CIRC LSI (digital signal processing LSI for CD)

BCLK (input)

- Bit clock. Clock for DATA Strobe.

- (3) LRCK (input) LR clock. Indicates Lcн and Rcн of DATA input.

- (4) C2PO (positive logic input)

C2 pointer signal from CIRC. Indicates an error is included in the DATA input. Interface mode with the CD player is controlled at DRVIF register.

- 1.2 Buffer memory interface (27 pins)

- XMWR (memory write, negative logic output)

Data write strobe signal of the buffer memory.

- (2) XMOE (memory output enable, negative logic output) Data read strobe signal of the buffer memory.

- (3) BA0 to 15 (Buffer memory address, output) Address signal of the buffer memory.

- (4) BDB0 to 7 (Buffer data bus, I/O)Data bus signal of the buffer memory.

- (5) BDBP (Buffer data bus, I/O) Buffer memory data bus signal for error pointer.

- 1.3 CPU interface (16 pins)

- (1) XWR (CPU write, negative logic input) Write strobe signal of the CPU register.

- (2) XRD (CPU read, negative logic input) Read out strobe signal of the CPU register.

- (3) XCS (CPU chip select, negative logic input) Chip select negative logic signal from the CPU.

- (4) A0 to 3 (CPU address, input)Address signal for the CPU selection of the IC internal register.

- (5) DB0 to 7 (CPU data bus, I/O) CPU data bus signal.

- (6) INT (CPU interrupt, output) Interrupt request output to the CPU. This pin polarity is controlled at the CONFIG register.