### High-speed Buffer Amplifier for CCD Image Sensor

# CXA3691AEN

#### **Description**

The CXA3691AEN is a high-speed buffer amplifier IC. (Applications: CCD image sensor output buffers, Digital still cameras, Camcorders, Other general buffers)

#### **Features**

- Power consumption: 24mW (typ.)

(IDRV = 50μA (220kΩ when Vcc = 15V), ISF pin connected to GND, during no signal)

- ◆ Push-pull output

- ♦ High-speed response:  $500V/\mu s$  (IDRV =  $50\mu A$  (220k $\Omega$  when Vcc = 15V), CL = 20pF)

- ◆ Internal sink current mode for CCD with open source output (Settable by external resistance RISF)

- ♦ Enables to set the responsibility by changing the drive current by an external resistor

#### **Structure**

Bipolar silicon monolithic IC

### **Absolute Maximum Ratings**

(Ta = 25°C)

| <ul> <li>Supply voltage</li> </ul> | Vcc  | 16                       | V  |

|------------------------------------|------|--------------------------|----|

| <ul> <li>Supply voltage</li> </ul> | IN   | GND - 0.3 to $Vcc + 0.3$ | V  |

| Storage temperature                | Tstg | -65 to +150              | °C |

| Allowable power dissipation        | Pp   | 0.28                     | W  |

|                                    |      |                          |    |

(when mounted on a two-layer board;  $50mm \times 50mm$ , t = 1.6mm)

#### **Recommended Operating Conditions**

| Supply voltage                            | VCC | 9.0 to 15.5 | V            |

|-------------------------------------------|-----|-------------|--------------|

| <ul> <li>Operating temperature</li> </ul> | Та  | -20 to +75  | $^{\circ}$ C |

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

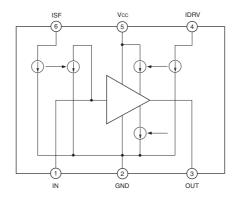

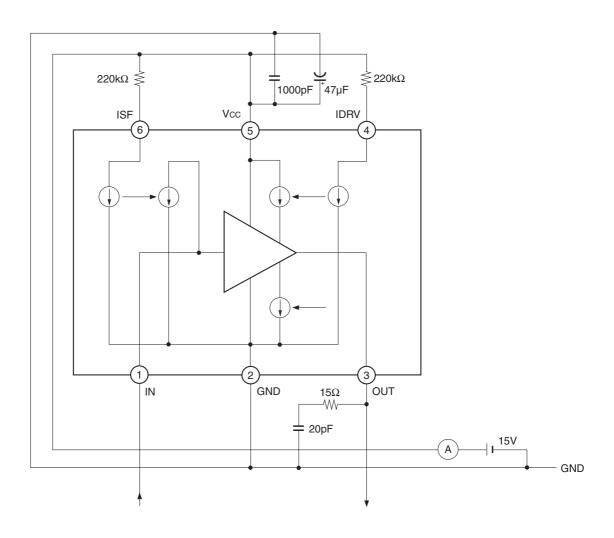

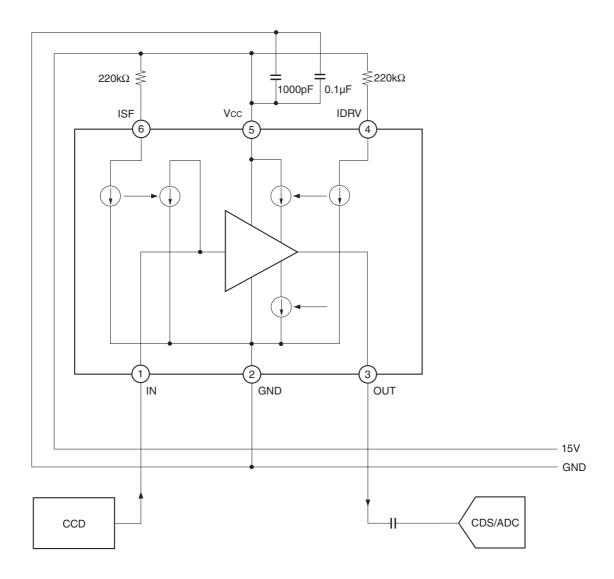

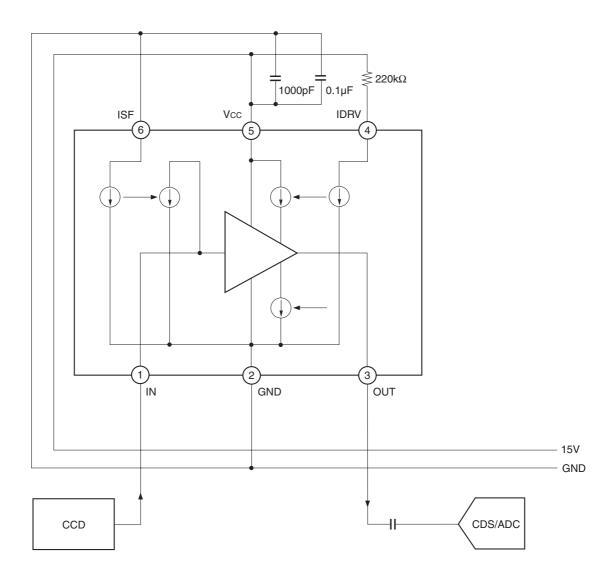

# Block Diagram and Pin Configuration

(Top View)

# Pin Description and I/O Pin Equivalent Circuit

| Pin<br>No. | Symbol | I/O | Standard voltage level | Equivalent circuit             | Description                                                                                                                                                                                                                                                                                                     |

|------------|--------|-----|------------------------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2          | GND    | _   | 0V                     | _                              | GND.                                                                                                                                                                                                                                                                                                            |

| 5          | Vcc    | _   | 15V                    |                                | Supply voltage input.                                                                                                                                                                                                                                                                                           |

| 1          | IN     | I   | CCD<br>output voltage  | Vcc                            | Input.                                                                                                                                                                                                                                                                                                          |

| 6          | ISF    | -   |                        | Vcc<br>6 Wy<br>30k             | External resistor connection for setting the sink current for CCD with open source output. Connect an external resistor between this pin and Vcc (Pin 5). Connect this pin to GND (Pin 2) when not using this function. * The minimum value of the external resistance should be $100k\Omega$ (when Vcc = 15V). |

| 3          | OUT    | 0   | ≈IN                    | Vcc<br>₹50<br>3<br>GND         | Output.                                                                                                                                                                                                                                                                                                         |

| 4          | IDRV   | ı   | _                      | Vcc<br>4<br>Www<br>30k<br>S20k | External resistor connection for setting the drive current. Connect an external resistor between this pin and Vcc (Pin5). * The minimum value of the external resistance should be 100kΩ (when Vcc = 15V).                                                                                                      |

# **Electrical Characteristics**

(Ta = 25°C, Vcc = 15V, R<sub>IDRV</sub> = 220k $\Omega$ , ISF pin: connected to GND)

### **DC Characteristics**

| Item               | Symbol  | Measurement conditions                                                                          | Min.                     | Тур.       | Max.                                              | Unit |

|--------------------|---------|-------------------------------------------------------------------------------------------------|--------------------------|------------|---------------------------------------------------|------|

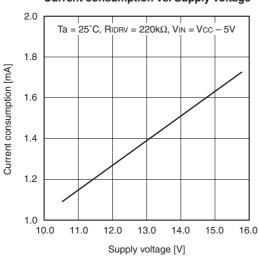

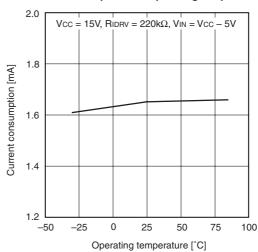

| Supply current     | Icc     | IN = 10V, Ridry = $220k\Omega$                                                                  | 1.4                      | 1.6        | 1.8                                               | mA   |

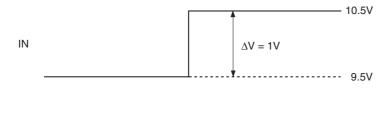

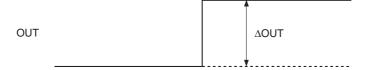

| Voltage gain       | VGAIN   | *1 IN: $10Vdc \Delta V = 1V$ GAIN = $\Delta OUT/\Delta V$                                       | _                        | 0.999      | _                                                 | V/V  |

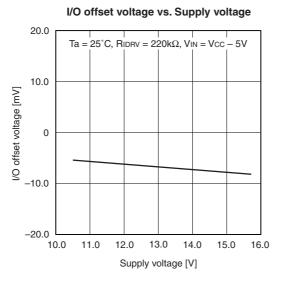

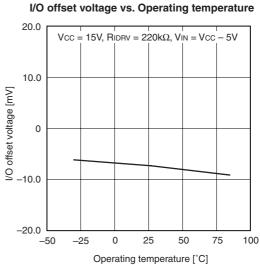

| I/O offset voltage | Voffset | IN = 10V<br>VOFFSET = OUT-IN                                                                    | -100                     | _          | 100                                               | mV   |

| I/O voltage range  | VRANGE  | $R_{IDRV} = 100k\Omega$ $R_{IDRV} = 150k\Omega$ $R_{IDRV} = 220k\Omega$ $R_{IDRV} = 330k\Omega$ | 3.3<br>2.9<br>2.5<br>2.1 |            | Vcc - 2.0<br>Vcc - 1.85<br>Vcc - 1.8<br>Vcc - 1.7 | ٧    |

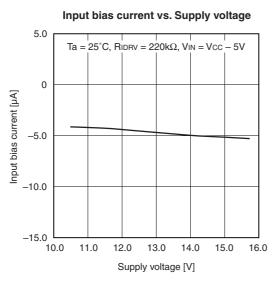

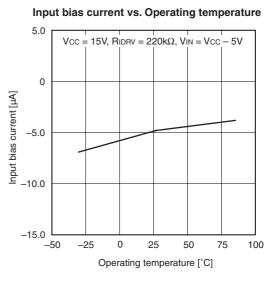

| Input bias current | IBIAS   | IN = 10V, ISF = 0V                                                                              | <b>–15</b>               | <b>-</b> 5 | 6                                                 | μΑ   |

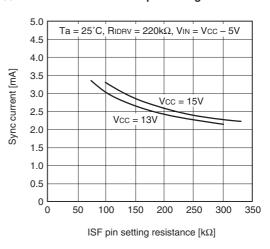

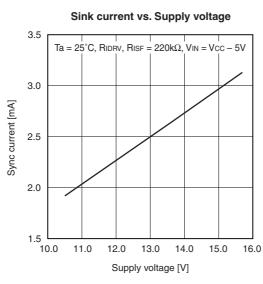

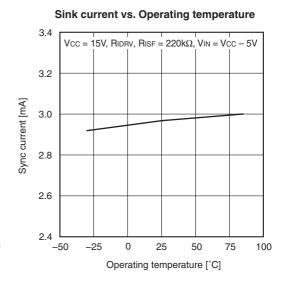

| Sync current       | Isink   | IN = 10V, RISF = 220kΩ                                                                          | 2.6                      | 2.9        | 3.2                                               | mA   |

# \*1 Voltage gain

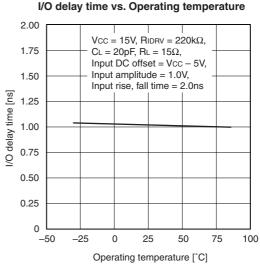

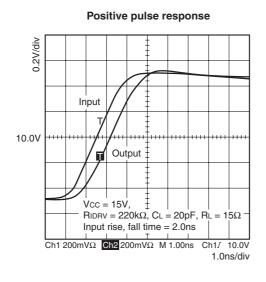

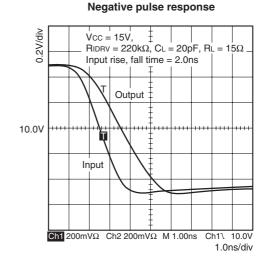

### **AC Characteristics**

(Ta = 25°C, Vcc = 15V, IDRV =  $50\mu A$  (220k $\Omega$  when Vcc = 15V), ISF pin: connected to GND, RL = 15 $\Omega$ , CL = 20pF)

| Item           | Symbol | Measurement conditions               | Min. | Тур. | Max. | Unit |

|----------------|--------|--------------------------------------|------|------|------|------|

| Bandwidth      | GBW    | IN = 50mVp-p                         | _    | 220  | _    | MHz  |

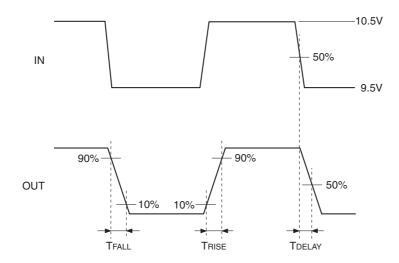

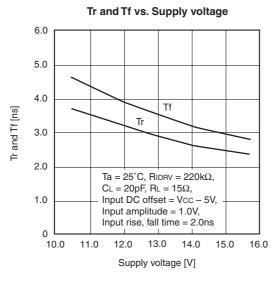

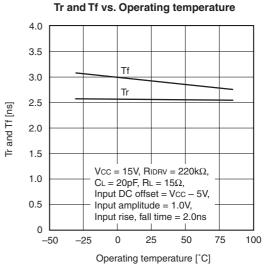

| Rise time      | Trise  | *1<br>IN = 9.5 to 10.5V<br>10 to 90% | _    | 2.5  | 3.5  | ns   |

| Fall time      | TFALL  | *1<br>IN = 10.5 to 9.5V<br>10 to 90% | 1    | 3.0  | 4.0  | ns   |

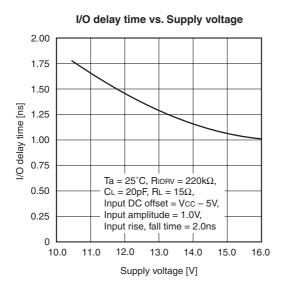

| I/O delay time | TDELAY | *1<br>IN = 9.5 to 10.5V<br>@50%      | 0.9  | 1.0  | 2.0  | ns   |

$<sup>^{*1}</sup>$  Rise time, fall time and I/O delay time

# **Evaluation Circuit**

### **Description of Operation**

#### **Current Settings**

#### 1. Output Drive Current

The small signal output impedance of the OUT pin (Pin 3) can be set by connecting the IDRV pin (Pin 4) to Vcc through a resistor. The inflow current to the IDRV pin is multiplied by 10 times inside the IC, and flows as the output stage idling current.

The IDRV pin has an internal  $50k\Omega$  resistor, so the inflow current to the IDRV pin can be calculated as follows.

IIDRV =

$$(Vcc - VbE \times 2)/(RidRV + 50kΩ)$$

=  $(15 - 1.46)/270kΩ$

=  $50.1μA$

Here, Vcc = 15V, VBE = 0.73V (typ.), and RIDRV =  $220k\Omega$ .

The small signal output impedance at this time can be calculated as follows.

ROUT =

$$(26\text{mV}/(10 \times \text{IiDRV}))/2$$

=  $(26\text{mV}/501\mu\text{A})/2$

=  $26\Omega$

#### 2. Sink Current for CCD with open source output

The sink current of the IN pin (Pin 6) can be set by connecting the ISF pin (Pin 1) to Vcc through a resistor. This sink current can be used as the CCD output stage source follower drive current. The inflow current to the ISF pin is multiplied by 58 times inside the IC, and flows as the sink current.

The ISF pin has an internal 50k $\Omega$  resistor, so the inflow current to the ISF pin can be calculated as follows.

IISF = (Vcc - VBE

$$\times$$

2)/(RISF + 50kΩ)

= (15 - 1.46)/270kΩ

= 50.1μA

Here, Vcc = 15V, VBE = 0.73V (typ.), and RISF = 220k $\Omega$ . The sink current at this time can be calculated as follows.

$$Isink = 58 \times IISF$$

$$= 2.9mA$$

Note) This IC operation depends on IDRV and ISF.

This specification is described based on IDRV of  $220k\Omega$  when Vcc = 15V. However , set it to  $180k\Omega$  to occur the same current when using under the condition that Vcc = 13V. [IDRV and ISF vs external resistor]

Current (µA) 90 68 50 35 26 Unit When Vcc = 15V 100 150 220 330 470 kO. When Vcc = 13V 78 120 180 270 390  $k\Omega$

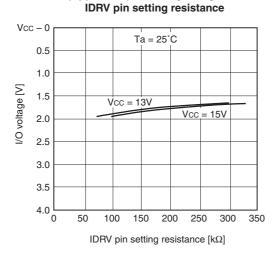

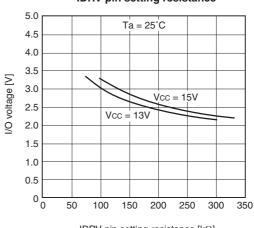

## **Example of Representative Characteristics**

# (Upper side) I/O voltage range vs.

# (Lower side) I/O voltage range vs. IDRV pin setting resistance

IDRV pin setting resistance  $[k\Omega]$

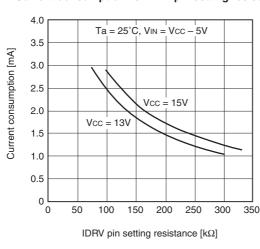

#### Current consumption vs. IDRV pin setting resistance

#### Sink current vs. ISF pin setting resistance

#### Current consumption vs. Supply voltage

#### Current consumption vs. Operating temperature

# Application Circuit 1 (when using CCD with open source output )

Application circuits shown are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits or for any infringement of third party patent and other right due to same.

# Application Circuit 2 (when using CCD with internal current source)

Application circuits shown are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits or for any infringement of third party patent and other right due to same.

## **Notes on Operation**

- ◆ Provide the widest GND pattern possible on the board.

- Use a 1000pF (recommended) and a 0.1μF (recommended) ceramic capacitors in parallel for the bypass capacitor connected between the power supply and GND, and connect them as close to the IC pins as possible.

- ◆ Load capacitance causes the input/output wiring response to worsen and results in noise. Use the shortest wiring layout possible, and shield it with GND.

- When the output pin (Pin 3) is shorted to either the power supply or GND, an overcurrent may flow to the output stage elements and damage them.

When the input pin (Pin 1) is shorted to GND, an overcurrent may flow to the internal parasitic elements and damage them.

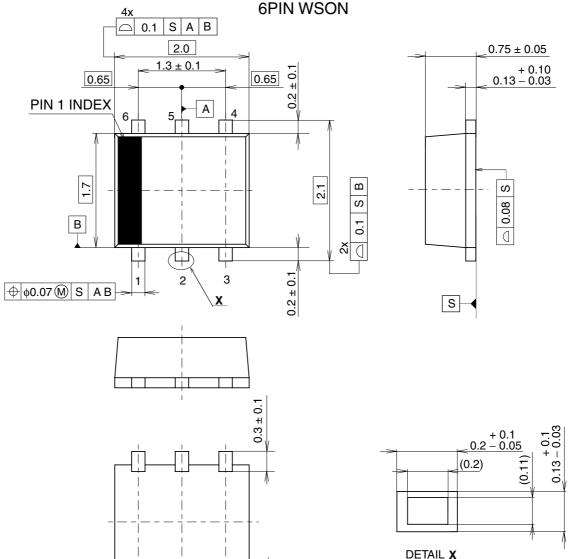

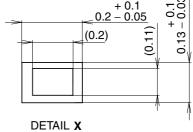

# **Package Outline**

(Unit: mm)

| SONY CODE  | WSON-6P-051 |

|------------|-------------|

| EIAJ CODE  |             |

| JEDEC CODE |             |

$0.1 \pm 0.03$ + 0.1 6 - 0.20 – 0.05

0.1 ± 0.03

#### PACKAGE STRUCTURE

| • | .,                 |             |  |  |  |  |

|---|--------------------|-------------|--|--|--|--|

|   | PACKAGE MATERIAL   | EPOXY RESIN |  |  |  |  |

|   | TERMINAL TREATMENT | Sn-Bi       |  |  |  |  |

|   | TERMINAL MATERIAL  | COPPER      |  |  |  |  |

|   | PACKAGE MASS       | 0.008g      |  |  |  |  |

#### **LEAD PLATING SPECIFICATIONS**

| ITEM               | SPEC.           |

|--------------------|-----------------|

| LEAD MATERIAL      | COPPER ALLOY    |

| SOLDER COMPOSITION | Sn-Bi Bi:1-4wt% |

| PLATING THICKNESS  | 5-18µm          |