## SONY

# **CXA3555N**

## All Band Tuner IC with On-chip PLL

#### **Description**

The CXA3555N is a monolithic TV tuner IC which integrates local oscillator and mixer circuits for VHF band, local oscillator and mixer circuits for UHF band, an IF amplifier and a tuning PLL onto a single chip, enabling further miniaturization of the tuner.

#### **Features**

- Low power consumption (5V, 63mA typ.)

- Low noise figure, low distortion characteristics

- High gain/low gain selectable

- Supports IF double-tuned/adjacent channel trap

- Balanced oscillator circuits (3 sets) with excellent oscillation stability

- On-chip PLL supports I2C bus

- On-chip high voltage drive transistor for charge pump

- Frequency step selectable from 31.25, 50 or 62.5kHz (when using a 4MHz crystal)

- · Low-phase noise synthesizer

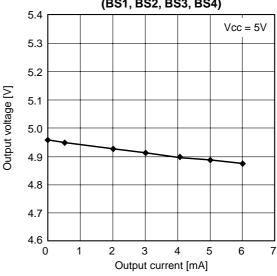

- On-chip 4-output band switch (output voltage: 5V, current capacity: 5mA)

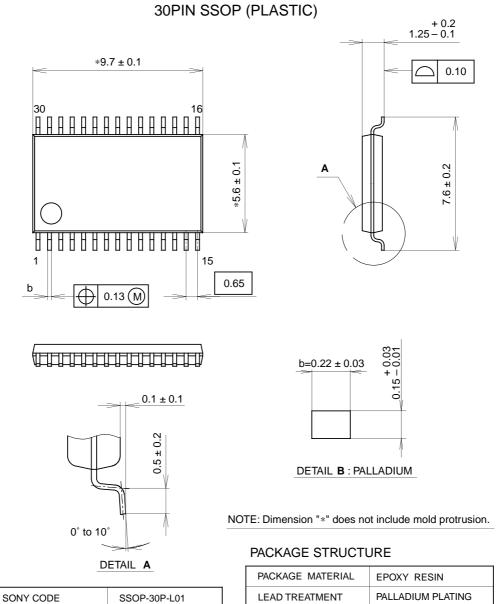

- 30-pin SSOP small package

#### **Applications**

- TV tuners

- VCR tuners

- CATV tuners

#### Structure

Bipolar silicon monolithic IC

#### **Absolute Maximum Ratings**

| <ul> <li>Supply voltage</li> </ul>      | Vcc  | -0.3 to $+5.5$ | V  |

|-----------------------------------------|------|----------------|----|

| Operating temperature                   | Topr | -25 to +75     | °C |

| <ul> <li>Storage temperature</li> </ul> | Tstg | -55 to +150    | °C |

| • Allowable power dissipa               | tion |                |    |

|                                         | Pp   | 580            | mW |

#### **Operating Conditions**

Supply voltage Vcc 4.75 to 5.30 V

**Note:** This IC has pins whose electrostatic discharge strength is weak as the operating frequency is high and the high-frequency process is used for this IC. Take care of handling the IC.

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

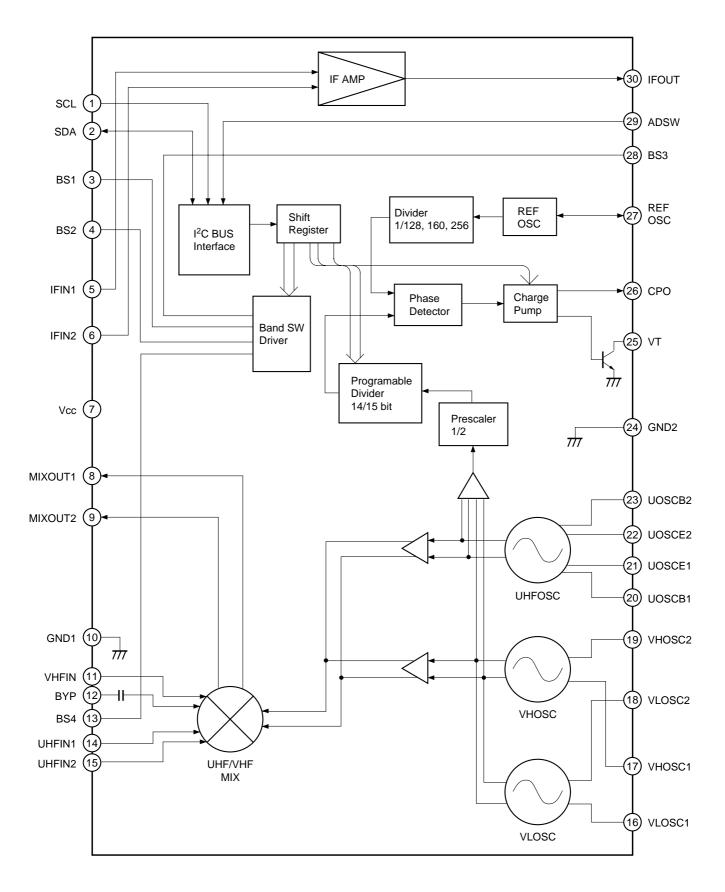

### **Block Diagram and Pin Configuration**

## **Pin Description**

| Pin<br>No. | Symbol  | Description                                             |

|------------|---------|---------------------------------------------------------|

| 1          | SCL     | SCL input                                               |

| 2          | SDA     | SDA I/O                                                 |

| 3          | BS1     | Band switch output 1                                    |

| 4          | BS2     | Band switch output 2                                    |

| 5          | IFIN1   | IF amplifier input                                      |

| 6          | IFIN2   | IF amplifier input                                      |

| 7          | Vcc     | Power supply                                            |

| 8          | MIXOUT1 | MIX output (open collector)                             |

| 9          | MIXOUT2 | MIX output (open collector)                             |

| 10         | GND1    | Analog circuit GND                                      |

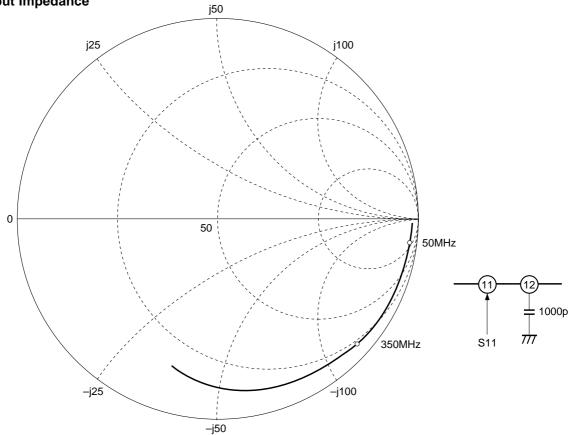

| 11         | VHFIN   | VHF input                                               |

| 12         | BYP     | VHF input GND and gain switching (low: GND, high: open) |

| 13         | BS4     | Band switch output 4                                    |

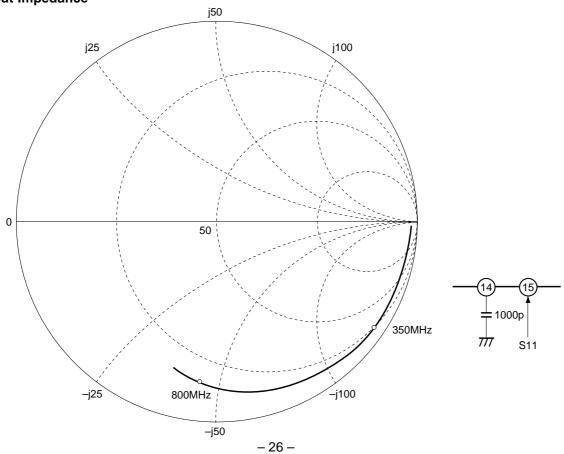

| 14         | UHFIN1  | UHF input                                               |

| 15         | UHFIN2  | UHF input                                               |

| 16         | VLOSC1  | VHF Low-band oscillator                                 |

| 17         | VHOSC1  | VHF High-band oscillator                                |

| 18         | VLOSC2  | VHF Low-band oscillator                                 |

| 19         | VHOSC2  | VHF High-band oscillator                                |

| 20         | UOSCB1  | UHF oscillator (base pin)                               |

| 21         | UOSCE1  | UHF oscillator (emitter pin)                            |

| 22         | UOSCE2  | UHF oscillator (emitter pin)                            |

| 23         | UOSCB2  | UHF oscillator (base pin)                               |

| 24         | GND2    | PLL circuit GND                                         |

| 25         | VT      | Tuning voltage output (open collector)                  |

| 26         | CPO     | Charge pump output (loop filter connection)             |

| 27         | REFOSC  | Crystal connection for PLL reference oscillator         |

| 28         | BS3     | Band switch output 3                                    |

| 29         | ADSW    | Address selection (I <sup>2</sup> C bus)                |

| 30         | IFOUT   | IF amplifier output                                     |

## **Pin Description**

| Pin<br>No. | Symbol | Pin voltage [V] | Equivalent circuit       | Description                                        |

|------------|--------|-----------------|--------------------------|----------------------------------------------------|

| 1          | SCL    | _               | 7 40k 1777               | Clock input                                        |

| 2          | SDA    |                 | 40k<br>2 40k<br>1 5p     | Data input                                         |

| 3          | BS1    |                 | 7                        |                                                    |

| 4          | BS2    | High: 4.9       | (3)<br>4) 70k ≶          | Band switch outputs. This pin corresponding to the |

| 13         | BS4    | Low: 0.0        |                          | selected band goes High.                           |

| 28         | BS3    |                 | (3)<br>(28)<br>//// //// |                                                    |

| Pin<br>No. | Symbol  | Pin voltage<br>[V]                                         | Equivalent circuit                              | Description                                                                                            |

|------------|---------|------------------------------------------------------------|-------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| 5          | IFIN1   | 2.0                                                        | 5<br>1.6k<br>6<br>1.6k                          | IF inputs. These pins must be connected                                                                |

| 6          | IFIN2   | 2.0                                                        |                                                 | to the mixer outputs via coupling capacitance.                                                         |

| 7          | Vcc     | _                                                          |                                                 | Power supply.                                                                                          |

| 8          | MIXOUT1 | _                                                          | 8 9                                             | Mixer outputs. These pins output the signal in open collector format, and they                         |

| 9          | MIXOUT2 |                                                            |                                                 | must be connected to the power supply via a load.                                                      |

| 10         | GND1    | _                                                          |                                                 | Analog circuit GND.                                                                                    |

| 11         | VHFIN   | 2.4 during<br>VHF reception<br>0.0 during<br>UHF reception | 7<br>  15p                                      | VHF input.<br>The input format is unbalanced input.                                                    |

| 12         | ВҮР     | Vcc<br>(when open)                                         | 3k \$ 3k                                        | VHF input GND and gain switching. GND: low gain Open: high gain (However, when control byte GC is "0") |

| 14         | UHFIN1  | 0.0 during<br>VHF reception                                | (14)<br>(15)                                    | UHF inputs. Input a balanced signal to Pins 14 and 15, or ground                                       |

| 15         | UHFIN2  | 2.3 during<br>UHF reception                                | 3k ₹ 3k ₹ → W → → → → → → → → → → → → → → → → → | either of Pin 14 or 15 with a capacitor and input the signal to the other pin.                         |

| Pin<br>No. | Symbol | Pin voltage<br>[V]                                         | Equivalent circuit                                                                                     | Description                                                                                                                                         |

|------------|--------|------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 16         | VLOSC1 | 0.0                                                        | 7<br>16<br>18<br>33<br>33<br>33<br>33<br>33<br>4<br>11<br>11<br>11<br>11<br>11<br>11<br>11<br>11<br>11 | External resonance circuit                                                                                                                          |

| 18         | VLOSC2 | 0.0                                                        | 50k \$ \$ 50k                                                                                          | connection for VL oscillator.                                                                                                                       |

| 17         | VHOSC1 | 0.0                                                        | 7<br>19<br>20<br>20<br>20<br>20<br>20<br>11<br>11<br>11<br>11                                          | External resonance circuit                                                                                                                          |

| 19         | VHOSC2 | 0.0                                                        | 50k \$ \$ \$ 50k                                                                                       | connection for VH oscillator.                                                                                                                       |

| 20         | UOSCB1 | 2.4 during<br>VHF reception<br>2.2 during<br>UHF reception | 7                                                                                                      |                                                                                                                                                     |

| 21         | UOSCE1 | 2.0 during<br>VHF reception<br>1.5 during<br>UHF reception | 22                                                                                                     | External resonance circuit                                                                                                                          |

| 22         | UOSCE2 | 2.0 during<br>VHF reception<br>1.5 during<br>UHF reception | 20<br>3k<br>3k<br>3k                                                                                   | connection for UHF oscillator.                                                                                                                      |

| 23         | UOSCB2 | 2.4 during<br>VHF reception<br>2.2 during<br>UHF reception | mmmm                                                                                                   |                                                                                                                                                     |

| 24         | GND2   | _                                                          |                                                                                                        | PLL circuit GND.                                                                                                                                    |

| 25         | VT     | _                                                          | (26)<br>(25)                                                                                           | Varicap drive voltage output. This pin outputs the signal in open collector format, and it must be connected to the tuning power supply via a load. |

| 26         | СРО    | 2.0                                                        |                                                                                                        | Charge pump output. Connects the loop filter.                                                                                                       |

| Pin<br>No. | Symbol | Pin voltage<br>[V]  | Equivalent circuit | Description                                       |

|------------|--------|---------------------|--------------------|---------------------------------------------------|

| 27         | REFOSC | 4.4                 | 27 25p 38p         | Crystal connection for reference oscillator.      |

| 29         | ADSW   | 1.25<br>(when open) | 7                  | Address selection. Controls address bits 1 and 2. |

| 30         | IFOUT  | 2.8                 | 30                 | IF output.                                        |

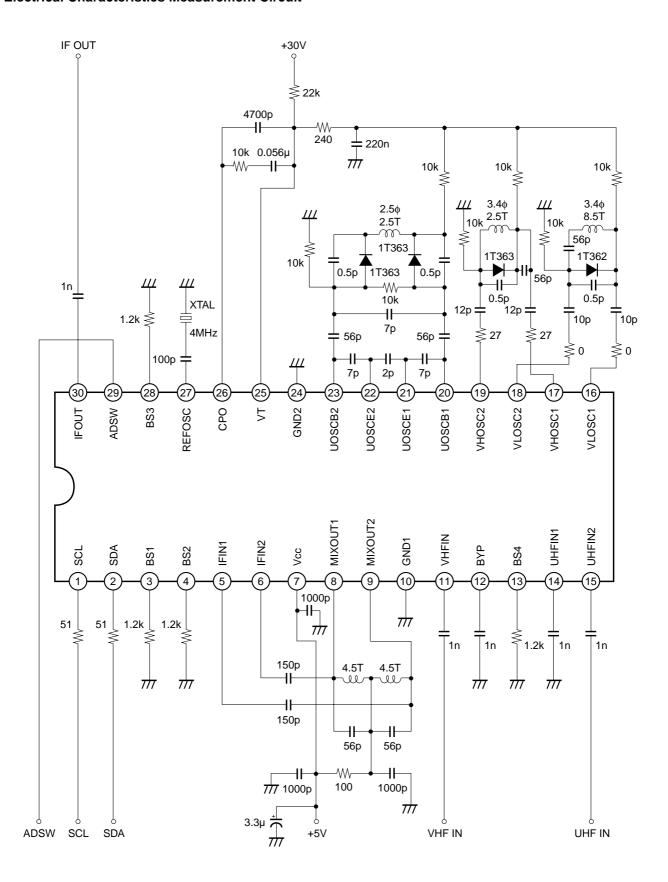

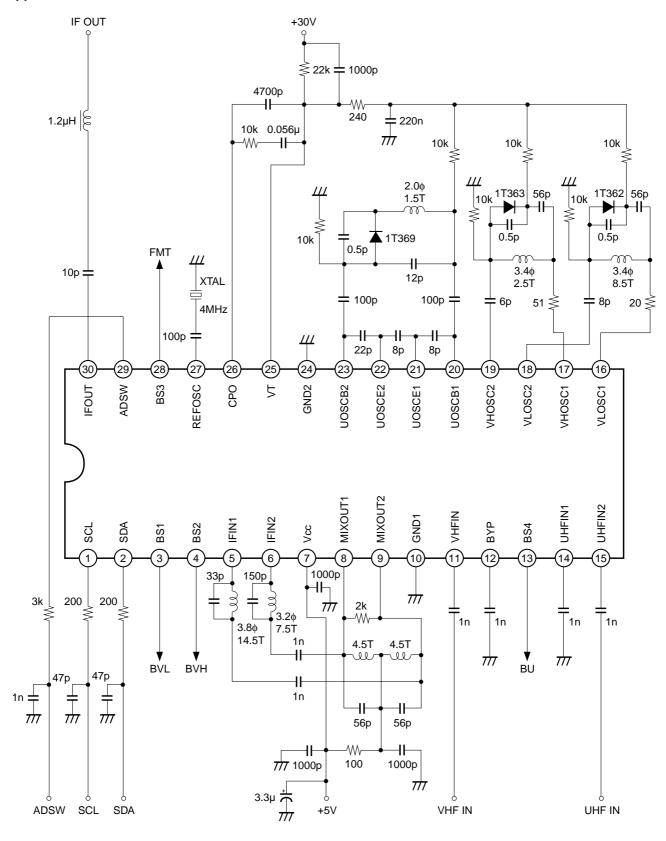

## **Electrical Characteristics (See the Electrical Characteristics Measurement Circuit.)**

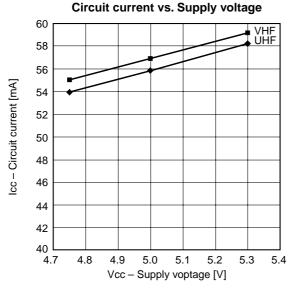

### **Circuit Current**

$(Vcc = 5V, IFVcc = 5V, Ta = 25^{\circ}C)$

| Item            | Symbol | Measurement conditions                                      |    | Тур. | Max. | Unit |

|-----------------|--------|-------------------------------------------------------------|----|------|------|------|

| a: :            | Iccv   | Vcc current<br>Band switch output open during VHF operation | 35 | 56   | 78   | mA   |

| Circuit current | Iccu   | Vcc current<br>Band switch output open during UHF operation | 35 | 56   | 78   | mA   |

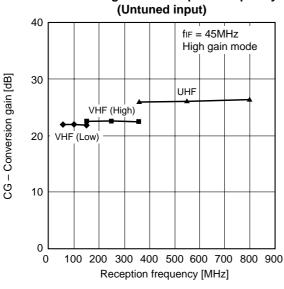

## **OSC/MIX/IF Amplifier Block**

| Item                 | Symbol | Measurement conditions                                            | Min. | Тур. | Max. | Unit |

|----------------------|--------|-------------------------------------------------------------------|------|------|------|------|

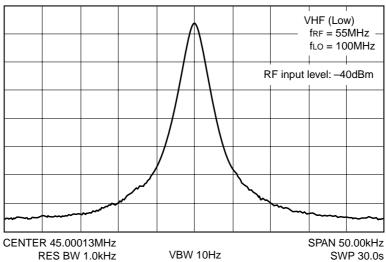

|                      | CG1    | VHF operation fRF = 55MHz High gain mode                          | 19.0 | 22.0 | 25.0 | dB   |

| -                    | CG2    | VHF operation fRF = 360MHz High gain mode                         | 19.5 | 22.5 | 25.5 | dB   |

|                      | CG3    | UHF operation fre = 360MHz High gain mode                         | 23.0 | 26.0 | 29.0 | dB   |

| Conversion gain*1    | CG4    | UHF operation fre = 800MHz High gain mode                         | 23.0 | 26.0 | 29.0 | dB   |

| Conversion gain**    | CG5    | VHF operation fre = 55MHz Low gain mode                           | 17.0 | 20.0 | 23.0 | dB   |

|                      | CG6    | VHF operation fre = 360MHz Low gain mode                          | 17.5 | 20.5 | 23.5 | dB   |

|                      | CG7    | UHF operation fre = 360MHz Low gain mode                          | 21.0 | 24.0 | 27.0 | dB   |

|                      | CG8    | UHF operation fre = 800MHz Low gain mode                          | 21.0 | 24.0 | 27.0 | dB   |

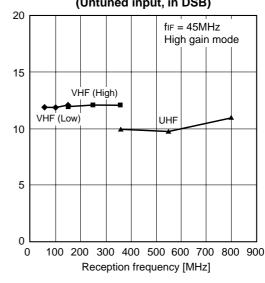

|                      | NF1    | VHF operation fre = 55MHz High gain mode                          |      | 12   | 15   | dB   |

|                      | NF2    | VHF operation fRF = 360MHz High gain mode                         |      | 12   | 15   | dB   |

|                      | NF3    | UHF operation fRF = 360MHz High gain mode                         |      | 10   | 13   | dB   |

| Noise figure*1, *2   | NF4    | UHF operation fref = 800MHz High gain mode                        |      | 11   | 14   | dB   |

| Noise ligure ', -    | NF5    | VHF operation fRF = 55MHz Low gain mode                           |      | 13   | 16   | dB   |

|                      | NF6    | VHF operation fre = 360MHz Low gain mode                          |      | 13   | 16   | dB   |

|                      | NF7    | UHF operation fRF = 360MHz Low gain mode                          |      | 11   | 14   | dB   |

|                      | NF8    | UHF operation fref = 800MHz Low gain mode                         |      | 12   | 15   | dB   |

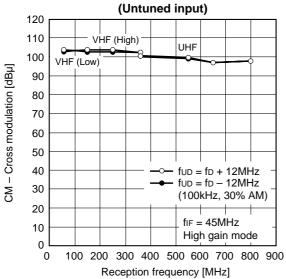

|                      | CM1    | VHF operation fD = 55MHz fUD = ±12MHz (30% AM) High gain mode     | 99   | 103  |      | dΒμ  |

|                      | CM2    | VHF operation fp = 360MHz<br>fup = ±12MHz (30% AM) High gain mode | 99   | 103  |      | dΒμ  |

|                      | СМЗ    | UHF operation fd = 360MHz<br>fud = ±12MHz (30% AM) High gain mode | 97   | 101  |      | dΒμ  |

| 1% cross             | CM4    | UHF operation fD = 800MHz<br>fUD = ±12MHz (30% AM) High gain mode | 94   | 98   |      | dΒμ  |

| modulation 1*1, *3   | CM5    | VHF operation fd = 55MHz<br>fud = ±12MHz (30% AM) Low gain mode   | 100  | 104  |      | dΒμ  |

|                      | CM6    | VHF operation fD = 360MHz<br>fUD = ±12MHz (30% AM) Low gain mode  | 100  | 104  |      | dΒμ  |

|                      | CM7    | UHF operation fd = 360MHz<br>fud = ±12 MHz (30% AM) Low gain mode | 98   | 102  |      | dΒμ  |

|                      | CM8    | UHF operation fd = 800MHz<br>fud = ±12 MHz (30% AM) Low gain mode | 94   | 98   |      | dΒμ  |

| Maximum output power | Pomax  | 50Ω load, saturation output                                       | 8    | 11   |      | dBm  |

| Item                        | Symbol | Measurement conditions                                                     | Min. | Тур. | Max. | Unit   |

|-----------------------------|--------|----------------------------------------------------------------------------|------|------|------|--------|

|                             | ∆fsw1  | VHF operation fosc = 100MHz<br>Δf from 3s to 3min after switch ON          |      |      | ±300 | kHz    |

| Switch ON drift<br>(PLL not | ∆fsw2  | VHF operation fosc = 405MHz<br>Δf from 3s to 3min after switch ON          |      |      | ±600 | kHz    |

| operating) *4               | ∆fsw3  | UHF operation fosc = 405MHz<br>Δf from 3s to 3min after switch ON          |      |      | ±350 | kHz    |

|                             | ∆fsw4  | UHF operation fosc = 845MHz<br>Δf from 3s to 3min after switch ON          |      |      | ±400 | kHz    |

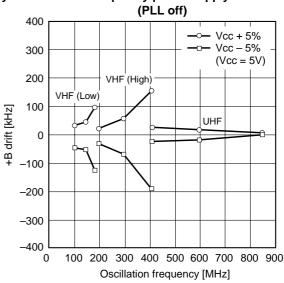

|                             | ∆fst1  | VHF operation fosc = 100MHz<br>Δf when Vcc 5V changes ±5%                  |      |      | ±100 | kHz    |

| Supply voltage drift        | ∆fst2  | VHF operation fosc = 405MHz<br>Δf when Vcc 5V changes ±5%                  |      |      | ±450 | kHz    |

| (PLL not operating) *4      | ∆fst3  | UHF operation fosc = 405MHz<br>Δf when Vcc 5V changes ±5%                  |      |      | ±100 | kHz    |

|                             | ∆fst4  | UHF operation fosc = 845MHz<br>Δf when Vcc 5V changes ±5%                  |      |      | ±100 | kHz    |

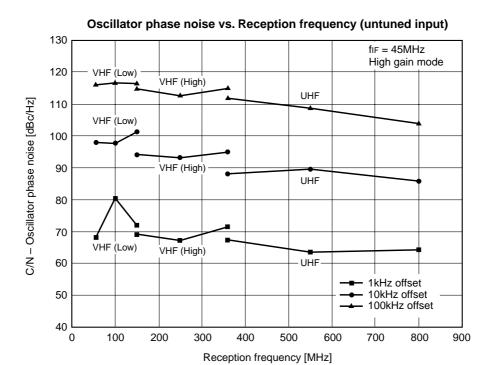

| Oscillator phase            | C/N1   | VHF operation 10kHz offset CP = 1<br>Phase comparison frequency = 31.25kHz | 86   |      |      | dBc/Hz |

| noise                       | C/N2   | UHF operation 10kHz offset CP = 1<br>Phase comparison frequency = 31.25kHz | 80   |      |      | dBc/Hz |

<sup>\*1</sup> Value measured with untuned input.

$<sup>\</sup>ensuremath{^{*2}}$  NF meter direct-reading value (DSB measurement).

<sup>\*3</sup> Value with a desired reception signal input level of –30dBm, an interference signal of 100kHz/30% AM, and an interference signal level where S/I = 46dB measured with a spectrum analyzer.

<sup>\*4</sup> Value when the PLL is not operating.

## **PLL Block**

| Item                        | Symbol  | Measurement conditions                                              | Min. | Тур. | Max.       | Unit |

|-----------------------------|---------|---------------------------------------------------------------------|------|------|------------|------|

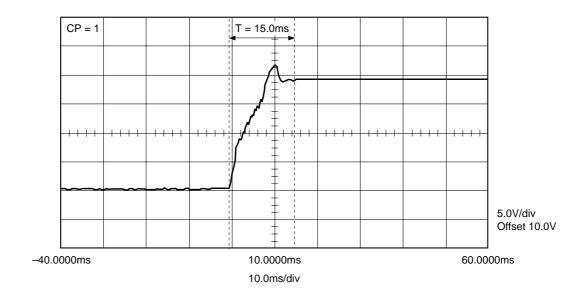

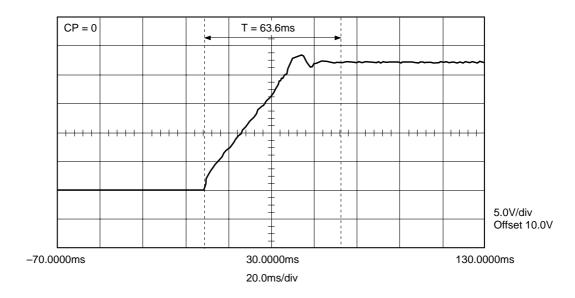

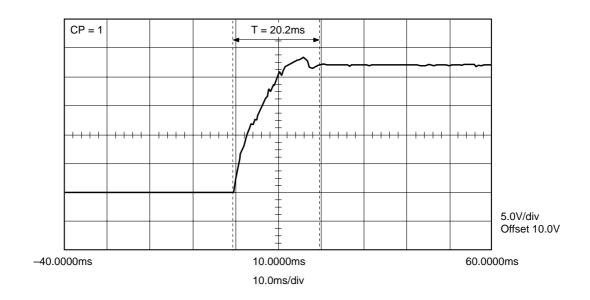

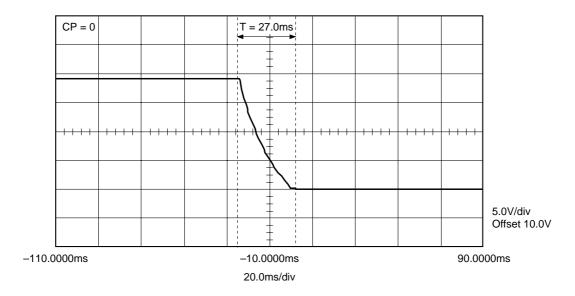

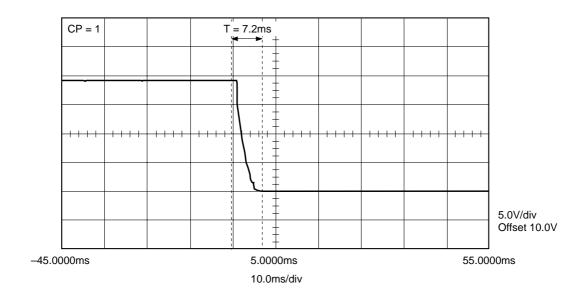

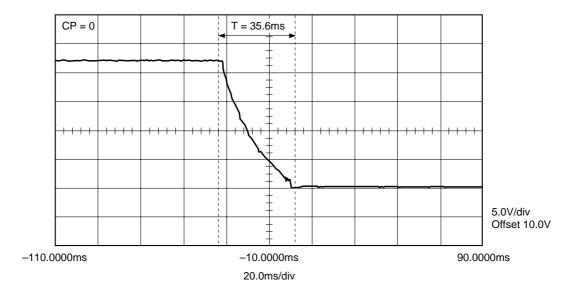

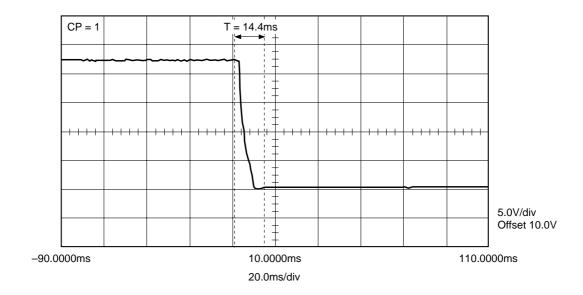

| Lock up timo                | LUT1    | VHF operation $CP = 1$<br>fosc 100MHz $\leftrightarrow$ fosc 405MHz |      |      | 50         | ms   |

| Lock-up time                | LUT2    | UHF operation CP = 1 fosc 405MHz ↔ fosc 845MHz                      |      |      | 50         | ms   |

| Reference leak              | REFL    | Phase comparison frequency<br>= 31.25kHz CP = 1                     | 54   |      |            | dBc  |

| CL and DA inputs            |         |                                                                     |      |      |            |      |

| "H" level input voltage     | ViH     |                                                                     | 3    |      | Vcc        | V    |

| "L" level input voltage     | VIL     |                                                                     | GND  |      | 1.5        | V    |

| "H" level input current     | Іін     | VIH = VCC                                                           |      | 0    | -0.1       | μA   |

| "L" level input current     | lı∟     | VIL = GND                                                           |      | -0.2 | -4         | μA   |

| AD input                    | 1       |                                                                     |      |      | '          |      |

| "H" level input voltage     | VIH     |                                                                     | 3    |      | Vcc        | V    |

| "L" level input voltage     | VIL     |                                                                     | GND  |      | 1          | V    |

| "H" level input current     | Іін     | VIH = VCC                                                           |      | 100  | 200        | μA   |

| "L" level input current     | lıL     | VIL = GND                                                           |      | -35  | -100       | μA   |

| SDA output                  |         |                                                                     |      |      |            |      |

| "H" output leak current     | ISDALK  | VIN = 5.5V                                                          |      |      | 5          | μA   |

| "L" output voltage          | VSDAL   | Sink = -3mA                                                         | GND  |      | 0.4        | V    |

| CPO (charge pump)           |         |                                                                     |      |      |            |      |

| Output current 1            | ICPO1   | When CP = 0 is selected                                             | ±30  | ±50  | ±80        | μA   |

| Leak current 1              | LeakCP1 | When CP = 0 is selected                                             |      |      | 30         | nA   |

| Output current 2            | ICPO2   | When CP = 1 is selected                                             | ±120 | ±200 | ±320       | μA   |

| Leak current 2              | LeakCP2 | When CP = 1 is selected                                             |      |      | 100        | nA   |

| VT (VC voltage output)      |         |                                                                     |      |      |            |      |

| Maximum output voltage      | Vтн     |                                                                     |      |      | 34         | V    |

| Minimum output voltage      | VTL     | Sink current = 1mA                                                  |      | 0.15 | 0.8        | V    |

| REFOSC                      |         |                                                                     |      |      |            |      |

| Oscillation frequency range | Fxтоsc  |                                                                     | 3    |      | 12         | MHz  |

| Input capacitance           | Схтоѕс  |                                                                     | 22   | 24   | 26         | pF   |

| Negative resistance         | RNEG    | Crystal source impedance fREF = 4MHz                                | -1   | -3   |            | kΩ   |

| Band SW                     | •       |                                                                     |      | •    |            |      |

| Output current              | IBS     | When ON                                                             |      |      | <b>-</b> 5 | mA   |

| Saturation voltage          | Vsat    | When ON Source current = 5mA                                        |      | 100  | 300        | mV   |

| Leak current                | LeakBS  | When OFF IFVcc = 5.5V                                               |      | 0.5  | 3          | μA   |

| Item                              | Symbol         | Measurement conditions | Min. | Тур. | Max. | Unit |

|-----------------------------------|----------------|------------------------|------|------|------|------|

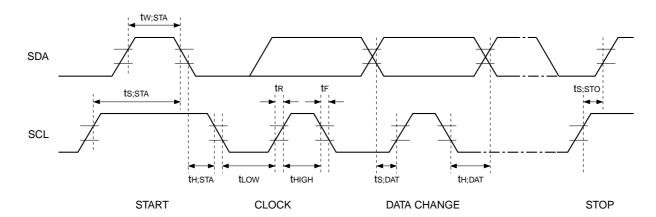

| Bus timing (I <sup>2</sup> C bus) | •              |                        | •    | •    |      |      |

| SCL clock frequency               | fscL           |                        | 0    |      | 400  | kHz  |

| Start waiting time                | tw;sta         |                        | 1300 |      |      | ns   |

| Start hold time                   | <b>t</b> H;STA |                        | 600  |      |      | ns   |

| Low hold time                     | tLOW           |                        | 1300 |      |      | ns   |

| High hold time                    | <b>t</b> HIGH  |                        | 600  |      |      | ns   |

| Start setup time                  | ts;sta         |                        | 600  |      |      | ns   |

| Data hold time                    | <b>t</b> H;DAT |                        | 0    |      | 900  | ns   |

| Data setup time                   | ts;dat         |                        | 600  |      |      | ns   |

| Rise time                         | <b>t</b> R     |                        |      |      | 300  | ns   |

| Fall time                         | tғ             |                        |      |      | 300  | ns   |

| Stop setup time                   | <b>t</b> s;sto |                        | 600  |      |      | ns   |

#### **Electrical Characteristics Measurement Circuit**

#### **Application Circuit**

Application circuits shown are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits or for any infringement of third party patent and other right due to same.

#### **Description of Functions**

The CXA3555N is an analog terrestrial TV broadcasting tuner IC which converts frequencies to IF in order to tune and detect only the desired reception frequency of VHF and UHF band signals.

In addition to the mixer, local oscillation and IF amplifier circuits required for frequency conversion to IF, this IC also integrates a PLL circuit for local oscillation frequency control onto a single chip.

The functions of the various circuits are described below.

#### 1. Mixer circuit

This circuit outputs the frequency difference between the signal input to VHFIN or UHFIN and the local oscillation signal.

#### 2. Local oscillation circuit

A VCO is formed by externally connecting an LC resonance circuit composed of a varicap diode and inductance.

#### 3. IF amplifier circuit

This circuit amplifies the mixer IF output, and consists of an amplifier stage and low impedance output stage.

#### 4. PLL circuit

This PLL circuit fixes the local oscillation frequency to the desired frequency. It consists of a programmable divider, reference divider, phase comparator, charge pump and reference oscillator. The control format supports the I<sup>2</sup>C bus format.

The frequency steps of 31.25, 50 or 62.5kHz can be selected by the I<sup>2</sup>C bus data-based reference divider frequency division setting value.

#### 5. Band switch circuit

The CXA3555N has four sets of built-in PNP transistors for switching between the VL, VH and UHF bands and for switching the FM trap, etc. These PNP transistors can be controlled by the bus data.

The emitters for these PNP transistors are connected to the power supply pin (Vcc), and are ON and output 5V when the bus data is "1 (H)".

#### Description of Analog Block Operation (See the Electrical Characteristics Measurement Circuit.)

#### VHF-Low oscillator circuit

This is a completely balanced oscillator circuit. The oscillation frequency is varied by connecting an LC parallel resonance circuit including a varicap between Pins 16 and 18 via coupled capacitance and controlling the voltage applied to the varicap.

#### VHF-High oscillator circuit

This is a completely balanced oscillator circuit. The oscillation frequency is varied by connecting an LC parallel resonance circuit including a varicap between Pins 17 and 19 via coupled capacitance and controlling the voltage applied to the varicap.

#### VHF mixer circuit

- The mixer circuit employs a double balanced mixer with little local oscillation signal leakage.

- The input format is base input type, with Pin 12 grounded either directly or via a capacitor and the RF signal input to Pin 11.

- (Pin 12 can also be used to switch the IC gain according to the applied DC voltage value. When switching the gain with Pin 12, the GC bit of the PLL data must be set to "0".)

- The RF signal is fed from the oscillator, converted to IF frequency and output from Pins 8 and 9. Pins 8 and 9 are open collectors, so external power feed is necessary. Also, connect single-tuned filters to Pins 8 and 9.

#### **UHF** oscillator circuit

- The oscillator circuit is designed so that two collector ground type Colpitts oscillators perform differential oscillation operation via an LC resonance circuit including a varicap.

- Resonance capacitance is connected between Pins 20 and 21, Pins 21 and 22, and Pins 22 and 23, and an LC resonance circuit including a varicap is connected between Pins 20 and 23.

#### **UHF** mixer circuit

- This circuit employs a double balanced mixer like the VHF mixer circuit.

- The input format is base input type, with Pins 14 and 15 as the RF input pins. The input method can be selected from balanced input consisting of differential input to Pins 14 and 15 or unbalanced input consisting of grounding Pin 14 via a capacitor and input to Pin 15.

- Pins 8 and 9 are the mixer outputs. Pins 8 and 9 are open collectors, so external power feed is necessary. Also, connect single-tuned filters to Pins 8 and 9.

#### IF amplifier circuit

- Pins 5 and 6 are the IF amplifier inputs, and the input impedance is approximately 1.6kΩ.

- The signals frequency converted by the mixer are output from Pins 8 and 9, and Pins 8 and 9 are connected to Pins 5 and 6 via capacitors. (An adjacent channel trap circuit can be formed by connecting LC parallel circuits in place of capacitors.)

- The signal amplified by the IF amplifier is output from Pin 30. The output impedance is approximately  $10\Omega$ .

#### **Description of PLL Block**

This IC is controlled by the I<sup>2</sup>C bus.

The PLL of this IC performs high-speed phase comparison, providing low reference leak and quick lock-up time characteristics.

During power on, the power-on reset circuit operates to initialize the frequency data to all "0" and the band data to all "OFF". Power-on reset is performed when  $Vcc \ge 3.2V$  at room temperature (Ta = 25°C).

#### 1) Address setting

Up to four addresses can be selected by the hardware bit settings, so that multiple PLL can exist within one system.

The responding address can be set according to the ADSW pin voltage.

#### **Address**

| 1 | 1 | 0 | 0 | 0 | MA1 | MA0 | R/W |

|---|---|---|---|---|-----|-----|-----|

|   |   | l |   |   |     |     |     |

#### Hardware bits

| ADSW pin voltage         | MA1 | MA0 |

|--------------------------|-----|-----|

| 0 to 0.1Vcc              | 0   | 0   |

| OPEN or 0.2Vcc to 0.3Vcc | 0   | 1   |

| 0.4Vcc to 0.6Vcc         | 1   | 0   |

| 0.9Vcc to Vcc            | 1   | 1   |

#### 2) Frequency data setting

The VCO lock frequency is obtained according to the following formula.

$fosc = 2 \times fref \times (32M + S)$

fosc: local oscillator frequency

fref: phase comparison frequency

M: main divider frequency division ratio

S: swallow counter frequency division ratio

The variable frequency division ranges of M and S are as follows, and are set as binary.

$S < M \le 1023$

$0 \le S \le 31$

#### 3) Control format

When performing control for this IC, byte 1 contains the address data, bytes 2 and 3 contain the frequency data, byte 4 contains the control data, and byte 5 contains the band switch data.

These data are latch transferred in the manner of byte 1, byte 2 + byte 3, and byte 4 + byte 5.

When the correct address is received and acknowledged, the data is recognized as frequency data if the first bit of the next byte is "0", and as control data and band switch data if this bit is "1".

Also, when data transmission is stopped part-way, the previously programmed data is valid. Therefore, once the control and band switch data have been programmed, 3-byte commands consisting of the address and frequency data are possible.

Further, even if the I<sup>2</sup>C bus stop conditions are not met, data can be input by sending the start conditions and the new address.

The control format is as shown in the table below.

#### Slave Receiver

|               | MSB   |       |       |       |       |       |       | LSB   |   |

|---------------|-------|-------|-------|-------|-------|-------|-------|-------|---|

| Mode          | bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 |   |

| Address byte  | 1     | 1     | 0     | 0     | 0     | MA1   | MA0   | 0     | А |

| Divider byte1 | 0     | M9    | M8    | M7    | M6    | M5    | M4    | МЗ    | Α |

| Divider byte2 | M2    | M1    | MO    | S4    | S3    | S2    | S1    | S0    | Α |

| Control byte  | 1     | CP    | GC    | CD    | Х     | R1    | R0    | os    | Α |

| Band SW byte  | Х     | Х     | Х     | Х     | BS4   | BS3   | BS2   | BS1   | Α |

X: Don't care

A: Acknowledge bit MA0, MA1: address setting

M0 to: main divider frequency division ratio setting S0 to: swallow counter frequency division ratio setting

CD: charge pump OFF (when "1") OS: varicap output OFF (when "1")

CP: charge pump current switching (200µA when "1", 50µA when "0")

GC: gain switching (IC gain reduced by 2dB when "1") \*1 BS1 to BS4: band switch control (output PNP transistor ON when "1")

reference divider frequency division ratio setting (See the Reference Divider Frequency Division R0, R1: Ratio Table.)

#### **Reference Divider Frequency Division Ratio Table**

| R1 | R0 | Reference Divider |

|----|----|-------------------|

| 0  | 1  | 256               |

| 1  | 1  | 128               |

| Х  | 0  | 160               |

X: Don't care

<sup>\*1</sup> When switching the gain with the PLL data, ground Pin 12 (BYP) via a capacitor.

## I<sup>2</sup>C Bus Timing Chart

ts;sta = Start setup timetw;sta = Start waiting time

th;sta = Start hold time tLOW = Low clock pulse width tHIGH = High clock pulse width ts;DAT = Data setup time th;DAT = Data hold time

ts;sto = Stop setup time

tκ

= Rise time = Fall time

#### **Example of Representative Characteristics**

#### Band SW output voltage vs. Output current (BS1, BS2, BS3, BS4)

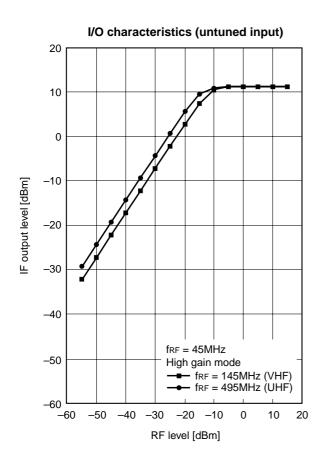

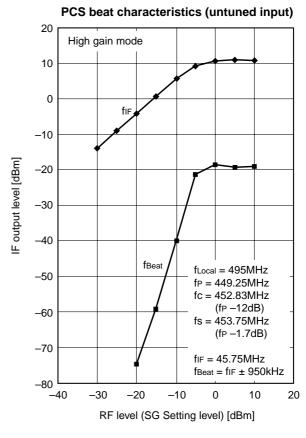

#### Conversion gain vs. Reception frequency (Untuned input)

Noise figure vs. Reception frequency (Untuned input, in DSB)

## Next adjacent cross modulation vs. Reception frequency

## Oscillation frequency power supply fluctuation

NF – Noise figure [dB]

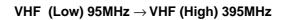

## **Tuning Response Time**

### UHF 413MHz $\rightarrow$ UHF 847MHz

## VHF (High) 395MHz $\rightarrow$ VHF (Low) 95MHz

### UHF 847MHz $\rightarrow$ UHF 413MHz

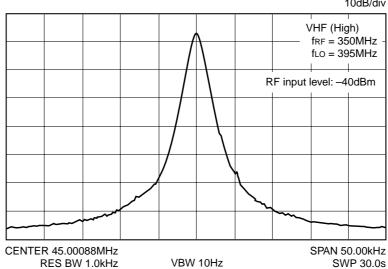

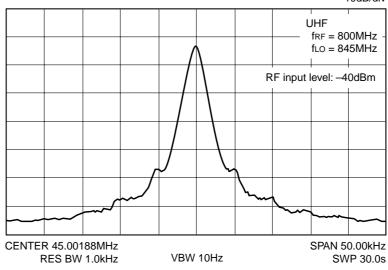

#### IF output spectrum

REF = -10.0dBm10dB/div

REF = -0.0dBm10dB/div

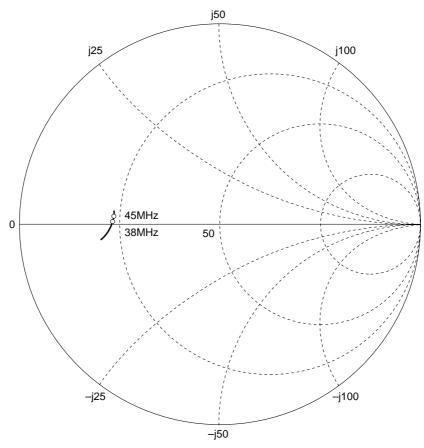

## **VHF Input Impedance**

## **UHF Input Impedance**

## **IF Output Impedance**

### Package Outline Unit: mm

**EIAJ CODE**

JEDEC CODE

P-SSOP30-5.6x9.7-0.65