# 2-Channel TRIAC Dimmable LED Driver IC

# **Features**

- · Best-in-class Dimmer Compatibility

- Leading-edge (TRIAC) Dimmers

- Trailing-edge Dimmers

- Digital Dimmers (with Integrated Power Supply)

- Correlated Color Temperature (CCT) Control System

- Up to 85% Efficiency

- · Flicker-free Dimming

- · Programmable Dimming Profile

- Constant CCT Dimming

- Black Body Line Dimming

- 0% Minimum Dimming Level

- Temperature Compensated LED Current

- End-of-line Programming Using Power Line Calibration - Lower LED Binning Requirement

- Programmable Series or Parallel 2-Channel Output

- Interleaved Output Eliminates Additional Transformer

- Programmable Quasi-resonant Second Stage with Constant-current Output

Flvback, Buck, and Tapped Buck

- Flyback, Buck, and Tapped E

Register Lockout

- Fast Startup

- Tight LED Current Regulation: Better than ±5%

- Primary-side Regulation (PSR)

- >0.9 Power Factor

- IEC-61000-3-2 Compliant

- Soft Start

- Protections:

- Output Open/Short

- Current-sense Resistor Open/Short

- External Overtemperature Using NTC

# **Overview**

The CS1630 and CS1631 are high-performance offline AC/DC LED drivers for dimmable and high color rendering index (CRI) LED replacement lamps and luminaires. It features Cirrus Logic's proprietary digital dimmer compatibility control technology and digital correlated color temperature (CCT) control system that enables two-channel LED color mixing. The CS1630 is designed for 120VAC line voltage applications, and the CS1631 is optimized for 230VAC line voltage applications.

The CS1630/31 integrates a critical conduction mode boost converter, providing power factor correction and superior dimmer compatibility with a primary-side regulated quasi-resonant second stage, which is configurable for isolated and non-isolated topologies. The digital CCT control system provides the ability to program dimming profiles, such as constant CCT dimming and black body line dimming. The CS1630/31 optimizes LED color mixing by temperature compensating LED current with an external NTC. The IC controller is also equipped with power line calibration for remote system calibration and end-of-line programming. The CS1630/31 provides a register lockout feature for security against potential access to proprietary registers.

# Applications

- · Dimmable Retrofit LED Lamps and LED Luminaries

- High CRI Lighting

- Offline LED Drivers

See page 53.

Commercial Lighting

# **Ordering Information**

Preliminary Product Information This document contains Cirrus Logic reserves th

This document contains information for a product under development. Cirrus Logic reserves the right to modify this product without notice.

Cirrus Logic, Inc. http://www.cirrus.com

Copyright © Cirrus Logic, Inc. 2012 (All Rights Reserved)

# 1. INTRODUCTION

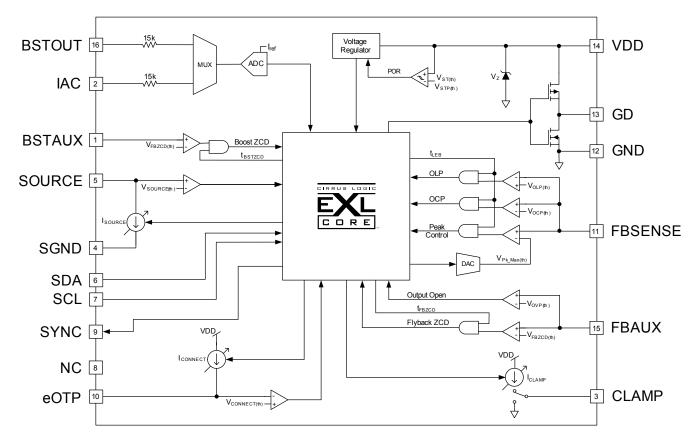

Figure 1. CS1630/31 Block Diagram

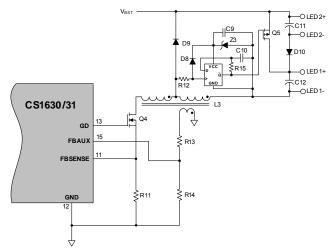

A typical schematic using the CS1630/31 IC is shown on the previous page.

Startup current is provided from a patent-pending, external high-voltage source-follower network. In addition to providing startup current, this unique topology is integral in providing compatibility with digital dimmers by ensuring VDD power is always available to the IC. During steady-state operation, an auxiliary winding on the boost inductor back-biases the source-follower circuit and provides steady-state operating current to the IC to improve system efficiency.

The rectified input voltage is sensed as a current into pin IAC and is used to control the adaptive dimmer compatibility algorithm and extract the phase of the input voltage for output dimming control. During steady-state operation, the external high-voltage, source-follower circuit is source-switched in critical conduction mode (CRM) to boost the input voltage. This allows the boost stage to maintain good power factor, provide dimmer compatibility, reduce bulk capacitor ripple current, and provide a regulated input voltage to the second stage.

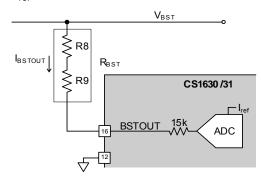

The current into the boost output voltage sense pin (BSTOUT) senses the output voltage of the CRM boost front-end.

The quasi-resonant second stage is implemented with peakcurrent mode primary-side control, which eliminates the need for additional components to provide feedback from the secondary and reduces system cost and complexity.

Voltage across an external user-selected resistor is sensed through pin FBSENSE to control the peak current through the second stage inductor. Leading-edge and trailing-edge blanking on pin FBSENSE prevents false triggering.

Pin FBAUX is used to sense the second stage inductor demagnetization to ensure quasi-resonant switching of the output stage.

An internal current source is adjusted by a feedback loop to regulate a constant reference voltage on pin eOTP for external negative temperature coefficient (NTC) thermistor measurements. An external NTC is connected to pin eOTP to provide thermal protection of the system and LED temperature compensation. The output current of the system is steadily reduced when the system temperature exceeds a programmable temperature set point. If the temperature reaches a designated high set point, the IC is shutdown and stops switching.

# 2. PIN DESCRIPTION

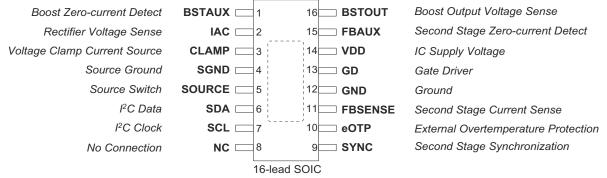

### Figure 2. CS1630/31 Pin Assignments

| Pin Name | Pin # | I/O | Description                                                                                                                                                                                                                                         |

|----------|-------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BSTAUX   | 1     | IN  | <b>Boost Zero-current Detect</b> — Boost Inductor demagnetization sensing input for zero-current detection (ZCD) information. The pin is connected to the PFC boost inductor auxiliary winding through an external resistor divider.                |

| IAC      | 2     | IN  | <b>Rectifier Voltage Sense</b> — A current proportional to the rectified line voltage is fed into this pin. The current is measured with an A/D converter.                                                                                          |

| CLAMP    | 3     | OUT | Voltage Clamp Current Source — Connect to a voltage clamp circuit on the output of the boost stage.                                                                                                                                                 |

| SGND     | 4     | PWR | Source Ground — Common reference current return for the SOURCE pin.                                                                                                                                                                                 |

| SOURCE   | 5     | IN  | <b>Source Switch</b> — Connected to the source of the boost stage external high-voltage FET.                                                                                                                                                        |

| SDA      | 6     | I/O | I <sup>2</sup> C™ Data — I <sup>2</sup> C data.                                                                                                                                                                                                     |

| SCL      | 7     | IN  | $I^2C^{TM}$ Clock — $I^2C$ clock.                                                                                                                                                                                                                   |

| NC       | 8     | -   | No Connection — Leave pin unconnected.                                                                                                                                                                                                              |

| SYNC     | 9     | OUT | <b>Second Stage Synchronization</b> — A digital synchronization signal that indicates which channel the controller is signaling for each gate switching period.                                                                                     |

| eOTP     | 10    | IN  | <b>External Overtemperature Protection</b> — Connect an external NTC thermistor to this pin, allowing the internal A/D converter to sample the change to NTC resistance.                                                                            |

| FBSENSE  | 11    | IN  | Second Stage Current Sense — The current flowing in the second stage FET is sensed across a resistor. The resulting voltage is applied to this pin and digitized for use by the second stage computational logic to determine the FET's duty cycle. |

| GND      | 12    | PWR | <b>Ground</b> — Common reference. Current return for both the input signal portion of the IC and the gate driver.                                                                                                                                   |

| GD       | 13    | OUT | Gate Driver — Gate drive for the second stage power FET.                                                                                                                                                                                            |

| VDD      | 14    | PWR | IC Supply Voltage — Connect a storage capacitor to this pin to serve as a reservoir for operating current for the device, including the gate drive current to the power transistor.                                                                 |

| FBAUX    | 15    | IN  | <b>Second Stage Zero-current Detect</b> — Second stage inductor sensing input. The pin is connected to the second stage inductor's auxiliary winding through an external resistor divider.                                                          |

| BSTOUT   | 16    | IN  | <b>Boost Output Voltage Sense</b> — A current proportional to the boost output is fed into this pin. The current is measured with an A/D converter.                                                                                                 |

Minimum/Maximum characteristics conditions:

•  $T_J = -40$  °C to +125 °C,  $V_{DD} = 11$  V to 17 V, GND = 0 V

# 3. CHARACTERISTICS AND SPECIFICATIONS

# 3.1 Electrical Characteristics

Typical characteristics conditions:

- T<sub>A</sub> = 25° C, V<sub>DD</sub> = 12V, GND = 0V

All voltages are measured with respect to GND.

- Unless otherwise specified, all currents are positive when flowing into the IC.

| Parameter                                      |          | Condition                                                   | Symbol                  | Min    | Тур                  | Max    | Unit     |

|------------------------------------------------|----------|-------------------------------------------------------------|-------------------------|--------|----------------------|--------|----------|

| VDD Supply Voltage                             |          |                                                             |                         |        |                      |        |          |

| Operating Range                                |          | After Turn-on                                               | V <sub>DD</sub>         | 11     | -                    | 17     | V        |

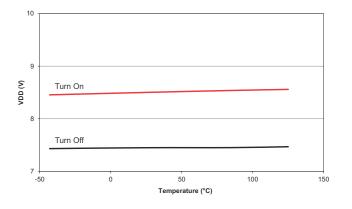

| Turn-on Threshold Voltage                      |          | V <sub>DD</sub> Increasing                                  | V <sub>ST(th)</sub>     | -      | 8.5                  | -      | V        |

| Turn-off Threshold Voltage (UVLO)              |          | V <sub>DD</sub> Decreasing                                  | V <sub>STP(th)</sub>    | -      | 7.5                  | -      | V        |

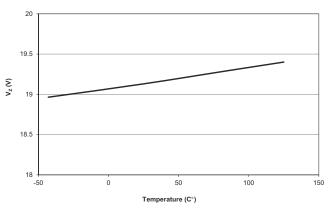

| Zener Voltage (No                              | ote 1)   | I <sub>DD</sub> = 20mA                                      | VZ                      | 18.5   | -                    | 19.8   | V        |

| VDD Supply Current                             |          |                                                             |                         |        |                      |        |          |

| Startup Supply Current                         |          | V <sub>DD</sub> <v<sub>ST(th)</v<sub>                       | I <sub>ST</sub>         | -      | -                    | 200    | μA       |

| Operating Supply Current (No                   | ote 5) C | C <sub>L</sub> = 0.25nF, f <sub>sw</sub> ≤60 kHz            |                         | -      | 5.8                  | -      | mA       |

| Reference                                      |          |                                                             |                         |        |                      |        |          |

| Reference Current<br>CS1630<br>CS1631<br>Boost |          | V <sub>BST</sub> = 200 V<br>V <sub>BST</sub> = 400 V        | I <sub>ref</sub>        | -      | 133<br>133           | -<br>- | μΑ<br>μΑ |

|                                                |          |                                                             | 5                       |        | _                    | 200    |          |

| Maximum Switching Frequency                    |          |                                                             | f <sub>BST(Max)</sub>   | -      |                      | 200    | kHz      |

| Clamp Current                                  |          |                                                             | ICLAMP                  | -      | -3.8                 | -      | mA       |

| Dimmer Attach Peak Current<br>CS1630<br>CS1631 |          | 108 ≤ V <sub>line</sub> ≤132<br>207≤ V <sub>line</sub> ≤253 |                         | -      | 590<br>508           | -<br>- | mA<br>mA |

| Boost Zero-current Detect                      |          |                                                             |                         |        | I                    |        |          |

| BSTZCD Threshold                               |          |                                                             | V <sub>BSTZCD(th)</sub> | -      | 200                  | -      | mV       |

| ZCD Sink Current (No                           | ote 2)   |                                                             | IBSTZCD                 | -2     | -                    | -      | mA       |

| BSTAUX Upper Voltage                           |          | I <sub>BSTZCD</sub> = 1mA                                   |                         | -      | V <sub>DD</sub> +0.6 | -      | V        |

| Boost Protection                               |          |                                                             |                         |        | •                    |        |          |

| Clamp Turn-on<br>CS1630<br>CS1631              |          | $108 \le V_{line} \le 132$<br>$207 \le V_{line} \le 253$    |                         | -<br>- | 146.7<br>141.7       | -<br>- | μΑ<br>μΑ |

| Second Stage Zero-current Detect               |          |                                                             |                         |        |                      |        |          |

| FBZCD Threshold                                |          |                                                             | V <sub>FBZCD(th)</sub>  | -      | 200                  | -      | mV       |

| ZCD Sink Current (No                           | ote 2)   |                                                             | I <sub>FBZCD</sub>      | -2     | -                    | -      | mA       |

| FBAUX Upper Voltage                            |          | I <sub>FBZCD</sub> = 1mA                                    |                         | -      | V <sub>DD</sub> +0.6 | -      | V        |

| Second Stage Current Sense                     |          |                                                             |                         |        |                      |        |          |

| Overcurrent Protection Threshold               |          |                                                             | V <sub>OCP(th)</sub>    | -      | 1.69                 | -      | V        |

| Sense Resistor Short Threshold                 |          |                                                             | V <sub>OLP(th)</sub>    | -      | 200                  | -      | mV       |

| Peak Control Threshold                         |          |                                                             | V <sub>Pk_Max(th)</sub> | -      | 1.4                  | -      | V        |

| Delay to Output                                |          |                                                             |                         | -      | -                    | 100    | ns       |

| Parameter                        |             | Condition               | Symbol                   | Min | Тур  | Max | Unit |

|----------------------------------|-------------|-------------------------|--------------------------|-----|------|-----|------|

| Second Stage Pulse Width Modu    | ilator      |                         |                          |     |      |     |      |

| Minimum Switching Frequency      |             |                         | t <sub>FB(Min)</sub>     | -   | 625  | -   | Hz   |

| Maximum Switching Frequency      |             |                         | t <sub>FB(Max)</sub>     | -   | 200  | -   | kHz  |

| Second Stage Gate Driver         |             |                         |                          |     | •    | •   | •    |

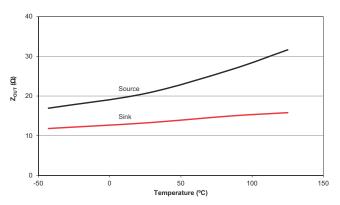

| Output Source Resistance         |             | V <sub>DD</sub> = 12V   |                          | -   | 24   | -   | Ω    |

| Output Sink Resistance           |             | V <sub>DD</sub> = 12V   |                          | -   | 11   | -   | Ω    |

| Rise Time                        | (Note 5)    | C <sub>L</sub> = 0.25nF |                          | -   | -    | 30  | ns   |

| Fall Time                        | (Note 5)    | C <sub>L</sub> = 0.25nF |                          | -   | -    | 20  | ns   |

| Second Stage Protection          | I           |                         |                          |     | 1    | 1   |      |

| Overcurrent Protection (OCP)     |             |                         | V <sub>OCP(th)</sub>     | -   | 1.69 | -   | V    |

| Overvoltage Protection (OVP)     |             |                         | V <sub>OVP(th)</sub>     | -   | 1.25 | -   | V    |

| Open Loop Protection (OLP)       |             |                         | V <sub>OLP(th)</sub>     | -   | 200  | -   | mV   |

| External Overtemperature Prote   | ction (eOTF | ?)                      |                          |     | 1    |     |      |

| Pull-up Current Source - Maximun | ı           |                         | I <sub>CONNECT</sub>     | -   | 80   | -   | μA   |

| Conductance Accuracy             | (Note 3)    |                         |                          | -   | -    | ±5  | %    |

| Conductance Offset               | (Note 3)    |                         |                          | -   | ±250 | -   | nS   |

| Current Source Voltage Threshold |             |                         | V <sub>CONNECT(th)</sub> | -   | 1.25 | -   | V    |

| Internal Overtemperature Protect | tion (iOTP) |                         |                          |     | 1    | 1   |      |

| Thermal Shutdown Threshold       | (Note 4)    |                         | T <sub>SD</sub>          | -   | 135  | -   | °C   |

| Thermal Shutdown Hysteresis      | (Note 4)    |                         | T <sub>SD(Hy)</sub>      | -   | 14   | -   | °C   |

Notes: 1. The CS1630/31 has an internal shunt regulator that limits the voltage on the VDD pin. V<sub>Z</sub>, the shunt regulation voltage, is defined in the VDD Supply Voltage section on page 4.

2. External circuitry should be designed to ensure that the ZCD current drawn from the internal clamp diode when it is forward biased does not exceed specification.

3. Conductance is the inverse of resistance  $(1/\Omega)$  and is expressed in siemens (S). A decrease in conductance is equivalent to an increase in resistance.

4. Specifications are guaranteed by design and are characterized and correlated using statistical process methods.

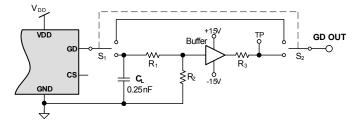

5. For test purposes, load capacitance (CL) is 0.25 nF and is connected as shown in the following diagram.

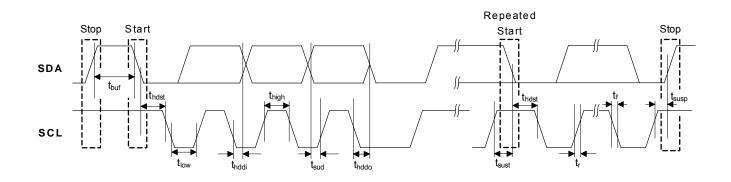

# 3.2 I<sup>2</sup>C Port Switching Characteristics

- Test conditions (unless otherwise specified): Inputs: Logic 0 = GND = 0V, Logic 1 = 3.3V.

- The CS1630/31 control port only supports I<sup>2</sup>C slave functionality.

- It is recommended that a  $2.2 k\Omega$  pull-up resistor be placed from the SDA pin to V<sub>DD</sub>.

| Parameter                                              | Symbol            | Min | Тур  | Max | Unit |

|--------------------------------------------------------|-------------------|-----|------|-----|------|

| SCL Clock Frequency                                    | f <sub>scl</sub>  | -   | -    | 400 | kHz  |

| Bus Free Time Between Transmissions                    | t <sub>buf</sub>  | 1.3 | -    | -   | μs   |

| Start Condition Hold Time (prior to first clock pulse) | t <sub>hdst</sub> | 0.6 | -    | -   | μs   |

| Clock Low time                                         | t <sub>low</sub>  | 1.3 | -    | -   | μs   |

| Clock High Time                                        | t <sub>high</sub> | 0.6 | -    | -   | μs   |

| Setup Time for Repeated Start Condition                | t <sub>sust</sub> | 0.6 | -    | -   | μs   |

| SDA Input Hold Time from SCL Falling                   | t <sub>hddi</sub> | 0   | -    | 0.9 | μs   |

| SDA Setup time to SCL Rising                           | t <sub>sud</sub>  | 100 | -    | -   | ns   |

| Setup Time for Stop Condition                          | t <sub>susp</sub> | 0.6 | -    | -   | μs   |

| SDA Input Voltage Low                                  | V <sub>il</sub>   | -   | 1.5  | -   | V    |

| SDA Input Voltage High                                 | V <sub>ih</sub>   | -   | 1.85 | -   | V    |

| SDA Output Voltage Low                                 | V <sub>ol</sub>   | -   | 0.25 | -   | V    |

# 3.3 Power Line Calibration Characteristics

Typical characteristics conditions:

- T<sub>A</sub> = 25°C, V<sub>DD</sub> = 12V, GND = 0V

All voltages are measured with respect to GND.

- Unless otherwise specified, all current is positive when flowing into the IC.

| Parameter                         | (Note 6) | Min        | Тур        | Мах        | Units   |

|-----------------------------------|----------|------------|------------|------------|---------|

| Input Line Frequency              | (Note 7) | 47         | 50/60      | 63         | Hz      |

| Input Voltage<br>CS1630<br>CS1631 | (Note 7) | 114<br>218 | 120<br>230 | 126<br>242 | V       |

| Dual-bit 00 ("00")                |          | 24         | 34         | 44         | Degrees |

| Dual-bit 01 ("01")                |          | 52         | 62         | 72         | Degrees |

| Dual-bit 10 ("10")                |          | 108        | 118        | 128        | Degrees |

| Dual-bit 11 ("11")                |          | 136        | 146        | 156        | Degrees |

| Special Character (SC)            |          | 80         | 90         | 100        | Degrees |

Notes: 6. The CS1630/31 supports leading-edge phase-cut waveforms only for power line calibration.

7. Range is recommended for power line calibration operation only.

Minimum/Maximum characteristics conditions:  $T_J = 25^{\circ} C$ ,  $V_{DD} = 11V$  to 17V, GND = 0V

# 3.4 Thermal Resistance

| Symbol        | Parameter                             |                            | Value    | Unit         |

|---------------|---------------------------------------|----------------------------|----------|--------------|

| $\theta_{JA}$ | Junction-to-Ambient Thermal Impedance | 2 Layer PCB<br>4 Layer PCB | 84<br>47 | °C/W<br>°C/W |

| $\theta_{JC}$ | Junction-to-Case Thermal Impedance    | 2 Layer PCB<br>4 Layer PCB | 39<br>31 | °C/W<br>°C/W |

# 3.5 Absolute Maximum Ratings

Characteristics conditions:

All voltages are measured with respect to GND.

| Pin                                 | Symbol              | Parameter                                                                   | Value                          | Unit   |

|-------------------------------------|---------------------|-----------------------------------------------------------------------------|--------------------------------|--------|

| 14                                  | V <sub>DD</sub>     | IC Supply Voltage                                                           | 18.5                           | V      |

| 1, 2, 5, 6, 7, 9,<br>10, 11, 15, 16 |                     | Analog Input Maximum Voltage                                                | -0.5 to (V <sub>DD</sub> +0.5) | V      |

| 1, 2, 6, 7, 9, 10,<br>11,15,16      |                     | Analog Input Maximum Current                                                | 5                              | mA     |

| 13                                  | $V_{GD}$            | Gate Drive Output Voltage                                                   | -0.3 to (V <sub>DD</sub> +0.3) | V      |

| 13                                  | I <sub>GD</sub>     | Gate Drive Output Current                                                   | -1.0 / +0.5                    | А      |

| 5                                   | I <sub>SOURCE</sub> | Current into Pin                                                            | 1.1                            | А      |

| 3                                   | I <sub>CLAMP</sub>  | Clamp Output Current                                                        | 5                              | mA     |

| -                                   | PD                  | Total Power Dissipation                                                     | 400                            | mW     |

| -                                   | Т <sub>Ј</sub>      | Junction Temperature Operating Range (Note 8)                               | -40 to +125                    | °C     |

| -                                   | T <sub>Stg</sub>    | Storage Temperature Range                                                   | -65 to +150                    | °C     |

| All Pins                            | ESD                 | Electrostatic Discharge Capability Human Body Model<br>Charged Device Model | 2000<br>500                    | V<br>V |

Notes: 8. Long-term operation at the maximum junction temperature will result in reduced product life. Derate internal power dissipation at the rate of 50mW/°C for variation over temperature.

### WARNING:

Operation at or beyond these limits may result in permanent damage to the device. Normal operation is not guaranteed at these extremes.

# 4. TYPICAL PERFORMANCE PLOTS

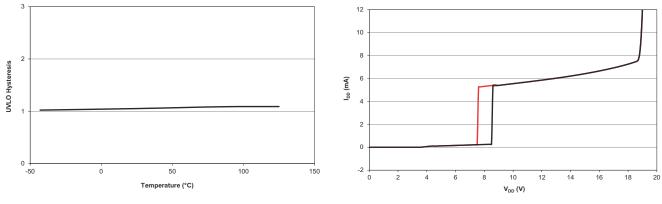

Figure 3. UVLO Characteristics

Figure 5. Turn-on/off Threshold Voltage vs. Temperature

Figure 7. Gate Drive Resistance vs. Temperature

Figure 4. Supply Current vs. Voltage

Figure 6. Zener Voltage vs. Temperature

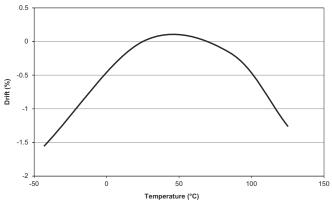

Figure 8. Reference Current (I<sub>ref</sub>) Drift vs. Temperature

# 5. GENERAL DESCRIPTION

# 5.1 Overview

The CS1630 and CS1631 are high-performance offline AC/DC LED drivers for dimmable and high color rendering index (CRI) LED replacement lamps and luminaires. It features Cirrus Logic's proprietary digital dimmer compatibility control technology and digital correlated color temperature (CCT) control system that enables two-channel LED color mixing. The CS1630 is designed for 120VAC line voltage applications, and the CS1631 is optimized for 230VAC line voltage applications.

The CS1630/31 integrates a critical conduction mode (CRM) boost converter, providing power factor correction and superior dimmer compatibility with a primary-side regulated quasi-resonant second stage, which is configurable for isolated and non-isolated topologies. The digital CCT control system provides the ability to program dimming profiles, such as constant CCT dimming and black body line dimming. The CS1630/31 optimizes LED color mixing by temperature compensating LED current with an external negative temperature coefficient (NTC) thermistor. The IC controller is also equipped with power line calibration for remote system calibration and end-of-line programming. The CS1630/31 provides a register lockout feature for security against potential access to proprietary registers.

# 5.2 Startup Circuit

An external, high-voltage source-follower circuit is used to deliver startup current to the IC. During steady-state operation, an auxiliary winding on the boost inductor biases this circuit to an off state to improve system efficiency, and all IC supply current is generated from the auxiliary winding. The patent pending technology of the external, high-voltage sourcefollower circuit enables system compatibility with digital dimmers (dimmers containing an internal power supply) by providing a continuous path for a dimmer's power supply to recharge during its off state. During steady-state operation, the high-voltage FET, Q1, is source-switched by a variable internal current source on the SOURCE pin to create the boost circuit. A Schottky diode with a forward voltage less than 0.6V is recommended for D5. Schottky diode D5 will limit inrush current through the internal diode, preventing damage to the IC.

# 5.3 Dimmer Switch Detection

The CS1630/31 dimmer switch detection algorithm determines if the SSL system is controlled by a regular switch, a leadingedge dimmer, or a trailing-edge dimmer. Dimmer switch detection is implemented using two modes: Dimmer Learn Mode and Dimmer Validate Mode. These assist in limiting the system power losses. Once the IC reaches its UVLO start threshold,  $V_{ST(th)}$ , and begins operating, the CS1630/31 is in Dimmer Learn Mode, allowing the dimmer switch detection circuit to set the operating state of the IC to one of three modes: No-dimmer Mode, Leading-edge Mode, or Trailing-edge Mode.

## 5.3.1 Dimmer Learn Mode

In Dimmer Learn Mode, the dimmer detection circuit spends approximately two line-cycles learning whether there is a dimmer switch and, if present, whether it is a trailing-edge or leading-edge dimmer. A modified version of the leading-edge algorithm is used. The trailing-side slope of the input line voltage is sensed to decide whether the dimmer switch is a trailing-edge dimmer. The dimmer detection circuit transitions to Dimmer Validate Mode once the circuit detects that a dimmer is present.

## 5.3.2 Dimmer Validate Mode

During normal operation, CS1630/31 is in Dimmer Validate Mode. This instructs the dimmer detection circuit to periodically validate that the IC is executing the correct algorithm for the attached dimmer. The dimmer detection algorithm periodically verifies the IC operating state as a protection against incorrect detection. As additional protection, the output of the dimmer detection algorithm is low-pass filtered to prevent noise or transient events from changing the IC's operating mode. The IC will return to Dimmer Learn Mode when it has determined that the wrong algorithm is being executed.

## 5.3.3 No-dimmer Mode

Upon detection that the line is not phase cut with a dimmer, the CS1630/31 operates in No-dimmer Mode, where it provides a power factor that is in excess of 0.9. The CS1630/31 accomplishes this by boosting in CRM and DCM mode. The peak current is modulated to provide link regulation. The CS1630/31 alternates between two settings of peak current. To regulate the boost output voltage, the CS1630/31 uses a peak current set by register PEAK\_CUR (see "Peak Current (PEAK\_CUR) – Address 51" on page 36). The time that this current is used is determined by an internal compensation loop to regulate the boost output voltage. The internal algorithm will reduce the peak current of the boost stage to maintain output voltage regulation and obtain the desired power factor.

# 5.3.4 Leading-edge Mode

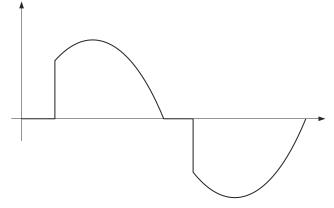

In Leading-edge Mode, the CS1630/31 regulates the boost output voltage (V<sub>BST</sub>) while maintaining the dimmer phase angle (see Figure 9). The device executes a CCM boost algorithm using dimmer attach current as the initial peak current for the initial firing event of the dimmer. Upon gaining control of the incoming current, the CS1630/31 transitions to a CRM boost algorithm to regulate the boost output voltage. The device periodically executes a probe event on the incoming waveform. The information from the probe event is used to maintain proper operation with the dimmer circuitry.

Figure 9. Leading-edge Mode Phase-cut Waveform

### 5.3.5 Trailing-edge Mode

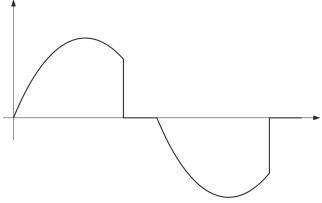

In Trailing-edge Mode, the CS1630/31 determines its operation based on the falling edge of the input voltage waveform (see Figure 10). To provide proper dimmer operation, the CS1630/31 executes the boost algorithm on the falling edge of the input line voltage that maintains a charge in the dimmer capacitor. To ensure maximum compatibility with dimmer components, the device boosts during this falling edge event using a peak current that must meet a minimum value. In Trailing-edge Mode, only the CRM boost algorithm is used.

Figure 10. Trailing-edge Mode Phase-cut Waveform

# 5.4 Correlated Color Temperature Control

The CS1630/31 color control system can adjust and maintain the correlated color temperature (CCT) for the LED color mixing application by connecting an external negative temperature coefficient (NTC) thermistor to the eOTP pin. The LED temperature variation can be accurately detected by the internal eOTP feedback loops (see "External Overtemperature Protection" on page 17).

Red and amber LEDs are necessary components in colormixing applications when providing warm white or other CCTs. When mixing colors, red and amber LEDs are the most temperature sensitive, so they cause a large variation in temperature. The CS1630/31 is capable of providing LED CCT and luminosity with temperature compensation using the NTC thermistor to resolve the significant change in the luminous output due to temperature variations.

Since LED lumens are mainly a function of temperature and forward current, color temperature and luminosity can be maintained by independently adjusting each string's output current as the ambient temperature changes. This can be done by mapping the NTC reading to a required value of the current in each string using a digital mapping block.

In the CS1630/31, only one of the LED string currents is compensated for due to temperature variations. The current in the other string is kept constant over temperature, which may result in the luminosity decreasing slightly as temperature increases. In order for the ADC to resolve the entire range of possible temperature variation in the LEDs, it is recommended to select a series resistor ( $R_S$ ) and an NTC ( $R_{NTC}$ ) with the appropriate Beta value, which retains the total resistance ( $R_S + R_{NTC}$ ) at all possible operating temperatures within the tracking range of the ADC. The final temperature to digital code mapping depends on these variables.

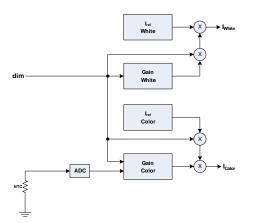

The CS1630/31 color control system also has the ability to maintain a constant CCT or change CCT as the light dims. OTP configurations allow the selection of the dimming profile. A specific CCT profile can be programmed to the digital mapping device. In this case, the mapping is two-dimensional: one current versus temperature profile is generated for each dim level. The CS1630/31 provides two-dimensional mapping for the color LED's current only, and one-dimensional mapping (current versus dim level) for the other string. A simplified block diagram of the color control system is shown in Figure 11.

Figure 11. Block Diagram of Color Control System

The reference currents are the required values at  $T_A = 25$  °C and dim = 100%. They are multiplied by the appropriate gains, and these values are passed to the final power stage. The CS1630/31 uses polynomial approximations in one and two dimensions to generate the color gains. These polynomials can be up to third-order.

GAIN<sub>DTR</sub> approximations create a custom temperature compensation profile and dimming profile of the temperature-sensitive LEDs (see Equation 1). Profiles are programmed through the Color Polynomial Coefficient registers (see "Color Polynomial Coefficient (P30, P20, P10, P03, P02, P01, P21, P12, P11, P00) – Address 5 - 24" on page 26).

GAIN<sub>DR</sub> approximation allows custom dimming profile of the white LEDs (see Equation 2). The profile is programmed through the Color Polynomial Coefficient registers (see "Color Polynomial Coefficient (Q3, Q2, Q1, Q0) – Address 25 - 32" on page 27).

Cirrus Logic, Inc. and its affiliates and subsidiaries generally make no representations or warranties that the combination of Cirrus Logic's products with light-emitting diodes ("LEDs"), converter materials, and/or other components will not infringe any third-party patents, including any patents related to color mixing in LED lighting applications, such as, for example, U.S. Patent No. 7,213,940 and related patents of Cree, Inc. For more information, please see Cirrus Logic's Terms and Conditions of Sale, or contact a Cirrus Logic sales representative.

# 5.5 Dimming Signal Extraction and the Dim Mapping Algorithm

When operating with a dimmer, the dimming signal is extracted in the time domain and is proportional to the conduction angle of the dimmer. A control variable is passed to the quasi-resonant second stage to achieve 0% to 100% output currents.

# 5.6 Boost Stage

The high-voltage FET in the source-follower startup circuit is source-switched by a variable current source on the SOURCE pin to operate a boost circuit. Peak FET switching current is set by the PEAK\_CUR register (see "Peak Current (PEAK\_CUR) – Address 51" on page 36).

In No-dimmer Mode, the boost stage begins operating when the start threshold is reached during each rectified half line-cycle and is disabled at the nominal boost output voltage. The peak FET switching current determines the percentage of the rectified input voltage conduction angle over which the boost stage will operate. The control algorithm adjusts the peak FET switching current to maximize the operating time of the boost stage, thus improving the input power factor.

When operating in Leading-edge Mode, the boost stage ensures the hold current requirement of the dimmer is met from the initiation of each half-line dimmer conduction cycle until the peak of the rectified input voltage. Trailing-edge Mode boost stage ensures that the trailing-edge is exposed at the correct time with the correct current.

$$\mathsf{GAIN}_{DTR}^{=} \mathsf{P30} \cdot \mathsf{T}^3 + \mathsf{P20} \cdot \mathsf{T}^2 + \mathsf{P10} \cdot \mathsf{T} + \mathsf{P03} \cdot \mathsf{D}^3 + \mathsf{P02} \cdot \mathsf{D}^2 + \mathsf{P01} \cdot \mathsf{D} + \mathsf{P21} \cdot \mathsf{T}^2 \cdot \mathsf{D} + \mathsf{P12} \cdot \mathsf{T} \cdot \mathsf{D}^2 + \mathsf{P11} \cdot \mathsf{T} \cdot \mathsf{D} + \mathsf{P00} \quad [\mathsf{Eq.1}]$$

where,

T = the measured normalized temperature and is  $0 \le T < 1.0$

D = the normalized dim value and is  $0 \le D < 1.0$

GAIN<sub>DTR</sub> = gain of the channel based on the temperature measurement and the dim value:

$$GAIN_{DR} = (Q3 \cdot D^3) + Q2 \cdot D^2 + Q1 \cdot D + Q0$$

[Eq.2]

where,

D = the normalized dim value and is  $0 \le D < 1.0$ GAIN<sub>DR</sub> = gain of the channel based on the dim value

### 5.6.1 Maximum Peak Current

The maximum boost inductor peak current is configured by adjusting the peak switching current with  $I_{PK(code)}$ . The PEAK\_CUR register (see "Peak Current (PEAK\_CUR) – Address 51" on page 36) is used to store  $I_{PK(code)}$ . Maximum power output is proportional to  $I_{PK(code)}$ , as shown in Equation 3:

$$P_{in, max} = \frac{\delta(I_{PK} \cdot V_{rms, typical})}{2}$$

[Eq.3]

where,

$\delta$  = correction term = 0.55

V<sub>rms, typical</sub> = nominal operating input RMS voltage

$I_{PK} = I_{PK(code)} \cdot 4.1 \text{ mA}$

# 5.6.2 Output BSTOUT Sense & Input IAC Sense

A current proportional to the boost output voltage,  $V_{BST}$ , is supplied to the IC on pin BSTOUT and is used as a feedback control signal. The ADC is used to measure the magnitude of the I<sub>BSTOUT</sub> current through resistor R<sub>BST</sub>. The magnitude of the I<sub>BSTOUT</sub> current is then compared to an internal reference current (I<sub>ref</sub>) of 133µA.

Figure 12. BSTOUT Input Pin Model

Resistor  $R_{BST}$  sets the feedback current at the nominal boost output voltage. For 230VAC line voltage applications,  $R_{BST}$  is calculated as shown in Equation 4:

$$R_{BST} = \frac{V_{BST}}{I_{ref}} = \frac{400V}{133\mu A} \cong 3M\Omega \qquad [Eq.4]$$

where,

V<sub>BST</sub> = Nominal boost output voltage

Iref = Internal reference current

For 120VAC line voltage applications (CS1630), nominal boost output voltage, V<sub>BST</sub>, is 200V, and resistor R<sub>BST</sub> is 1.5M $\Omega$ . By using digital loop compensation, the voltage feedback signal does not require an external compensation network.

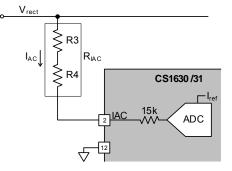

A current proportional to the AC input voltage is supplied to the IC on pin IAC and is used by the boost control algorithm.

Figure 13. IAC Input Pin Model

Resistor  $\mathsf{R}_{\text{IAC}}$  sets the  $\mathsf{I}_{\text{AC}}$  current and is derived from Equation 5:

$$R_{IAC} = R_{BST}$$

[Eq.5]

For optimal performance, resistors  $R_{IAC}$  and  $R_{BST}$  should use 1% tolerance or better resistors for best  $V_{BST}$  voltage accuracy.

# 5.6.3 Boost Auxiliary Winding

The boost auxiliary winding is used for zero-current detection (ZCD). The voltage on the auxiliary winding is sensed through the BSTAUX pin of the IC. It is also used to deliver startup current during startup time (see "Startup Circuit" on page 10).

# 5.6.4 Boost Overvoltage Protection

The CS1630/31 supports boost overvoltage protection (BOP) to protect the bulk capacitor C8 (see Figure 14). If the boost output voltage exceeds the overvoltage protection thresholds programmed in the OTP registers a BOP fault signal is generated. The voltage level, V<sub>BOP(th)</sub>, can be set within 227V to 257V for a CS1630 and 432V to 462V for a CS1631 (see "Configuration 53 (Config53) - Address 85" on page 42). The control logic continuously averages the BOP fault signal using a leaky integrator. When the output of the leaky integrator exceeds a certain threshold, which can be set using bits BOP\_INTEG[3:0] in register Config53 (see "Configuration 53 (Config53) - Address 85" on page 42), a boost overvoltage fault is declared and the system stops boosting. More information on the leaky integrator size and sample rate is provided in section 6.23 "Configuration 18 (Config18) -Address 50" on page 35.

During a boost overvoltage protection event, the second stage is kept enabled only if the MAX\_CUR bit in register Config45 (see "PU Coefficient (PID) – Address 45" on page 33) is set to '1' (enabled), and its dim input is railed to full scale. This allows the second stage to quickly dissipate the stored energy on the bulk capacitor C8, bringing down the boost output voltage to a safe value. A visible flash on the LED might appear, indicating that an overvoltage event has occurred. When the boost output voltage drops to 195V (for a 120V application), or 392V (for a 230V application), the boost stage is enabled if bit

BOP\_RSTART in register Config54 (see "Configuration 54 (Config54) – Address 86" on page 43) is set to '1', and the system returns to normal operation. If bit BOP\_RSTART is set to '0', a boost overvoltage fault is latched and the system stays in the fault mode until the input power is recycled.

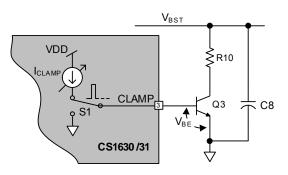

# 5.7 Voltage Clamp Circuit

To keep dimmers conducting and prevent them from misfiring, a minimum power needs to be delivered from the dimmer to the load. This power is nominally around 2W for 230V and 120V TRIAC dimmers. At low dim angles ( $\leq$ 90°), this excess power cannot be converted into light by the second stage due to the dim mapping at light loads. The output voltage of the boost stage (V<sub>BST</sub>) can rise above the safe operating voltage of the primary-side bulk capacitor C8.

The CS1630/31 provides active clamp circuitry on the CLAMP pin, as shown in Figure 14.

Figure 14. CLAMP Pin Model

A PWM control loop ensures that the voltage on V<sub>BST</sub> does not exceed 227V for 120VAC applications or 424V for 230VAC applications. This control turns on the BJT of the voltage clamp circuit, allowing the clamp circuit to sink current through the load resistor, preventing  $V_{BST}$  from exceeding the maximum safe voltage.

# 5.7.1 Clamp Overpower Protection

The CS1630/31 clamp overpower protection (COP) control logic continuously monitors the 'ON' time of the clamp circuit. If the cumulative 'ON' time exceeds 84.48ms during the internally generated 1 second window time, a COP event is actuated, disabling the boost and second stages. The clamp circuitry is turned off during the fault event.

# 5.8 Quasi-resonant Second Stage

The second stage is a quasi-resonant current-regulated DC-DC converter capable of flyback, buck, or tapped buck operation. The second stage output configuration is set by bit S2CONFIG in the Config12 register (see "Configuration 12 (Config12) – Address 44" on page 33) and bit BUCK in the Config10 register (see "Configuration 10 (Config10) – Address 42" on page 32). To deliver the highest possible efficiency, the second stage can operate in quasi-resonant mode and provides constant output current with minimum line-frequency ripple. Primary-side control is used to simplify system design and reduce system cost and complexity.

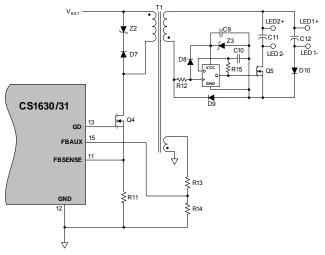

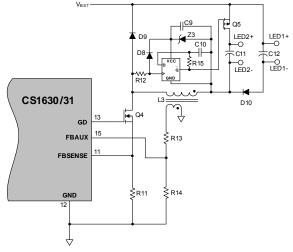

The digital algorithm ensures monotonic dimming from 0% to 100% of the dimming range with a linear relationship between the dimming signal and the LED current. Figure 15 illustrates a quasi-resonant flyback stage configured for 2-channel parallel output.

Figure 15. Flyback Parallel Output Model

The flyback stage is controlled by measuring current in the transformer primary and voltage on the auxiliary winding. Quasi-resonant operation is achieved by detecting transformer flyback using an auxiliary winding.

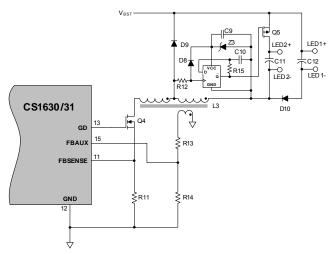

A quasi-resonant buck stage configured for 2-channel parallel output is illustrated in Figure 16.

Figure 16. Buck Parallel Output Model

# CS1630/31

The buck stage is controlled by measuring current in the buck inductor and voltage on the auxiliary winding. Quasi-resonant operation is achieved by detecting buck inductor demagnetization using an auxiliary winding. The digital control algorithm rejects line-frequency ripple created on the second stage input by the front-end boost stage, resulting in the highest possible LED efficiency and long LED life.

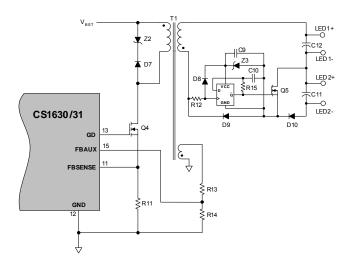

The tapped buck stage operates similar to a buck stage. The tapped buck topology provides minimum turn-on time and improves conversion efficiency when large input-to-output voltage ratio is present. The tapped buck inductor behaves as a transformer for voltage conversion and is controlled by measuring current in the tapped inductor and voltage on the auxiliary winding. Quasi-resonant operation is achieved by detecting tapped inductor demagnetization using an auxiliary winding.

Figure 17. Tapped Buck Parallel Output Model

# 5.8.1 Series and Parallel 2-Channel Output

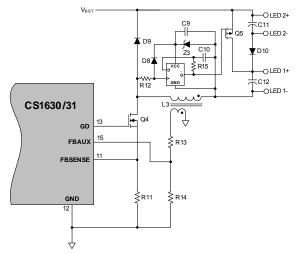

The CS1630/31 is designed to be programmed to support series or parallel 2-channel output configurations using one set of power magnetics. Series or parallel configuration is set by bit STRING and bit LED\_ARG in the Config3 register (see "Configuration 3 (Config3) – Address 35" on page 29). Parallel connections for a flyback stage and buck stage are connected differently: an NMOS switch is used in flyback configuration, and a PMOS switch is used in buck/tapped buck configuration (see Figures 15, 16, and 17).

Figure 18. Flyback Series Output Model

Similarly, series connection in a flyback stage and buck stage also uses an NMOS switch and a PMOS switch, respectively, as shown in Figures 18 and 19.

Figure 19. Buck Series Output Model

Figure 20 illustrates the tapped buck stage configured for series output mode.

Figure 20. Tapped Buck Series Output Model

To maintain constant output current with minimum linefrequency ripple, the following are required:

- For parallel configurations, a minimum voltage potential difference between two strings is required.

- For series configurations, a minimum current amplitude difference between two strings is required.

# 5.8.2 Primary-side Current Control for 2-Channel Output

The CS1630/31 regulates 2-channel output current independently using primary-side control, which eliminates the need for opto-coupler feedback. The control loop operates in peak current control mode, with the peak current set cycle-by-cycle by the two independent current regulation loops. Demagnetization time of the second stage inductor is sensed by the FBAUX pin using an auxiliary winding on the second stage inductor. The FBAUX pin supplies an input to the digital control loop.

The power conversion for 2-channel output is carried out by interleaving the PWM. The 2-channel control system consists of two components:

- A toggle device (phase synchronizer circuit) on the secondary side that alternatively activates each output channel for each switching event

- A digital sequencer on the primary side determines which output channel is active for any given switching event

As the output is toggled between each channel, a sequencer on the primary side identifies the current control phase and regulates the current in each output channel. To ensure proper operation for a parallel configuration, the two output channels should target a voltage differential that is greater than 20%. For a series configuration, the two output channels should target a current differential that is greater then 20%.

# 5.8.3 Auxiliary Winding Configuration

The second-stage inductor auxiliary winding is used for zerocurrent detection (ZCD) and overvoltage protection (OVP). The auxiliary winding is sensed through the FBAUX pin of the IC.

# 5.8.4 Control Parameters

The second-stage control parameters are set to assure:

- Line Regulation The LED current remains constant despite a ±10% AC line voltage variation.

- Effect of Variation in Transformer Magnetizing Inductance — The LED current remains constant over a ±20% variation in magnetizing inductance.

The FBSENSE input is used to sense the current in the second stage inductor. When this current reaches a certain threshold, the gate drive turns off (output on pin GD).

Two OTP values are required to set the second-stage output currents, CH1CUR for channel 1 and CH2CUR for channel 2 (see "Channel 1 Output Current (CH1CUR) – Address 41" on page 32 and "Channel 2 Output Current (CH2CUR) – Address 43" on page 32). Equations 6 and 7 are used to calculate the values to be programmed into registers CH1CUR and CH2CUR.

$$CH1CUR = \frac{1022 \cdot R_{CS} \cdot I_{CH1}}{V_{CS}}$$

[Eq.6]

$$CH2CUR = \frac{1022 \cdot R_{CS} \cdot I_{CH2}}{V_{CS}}$$

[Eq.7]

where,

- R<sub>CS</sub> = Resistance of current sense resistor

- $V_{CS}$  = Full scale voltage across sense resistor (~1.4V)

- I<sub>CH1</sub> = Target current in channel 1 LED string

- I<sub>CH2</sub> = Target current in channel 2 LED string

R<sub>CS</sub> is determined by the input voltage, switching frequency, auxiliary transformer turns ratio, target output current and output voltage for each channel.

The zero-current detect input on pin FBAUX is used to determine the demagnetization cycle  $T_2$ . The controller then uses these inputs to control the gate drive output, GD.

# 5.8.5 Frequency Dithering

The peak amplitude of switching harmonics can be reduced by spreading the energy into wider spectrums. The frequency dithering level can be managed using bits DITLEVEL[1:0] in register Config61 (see "Configuration 61 (Config61) – Address 93" on page 47). Additionally, the CS1630/31 has an option to enable dithering only in No-dimmer Mode by setting bit DITNODIM to '1'. If output currents differ, the CS1630/31 also has an option to allow for less dither on one of the two channels by selecting the channel using bit DITCHAN. The channel selected for less dither attenuates the dither level by the percentage configured by bits DITATT[1:0].

### 5.8.6 Output Open Circuit Protection

Output open circuit protection and output overvoltage protection (OVP) are implemented by monitoring the output voltage through the second-stage inductor auxiliary winding. If the voltage on the FBAUX pin exceeds a threshold ( $V_{OVP(th)}$ ) of 1.25V, a fault condition occurs. The IC output is disabled and the CS1630/31 attempts to restart after one second.

### 5.8.7 Overcurrent Protection (OCP)

Overcurrent protection is implemented by monitoring the voltage across the second-stage sense resistor. If this voltage exceeds a threshold ( $V_{OCP(th)}$ ) of 1.69V, a fault condition occurs. The IC output is disabled, and the CS1630/31 attempts to restart after one second.

## 5.8.8 Open Loop Protection (OLP)

Open loop protection and protection against a short of the second stage sense resistor are implemented by monitoring the voltage across this resistor. If the voltage on pin FBSENSE does not reach the protection threshold ( $V_{OLP(th)}$ ) of 200mV, the IC output is disabled and the CS1630/31 attempts to restart after one second.

## 5.9 Overtemperature Protection

The CS1630/31 incorporates an internal overtemperature protection (iOTP) circuit for IC protection and the circuitry required to connect an external overtemperature protection (eOTP) device. Typically, a NTC thermistor is used.

### 5.9.1 Internal Overtemperature Protection

Internal overtemperature protection (iOTP) is activated and power switching devices are disabled when the die temperature of the CS1630/31 exceeds 135°C. A hysteresis of about 7°C occurs before resuming normal operation.

## 5.9.2 External Overtemperature Protection

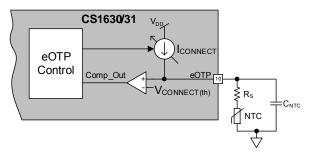

The external overtemperature protection (eOTP) pin is used to implement overtemperature protection using an external negative temperature coefficient (NTC) thermistor,  $R_{NTC}$ . The total resistance on the eOTP pin is converted to an 8-bit digital 'CODE' (which gives an indication of the temperature) using a digital feedback loop that adjusts the current ( $I_{CONNECT}$ ) into the NTC and series resistor ( $R_S$ ) to maintain a constant reference voltage of 1.25V ( $V_{CONNECT}$ (th)). Figure 21 illustrates the functional block diagram when connecting an optional external NTC temperature sensor to the eOTP circuit.

Figure 21. eOTP Functional Diagram

Current  $I_{CONNECT}$  is generated from an 8-bit controlled current source with a full-scale current of 80  $\mu$ A. See Equation 8:

$$I_{\text{CONNECT}} = \frac{V_{\text{CONNECT}(th)}}{R}$$

[Eq.8]

When the loop is in equilibrium, the voltage on the eOTP pin fluctuates around V<sub>CONNECT(th)</sub>. The digital 'CODE' output by the ADC is used to generate I<sub>CONNECT</sub>. In normal operating mode, the I<sub>CONNECT</sub> current is updated once every seventh half line-cycle by a single  $\pm$  LSB step. See Equation 9.

$$\text{CODE} \cdot \left[ \frac{I_{\text{CONNECT}}}{2^{N}} \right] = \frac{V_{\text{CONNECT(th)}}}{R_{\text{NTC}} + R_{S}} \qquad [\text{Eq.9}]$$

Solving Equation 9 for CODE:

$$CODE = \frac{2^{N} \cdot V_{CONNECT(th)}}{I_{CONNECT} \cdot (R_{NTC} + R_{S})}$$

$$= \frac{256 \cdot 1.25 V}{(80 \mu A) \cdot (R_{NTC} + R_{S})} \qquad [Eq. 10]$$

$$= \frac{4 \cdot 10^{6}}{(R_{NTC} + R_{S})}$$

The tracking range of this ADC is approximately  $15.5 \mathrm{k}\Omega$  to  $4\mathrm{M}\Omega$ . The series resistor R<sub>S</sub> is used to adjust the resistance of the NTC to fall within this ADC tracking range so that the entire 8-bit dynamic range of the ADC is well used. A  $14\mathrm{k}\Omega$  (±1% tolerance) series resistor is required to allow measurements of up to  $130^{\circ}$ C to be within the eOTP tracking range when a  $100\mathrm{k}\Omega$  NTC with a Beta of 4334 is used. The eOTP tracking circuit is designed to function accurately with an external capacitance of a maximum of 470 pF. A higher 8-bit code output reflects a lower resistance and hence a higher external temperature.

The ADC output code is filtered to suppress noise and compared against a programmable code value that corresponds to the desired shutoff temperature set point. If the temperature exceeds this threshold, the chip enters an external overtemperature state and shuts down. The external overtemperature state is not a latched protection state, and the ADC keeps tracking the temperature in this state in order to clear the fault state once the temperature drops below 110°C. If an external overtemperature protection thermistor is not used, connect the eOTP pin to GND using a  $50k\Omega$  to  $500k\Omega$  resistor to disable the eOTP feature.

When exiting reset, the chip enters startup and the ADC quickly (<5ms) tracks the external temperature to check if it is below the 110°C reference code before the boost and second stages are powered up. If this check fails, the chip will wait until this condition becomes true before initializing the rest of the system.

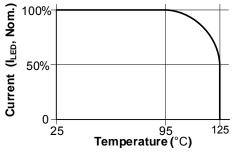

For external overtemperature protection, a second low-pass filter with a time constant of two seconds filters the ADC output and uses it to scale down the internal dim level of the system (and hence the LED current, I<sub>LED</sub>) if the temperature exceeds 95 °C (see Figure 22). The filter is applied to the ADC output and uses it to scale down the internal dim level of the system (and hence the LED current, I<sub>LED</sub>) if the temperature exceeds a programmable 8-bit threshold that corresponds to Tempeorp. The large time constant for this filter ensures that the dim scaling does not happen spontaneously and is not noticeable (suppress spurious glitches). Temperature threshold must set be such that Temp<sub>eOTP</sub> < Temp<sub>Wakeup</sub> < Temp<sub>Shutdown</sub>. Register Config59 sets TempeOTP. Register Config46 sets TempWakeup. Register Config44 sets Temp<sub>Shutdown</sub> (see "Configuration 59 (Config59) - Address 91" on page 46, "Configuration 44 (Config44) - Address 76" on page 36, and "Configuration 58 (Config58) - Address 90" on page 45).

For example, the system can be set up such that the  $I_{LED}$  starts reducing when  $R_{NTC} \sim 6.3 \mathrm{k}\Omega$  (assuming a  $14 \mathrm{k}\Omega, \pm 1\%$  tolorance, series resistor  $R_S$ ), which corresponds to a temperature of 95°C (Temp\_{eOTP} code is 196) for a 100 \mathrm{k}\Omega NTC with a Beta of 4334 (100 kW at 25°C). The  $I_{LED}$  current is scaled until the NTC value reaches  $2.5 \mathrm{k}\Omega$  (Temp\_Shutdown code is set to 242, which implies 125°C). The CS1630/31 uses this calculated value to scale the output LED current,  $I_{LED}$ , as shown in Figure 22.

Figure 22. eOTP Temperature vs. Impedance

Beyond this temperature, the IC shuts down using the mechanism discussed above. If the external overtemperature protection and the temperature compensation for CCT control features are not required, connect the eOTP pin to GND using a  $50 k\Omega$  to  $500 k\Omega$  resistor to disable the eOTP feature.

# 5.10 Power Line Calibration

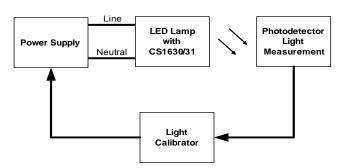

The CS1630/31 integrates power line calibration technology within the controller to enable calibration and end-of-line programming without the need for an additional electrical connection as shown in Figure 23.

Figure 23. Power Line Calibration Block Diagram

The power line calibration uses a phase-cut mechanism for data generation and return-to-zero data encoding to eliminate the need for clock synchronization. A code/command can be created by using the combination of input phase angles, as detailed in "Power Line Calibration Characteristics" on page 7. When an initial program mode command has been detected, the controller will begin to enter calibration mode. After key parameters of the lighting system have been characterized and programmed, a burn-in code plus an end-program mode command is transmitted, instructing the controller to exit the calibration mode. Power line calibration and end-of-line programming requires no human intervention. The CS1630/31 provides registers that allow up to three attempts for LED output current trimming over power line calibration. Six registers store the three optional color control system calibration values for channel 1 color calibration and channel 2 color calibration. For more detail regarding color calibration, see "Channel 1 Color Calibration 3A (CH1 CAL3A) - Address 119" on page 49 through "Channel 2 Color Calibration 3C (CH2 CAL3C) - Address 126" on page 51.

## 5.10.1 Power Line Calibration Specification

To ensure the success of phase detection, the angle for each bit is specified as shown in "Power Line Calibration Characteristics" on page 7. The CS1630/31 power line calibration system operates under universal line voltage and frequency with a leading-edge, phase-cut waveform.

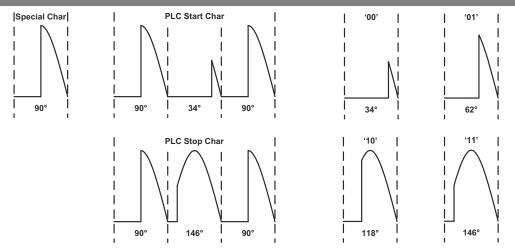

### Figure 24. Power Line Calibration Mode Character Waveforms

### 5.10.2 PLC Program Mode Characters

In order to program the CS1630/31, a set of encoded characters is built from specific phase-cut waveform patterns. Figure 24 illustrates the phase-cut waveform encoding recognized by the CS1630/31 power line calibration system. As shown in Table 1, six characters are formed using the special character and two-bit encoded data.

| Character                                                               | Code            | Notes                                      |  |  |

|-------------------------------------------------------------------------|-----------------|--------------------------------------------|--|--|

| Start Char                                                              | (SC)00(SC)      | PLC Program Start Character <sup>(1)</sup> |  |  |

| Stop Char                                                               | (SC)11(SC)      | PLC Program Stop Character <sup>(1)</sup>  |  |  |

| Duo-bit '00'                                                            | 00              | 2-bit Data [00]                            |  |  |

| Duo-bit '01'                                                            | 01              | 2-bit Data [01]                            |  |  |

| Duo-bit '10'                                                            | 10              | 2-bit Data [10]                            |  |  |

| Duo bit '11'                                                            | 2-bit Data [11] |                                            |  |  |

| Note: (1) A Special Character (SC) must precede and follow the Duo-bit. |                 |                                            |  |  |

Table 1. Power Line Calibration Characters

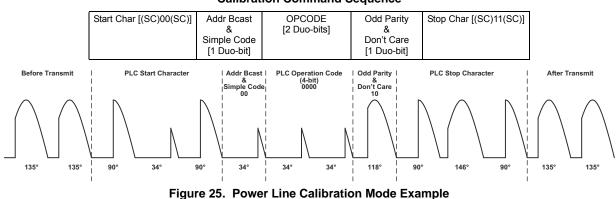

## 5.10.3 Calibration Mode Operation Code

The CS1630/31 power line calibration system requires a start and stop operation code to activate and deactivate power line calibration mode. Once in the power line calibration mode, operation codes (OPCODE) will be used to program specific addresses using the OPCODE listed in Table 2.

| Name                                                                                                                                                               | OPCODE | Description                                |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------------------------------------------|--|--|

| NOP                                                                                                                                                                | 0000   | No Operation                               |  |  |

| INIT_PROG_MODE                                                                                                                                                     | 0001   | Initialize program mode <sup>(1)</sup>     |  |  |

| I2C_WRITE                                                                                                                                                          | 0010   | Perform a generic I <sup>2</sup> C write   |  |  |

|                                                                                                                                                                    | 0011   | Reserved                                   |  |  |

| BURN_OTP                                                                                                                                                           | 0100   | Initiate an OTP write cycle <sup>(3)</sup> |  |  |

| STR1_OFFSET                                                                                                                                                        | 0101   | Write String 1 offset <sup>(2)</sup>       |  |  |

| STR2_OFFSET                                                                                                                                                        | 0110   | Write String 2 offset <sup>(2)</sup>       |  |  |

| WRITE_CRC                                                                                                                                                          | 0111   | Write CRC value                            |  |  |

| END_PROG_MODE                                                                                                                                                      | 1000   | Disable programming mode                   |  |  |

| WRITE_DIM                                                                                                                                                          | 1001   | Sets PLC dim value                         |  |  |

| Notes: (1) Allows other commands to program the device under test.<br>(2) Range of Offset tolerance is ±15%.<br>(3) The light is flashed to indicate pass or fail. |        |                                            |  |  |

### Table 2. Power Line Calibration Operation Code

The LED light flashes seven times to indicate a command error. The LED flashes two times when OTP registers are programmed successfully and four times when programming is unsuccessful. Figure 25 illustrates an example of a power line calibration mode command sequence and the cutwaveform pattern.

### **Calibration Command Sequence**

## 5.10.4 Register Lockout

The CS1630/31 provides register lockout for security against unauthorized access to proprietary registers using the I<sup>2</sup>C or PLC communication port. A 32-bit long-word is used for password protection when accessing the OTP registers. The register lockout password can be set by programming the Lockout Key registers (see "Lockout Key (LOCK0, LOCK1, LOCK2, LOCK3) – Address 1 - 4" on page 26). Register lockout is enabled by setting bit LOCKOUT in register Config0 (see "Configuration 0 (Config0) – Address 0" on page 26).

# 5.11 I<sup>2</sup>C<sup>™</sup> Communication Interface

The purpose of the communication system is to provide a mechanism to allow the transfer of data and accessibility to the device. Pins SDA and SCL are an  $I^2C$  communication port used to provide access to control registers inside the EXL core. In applications that do not use  $I^2C$  communication, pins SDA and SCL should be connected to VDD. When SDA and SCL are connected to VDD, read/write register values are controlled internally by the EXL core.

A one-time programmable (OTP) memory is implemented as part of the communication system to store trim and key parameters. After power-on reset (POR), the OTP memory is uploaded into shadow registers as part of startup, and a cyclic redundancy check (CRC) is calculated and checked on the data read from the OTP memory. If the computed CRC does not match the CRC value saved in the OTP memory, default values are used for some of the parameters. Shadow registers can be written using the I<sup>2</sup>C interface. In order to write to or read from the I<sup>2</sup>C port, a defined messaging protocol must be implemented.

The OTP memory is organized as 128 addressable bytes (8 bits). The contents of the OTP memory are read at reset and are addressable by the  $I^2C$  interface. The shadow register values are used to control the internal operational parameters of the IC and can be modified. However, in the event of a POR or any kind of reset, the shadow registers will be rewritten with the OTP memory content. In the event that a CRC verification fails during normal operation, the registers will be rewritten with OTP memory content, negating any changes that have been made to the shadow registers.

The CRC is verified after the OTP memory has been uploaded at POR, periodically during the operation of the IC, and at the exit of Control Port mode. The CRC can be disabled by writing to the CRC disable register, or by enabling the Control Port mode (see "Control Port Enable" on page 21). The shadow registers will be restored from OTP memory on a POR event, or any reset type event. The CRC is calculated using Equation 11.

$$CRC = CRC \div (x^8 + x^2 + x + 1)$$

[Eq.11]

The CRC calculation is implemented in hardware using a linear feedback shift register starting with address 0 and ending with address 57 (see Figure 26). The current CRC is stored in address 63.

Figure 26. CRC Hardware Representation

To perform a successful write to the OTP memory, the CRC must be calculated and stored in the CRC registers prior to issuing the OTP write command. OTP memory can only be written once. OTP shadow registers accessible to the user are described in "One-Time Programmable (OTP) Registers" on page 24.

# 5.11.1 PC Control Port Protocol

The communication port is designed to allow a master device to read and write the OTP shadow registers of the CS1630/31 and the capability of programming the OTP memory using the data in the shadow registers. The OTP shadow registers provide a mechanism for configuring the device and calibrating the system prior to programming the device. The CS1630/31 communication port physical layer adheres to the I<sup>2</sup>C bus specification by Philips Semiconductor version 2.1, January 2000 (see "I<sup>2</sup>C Port Switching Characteristics" on page 6). The CS1630/31 control port only supports I<sup>2</sup>C slave functionality. The CS1630/31 I<sup>2</sup>C interface is intended for use with a single master and no other slaves on the bus.

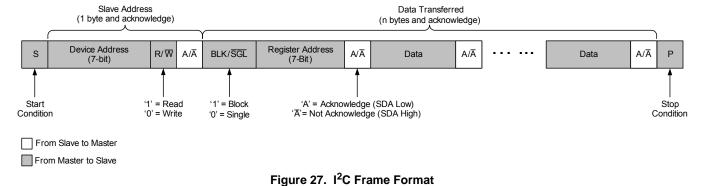

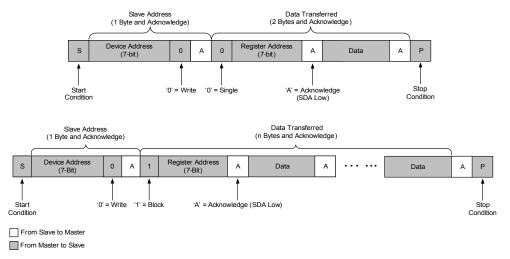

Figure 27 illustrates the frame format used for  $I^2C$  data transfers. The first bit is a Start condition (bit S) followed by an 8-bit slave address that is comprised of a 7-bit device address plus a Read/Write (R/W) bit. The R/W bit is the least significant bit of the slave address byte, which indicates

whether data transfer is a read or write operation. This bit should be set to '0' to perform a write operation and '1' to perform a read operation. The 7-bit device address is the 7 most significant bit of the slave address. For data transfers, the CS1630/31 acknowledges a binary device address of '0010000', which is reserved for accessing OTP shadow registers (see "One-Time Programmable (OTP) Registers" on page 24).

After the 7-bit device address is received, the Control Port performs a compare to determine if it matches the CS1630/31 device address. If the compare is true, the Control Port will respond with an Acknowledge (bit A) and prepares the device for a read or write operation. Since the CS1630/31 is always in slave mode, the device sends an Acknowledge at the end of each byte. The final bit is the Stop condition (bit P), which is sent by the master to finish a data transfer.

The communication port supports single and block data transfers. The block read or write capability is available by setting the MSB of the register address to '1'. Device address 0x10 provides access to the OTP shadow registers in the address range of 0x00 to 0x7F.

## 5.11.2 Control Port Enable

Control Port mode is enabled and initiated by transmitting a two-byte hardware pass code using an  $I^2C$  block write.

To enable the control port, the master needs to write a Start condition followed by a slave address of 0x22 (7 MSB device address = '0010001' and the LSB  $\underline{R/W}$  = '0' for a write operation). Then a 0x81 (MSB BLK/SGL = '1' and 7 LSB register address = '0000001') followed by two bytes of data 0xF4 and 0x4F, ending the transmission with a Stop condition.

Once in Control Port mode, the CS1630/31 can be configured to perform color calibration functions and program the OTP memory. Several other system configuration tasks can be performed by writing and reading the shadow registers using the  $I^2C$  port.

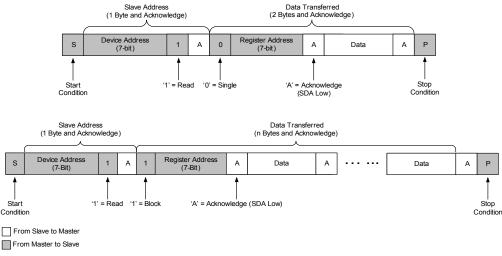

# 5.11.3 Read Operation

To perform a read operation, the master must write the 7-bit device address, the R/W bit, the Block/Single (BLK/SGL) bit, and the 7-bit shadow register address. The master can then read the required bytes from the shadow registers. Figure 28 illustrates protocol for a single and block read operation.

To perform a single shadow register read, a write to the Control Port must be used to set up the shadow register address and the BLK/SGL configuration bit (indicating a single read operation). To initiate a single read operation, a Start condition followed by a slave address of 0x21 (7 MSB device address = '0010000' and the LSB R/W = '1' for a read operation) is sent at the start of the message. The MSB of the second byte is cleared to '0' to indicate a single byte read. The remaining 7 bits of the second byte represent the shadow register address of the read operation. After receiving the Acknowledge from the Control Port, the master should terminate the message by sending a Stop condition. The protocol for a single read operation is illustrated by the top frame in Figure 28.

To initiate a block read operation, a Start condition followed by a slave address of 0x21 (7 MSB device address = '0010000' and the LSB R/W = '1' for a read operation) is sent at the start of the message. The MSB of the second byte is set to '1' to indicate a block read. The remaining 7 bits of the second byte represent the starting shadow register address of the read operation. The slave continues to send data bytes until the master sends a Stop condition after receiving the Acknowledge, signifying the end of the block read message. The protocol for a block read operation is illustrated by the bottom frame in Figure 28.

## 5.11.4 Write Operation

To perform a write operation, the master must write the 7-bit device address, the R/W bit, the BLK/SGL bit, and the 7-bit shadow register address. The master can then write the required bytes to the shadow registers. Figure 29 illustrates protocol for a single and block write operation.

Figure 28. Frame Formats for Read Operation

To perform a single shadow register write, a write to the Control Port must be used to set up the shadow register address and the BLK/SGL configuration bit (indicating a single write operation). To initiate a single write operation, a Start condition followed by a slave address of 0x20 (7 MSB device address = '0010000' and the LSB R/W = '0' for a write operation) is sent at the start of the message. The most significant bit of the second byte is cleared to '0' to indicate a single byte write. The remaining 7 bits of the second byte represent the shadow register address of the write operation. After receiving the Acknowledge from the Control Port, the master should terminate the message by sending a Stop condition. The protocol for a single write operation is shown as the top frame in Figure 29.

To initiate a block write operation, a Start condition followed by a slave address of 0x20 (7 MSB device address = '0010000'and the LSB R/W = '0' for a write operation) is sent at the start of the message. The MSB of the second byte is set to '1' to indicate a block write. The remaining 7 bits of the second byte represent the starting shadow register address of the write operation. The slave continues to send data bytes until the master sends a Stop condition after receiving the Acknowledge, signifying the end of the block write message. The protocol for a block write operation is illustrated by the bottom frame in Figure 29. Block writes will wrap around from shadow register address 127 to 0 if a Stop condition is not received.

# 5.11.5 Customer I<sup>2</sup>C Lockout

The CS1630/31 provides a mechanism that locks or disables the I<sup>2</sup>C control port. This feature provides security against potential access to proprietary register settings and OTP memory (color compensation) through the I<sup>2</sup>C control port. To enable the lockout feature, the LOCKOUT bit is set to '1' in the Config0 register (see "Configuration 0 (Config0) – Address 0" on page 26) and setting a 32-bit Lockout Key in registers LOCK3, LOCK2, LOCK1, and LOCK0 (at register address 0x01 to 0x04). The value of the Lockout Key is user programmable and stored in OTP memory (see "Lockout Key (LOCK0, LOCK1, LOCK2, LOCK3) – Address 1 - 4" on page 26).