# CMX7861 FirmCODEC<sup>®</sup>

D/7861\_FI-1.x/2 June 2012

# DATASHEET

Advance Information

# 7861FI-1.x Programmable Baseband Interface

# Features

- Dual Channel Codecs

- o Can operate in modem or codec mode

- Two ADCs 16 bit

- o Two DACs 14 bit

- Programmable input and output gain

- Differential/single ended inputs/outputs

- Digital Channel Filters

- Two fully-programmable digital filters

- Filter design and configuration support

- Auxiliary ADCs

- Four 10-bit DACs

- Autonomous RAMDAC sequencer

- Auxiliary ADC

- One 10-bit ADC with four-input MUX

- ADC averaging, trip on high/low 'watch' modes

- Auxiliary GPIO

- Four programmable input/outputs

- Auxiliary Synthesised Clock Generators

- Two programmable clock outputs

- C-BUS Host Serial Interface

- o SPI-like with register addressing

- Read/write 128-byte FIFOs and data buffers

- Streamline transfers, low host service latency

- Master SSP Interface

- External slave device control

- Serial Flash connection

- Pass-through (Thru-port) mode expands host C-BUS/SPI capacity

# Features Cont.

- Low-power 3.0V to 3.6V operation

- Multiple power-saving options

- Small 64-pin VQFN Package

- Evaluation support

- PE0601-7861 Evaluation kit

- o PE0002 Interface card

# Applications

- General-purpose DSP analogue/digital interface

- o Sensors

- Control systems

- Telemetry/SCADA/data modems

- High Performance Narrowband Data Radio

- DMR

- o APCO P25

- Software Defined Radio (SDR)

- o 6.25kHz to 25kHz RF channel spacings

- worldwide compatibility e.g. ETSI, FCC, ARIB, FCC Part 90 per spectral efficiency requirements

- High Performance I/Q Radio Interface

- Tx and Rx: 'direct connect' to zero IF transceiver

- Simple external RC filters

- Digital filter configurable for multiple RF channel spacings (Rx), Default is for DMR

- I/Q trims

# **1** Brief Description

# 1.1 General

The CMX7861 FirmCODEC<sup>®</sup> is a general-purpose, dual-channel baseband interface device for use in DSP-based systems. The device is a combination of codec, embedded signal processing and auxiliary system support functions that, together, allow simple interfacing to analogue and digital systems.

Single-ended and differential interface options are provided and I/Q-based operation is supported. The device can also be used in radio systems operating with channel bandwidths up to 50kHz, interfacing RF devices to baseband DSP/microcontroller, performing the main data conversion and auxiliary operations for monitoring and control.

Fully-programmable on-chip digital channel filters can be utilised for signal conditioning purposes. Intelligent auxiliary ADC, DAC and GPIO sub-systems perform valuable functions and minimise host interaction and host I/O resources. Two synthesised system clock generators develop clock signals for off-chip use. The C-BUS/SPI master interface expands host C-BUS/SPI ports to control external devices.

The CMX7861 utilises CML's proprietary *FirmASIC*<sup>®</sup> component technology that enables on-chip subsystems to be configured by a Function Image<sup>TM</sup> data file, which is uploaded during device initialisation and defines the device's function and feature set. The Function Image<sup>TM</sup> can be loaded automatically from a host  $\mu$ C over the C-BUS serial interface or from an external memory device. The device's functions and features can be enhanced by subsequent Function Image<sup>TM</sup> releases, facilitating in-the-field upgrades.

The CMX7861 operates from a 3.3V supply and includes selectable power saving modes. It is available in a 64-VQFN package.

# **1.2 Codec and Modem Modes**

Two general modes of operation are supported: codec mode and modem mode.

Codec mode is intended for applications where a general purpose codec is required. When in codec mode the CMX7861 will provide digital-to-analogue and analogue-to-digital conversion, producing a flat pass band over the sampled bandwidth. Simple programmable transmit and receive filter options are provided but there are no signal interpolation facilities available, and the maximum sample rate is limited.

Modem mode is suited to applications where the CMX7861 is used to transmit modulated data and receive that data. Modem mode provides a transmit signal interpolator which will aid in the modulation process by converting mapped symbols to a filtered, modulated output. Receive channel filters are also provided, however filter design is more complex than codec mode as ADC and DAC roll off need to be considered when designing filters. Modem mode is, in general, more efficient than codec mode and is capable of providing a higher sample rate.

This datasheet is the first part of a two-part document.

# CONTENTS

| <u>Secti</u> | on               |                                                                         | <u>Page</u> |

|--------------|------------------|-------------------------------------------------------------------------|-------------|

| 1            | 1.1 Ge<br>1.2 Co | ription<br>eneral<br>dec and Modem Modes<br>story                       | 2<br>2      |

| •            |                  |                                                                         |             |

| 2            |                  | grams                                                                   |             |

| 3            | •                |                                                                         |             |

|              |                  | wer Supply Signal Definitions                                           |             |

| 4            | PCB Layo         | ut Guidelines and Power Supply Decoupling                               | 10          |

| 5            | External C       | components                                                              | 11          |

|              |                  | al Interface                                                            |             |

|              |                  | BUS Interface                                                           | 11          |

|              | -                | gnal Output                                                             |             |

|              | 5.3.1            | Output Signal Routing                                                   |             |

|              | 5.3.2            | Output Reconstruction Filter – (I/Q mode)                               |             |

|              | 5.3.3            | Output Reconstruction Filter – Single-ended Outputs                     |             |

|              | -                | gnal Input                                                              |             |

|              | 5.4.1            | Input Signal Routing                                                    |             |

|              | 5.4.2            | Input Anti-alias Filter (I/Q mode)                                      |             |

|              | 5.4.3            | Input Anti-alias Filter (Inputs 3 and 4)                                |             |

| 6            |                  | escription                                                              |             |

|              |                  | /X7861 Features                                                         |             |

|              | -                | gnal Interfaces                                                         |             |

| 7            |                  | escriptions                                                             |             |

|              |                  | al Frequency                                                            | 21          |

|              |                  | st Interface                                                            |             |

|              | 7.2.1            | C-BUS Operation                                                         |             |

|              |                  | nction Image™ Loading                                                   |             |

|              | 7.3.1            | FI Loading from Host Controller                                         |             |

|              | 7.3.2            | FI Loading from Serial Memory                                           |             |

|              |                  | vice Control                                                            |             |

|              | 7.4.1            | Normal Operation Overview                                               |             |

|              | 7.4.2            | Basic Tx and Rx Operation                                               |             |

|              | 7.4.3            | Device Configuration (Using the Programming Register)                   |             |

|              | 7.4.4<br>7.4.5   | Device Configuration (Using dedicated registers)<br>Interrupt Operation |             |

|              | 7.4.5            | Signal Control                                                          |             |

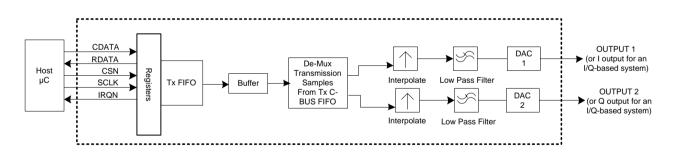

|              | 7.4.7            | Tx Mode Processing                                                      |             |

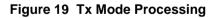

|              | 7.4.8            | Rx Mode Processing                                                      |             |

|              | 7.4.9            | Duplex Mode                                                             |             |

|              | 7.4.10           | Other Modes                                                             |             |

|              | 7.4.11           | Data Transfer                                                           |             |

|              | 7.4.12           | Sample Format                                                           |             |

|              | 7.4.13           | Data Buffering                                                          |             |

|              | 7.4.14           | Managing Data Transfer                                                  |             |

|              | 7.4.15           | GPIO Pin Operation                                                      |             |

|   | 7.4.16    | Auxiliary ADC Operation                   | 42 |

|---|-----------|-------------------------------------------|----|

|   | 7.4.17    | Auxiliary DAC/RAMDAC Operation            | 43 |

|   | 7.4.18    | SPI Thru-Port                             | 43 |

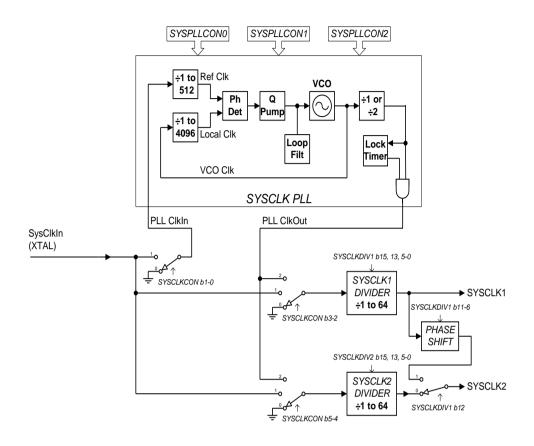

|   | 7.5 Di    | gital System Clock Generators             | 44 |

|   | 7.5.1     | Main Clock Operation                      | 44 |

|   | 7.5.2     | System Clock Operation                    | 44 |

|   | 7.6 Sig   | gnal Level Optimisation                   | 45 |

|   | 7.6.1     | Transmit Path Levels                      | 45 |

|   | 7.6.2     | Receive Path Levels                       | 46 |

|   | 7.7 Ap    | pplication Information                    | 46 |

|   | 7.7.1     | ADC and DAC Filters                       | 46 |

|   | 7.7.2     | ADC and DAC Sample Timing Synchronisation | 46 |

|   | 7.8 Co    | odec And Modem Mode Descriptions          |    |

|   | 7.8.1     | Codec Mode                                | 47 |

|   | 7.8.2     | Modem Mode                                | 48 |

|   | 7.9 C-    | BUS Register Summary                      | 49 |

| 8 | Performar | nce Specification                         | 50 |

|   | 8.1 Ele   | ectrical Performance                      | 50 |

|   | 8.1.1     | Absolute Maximum Ratings                  | 50 |

|   | 8.1.2     | Operating Limits                          | 50 |

|   | 8.1.3     | Operating Characteristics                 | 51 |

|   | 8.1.4     | Performance Characteristics               | 55 |

|   |           | BUS Timing                                |    |

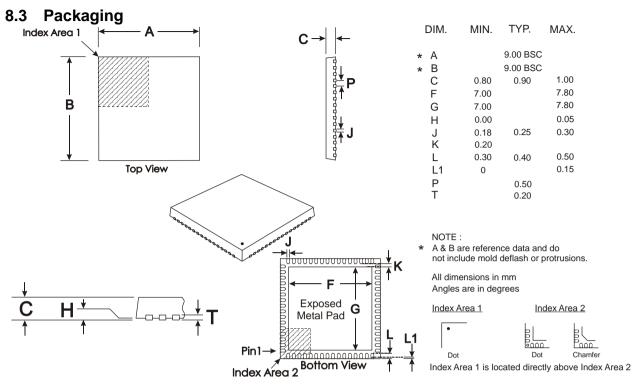

|   | 8.3 Pa    | ackaging                                  | 57 |

|   |           |                                           |    |

# Table

# <u>Page</u>

| nal/Pin List                                    | 7  |

|-------------------------------------------------|----|

| finition of Power Supply and Reference Voltages |    |

| OTEN Pin States                                 | 24 |

| O Transfer Summary                              |    |

| ADC1/ADC2 sample blocks                         |    |

| ADC1/ADC2, Phase/Magnitude sample blocks        |    |

| DAC1/DAC2 sample blocks                         |    |

| BUS Registers                                   |    |

# <u>Figure</u>

# <u>Page</u>

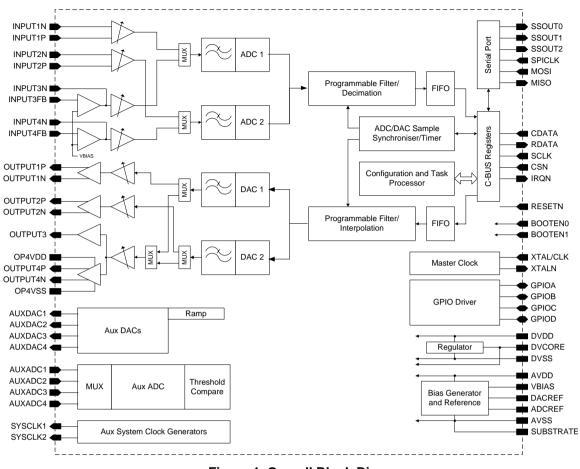

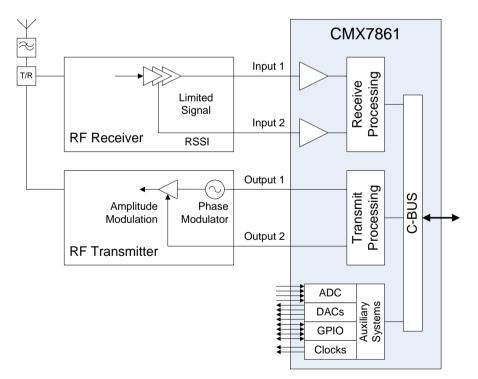

| Figure 1 | Overall Block Diagram                                                        | 6    |

|----------|------------------------------------------------------------------------------|------|

| Figure 2 | CMX7861 Power Supply and De-coupling                                         | . 10 |

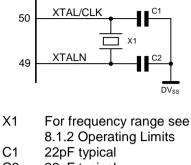

| Figure 3 | Recommended External Components - Xtal Interface                             | . 11 |

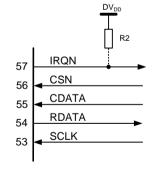

| Figure 4 | Recommended External Components - C-BUS Interface                            | . 11 |

| Figure 5 | Analogue Output Routing                                                      | . 13 |

| Figure 6 | Recommended External Components – I/Q Output Reconstruction Filter           | . 14 |

| Figure 7 | Recommended External Components - Single-ended Outputs Reconstruction Filter | . 14 |

| Figure 8 | Analogue Input Routing                                                       | . 15 |

| Figure 9 | Input Anti-alias FIIter: Inputs 1 and 2                                      | . 16 |

| Figure 1 | 0 Input Anti-alias FIIter: Inputs 3 and 4                                    | . 16 |

| Figure 1 | 1 CMX7861 Interface to Analogue Systems                                      | . 19 |

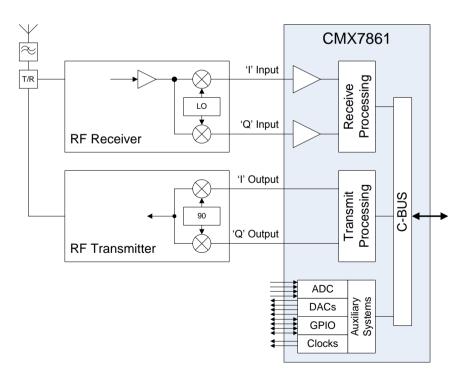

| Figure 1 | 2 CMX7861 I/Q Tx, I/Q Rx                                                     | . 19 |

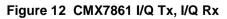

| Figure 13 | CMX7861 Two-point Tx, Classic FM Limiter-Discriminator Rx | 20   |

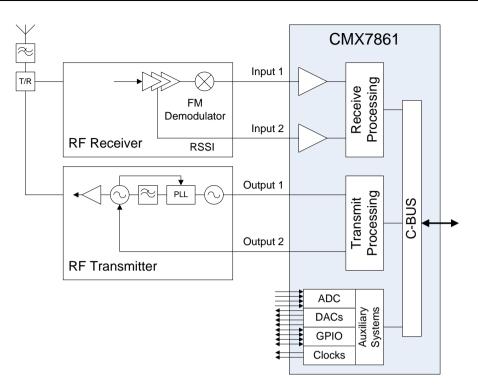

|-----------|-----------------------------------------------------------|------|

| Figure 14 | CMX7861 Polar Tx, Amplitude and Phase Rx                  | 20   |

| Figure 15 | Basic C-BUS Transactions                                  | . 22 |

| Figure 16 | C-BUS Data Streaming Operation                            | . 23 |

| Figure 17 | FI Loading from Host                                      | . 25 |

| -         | FI Loading from Serial Memory                             |      |

|           | Tx Mode Processing                                        |      |

|           | Rx Mode Processing                                        |      |

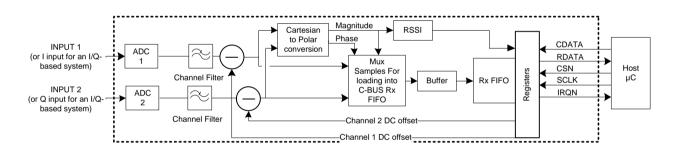

| Figure 21 | Constellation Diagram – no frequency or phase error       | . 34 |

| Figure 22 | Constellation Diagram – phase error                       | . 34 |

|           | Constellation Diagram – frequency error                   |      |

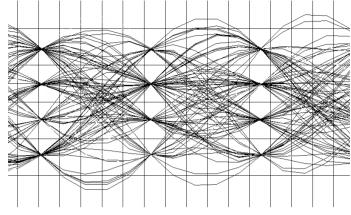

| Figure 24 | Received Eye Diagram                                      | . 35 |

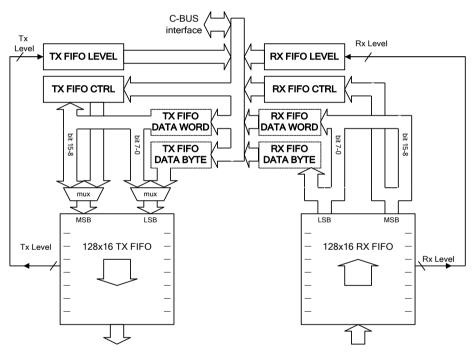

|           | Tx and Rx Data FIFOs                                      |      |

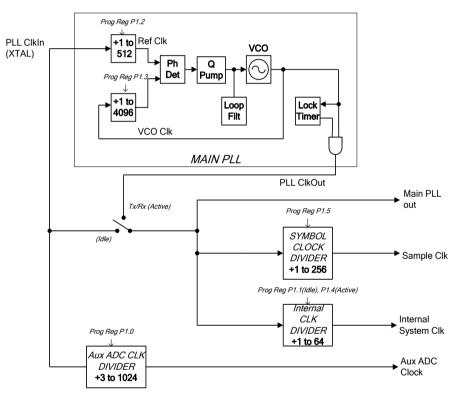

| Figure 26 | Main Clock Generation                                     | 44   |

| •         | Digital System Clock Generation Schemes                   |      |

|           | ADC/DAC Sample Timing Synchronisation                     |      |

|           | C-BUS Timing                                              |      |

| Figure 30 | Mechanical Outline of 64-pin VQFN (Q1)                    | . 57 |

Information in this datasheet should not be relied upon for final product design. It is always recommended that you check for the latest product datasheet version from the CML website: [www.cmlmicro.com].

# 1.3 History

| Version | Changes                                                                    | Date     |

|---------|----------------------------------------------------------------------------|----------|

|         |                                                                            |          |

| 2       | Note 32 expanded and Note 48 added in section 8.1.3, to cover dc operation | May 2012 |

| 1       | First issue                                                                | Dec 2011 |

# 2 Block Diagrams

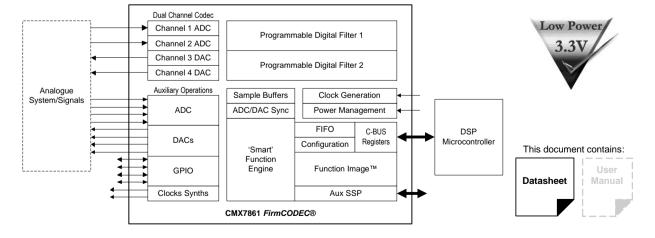

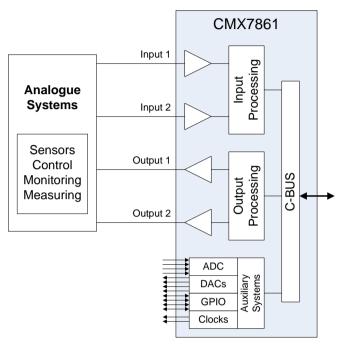

Figure 1 Overall Block Diagram

Figure 1 Illustrates the overall functionality of the CMX7861 and the auxiliary functions.

# 3 Signal/Pin List

| Pin | Pin Name | Туре  | Description                                                                                                                                                                                                                           |  |

|-----|----------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1   | GPIOB    | BI    | General Purpose I/O.                                                                                                                                                                                                                  |  |

| 2   | BOOTEN1  | IP+PU | The combined state of BOOTEN1 and BOOTEN2, upon RESET,                                                                                                                                                                                |  |

| 3   | BOOTEN2  | IP+PU | determine the Function Image™ load interface.                                                                                                                                                                                         |  |

| 4   | DVSS1    | PWR   | Negative supply rail (ground) for the digital on-chip circuits.                                                                                                                                                                       |  |

| 5   | DVDD1    | PWR   | 3.3V positive supply rail for the digital on-chip circuits. This pin should be decoupled to DVSS by capacitors mounted close to the device pin.                                                                                       |  |

| 6   | SSOUT2   | OP    | SPI: Slave Select Out 2                                                                                                                                                                                                               |  |

| 7   | RESETN   | IP    | Logic input used to reset the device (active low).                                                                                                                                                                                    |  |

| 8   | GPIOC    | BI    | General Purpose I/O.                                                                                                                                                                                                                  |  |

| 9   | GPIOD    | BI    | General Purpose I/O.                                                                                                                                                                                                                  |  |

| 10  | DVSS2    | PWR   | Negative supply rail (ground) for the digital on-chip circuits.                                                                                                                                                                       |  |

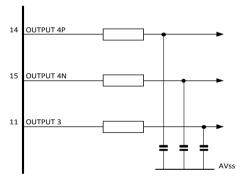

| 11  | OUTPUT3  | OP    | Single ended analogue signal output.                                                                                                                                                                                                  |  |

| 12  | AVDD1    | PWR   | Positive 3.3V supply rail for the analogue on-chip circuit. Levels and thresholds within the device are proportional to this voltage. This pin should be decoupled to AV <sub>SS</sub> by capacitors mounted close to the device pin. |  |

| 13  | OP4VSS   | PWR   | Negative supply rail (ground) for the on-chip speaker driver circuit.                                                                                                                                                                 |  |

| 14  | OUTPUT4P | OP    | Low impedance differential output speaker driver. Together these                                                                                                                                                                      |  |

| 15  | OUTPUT4N | OP    | are referred to as Output 4.                                                                                                                                                                                                          |  |

| 16  | OP4VDD   | PWR   | Positive supply rail for on-chip speaker driver circuit. Levels and thresholds within the device are proportional to this voltage. This pin should be decoupled to OP4VSS by capacitors mounted close to the device pin.              |  |

| 17  | OUTPUT1P | OP    | Differential outputs; 'P' is positive, 'N' is negative. Together these are referred to as Output 1. Can also be used as the 'I' output in                                                                                             |  |

| 18  | OUTPUT1N | OP    | an I/Q based system.                                                                                                                                                                                                                  |  |

| 19  | OUTPUT2P | OP    | Differential outputs; 'P' is positive, 'N' is negative. Together these                                                                                                                                                                |  |

| 20  | OUTPUT2N | OP    | <ul> <li>are referred to as Output 2. Can also be used as the 'Q' output in<br/>an I/Q based system.</li> </ul>                                                                                                                       |  |

| 21  | AVSS2    | PWR   | Negative supply rail (ground) for the analogue on-chip circuits                                                                                                                                                                       |  |

| 22  | DACREF   | PWR   | DAC reference voltage, connect to AVss.                                                                                                                                                                                               |  |

| 23  | INPUT3N  | IP    | Negative input 'N' and feedback 'FB' connections to a single                                                                                                                                                                          |  |

| 24  | INPUT3FB | OP    | ended amplifier. Together these are referred to as Input 3. Gain and filtering circuitry can be constructed around these pins.                                                                                                        |  |

# Table 1 Signal/Pin List

$\ensuremath{\textcircled{}^{\circ}}$  2012 CML Microsystems Plc

| Pin | Pin Name | Туре | Description                                                                                                                                                                                                                                                                     |  |

|-----|----------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 25  | INPUT4N  | IP   | Negative input 'N' and feedback 'FB' connections to a single                                                                                                                                                                                                                    |  |

| 26  | INPUT4FB | OP   | ended amplifier. Together these are referred to as Input 4. Gain and filtering circuitry can be constructed around these pins.                                                                                                                                                  |  |

| 27  | VBIAS    | OP   | Internally generated bias voltage of approximately AV <sub>DD</sub> /2. If V <sub>BIAS</sub> is powersaved this pin will be connected via a high impedance to AV <sub>DD</sub> . This pin must be decoupled to AV <sub>SS</sub> by a capacitor mounted close to the device pin. |  |

| 28  | INPUT1P  | IP   | Differential inputs; 'P' is positive, 'N' is negative. Together these                                                                                                                                                                                                           |  |

| 29  | INPUT1N  | IP   | are referred to as Input 1. Can also be used as the 'I' Input in an I/Q based system.                                                                                                                                                                                           |  |

| 30  | ADCREF   | PWR  | ADC reference voltage, connect to AV <sub>SS.</sub>                                                                                                                                                                                                                             |  |

| 31  | INPUT2P  | IP   | Differential inputs; 'P' is positive, 'N' is negative. Together these                                                                                                                                                                                                           |  |

| 32  | INPUT2N  | IP   | are referred to as Input 2. Can also be used as the 'Q' Input in an I/Q based system.                                                                                                                                                                                           |  |

| 33  | AUXADC1  | IP   |                                                                                                                                                                                                                                                                                 |  |

| 34  | AUXADC2  | IP   | Auxiliary ADC inputs multiplexed to a single ADC with Threshold                                                                                                                                                                                                                 |  |

| 35  | AUXADC3  | IP   | and Compare operations.                                                                                                                                                                                                                                                         |  |

| 36  | AUXADC4  | IP   |                                                                                                                                                                                                                                                                                 |  |

| 37  | AVDD3    | PWR  | Positive 3.3V supply rail for the analogue on-chip circuit. Levels and thresholds within the device are proportional to this voltage. This pin should be decoupled to $AV_{SS}$ by capacitors mounted close to the device pin.                                                  |  |

| 38  | AVSS3    | PWR  | Negative supply rail (ground) for the analogue on-chip circuits.                                                                                                                                                                                                                |  |

| 39  | AUXDAC1  | OP   |                                                                                                                                                                                                                                                                                 |  |

| 40  | AUXDAC2  | OP   | Auxiliary DAC outputs with DAC1 output having an optional                                                                                                                                                                                                                       |  |

| 41  | AUXDAC3  | OP   | ramping RAMDAC operation.                                                                                                                                                                                                                                                       |  |

| 42  | AUXDAC4  | OP   |                                                                                                                                                                                                                                                                                 |  |

| 43  | DVSS3    | PWR  | Negative supply rail (ground) for the digital on-chip circuits                                                                                                                                                                                                                  |  |

| 44  | DVCORE1  | PWR  | Digital core supply, nominally 1.8V. This pin should be decoupled to $DV_{SS}$ by capacitors mounted close to the device pins and connected with a power supply track to DVCORE2.                                                                                               |  |

| 45  | DVDD2    | PWR  | 3.3V positive supply rail for the digital on-chip circuits. This pin should be decoupled to $DV_{SS}$ by capacitors mounted close to the device pin.                                                                                                                            |  |

| 46  | NC       | NC   | Do not connect.                                                                                                                                                                                                                                                                 |  |

| 47  | DVSS4    | PWR  | Negative supply rail (ground) for the digital on-chip circuits.                                                                                                                                                                                                                 |  |

| 48  | DVSS5    | PWR  | Negative supply rail (ground) for the digital on-chip circuits.                                                                                                                                                                                                                 |  |

| 49  | XTALN    | OP   | Output of the on-chip Xtal oscillator inverter.                                                                                                                                                                                                                                 |  |

| 50  | XTAL/CLK | IP   | Input to the oscillator inverter from the Xtal circuit or external clock source.                                                                                                                                                                                                |  |

| 51  | SYSCLK1  | OP   | Synthesised digital clock output 1.                                                                                                                                                                                                                                             |  |

$\ensuremath{\textcircled{}^\circ}$  2012 CML Microsystems Plc

| Pin                     | Pin Name  | Туре  | Description                                                                                                                                                                                                                  |  |

|-------------------------|-----------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 52                      | SYSCLK2   | OP    | Synthesised digital clock output 2.                                                                                                                                                                                          |  |

| 53                      | SCLK      | IP    | C-BUS serial clock input from the µC.                                                                                                                                                                                        |  |

| 54                      | RDATA     | TS OP | Three-state C-BUS serial data output to the $\mu$ C. This output is high impedance when not sending data to the $\mu$ C.                                                                                                     |  |

| 55                      | CDATA     | IP    | C-BUS serial data input from the $\mu$ C.                                                                                                                                                                                    |  |

| 56                      | CSN       | IP    | C-BUS chip select input from the $\mu$ C.                                                                                                                                                                                    |  |

| 57                      | IRQN      | OP    | 'wire-Orable' output for connection to the Interrupt Request input of the $\mu$ C. This output is pulled down to DV <sub>SS</sub> when active and is high impedance when inactive. An external pull-up resistor is required. |  |

| 58                      | DVCORE2   | PWR   | Digital core supply, nominally 1.8V. This pin should be decoupled to $DV_{SS}$ by capacitors mounted close to the device pins, and connected, with a power supply track, to DVCORE1.                                         |  |

| 59                      | MOSI      | OP    | SPI: Master Out Slave In.                                                                                                                                                                                                    |  |

| 60                      | SSOUT1    | OP    | SPI: Slave Select Out 1.                                                                                                                                                                                                     |  |

| 61                      | MISO      | IP    | SPI: Master In Slave Out.                                                                                                                                                                                                    |  |

| 62                      | SSOUT0    | OP    | SPI: Slave Select Out 0.                                                                                                                                                                                                     |  |

| 63                      | SPICLK    | OP    | SPI: Serial Clock.                                                                                                                                                                                                           |  |

| 64                      | GPIOA     | BI    | General Purpose I/O.                                                                                                                                                                                                         |  |

| Exposed<br>Metal<br>Pad | SUBSTRATE | ~     | On this device, the central metal pad may be electrically unconnected or, alternatively, may be connected to analogue ground (AVss). No other electrical connection is permitted.                                            |  |

IP Notes: = Input (+ PU/PD = internal pull-up / pull-down resistor of approximately  $75k\Omega$ )

- =

- OP Output BI Bidirectional

- = TS OP =

- Three-state Output PWR Power Connection =

- NC

- = No Connection - should NOT be connected to any signal

# 3.1 Power Supply Signal Definitions

# Table 2 Definition of Power Supply and Reference Voltages

| Signal Name                          | Pin name                                                       | Usage                                                       |  |

|--------------------------------------|----------------------------------------------------------------|-------------------------------------------------------------|--|

| AV <sub>DD</sub> AVDD1, AVDD2, AVDD3 |                                                                | Power supply for analogue circuits                          |  |

| DV <sub>DD</sub> DVDD1, DVDD2        |                                                                | Power supply for digital circuits, nominally 3.3V           |  |

| DV <sub>core</sub> DVCORE1, DVCORE2  |                                                                | Power for digital core voltage of approximately 1.8V        |  |

| V <sub>BIAS</sub>                    | VBIAS                                                          | CMX7861 generated bias voltage of approximately $AV_{DD}/2$ |  |

| DV <sub>SS</sub>                     | DVSS1, DVSS2, DVSS3,<br>DVSS4, DVSS5                           | Ground for digital circuits                                 |  |

| AV <sub>SS</sub>                     | AVSS1, AVSS2, AVSS3,<br>SUBSTRATE (Optional)<br>DACREF, ADCREF | Ground for analogue circuits                                |  |

#### **Digital Ground Plane** C-BUS CORF3 SYSCLK2 SYSCI K SOLT SCLK RDAT CCI DA<sup>7</sup> ŝ Active low reset from supervisory IC or RC circuit 64 63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 GPIOE DVSS5 48 BOOTEN1 DVSS4 47 2 DVDD DV BOOTEN2 NC 3 46 DVss DVSS1 DVDD2 45 DVDD1 DVCORE1 44 5 C 28 C22 SSOUT2 DVSS3 + C20 C21 CMX7861Q1 43 6 RESETN AUXDAC4 42 GPIOC DV AUXDAC3 41 8 GPIOD AUXDAC2 40 9 **DV**<sub>SS</sub> DVSS2 AUXDAC1 10 39 \_\_\_\_\_ OUTPUT3 AVSS3 38 11 AVDD1 AVDD3 12 37 OP4VSS AUXADC4 C23 C24 13 36 OUTPUT4P AUXADC3 :29 C30 14 35 OUTPUT4N AUXADC2 15 34 AVs OP4VDD AUXADC1 16 33 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 17 OUTPUT1P AVSS2 OUTPUT1N VBIAS INPUT1P **OUTPUT2P OUTPUT2N** INPUT1N **NPUT3N** NPUT4N **NPUT4FE** ADCREF NPUT2F DACREF NPUT3FE NPUT2N Analogue Ground Plane AV

# 4 PCB Layout Guidelines and Power Supply Decoupling

| C20 | 10µF | C26 | 22µF  |

|-----|------|-----|-------|

| C21 | 10nF | C27 | 10nF  |

| C22 | 10nF | C28 | 10nF  |

| C23 | 10µF | C29 | 10µF  |

| C24 | 10nF | C30 | 10nF  |

| C25 | 10nF | C31 | 100nF |

# Figure 2 CMX7861 Power Supply and De-coupling

# Notes:

To achieve good noise performance,  $AV_{DD}$  and  $V_{BIAS}$  decoupling and protection of the receive path from extraneous in-band signals is very important. It is recommended that the printed circuit board is laid out with a ground plane in the CMX7861 analogue area to provide a low impedance connection between the  $AV_{SS}$  pins and the  $AV_{DD}$  and  $V_{BIAS}$  decoupling capacitors.

# 5 External Components

# 5.1 Xtal Interface

C2 22pF typical

# Figure 3 Recommended External Components - Xtal Interface

Notes:

The clock circuit can operate with either a Xtal or external clock generator. If using an external clock generator it should be connected to the XTAL/CLK pin and the Xtal and other components are not required. For external clock generator frequency range see 8.1.2 Operating Limits. When using an external clock generator the Xtal oscillator circuit may be disabled to save power, see 9.2.3 Program Block 1 – Clock Control for details. Also refer to section 7.1 Xtal Frequency.

The tracks between the Xtal and the device pins should be as short as possible to achieve maximum stability and best start up performance. It is also important to achieve a low impedance connection between the Xtal capacitors and the ground plane.

The  $DV_{SS}$  to the Xtal oscillator capacitors C1 and C2 should be of low impedance and preferably be part of the  $DV_{SS}$  ground plane to ensure reliable start up. For correct values of capacitors C1 and C2 refer to the documentation of the Xtal used.

# 5.2 C-BUS Interface

R2 10kΩ - 100kΩ

# Note:

If the IRQN line is connected to other compatible pull-down devices only one pull-up resistor is required on the IRQN node.

Figure 4 Recommended External Components - C-BUS Interface

```

© 2012 CML Microsystems Plc

```

# 5.3 Signal Output

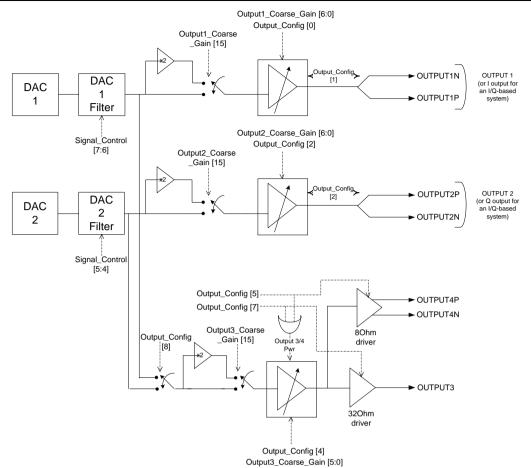

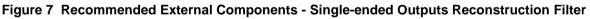

# 5.3.1 Output Signal Routing

The CMX7861 has four possible analogue outputs:

- Differential output 1 OUTPUT1P and OUTPUT1N (or I output for an I/Q-based system)

- Differential output 2 OUTPUT2P and OUTPUT2N (or Q output for an I/Q-based system)

- Single-ended output 3 OUTPUT3 that can drive headset/earpieces

- Differential output 4 OUTPUT4P and OUTPUT4N a low-impedance speaker driver

The CMX7861's two DACs (DAC 1 and DAC 2) can output analogue waveforms on any or all of these four outputs. CMX7861 allows us to connect the two DACs to any of the four analogue outputs.

Due to the highly-flexible nature of the CMX7861 and the multitude of input and output configurations, it is important to clearly understand the differences between Pin/Signal names, and the internal signal streams controlled by most of the registers. To help clarify this situation, the following convention has been used throughout the text and on diagrams within this document:

- •Outputs from the device to external systems will be referred to as OUTPUT1, 2, 3, or 4. Where appropriate, OUTPUT 1 and 2 may also be referred to as I and Q outputs respectively (if the description is specifically for an I/Q-based system).

- •Internal signal streams routed to the four outputs and processed by the two DACs will be referred to as DAC1 and/or DAC2 samples.

Figure 5 Analogue Output Routing, shows the analogue output signal routing and control.

Figure 5 Analogue Output Routing

The registers that control analogue output signal routing are described in the following sections:

- 9.1.10 Signal Control \$61 write

- 9.1.21 Output 1 4 Configuration \$B3 write

- 9.1.22 Output 1 and 2 Coarse Gain \$B4, \$B5 write

- Include Output3 coarse gain register here when it is defined

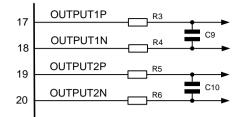

# 5.3.2 Output Reconstruction Filter – (I/Q mode)

When output 1 (or I) and output 2 (or Q) are used as I/Q outputs, internal reconstruction filtering is provided with four selectable bandwidths (-3dB point shown in section 9.1.21). The bandwidth of the internal reconstruction filter may be selected using the Output 1 - 4 Configuration - \$B3 write or Signal Control - \$61 write registers.

To complete the output reconstruction filter one of the following external RC networks should be used for each of the differential outputs. The external RC network should have a bandwidth that matches the bandwidth of the selected internal reconstruction filter.

| Bandwidth (kHz) | R3-R6 (kOhms) | C9-C10 (pF) |

|-----------------|---------------|-------------|

| 100             | 22            | 33          |

| 50              | 20            | 75          |

| 25              | 22            | 150         |

| 12.5            | 22            | 270         |

# Figure 6 Recommended External Components – I/Q Output Reconstruction Filter

When transmitting an I/Q signal, each I/Q output will produce a signal with bandwidth half the channel bandwidth. A reconstruction filter with a -3dB point close to half the channel bandwidth will therefore have significant roll off within the channel bandwidth – which is undesirable. An appropriate choice for channels occupying up to a 12.5kHz bandwidth (channel bandwidth/2 = 6.25kHz) would be a reconstruction filter of 12.5kHz bandwidth.

# 5.3.3 Output Reconstruction Filter – Single-ended Outputs

To complete the output reconstruction filter one of the following external RC networks should be used for each of the single-ended outputs. The external RC network should have a bandwidth that matches the bandwidth of the selected internal reconstruction.

# 5.4 Signal Input

# 5.4.1 Input Signal Routing

The CMX7861 has four possible analogue input paths:

- Differential input 1 INPUT1P and INPUT1N (or I input for an I/Q-based system)

- Differential input 2 INPUT2P and INPUT2N (or Q input for an I/Q-based system)

- Single-ended input 3 INPUT3N and INPUT3FB

- Single-ended input 4 INPUT4N and INPUT4FB

Due to the highly-flexible nature of the CMX7861 and the multitude of input and output configurations, it is important to clearly understand the differences between Pin/Signal names, and the internal signal streams controlled by most of the registers. To help clarify this situation, the following convention has been used throughout the text and on diagrams within this document:

- •Inputs to the device from external systems will be referred to as INPUT1, 2, 3, or 4. Where appropriate, INPUT 1 and 2 may also be referred to as I and Q inputs respectively (if the description is specifically for an I/Q-based system).

- •Internal signal streams routed from the four inputs and processed by the two ADCs will be referred to as ADC1 and/or ADC2 samples.

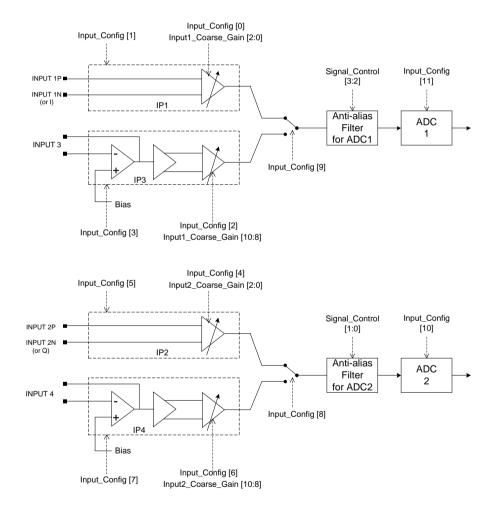

Figure 8 Analogue Input Routing, shows the analogue input signal routing and control.

Figure 8 Analogue Input Routing

The registers that control analogue input signal routing are described in the following sections:

- 9.1.10 Signal Control \$61 write

- 9.1.19 Input 1 4 Configuration \$B0 write

- 9.1.20 Input 1-4 Coarse Gain \$B1, \$B2 write

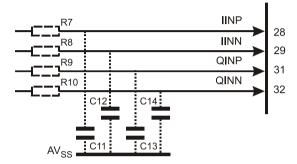

#### 5.4.2 Input Anti-alias Filter (I/Q mode)

When Input 1 (I) and Input 2 (Q) are used as the inputs to ADCs 1 and 2, the device has a programmable anti-alias filter in the input path, which is controlled using the Input 1 - 4 Configuration - \$B0 write or Signal Control - \$61 write registers. This should be sufficient for most applications, however if additional filtering is required it can be done at the input to the device.

Figure 9 Input Anti-alias Filter: Inputs 1 and 2

The input impedance of pins 28 to 32 varies with the input gain setting, approx 14kOhm at +22.4dB rising to 100kOhm at 0dB. The output impedance of the circuit driving the inputs shown above should be no more than approximately 1kOhm, for the above RC network R7-10 <= approx. 1kOhm. Recommended values for R7-10 and C11-14 will depend on the filtering required.

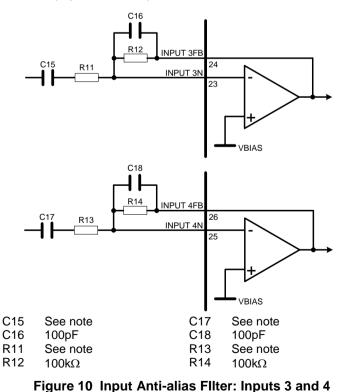

#### 5.4.3 Input Anti-alias Filter (Inputs 3 and 4)

Notes:

Assuming R12 and R14 at 100kOhm, R11 and R13 should be selected to provide the required dc gain (assuming C15 and C17 are not present) as follows:

$$|GAIN_{AUDIO1}| = 100k\Omega / R11$$

$|GAIN_{AUDIO2}| = 100k\Omega / R13$

The gain should be such that the resultant output at the pins is within the input signal range.

C15 and C17 should be selected to maintain the lower frequency roll-off of the AUDIO inputs as follows:

$$\begin{array}{l} C15 \geq 0.1 \mu F \times \left| \text{GAIN}_{AUDIO1} \right| \\ C17 \geq 0.1 \mu F \times \left| \text{GAIN}_{AUDIO2} \right| \end{array}$$

The High Frequency cut off = ~ 16KHz

$$\left(\frac{1}{2\pi . R_{14}C_{18}}\right)$$

The Low Frequency cut off =  $\sim 16$  Hz

$$\left(\frac{1}{2\pi . R_{13}C_{17}}\right)$$

# 6 General Description

# 6.1 CMX7861 Features

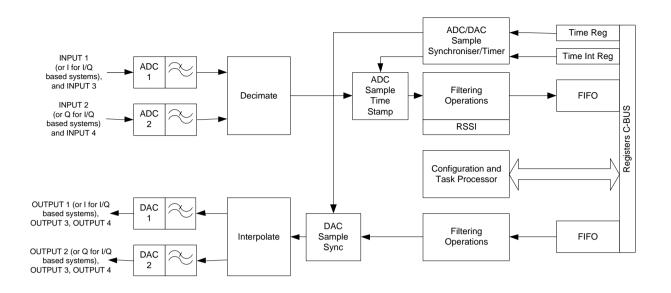

The CMX7861 *FirmCODEC*<sup>®</sup> is a general-purpose, dual-channel baseband interface device for use in DSP-based systems and supports duplex operation of two ADC and two DAC channels. Flexibility is the key to the device with target applications being sensors, control and monitoring systems and providing an interface to RF systems.

The device is highly configurable with selectable single-ended and differential inputs and outputs plus the ability to operate in I/Q mode.

A flexible power control facility allows the device to be placed in its optimum powersave mode when not actively processing signals.

On-chip auxiliary functions include: an Xtal clock generator with phase locked loop and buffered output to provide a system clock output (if required) for other devices, a multiplexed input ADC, DAC outputs and GPIO.

Fully-programmable on-chip digital channel filters can be used for signal conditioning purposes prior to passing data to the host DSP. The C-BUS/SPI master interface expands host C-BUS/SPI ports to control external devices.

Block diagrams of the device are shown in section 2.

Note: In the list below, the greyed-out text indicates future planned updates

#### **Tx Functions:**

- Single-ended and differential analogue outputs

- Interpolation stage with filtering providing pulse shape filtering for mapped symbols

- RAMDAC capability for PA ramping control

- Tx trigger feature allowing precise control of burst start time

- Tx burst sequence for automatic RAMDAC ramp and Tx hardware switching

#### Rx Functions:

- Single-ended and differential analogue inputs

- Rx channel filtering

- Received signal strength indication (RSSI)

- I/Q and Phase/Magnitude output formats for FM systems

- AGC using SPI Thru-Port

# Auxiliary Functions:

- Two programmable system clock outputs

- Auxiliary ADC with four selectable input paths

- SPI Thru-Port for interfacing to synthesisers, a Cartesian loop IC (CMX998) and/or other seriallycontrollable devices

- Four auxiliary DACs, one with built-in programmable RAMDAC

#### Interface:

- Optimised C-BUS (4-wire, high-speed synchronous serial command/data bus) interface to host for control and data transfer, including streaming C-BUS for efficient data transfer

- Open drain IRQ to host

- Four GPIO pins

- Tx trigger input (provided by GPIOA)

- Serial memory or C-BUS (host) boot mode

# 6.2 Signal Interfaces

The CMX7861 *FirmCODEC* IC can be used to provide any interface the user requires depending on the data supplied to the device. Typical interfaces are baseband, I/Q and phase/magnitude.

Figure 11 CMX7861 Interface to Analogue Systems

Figure 13 CMX7861 Two-point Tx, Classic FM Limiter-Discriminator Rx

Figure 14 CMX7861 Polar Tx, Amplitude and Phase Rx

# 7 Detailed Descriptions

# 7.1 Xtal Frequency

The CMX7861 is designed to work with a Xtal, or an external frequency oscillator within the ranges specified in section 8.1.3 Operating Characteristics. Program Block 1 (see User Manual) must be loaded with the correct values to ensure that the device will work to specification with the user-selected clock frequency. A table of configuration values can be found in Table 17 Xtal/Clock Frequency Settings for Program Block 1, supporting sample rates up to 144k samples per second when the Xtal frequency is 9.6MHz or the external oscillator frequency is 9.6 or 19.2 MHz. Rates other than those tabulated (within this range) are possible, see section 9.2.3 Program Block 1 – Clock Control. Further information can be provided on request. The accuracy of the sample rates provided is affected by the accuracy of the Xtal or oscillator used.

# 7.2 Host Interface

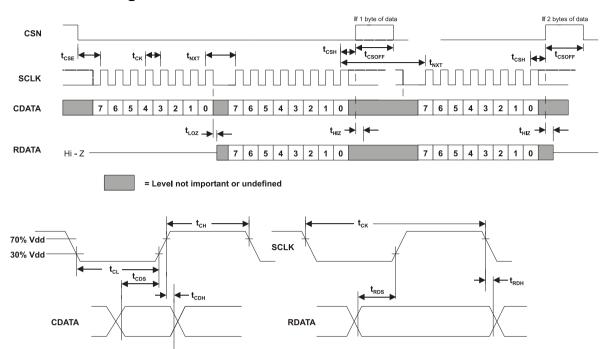

A serial data interface (C-BUS) is used for command, status and data transfers between the CMX7861 and the host  $\mu$ C; this interface is compatible with Microwire<sup>TM</sup>, SPI<sup>TM</sup> and other similar interfaces. Interrupt signals notify the host  $\mu$ C when a change in status has occurred; the  $\mu$ C should read the IRQ Status register across the C-BUS and respond accordingly. Interrupts only occur if the appropriate mask bit has been set, see 7.4.5 Interrupt Operation.

# 7.2.1 C-BUS Operation

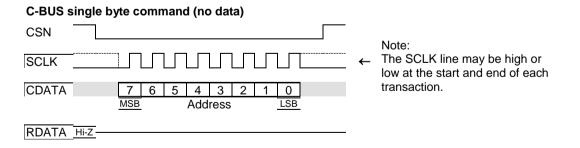

This block provides for the transfer of data and control or status information between the CMX7861 internal registers and the host  $\mu$ C over the C-BUS serial bus. Single register transactions consist of a single register address byte sent from the  $\mu$ C, which may be followed by a data word sent from the  $\mu$ C to be written into one of the CMX7861's write-only registers, or a data word read out from one of the CMX7861's read-only registers. Streaming C-BUS transactions consist of a single register address byte followed by many data bytes being written to or read from the CMX7861. All C-BUS data words are a multiple of 8 bits wide, the width depending on the source or destination register. Note that certain C-BUS transactions require only an address byte to be sent from the  $\mu$ C, no data transfer being required. The operation of the C-BUS is illustrated in Figure 15.

Data sent from the  $\mu$ C on the CDATA (command data) line is clocked into the CMX7861 on the rising edge of the SCLK input. Data sent from the CMX7861 to the  $\mu$ C on the RDATA (reply data) line is valid when SCLK is high. The CSN line must be held low during a data transfer and kept high between transfers. The C-BUS interface is compatible with most common  $\mu$ C serial interfaces and may also be easily implemented with general purpose  $\mu$ C I/O pins controlled by a simple software routine. Section 8.2 C-BUS Timing gives detailed C-BUS timing requirements.

Note that, due to internal timing constraints, there may be a delay of up to 60µs between the end of a C-BUS write operation and the device reading the data from its internal register.

| CSN                   |                                                                                                                                                                                                                                |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCLK                  |                                                                                                                                                                                                                                |

| CDATA                 | 7         6         5         4         3         2         1         0         n-1         n-2         n-3         2         1         0           MSB         Address         LSB         MSB         Write data         LSB |

| RDATA                 | <u>Hi-Z</u>                                                                                                                                                                                                                    |

| <b>C-BUS</b> r<br>CSN | n-bit register read                                                                                                                                                                                                            |

| SCLK                  |                                                                                                                                                                                                                                |

| CDATA                 | 7         6         5         4         3         2         1         0           MSB         Address         LSB                                                                                                              |

| RDATA                 | Hi-Z         n-1         n-2         n-3         2         1         0           MSB         Read data         LSB                                                                                                             |

|                       | Data value unimportant                                                                                                                                                                                                         |

|                       | Repeated cycles                                                                                                                                                                                                                |

|                       | Either logic level valid (and may change)                                                                                                                                                                                      |

|                       | Either logic level valid (but must not change from low to high)                                                                                                                                                                |

#### C-BUS n-bit register write

#### Figure 15 Basic C-BUS Transactions

To increase the data bandwidth between the  $\mu$ C and the CMX7861, certain of the C-BUS read and write registers are capable of data-streaming operation. This allows a single address byte to be followed by the transfer of multiple read or write data words, all within the same C-BUS transaction. This can significantly increase the transfer rate of large data blocks, as shown in Figure 16.

# Example of C-BUS data-streaming (8-bit write register)

| CSN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| CDATA         7         6         5         4         3         2         1         0         7         6         5         4         3         2         1         0         7         6         5         4         3         2         1         0         7         6         5         4         3         2         1         0         7         6         5         4         3         2         1         0         7         6         5         4         3         2         1         0         7         6         5         4         3         2         1         0         7         6         5         4         3         2         1         0         7         6         5         4         3         2         1         0         7         6         5         4         3         2         1         0         7         6         5         4         3         2         1         0         7         6         5         4         3         2         1         0         7         6         5         4         3         2         1         0         7         6 |

| RDATA Hi-Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Example of C-BUS data-streaming (8-bit read register) CSN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| CDATA     7     6     5     4     3     2     1     0       Address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| RDATA       Hi-Z       7       6       5       4       3       2       1       0       7       6       5       4       3       2       1       0       7       6       5       4       3       2       1       0       7       6       5       4       3       2       1       0       7       6       5       4       3       2       1       0       7       6       5       4       3       2       1       0       7       6       5       4       3       2       1       0       7       6       5       4       3       2       1       0       7       6       5       4       3       2       1       0       7       6       5       4       3       2       1       0       7       6       5       4       3       2       1       0       7       6       5       4       3       2       1       0       7       6       5       4       3       2       1       0       7       6       5       4       3       2       1       0       7       6       5       4       3<                                                                                                                 |

| Data value unimportant                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Repeated cycles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Either logic level valid (and may change)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Either logic level valid (but must not change from low to high)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Figure 16 C-BUS Data Streaming Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

Notes:

- 1. For Command byte transfers only the first 8 bits are transferred (\$01 = Reset)

- 2. For single byte data transfers only the first 8 bits of the data are transferred

- 3. The CDATA and RDATA lines are never active at the same time. The address byte determines the data direction for each C-BUS transfer.

- 4. The SCLK can be high or low at the start and end of each C-BUS transaction

- 5. The gaps shown between each byte on the CDATA and RDATA lines in the above diagram are optional, the host may insert gaps or concatenate the data as required.

# 7.3 Function Image<sup>™</sup> Loading

The Function Image<sup>™</sup> (FI), which defines the operational capabilities of the device, may be obtained from the CML Technical Portal, following registration and authorisation. This is in the form of a 'C' header file which can be included into the host controller software or programmed into an external serial memory. The Function Image<sup>™</sup> size will not exceed 128kbytes, although a typical FI will be considerably less than this. Note that the BOOTEN1/2 pins are only read at power-on, when the RESETN pin goes high, or following a C-BUS General Reset, and must remain stable throughout the FI loading process. Once the FI load has completed, the BOOTEN1/2 pins are ignored by the CMX7861 until the next power-up or Reset.

The BOOTEN1 and BOOTEN2 pins are both fitted with internal low-current pull-up devices.

For serial memory load operation, BOOTEN2 should be pulled low by connecting it to DV<sub>ss</sub> either directly or via a 47k resistor (see Table 3).

Whilst booting, the boot loader will return the checksum of each block loaded in the C-BUS Rx Data FIFO. The checksums can be verified against the values provided with the FI to ensure that the FI has loaded correctly.

Once the FI has been loaded, the CMX7861 performs these actions:

- (1) The product identification code (\$7861) is reported in the C-BUS Rx Data FIFO

- (2) The FI version code is reported in the C-BUS Rx Data FIFO.

|                    | BOOTEN2 | BOOTEN1 |

|--------------------|---------|---------|

| C-BUS host load    | 1       | 1       |

| reserved           | 1       | 0       |

| Serial memory load | 0       | 1       |

| reserved           | 0       | 0       |

# Table 3 BOOTEN Pin States

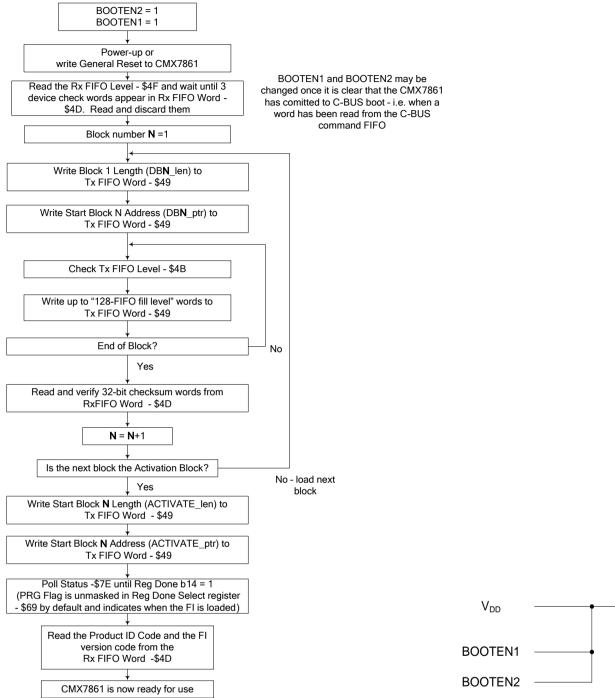

# 7.3.1 FI Loading from Host Controller

The FI can be included into the host controller software build and downloaded into the CMX7861 at power-up over the C-BUS interface, using the Tx FIFO. For Function Image<sup>™</sup> load, the FIFO accepts raw 16-bit Function Image<sup>™</sup> data (using the Tx FIFO Word) - \$49 write register, there is no need for distinction between control and data fields. The BOOTEN1/2 pins must be set to the C-BUS load configuration, the CMX7861 powered or reset, and then data can then be sent directly over the C-BUS to the CMX7861.

If the host detects a brownout, the BOOTEN1 and BOOTEN2 pins should be set to re-load the FI. A General Reset should then be issued or the RESETN pin used to reset the CMX7861 and the appropriate FI load procedure followed.

Streaming C-BUS may be used to load the Tx FIFO Word - \$49 write register with the Function Image<sup>™</sup>, and the Tx FIFO Level - \$4B read register used to ensure that the FIFO is not allowed to overflow during the load process.

The download time is limited by the clock frequency of the C-BUS; with a 5MHz SCLK it should take less than 250ms to complete even when loading the largest possible Function Image™.

CMX7861

CMX7861 FirmCODEC® Programmable Baseband Interface

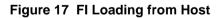

#### 7.3.2 FI Loading from Serial Memory

The FI must be converted into a format for the serial memory programmer (normally Intel Hex) and loaded into the serial memory either by the host or an external programmer. The serial memory should contain the same data stream as written to the Command FIFO shown in Figure 17. The most significant byte of each 16-bit word should be stored first in serial memory.

The serial memory should be interfaced to the CMX7861 SPI Thru-Port using SSOUT0 as the chip select. The CMX7861 needs to have the BOOTEN pins set to Serial Memory Load, and then on power-on following the RESETN pin becoming high, or following a C-BUS General Reset, the CMX7861 will automatically load the data from the serial memory without intervention from the host controller.

#### Figure 18 FI Loading from Serial Memory

The CMX7861 has been designed to function with the AT25F512 serial flash device, however other manufacturers' parts may also be suitable. The time taken to load the FI should be less than 500ms even when loading the largest possible Function Image<sup>™</sup>.

# 7.4 Device Control

Once the Function Image<sup>™</sup> is loaded, the CMX7861 can be set into one of four main modes using the Mode Register- \$6B write register:

- Idle mode for configuration or low power operation

- Transmit mode DAC operating

- Receive mode ADC operating