## The Leader in High Temperature Semiconductor Solutions

## **CHT-CG50LP DATASHEET**

Version: 1.6

# High-Temperature, Low-Power, Versatile Clock Generator

#### **General Description**

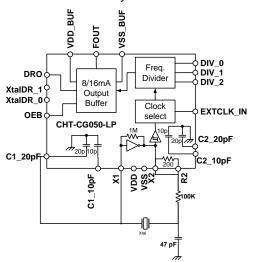

The CHT-CG50LP is a versatile, low-power high-temperature crystal clock generator with low pin count. Compared to CISSOID' industry standard CHT-CG50, the CHT-CG50LP has been optimized for lower power consumption, smaller die size while offering extra features such as built-in frequency division.

The chip features a programmable crystal oscillator driver with an enable/disable control signal, an external clock input and a frequency divider selectable from 1 to 512. Using an external crystal, it is intended to provide reliable precision performance throughout the -55 to +225°C temperature range for supply voltages between 3.3V and 5V.

The CHT-CG50LP can operate with crystals from 1MHz to 50MHz. It can also be used with 32.758kHz crystal for real time clock needs.

The output frequency can be selected by means of a programmable divider, providing division factors of 1, 2, 4, 8, 16, 32, 256 and 512. The programmability of the crystal driver allows working with a wide range of crystals. An output enable pin (OEB) is also included to put the output in high impedance mode. In applications requiring only a precision divider chain - where an external clock source is already present - the crystal driver may be bypassed via the input EXTCLK\_IN.

#### **Features**

- Power supply:

- 5V +/-10% (1MHZ 50MHz)

- o 3.3V +/-10% (1MHZ 30MHz)

- Qualified from -55 to +225°C (Tj)

- Two input sources: crystal (1 to 50 MHz), external clock (DC to 50MHz)

- Operates with 32.768kHz crystals

- Programmable frequency divider: F<sub>in</sub>, F<sub>in</sub>/2, F<sub>in</sub>/4, F<sub>in</sub>/8, F<sub>in</sub>/16, F<sub>in</sub>/32, F<sub>in</sub>/256 and F<sub>in</sub>/512

- Programmable output driver:

- High impedance

- 8mA/16mA drive capability

- Programmable crystal drive

- Built-in capacitors (10pF and/or 20pF)

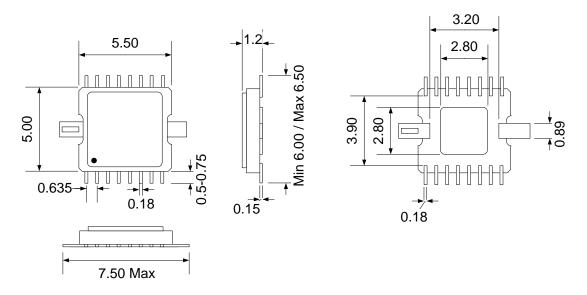

- Available in bare die and in hermetically sealed Ceramic TDFP16 package

- Validated at 225°C for 1000 hours (and still on-going)

#### **Applications**

Clock buffer & clock generation in downhole tools, aerospace, defense and HiRel applications

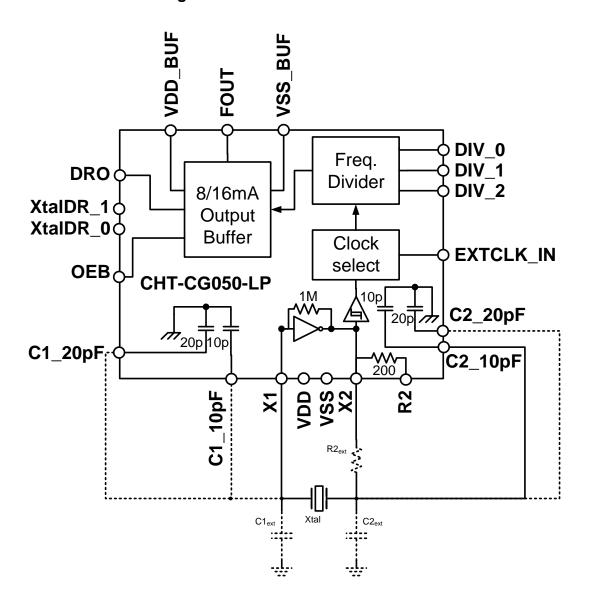

#### **Functional Block Diagram**

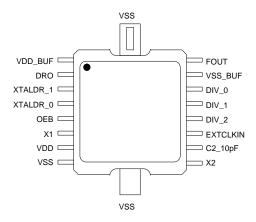

#### **Package and Pin Description**

| Pin #<br>(TDFP16) | Pin Name  | Description                                                                                                                                                                                                                                             |  |

|-------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1                 | VDD_BUF   | Output buffer power supply terminal. <sup>1</sup>                                                                                                                                                                                                       |  |

| 2                 | DRO       | Selection digital input pin for the output buffer strength: DRO=0 $\rightarrow$ 16mA buffer; DRO=1 $\rightarrow$ 8mA buffer. Features a built-in pull-down resistor (50k $\Omega$ Typ.)                                                                 |  |

| 3                 | XTALDR_1  | Selection digital input pin for the crystal drive circuitry (including the selection between internal and external clock). Refer to the text and truth table for use. Features an internal pull-down resistor (50k $\Omega$ Typ.).                      |  |

| 4                 | XTALDR_0  | Selection digital input pin for the crystal drive circuitry (including the selection between internal and external clock). Refer to the text and truth table for use. Features an internal pull-up resistor ( $50k\Omega$ Typ.).                        |  |

| 5                 | OEB       | Output Enable digital input: When driven LOW, output is enabled, When driven HIGH, output is at high impedance. Features a built-in pull-down resistor ( $50k\Omega$ Typ.)                                                                              |  |

| 6                 | X1        | Input of crystal driver. <u>Built-in 10pF capacitor (C1_10pF) hard-wired connected to this pin.</u>                                                                                                                                                     |  |

| 7                 | VDD       | Circuit core power supply terminal <sup>1</sup> .                                                                                                                                                                                                       |  |

| 8                 | vss       | Circuit core ground terminal <sup>1</sup> .                                                                                                                                                                                                             |  |

| 9                 | X2        | Output of crystal driver                                                                                                                                                                                                                                |  |

| 10                | C2_10pF   | Optional built-in 10pF capacitor with a common terminal connected to VSS.                                                                                                                                                                               |  |

| 11                | EXTCLK_IN | Input for an external clock source. Features an internal pull-down resistor (50k $\Omega$ Typ.).                                                                                                                                                        |  |

| 12                | DIV_2     | Selection bit of the frequency division factor - digital input - MSB                                                                                                                                                                                    |  |

| 13                | DIV_1     | Selection bit of the frequency division factor - digital input.                                                                                                                                                                                         |  |

| 14                | DIV_0     | Selection bit of the frequency division factor - digital input - LSB Note: Each DIV_n input pin features a built-in pull-down resistor (50k $\Omega$ Typ.) setting the frequency division rate to Fin:1 by default when DIV_n pins are left unconnected |  |

| 15                | VSS_BUF   | Output buffer ground terminal <sup>1</sup> .                                                                                                                                                                                                            |  |

| 16                | FOUT      | Output signal.                                                                                                                                                                                                                                          |  |

| NA                | R2        | Optional built-in 200 ohms resistance with a common terminal connected to X2. Not available in TDFP16.                                                                                                                                                  |  |

| NA                | C2_20pF   | Optional built-in 20pF capacitor with a common terminal connected to VSS. Not available in TDFP16.                                                                                                                                                      |  |

| NA                | C1_20pF   | Optional built-in 20pF capacitor with a common terminal connected to VSS. Not available in TDFP16.                                                                                                                                                      |  |

| NA                | C1_10pF   | Optional built-in 10pF capacitor with a common terminal connected to VSS. Connected to X1 pin in TDFP16.                                                                                                                                                |  |

<sup>&</sup>lt;sup>1</sup> VDD\_BUF and VDD are internally connected; VSS\_BUF and VSS are internally connected. Vertical large package leads and package heatsink (exposed pad) are internally connected to VSS

-

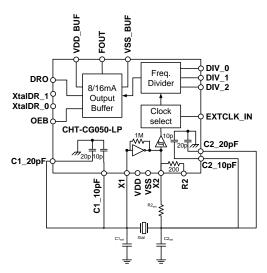

## **Configuration Examples & Minimum Connections**

| Pin Name                          | Minimum configura-<br>tion: 16mA Buffer;<br>div rate=1; crystal<br>mode with<br>Ron=400Ω | Ext Clock<br>configuration               | 8 mA Buffer with<br>512 div. rate config-<br>uration<br>crystal mode with<br>Ron=400Ω |  |

|-----------------------------------|------------------------------------------------------------------------------------------|------------------------------------------|---------------------------------------------------------------------------------------|--|

| VDD_BUF                           | Conn                                                                                     | ected to positive power s                | supply                                                                                |  |

| VSS_BUF                           | Conne                                                                                    | ected to negative power                  | supply                                                                                |  |

| VDD                               | Conn                                                                                     | ected to positive power s                | supply                                                                                |  |

| VSS                               | Conne                                                                                    | ected to negative power                  | supply                                                                                |  |

| X1                                |                                                                                          | Connected to crystal                     |                                                                                       |  |

| X2                                |                                                                                          | Connected to crystal                     |                                                                                       |  |

| FOUT                              |                                                                                          | Clock output                             |                                                                                       |  |

| C2_10pF                           | Connected to crystal                                                                     |                                          |                                                                                       |  |

| DIV_0<br>DIV_1<br>DIV_2           | Left unconnected                                                                         | : Division rate = 1                      | Connected to power supply                                                             |  |

| DRO                               | Left unconnected: Bu                                                                     | Left unconnected: Buffer strength = 16mA |                                                                                       |  |

| XTALDR_0                          | Left unconnected:                                                                        | Connected to ground                      | Left unconnected:                                                                     |  |

| XTALDR_1                          | Crystal mode ena-<br>bled with min crystal<br>driver strength <sup>2</sup>               | Left unconnected                         | Crystal mode ena-<br>bled with min crystal<br>driver strength <sup>2</sup>            |  |

| OEB                               | Left unconnected: Output enabled                                                         |                                          |                                                                                       |  |

| EXTCLK_IN                         | Left unconnected                                                                         | Connected to exter-<br>nal clock         | Left unconnected                                                                      |  |

| Total nbr of<br>connected<br>pins | 8                                                                                        | 10                                       | 12                                                                                    |  |

PUBLIC

Doc. DS-121206 V1.6 WWW.CISSOID.COM 4 of 12

<sup>&</sup>lt;sup>2</sup> Add 1 or 2 more connections if a different crystal drive is required

#### **Absolute Maximum Ratings**

#### **Operating Conditions**

Supply Voltage  $V_{\text{DD}}$  to GND Voltage on any Pin to GND

-0.5 to 6.0V -0.5 to  $V_{DD}$ +0.3V

Supply Voltage  $V_{\text{DD}}$  to GND Junction temperature

3.3V to 5V -55°C to +225°C

**ESD** Rating

Human Body Model

CLASS 2 (>2KV)

**CAUTION:** Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Frequent or extended exposure to absolute maximum rating conditions or above may affect device reliability.

PUBLIC Doc. DS-121206 V1.6

WWW.CISSOID.COM

5 of 12

#### **DC Electrical Characteristics**

Unless otherwise stated:  $V_{DD}=5V$ ,  $T_j=25^{\circ}C$ . **Bold underlined** values indicate values over the whole temperature range (-55 $^{\circ}C$  < T j < +225 $^{\circ}C$ ).

| Parameter                                                               | Condition                                                               | Min         | Тур   | Max         | Units                            |

|-------------------------------------------------------------------------|-------------------------------------------------------------------------|-------------|-------|-------------|----------------------------------|

| Supply voltage V <sub>DD</sub>                                          |                                                                         | <u>2.97</u> |       | <u>5.5</u>  | V                                |

|                                                                         | $V_{DD}$ = 3.3V, $F_{IN}$ = 10MHz, $C_L$ = 0pF<br>OEB = LOW, DRO = LOW  |             |       | <u>0.82</u> |                                  |

|                                                                         | $V_{DD}$ = 3.3V, $F_{IN}$ = 16MHz, $C_L$ = 0pF<br>OEB = LOW, DRO = LOW  |             |       | <u>1.25</u> |                                  |

|                                                                         | $V_{DD}$ = 3.3V, $F_{IN}$ = 20MHz, $C_L$ = 0pF<br>OEB = LOW, DRO = LOW  |             |       | <u>1.51</u> |                                  |

| Current consumption                                                     | $V_{DD}$ = 3.3V, $F_{IN}$ = 20MHz, $C_L$ = 22pF<br>OEB = LOW, DRO = LOW |             |       | <u>3.47</u> |                                  |

| Idd<br>(XTALDR_0=1,                                                     | $F_{IN} = 16MHz$ , $C_L = 0pF$<br>OEB = LOW, DRO = LOW                  |             |       | <u>2.2</u>  | mA                               |

| XTALDR_1=0)                                                             | $F_{IN} = 27MHz$ , $C_L = 0pF$<br>OEB = LOW, DRO = LOW                  |             |       | <u>3.51</u> |                                  |

|                                                                         | $F_{IN} = 40MHz$ , $C_L = 0pF$<br>OEB = LOW, DRO = LOW                  |             |       | <u>5.04</u> |                                  |

|                                                                         | $F_{IN} = 40MHz$ , $C_L = 22pF$<br>OEB = LOW, DRO = LOW                 |             |       | <u>9.5</u>  |                                  |

|                                                                         | F <sub>IN</sub> = 27MHz, OEB = HIGH                                     |             |       | <u>0.67</u> |                                  |

| Minimum HIGH level output voltage $\mathbf{V}_{\text{OH}}$              | Isource=16mA                                                            | <u>4.67</u> |       |             | V                                |

| Maximum LOW level output voltage <b>V</b> <sub>oL</sub>                 | Isink=16mA                                                              |             |       | 0.30        | V                                |

| Minimum HIGH level input voltage <b>V</b> <sub>IH</sub> (EXTCLK_IN pin) |                                                                         | <u>3.15</u> |       |             | V                                |

| Maximum LOW level input voltage <b>V</b> <sub>IL</sub> (EXTCLK_IN pin)  |                                                                         |             |       | <u>1.35</u> | V                                |

| Xtal driver On-Resistance                                               | XTALDR_0=1, XTALDR_1=0                                                  |             | 740   |             | Ω                                |

|                                                                         | XTALDR_0=0, XTALDR_1=1                                                  |             | 380   |             | Ω                                |

|                                                                         | XTALDR_0=1, XTALDR_1=1                                                  |             | 200   |             | Ω                                |

| Internal capacitors                                                     |                                                                         |             |       |             | <b>.</b>                         |

| Initial accuracy                                                        |                                                                         |             | 17    |             | %                                |

| Temperature drift                                                       | $\Delta T = 225^{\circ}C - 25^{\circ}C$                                 |             | 0.6   |             | %                                |

| TC1                                                                     | $C(T) = C(T_0) [1+TC1.(T-T_0)+$                                         |             | 0.023 |             | 10 <sup>-3</sup> /K              |

| TC2                                                                     | $TC2.(T-T_0)^2$                                                         |             | 0.013 |             | 10 <sup>-6</sup> /K <sup>2</sup> |

#### **AC Electrical Characteristics**

Unless otherwise stated: V<sub>DD</sub>=5V, T<sub>i</sub>=25°C. **Bold underlined** values indicate values over the whole temperature range (-55°C < T j < +225°C).

| Parameter                                                                                         | Condition                                         | Min                           | Тур       | Max             | Units |

|---------------------------------------------------------------------------------------------------|---------------------------------------------------|-------------------------------|-----------|-----------------|-------|

| Frequency range                                                                                   | $V_{DD} = 5V$ $V_{DD} = 3.3V$                     | 1 <sup>3</sup> 1 <sup>3</sup> |           | <u>50</u><br>30 | MHz   |

|                                                                                                   | $F_{IN}$ =1MHz, $V_{DD}$ = 5V                     |                               | 50/50     |                 |       |

| Duty cycle @ 50% V <sub>DD</sub>                                                                  | $F_{IN}$ =27MHz, $V_{DD}$ = 5V                    |                               | 51.7/48.3 |                 | %     |

|                                                                                                   | $F_{IN}$ =35MHz, $V_{DD}$ = 5V                    |                               | 52/48     |                 |       |

| Output rise time <sup>6</sup><br>10% to 90% V <sub>DD</sub>                                       | DRO=0, $Z_{LOAD} = 1M\Omega // 22pF$              |                               | 2.3       |                 | ns    |

| t <sub>r</sub>                                                                                    | DRO=0, $Z_{LOAD} = 600\Omega // 15pF$             |                               | 1.9       |                 | 115   |

| Output fall time <sup>6</sup><br>10% to 90% V <sub>DD</sub>                                       | DRO=0, $Z_{LOAD} = 1M\Omega // 22pF$              |                               | 2.2       |                 | no    |

| t <sub>f</sub>                                                                                    | DRO=0, $Z_{LOAD} = 600\Omega // 15pF$             |                               | 1.8       |                 | ns    |

| Oscillation established after V <sub>DD</sub> goes high <sup>7</sup> <b>t</b> <sub>power-on</sub> | V <sub>DD</sub> from 0 to 5V                      |                               | 1.9       |                 | ms    |

| Oscillation established after XTALDR_n goes HIGH <sup>7</sup> t <sub>start-up</sub>               | V <sub>DD</sub> = 5V<br>XTALDR_n from LOW to HIGH |                               | 0.4       |                 | ms    |

| Equivalent capacitance at driver input (X1) <sup>8</sup> C <sub>X1</sub>                          | Freq= 1MHz                                        |                               | 0.72      |                 | pF    |

| Equivalent capacitance at driver output $(X2)^8$ $C_{X2}$                                         | Freq= 1MHz                                        |                               | 0.71      |                 | pF    |

| Equivalent capacitance at limiting resistor (R2) <sup>8</sup> C <sub>R2</sub>                     | Freq= 1MHz                                        |                               | 0.6       |                 | pF    |

<sup>&</sup>lt;sup>3</sup> CG50LP also supports 32.768kHz crystal operation; refer to Circuit Functionality section for info about crystal network

<sup>4</sup> Duty cycle is measured with a unitary division factor and  $Z_{LOAD} = 1050\Omega$  // 22pF.

<sup>5</sup> Depends on crystal characteristics and on  $R2_{EXT}$  value.

<sup>6</sup> Depends on load conditions and **DRO** setting.

<sup>7</sup> Depends on used crystal and **XTALDR\_0**, **XTALDR\_1** settings.

<sup>&</sup>lt;sup>8</sup> Valid for die version

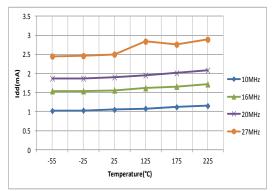

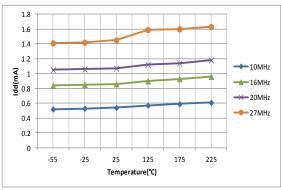

#### **Typical Performance Characteristics**

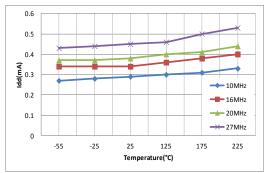

Figure 1: Current consumption ( $V_{DD} = 5V$ , OEB = LOW,  $C_L = 0$ pF, XTALDR\_0=1, XTALDR\_1=0)

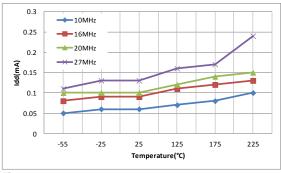

**Figure 2:** Current consumption (V<sub>DD</sub> = 3.3V, OEB = LOW, C<sub>L</sub> = 0pF, XTALDR\_0=1, XTALDR\_1=0)

**Figure 3:** Current consumption (VDD = 5V, OEB = HIGH, XTALDR\_0=1, XTALDR\_1=0)

**Figure 4:** Current consumption (VDD = 3.3V, OEB = HIGH, XTALDR\_0=1, XTALDR\_1=0)

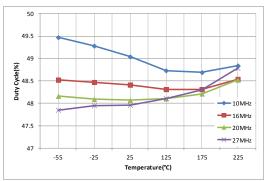

Figure 5: Duty cycle (V<sub>DD</sub>=5V)

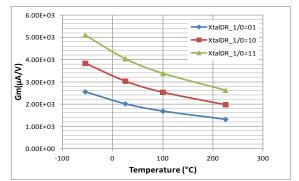

Figure 6: Crystal driver transconductance ( $V_{DD}$ =5V)

#### **Circuit Functionality**

#### **Operating conditions**

The CHT-CG-50LP is qualified for supply voltages ranging from 3.0V up to 5.5V.

The operating temperature range extends from -55°C to +225°C.

#### **Crystal driver**

The pins XTALDR\_0 and XTALDR \_1 allow to set-up the crystal driver strength or to select the external input clock

| XTALDR_0                | XTALDR _1               | Internal State                                                                           |

|-------------------------|-------------------------|------------------------------------------------------------------------------------------|

| 0 0 abled. Ext          |                         | Crystal driver dis-<br>abled. External<br>clock used.                                    |

| 1<br>(standard<br>mode) | 0<br>(standard<br>mode) | $\begin{array}{ll} \text{Min crystal drive} \\ (\text{Ron} \cong 740\Omega) \end{array}$ |

| 0                       | 1                       | Medium crystal drive (Ron $\cong$ 380 $\Omega$ )                                         |

| 1                       | 1                       | Max crystal drive (Ron $\cong$ 200Ω)                                                     |

XTALDR\_0 is internally pulled up ( $50k\Omega$  Typ.) and XTALDR\_1 internally pulled down ( $50k\Omega$  Typ.).

Reducing the drive strength of the crystal driver will help reducing the current consumption of the device

#### Frequency divider

Eight division factors (1, 2, 4, 8, 16, 32, 256 and 512) can be selected through the digital control lines **DIV\_0**, **DIV\_1** and **DIV\_2**.

| DIV_0 | DIV_1 | DIV_2 | Division rate |

|-------|-------|-------|---------------|

| 0     | 0     | 0     | 1             |

| 1     | 0     | 0     | 2             |

| 0     | 1     | 0     | 4             |

| 1     | 1     | 0     | 8             |

| 0     | 0     | 1     | 16            |

| 1     | 0     | 1     | 32            |

| 0     | 1     | 1     | 256           |

| 1     | 1     | 1     | 512           |

The 3 digital inputs pins are internally pulled down, enabling a frequency division rate of 1 by default when the pins are left unconnected (internally pulled down (50k $\Omega$  Typ.).

#### **Output buffer**

The output buffer has dedicated power supply terminals, allowing the system designer to properly decouple them

The output buffer features 2 fixed output strengths of 8mA and 16mA which can be selected from the digital input pin DRO. This enables the CHT-CG-50-LP to optimize the output signal integrity depending on the type of output load. The default output strength is 16mA when DRO is left unconnected (internally pulled down,  $50k\Omega$  Typ.). When HIGH (connected to VDD), the output strength is 8mA.

The output buffer can be set in highimpedance by setting OEB pin to HIGH.

#### 32 KHz operation

The figure below illustrates the recommended configuration for CG50LP operation with a 32KHz crystal

Figure 7. Configuration for 32KHz operation

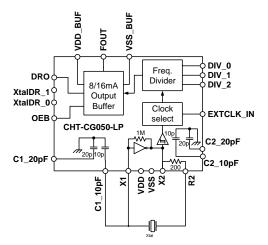

#### Typical application

The CHT-CG-50LP offers the final user several possible configurations depending upon the characteristics of the target application.

Figure 8. Full configuration.

Figure 9. Minimal configuration.

#### **Output impedance matching**

The CHT-CG50LP is able to provide an output signal with very short transition times (<10ns). During this transition periods, the output signal must be seen as a signal with a frequency above 100MHz. Under this assumption, PCB traces or cables connected to the output represent inductors or even transmission lines.

Signal integrity good practices must be considered when driving PCB traces or cables with the CHT-CG50LP output. PCB traces or cables can induce ringing and even reflections back to the output buffer. Too much reflection onto the output buffer may cause overshoots and undershoots on the CHT-CG50LP terminals exceeding the Absolute Maximum Ratings of the device leading to permanent damage.

To reduce or avoid ringing or signal reflection, impedance matching considerations must be taken into account. To do so, adapt the CHT-CG50LP output drives strength (DRO) to the final application load conditions, place capacitive loads as close as possible of the CHT-CG50LP output, keep traces and cables as short as possible and, when driving long traces or cables cannot be avoided, place a resistor in series with the output as close to it as possible in order to match the trace or cable impedance. This resistor, generally in the range from  $10\Omega$  to  $100\Omega$  must be experimentally determined given the final application load conditions.

#### **Package Dimensions (TDFP16)**

Physical dimensions (mm +/- 10%)

### **Ordering Information**

| Product Name | Ordering Reference    | Package Marking |              |

|--------------|-----------------------|-----------------|--------------|

| CHT-CG50LP   | CHT-PUL9560A-TDFP16-T | TDFP16          | CHT-PUL9560A |

#### **Contact**

| Headquarters and contact EMEA: | CISSOID S.A. – Rue Francqui, 3 – 1435 Mont Saint Guibert - Belgium T : +32 10 48 92 10 - F: +32 10 88 98 75 Email: sales@cissoid.com |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| Sales<br>Representatives:      | Visit our website: http://www.cissoid.com                                                                                            |

#### **Disclaimer**

Neither CISSOID, nor any of its directors, employees or affiliates make any representations or extend any warranties of any kind, either express or implied, including but not limited to warranties of merchantability, fitness for a particular purpose, and the absence of latent or other defects, whether or not discoverable. In no event shall CISSOID, its directors, employees and affiliates be liable for direct, indirect, special, incidental or consequential damages of any kind arising out of the use of its circuits and their documentation, even if they have been advised of the possibility of such a damage. The circuits are provided "as is". CISSOID has no obligation to provide maintenance, support, updates, or modifications.

PUBLIC