# CH7318C AC Coupled HDMI Level Shifter

## 1.0 FEATURES

- Converts low-swing AC coupled differential input to HDMI 1.4a compliant open-drain current steering Rx terminated differential output.

- HDMI TMDS level shifting operation up to 1.65Gb/s per lane (165MHz pixel clock).

- Enable feature to turn off TMDS inputs and outputs and to enter low-power state.

- Transparent operation: no re-timing or configuration required.

- Inter-Pair added skew < 250ps

- Intra-Pair added skew < 10ps

- Switching power only from a single 3.3V supply.

- Integrated 50-ohm termination resistors for AC coupled differential Inputs.

- Pass-gate voltage limiters allow 3.3V termination on GMCH pins, 5V DDC termination on HDMI connector pins.

- Human Body Model ESD protection: 8kV for all output pins and 2kV for all other pins.

- Level shifter for HDMI 1.4a HPD.

- Integrated pull-down resistor on HPD\_SINK input guarantees "input low" when no display is plugged in.

- Driver's current adjustment +10%.

- Inverting buffer for HPD signal

- Configurable pre-emphasis level (0dB, 2.0dB, 4.0 dB, & 6.0dB)

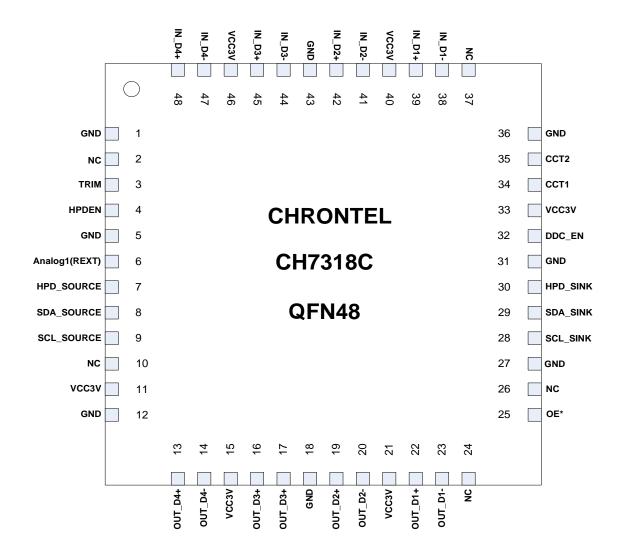

- Offered in a 48-Pin QFN Package.

## 2.0 GENERAL DESCRIPTION

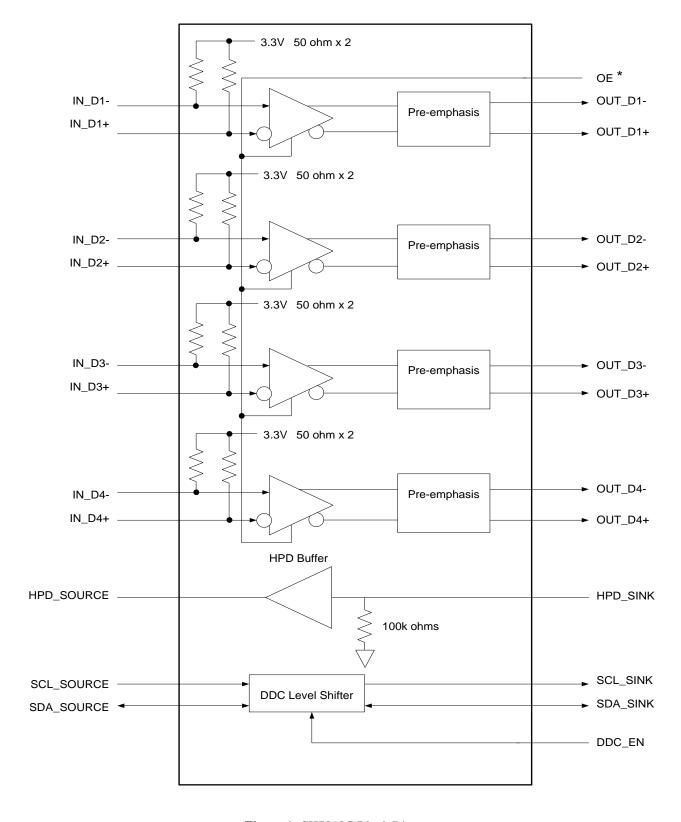

CH7318C is a high speed HDMI level shifter that converts low-swing AC coupled differential input to HDMI 1.4a compliant open-drain current steering Rx terminated differential output.

The CH7318C features integrated parallel termination resistors (50-ohm), which eliminate the requirement for external termination resistors on the TMDS differential This device has incorporated a ESD output pins. protection for DDC channels as well as TMDS signal lines. In addition, the DDC\_EN pin controls bias voltage to enable or disable the DDC passgate level shifter gates. The OE\* pin is a two- state output enable control for the differential input and the TMDS signal output. It can activate IN Dx pins and OUT Dx pins or switch them into high impedance. A unique preemphasis control is also implemented into CH7318C; this feature has four-level adjustment to increase rise and fall times which are degraded during the transmission over a long trace on PCB.

The device operates from a single +3.3V supply, and is characterized the operation temperature range from 0 °C to 70 °C (ambient temperature). The CH7318C is available in a 48-Pin QFN package.

Figure 1: CH7318C Block Diagram

# TABLE OF CONTENTS

| 1.0 | FEATURES                          | 1  |

|-----|-----------------------------------|----|

| 2.0 | GENERAL DESCRIPTION               | 1  |

| 3.0 | PIN-OUT                           | 5  |

| 3.1 | Package Diagram                   | 5  |

| 3.2 | Pin Descriptions                  | 6  |

| 4.0 | FUNCTIONAL DESCRIPTION            | 8  |

| 4.1 | Power Supply                      | 8  |

| 4.2 | Clocking                          | 8  |

| 4.3 | Reset                             | 8  |

| 4.4 | OE* Function                      | 8  |

| 4.5 | Pre-emphasis Function             | 9  |

| 5.0 | ELECTRICAL SPECIFICATIONS         | 10 |

| 5.1 | Absolute Maximum Ratings          | 10 |

| 5.2 | Recommended Operating Conditions  | 10 |

| 5.3 | Differential Input                |    |

| 5.4 | TMDS OUTPUTS                      | 11 |

| 5.5 | HPD_SINK INPUT; HPD_SOURCE OUTPUT | 12 |

| 5.6 | OE* INPUT                         | 12 |

| 5.7 | HPD Input Resistor                | 12 |

| 6.0 | PACKAGE DIMENSIONS                | 13 |

| 7.0 | REVISION HISTORY                  | 14 |

# FIGURE AND TABLES

## LIST OF TABLES

| Table 1: Pin Descriptions                                                                                   | 6  |

|-------------------------------------------------------------------------------------------------------------|----|

| Table 2: OE* Description                                                                                    | 8  |

| Table 3: OE* Function                                                                                       | 8  |

| Table 4: Pre-emphasis Selection Table                                                                       | 9  |

| Table 5: T <sub>SC</sub> , T <sub>AMB</sub> , T <sub>STOR</sub> , T <sub>J</sub> , T <sub>VPS</sub> Ratings |    |

| Table 6: Recommended Operating Conditions                                                                   |    |

| Table 7: Differential Input Characteristics for IN_D Signals                                                |    |

| Table 8: TMDS Output Characteristics for OUT_D signals                                                      | 11 |

| Table 9: HPD Input and Output Characteristics                                                               | 12 |

| Table 10: OE* Input Characteristics                                                                         |    |

| Table 11: DDC Termination Resistors                                                                         |    |

| Table 12: Revisions                                                                                         | 14 |

|                                                                                                             |    |

| LIST OF FIGURES                                                                                             |    |

| Figure 1: CH7318C Block Diagram                                                                             | 2  |

| Figure 2: 48-Pin QFN Pin Out                                                                                | 5  |

| Figure 3: 48 Pin QFN Package                                                                                |    |

## **3.0 PIN-OUT**

## 3.1 Package Diagram

Figure 2: 48-Pin QFN Pin Out

## 3.2 Pin Descriptions

**Table 1: Pin Descriptions**

| Pin #                     | Type   | Symbol              | Description                                                                                                                                                                       |                               |  |  |  |

|---------------------------|--------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|--|--|--|

| 1,5,12,18,27,3<br>1,36,43 | Ground | GND                 | Analog ground                                                                                                                                                                     |                               |  |  |  |

| 2,26                      |        | NC                  | Not Connect<br>Compliant and can be connected to                                                                                                                                  | o VCC3V                       |  |  |  |

| 11,15,21,<br>33,40,46     | Power  | VCC3V               | 3.3V DC analog supply                                                                                                                                                             |                               |  |  |  |

| 24,37                     |        | NC                  | Not Connect<br>Compliant and can be connected to                                                                                                                                  | o GND                         |  |  |  |

| 10                        |        | NC                  | Not connect                                                                                                                                                                       |                               |  |  |  |

| 3                         | In     | TRIM                | Enable for output current increasing 10%.  TRIM Output current  0V Default  3.3V +10%                                                                                             |                               |  |  |  |

| 4                         | In     | HPDEN               |                                                                                                                                                                                   |                               |  |  |  |

| 4                         | 111    | HPDEN               | Enable for different HPD_SOURCE output.  HPDEN HPD_SOURCE                                                                                                                         |                               |  |  |  |

|                           |        |                     | 0V Non-inverting output (in terms of HPD_Sink                                                                                                                                     |                               |  |  |  |

|                           |        |                     | 3.3V Inverting output (in terms of HPD_Sink) - Open drain                                                                                                                         |                               |  |  |  |

| 6                         |        | Analog1(REXT)       | 1.2K resistor tied to GND.                                                                                                                                                        |                               |  |  |  |

| 7                         | Out    | HPD_SOURCE          | 0V to 3.3V (nominal) output signal. This is level-shifted version of the HPD_SINK                                                                                                 |                               |  |  |  |

| 8                         | In/Out | SDA_SOURCE          | 3.3V DDC Data I/O. Pulled up by Connected to SDA_SINK through NMOS passgate.                                                                                                      |                               |  |  |  |

| 9                         | In     | SCL_SOURCE          | 3.3V DDC Clock I/O. Pulled up b<br>Connected to SCL_SINK through<br>NMOS passgate.                                                                                                |                               |  |  |  |

| 13,14                     | Out    | OUT_D4+,<br>OUT_D4- | HDMI 1.4a compliant TMDS outp<br>OUT_D4+ makes a differential ou                                                                                                                  |                               |  |  |  |

| 16,17                     | Out    | OUT_D3+,<br>OUT_D3- | HDMI 1.4a compliant TMDS outp<br>OUT_D3+ makes a differential ou                                                                                                                  |                               |  |  |  |

| 19,20                     | Out    | OUT_D2+,<br>OUT_D2- | HDMI 1.4a compliant TMDS outp<br>OUT_D2+ makes a differential ou                                                                                                                  |                               |  |  |  |

| 22,23                     | Out    | OUT_D1+,<br>OUT_D1- | HDMI 1.4a compliant TMDS output. OUT_D1+ makes a differential output signal with OUT_D1-                                                                                          |                               |  |  |  |

| 25                        | In     | OE*                 | Enable for level shifter path. 3.3V input.  OE* IN_D Term  1 High-Z  0 50 $\Omega$                                                                                                | nination OUT_D Outputs High-Z |  |  |  |

| 28                        | Out    | SCL_SINK            | 0       50Ω       Active         5V DDC Clock I/O. Pulled up by external termination to 5V.         Connected to SCL_SOURCE through voltage-limiting by integrated NMOS passgate. |                               |  |  |  |

| Pin # | Туре   | Symbol            | Description                                                                                                                                                                                                                       |                  |                                  |  |  |  |

|-------|--------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------------------------|--|--|--|

| 29    | In/Out | SDA_SINK          | 5V DDC Data I/O. Pulled up by external termination to 5V. Connected to SDA_SOURCE through voltage-limiting by integrated NMOS passgate.                                                                                           |                  |                                  |  |  |  |

| 30    | In     | HPD_SINK          | Low frequency, 0V to 5V (nominal) input signal. This signal comes from the HDMI connector. Voltage high indicates "plugged" state; Voltage low indicates "unplugged". HPD_SINK is pulled down by an integrated 100k ohm resistor. |                  |                                  |  |  |  |

| 32    | In     | DDC_EN            | Enables biases voltage                                                                                                                                                                                                            | e to the DDC pa  | ssgate level shifter gates.      |  |  |  |

|       |        |                   | DDC_EN                                                                                                                                                                                                                            |                  | Passgate                         |  |  |  |

|       |        |                   | 0V                                                                                                                                                                                                                                |                  | Disabled                         |  |  |  |

|       |        |                   | 3.3V                                                                                                                                                                                                                              |                  | Enabled                          |  |  |  |

| 34    | In     | CCT1              | Pre-emphasis control pin1. CCT1 is pulled down by an integrated 50 ohm resistor.                                                                                                                                                  |                  |                                  |  |  |  |

|       |        |                   | CCT1                                                                                                                                                                                                                              | CCT2             | Pre-emphasis level               |  |  |  |

|       |        |                   | '0'                                                                                                                                                                                                                               | '0'              | 0dB(default)                     |  |  |  |

|       |        |                   | '0'                                                                                                                                                                                                                               | '1'              | 2dB                              |  |  |  |

|       |        |                   | '1'                                                                                                                                                                                                                               | '0'              | 4dB                              |  |  |  |

|       |        |                   | '1'                                                                                                                                                                                                                               | '1'              | 6dB                              |  |  |  |

| 35    | In     | CCT2              | Pre-emphasis control ohm resistor                                                                                                                                                                                                 | pin 2. CCT2 is p | bulled down by an integrated 50k |  |  |  |

| 38,39 | In     | IN_D1-,<br>IN_D1+ | Low-swing diff input from GMCH PCIe outputs. IN_D1+ makes a differential pair with IN_D1                                                                                                                                          |                  |                                  |  |  |  |

| 41,42 | In     | IN_D2-,<br>IN_D2+ | Low-swing diff input from GMCH PCIe outputs. IN_D2+ makes a differential pair with IN_D2                                                                                                                                          |                  |                                  |  |  |  |

| 44,45 | In     | IN_D3-,<br>IN_D3+ | Low-swing diff input from GMCH PCIe outputs. IN_D3+ makes a differential pair with IN_D3                                                                                                                                          |                  |                                  |  |  |  |

| 47,48 | In     | IN_D4-,<br>IN_D4+ | Low-swing diff input IN_D4+ makes a diffe                                                                                                                                                                                         |                  |                                  |  |  |  |

## 4.0 FUNCTIONAL DESCRIPTION

## 4.1 Power Supply

3.3V +/- 10%

### 4.2 Clocking

This device does not re-time any data. The device contains no state machines. No inputs or outputs of the device are latched or clocked.

### 4.3 Reset

This device acts as a level shifter, reset is not required.

### 4.4 OE\* Function

When OE\* is asserted (low voltage) the IN\_D and OUT\_D signals are fully functional.

In put termination resistors are enabled and any internal bias circuits are turned on.

When OE\* is unasserted (high voltage) the OUT\_D outputs are in a high-impedance state. The IN\_D input buffers are disabled and IN\_D termination is disabled. Internal bias circuits for the differential inputs and outputs are turned off. Power consumption is minimized.

The HPD\_SINK input and HPD\_SOURCE output are not affected by OE\*.

The SCL and SDA passgates are not affected by OE\*.

**Table 2: OE\* Description**

| OE*                             | Device State                                                                                                                                                                                                                                                                         | Comments                                                                                                                                                                                                                                                                         |

|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Asserted (low voltage)          | Differential input buffers and output buffers enabled. Input impedance = 50 ohm.                                                                                                                                                                                                     | Normal functioning state for IN_D to OUT_D level shifting function.                                                                                                                                                                                                              |

| Unasserted<br>(high<br>voltage) | Low-power state.  Differential input buffers and termination are disabled. Differential input buffers are in a high-impedance state.  OUT_D level-shifting outputs are disabled. OUT_D level-shifting outputs are in a high-impedance state.  Internal bias currents are turned off. | Intended for lowest power condition when:  • No display is plugged in or  • The level shifted data path is disabled  HPD_SINK input and HPD_SOURCE output are not affected by OE*.  SCL_SOURCE, SCL_SINK, SDA_SOURCE and SDA_SINK signals and functions are not affected by OE*. |

Table 3: OE\* Function

| OE*                       | In_Dx                 | TMDS_OUTx | Notes                                                                  |

|---------------------------|-----------------------|-----------|------------------------------------------------------------------------|

| Unasserted (high voltage) | High-Z                | High-Z    | Device disabled. Low power state. Internal bias currents are disabled. |

| Asserted (low voltage)    | 50 ohm<br>Termination | Enabled   | Level shifting mode enabled.                                           |

## 4.5 Pre-emphasis Function

The CH7318C has an advanced pre-emphasis control mechanism for reducing jitter and increasing rise/fall times from long or lossy transmission high speed signal. Two pins are used to configure the pre-emphasis level for OUT\_Dx outputs:

**Table 4: Pre-emphasis Selection Table**

| CCT1 | CCT2 | Pre-emphasis Level |

|------|------|--------------------|

| '0'  | '0'  | 0dB(default)       |

| '0'  | '1'  | 2dB                |

| '1'  | '0'  | 4dB                |

| '1'  | '1'  | 6dB                |

## 5.0 ELECTRICAL SPECIFICATIONS

## 5.1 Absolute Maximum Ratings

Table 5: T<sub>SC</sub>, T<sub>AMB</sub>, T<sub>STOR</sub>, T<sub>J</sub>, T<sub>VPS</sub> Ratings

| Symbol            | Description                             | Min  | Тур        | Max | Units |

|-------------------|-----------------------------------------|------|------------|-----|-------|

|                   | All 3.3V power supplies relative to GND | -0.5 |            | 5.0 | V     |

| T <sub>SC</sub>   | Analog output short circuit duration    |      | Indefinite |     | Sec   |

| T <sub>STOR</sub> | Storage temperature                     | -65  |            | 150 | °C    |

| TJ                | Junction temperature                    |      |            | 150 | °C    |

| T <sub>VPS</sub>  | Vapor phase soldering (5 second)        |      |            | 260 | °C    |

|                   | Vapor phase soldering (11 second)       |      |            | 245 |       |

|                   | Vapor phase soldering (60 second)       |      |            | 225 |       |

#### Note:

- 1) Stresses greater than those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions above those indicated under the normal operating condition of this specification is not recommended. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

- 2) The device is fabricated using high-performance CMOS technology. It should be handled as an ESD sensitive device. Voltage on any signal pin that exceeds the power supply voltages by more than ± 0.5V can induce destructive latchup.

### 5.2 Recommended Operating Conditions

**Table 6: Recommended Operating Conditions**

| Symbol           | Description                        | Min  | Тур | Max  | Units |

|------------------|------------------------------------|------|-----|------|-------|

| VCC3V            | 3.3V Power Supply                  | 2.97 | 3.3 | 3.63 | V     |

| ICC              | Total current from VCC 3.3V supply | 0    | 60  |      | mA    |

| I <sub>PD</sub>  | Total Power Down Current           |      | 10  |      | μΑ    |

| T <sub>AMB</sub> | Ambient Operating temperature      | 0    |     | 70   | °C    |

## 5.3 Differential Input

Table 7: Differential Input Characteristics for IN\_D Signals.

| Symbol              | Description                                | Min   | Тур | Max | Units | Comments                                                                                                                                                                                                 |

|---------------------|--------------------------------------------|-------|-----|-----|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Tbit                | Unit Interval                              | 540   |     |     | ps    | Tbit is determined by the display mode. Nominal bit rate ranges from 250Mb/s to 1.65Gb/s per lane. (1.65Gb/s supported on both TMS and muxed outputs). Nominal Tbit at 1.65Gb/s=606ps. 540ps =606ps-10%. |

| V<br>RX-Diffp-p     | Differential Input Peak to<br>Peak Voltage | 0.175 |     | 1.2 | V     | VRX-DIFFp-p = 2* VRX-D+ - VRX-D- .<br>Applies to IN_D signals.                                                                                                                                           |

| T <sub>RX-EYE</sub> | Minimum Eye Width at IN_D input pair.      | 0.8   |     |     | Tbit  | The level shifter may add a maximum of 0.02UI jitter                                                                                                                                                     |

| Symbol                 | Description                                                              | Min | Тур | Max | Units | Comments                                                                                                                                   |

|------------------------|--------------------------------------------------------------------------|-----|-----|-----|-------|--------------------------------------------------------------------------------------------------------------------------------------------|

| V<br>CM-AC-pp          | AC Peak Common-Mode<br>Input Voltage                                     |     |     | 100 | mV    | VCM-AC-pp =  VRX-D+ + VRX-D-  / 2 - VRX-CM-DC. VRX-CM-DC = DC(avg) of  VRX-D++ VRX-D-  / 2 VCM-AC-pp includes all frequencies above 30kHz. |

| Z <sub>RX-DC</sub>     | DC Input Impedance                                                       | 40  | 50  | 60  | Ω     | Required IN_D+ as well as IN_D- DC impedance (50 $\Omega$ +/- 20% tolerance).                                                              |

| Z <sub>RX-HIGH-Z</sub> | Single-ended input resistance for IN_Dx when inputs are in HIGH-Z state. | 100 |     |     | kΩ    | Differential inputs must be in a high impedance state when OE* is HIGH                                                                     |

### 5.4 TMDS OUTPUTS

The level shifter's TMDS outputs are required to meet HDMI 1.4a specifications. The HDMI 1.4a Specification is assumed to be the correct reference in instances where this document conflicts with the HDMI 1.4a specification.

Table 8: TMDS Output Characteristics for OUT\_D signals

| Symbol                  | Description                            | Min        | Тур        | Max        | Units | Comments                                                                                               |

|-------------------------|----------------------------------------|------------|------------|------------|-------|--------------------------------------------------------------------------------------------------------|

| V <sub>H</sub>          | Single-ended high level output voltage | AVCC-10mV  | AVCC       | AVCC+10mV  | V     | AVCC is the DC termination voltage in the HDMI or DVI Sink. AVCC is nominally 3.3V                     |

| V <sub>L</sub>          | Single-ended low level output voltage  | AVcc-600mV | AVcc-500mV | AVcc-400mV | V     | The open-drain output pulls down from AVcc                                                             |

| V <sub>SWING</sub>      | Single-ended output swing voltage      | 450        | 500        | 600        | mV    |                                                                                                        |

| OFF                     | Single-ended current in high-Z state   |            |            | 10         | μΑ    | Measured with TMDS outputs pulled up to AVCC Max $(3.6V)$ through $50\Omega$ resistors.                |

| T <sub>R</sub>          | Rise time                              | 206        |            | 0.4Tbit    | ps    | Max rise/fall time @<br>1.65Gb/s = 242ps.<br>206ps = 242ps - 15%                                       |

| T <sub>F</sub>          | Fall time                              | 206        |            | 0.4Tbit    | ps    | Max rise/fall time @ 1.65Gb/s = 242ps. 206ps = 242ps - 15%                                             |

| T <sub>SKEW-INTRA</sub> | Intra-pair differential skew           |            |            | 10         | ps    | This differential skew budget is in addition to the skew presented between D+ and D-paired input pins. |

| T <sub>SKEW-INTER</sub> | Inter-pair differential skew           |            |            | 250        | ps    | This land-to-lane skew budget is in addition to skew between differential input pairs.                 |

| T <sub>JIT</sub>        | Jitter added to TMDS signals           |            |            | 10.8       | ps    | Jitter budget for TMDS signals as they pass through the level shifter.  12ps = 0.02 Tbit at 1.65Gb/s   |

## 5.5 HPD\_SINK INPUT; HPD\_SOURCE OUTPUT

**Table 9: HPD Input and Output Characteristics**

| Symbol               | Description                              | Min  | Тур | Max | Units | Comments                                                                                                                           |

|----------------------|------------------------------------------|------|-----|-----|-------|------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>IH-HPD</sub>  | Input high level                         | 2    | 5   | 5.3 | V     | Low-speed input changes state on cable plug/unplug.                                                                                |

| V <sub>IL-HPD</sub>  | HPD_SINK Input Low Level                 | 0    |     | 0.8 | V     |                                                                                                                                    |

| I<br>IN-HPD          | HPD_SINK Input leakage current           |      |     | 10  | μA    | Measured with HPD_SINK at $V_{\rm IH-HPD}$ max and $V_{\rm IL-HPD}$ min                                                            |

| V <sub>OH-HPDB</sub> | HPD_SOURCE Output High Level             | 2.5V |     | VCC | V     | VCC is 3.3v +/- 10%                                                                                                                |

| V <sub>OL-HPDB</sub> | HPD_SOURCE Output Low Level              | 0    |     | 0.2 | V     |                                                                                                                                    |

| T <sub>HPD</sub>     | HPD_SINK to HPD_SOURCE propagation delay |      |     | 200 | ns    | Time from HPD_SINK changing state to HPD# changing state. Includes HPD_SOURCE rise/fall time.                                      |

| T <sub>RF-HPDB</sub> | HPD_SOURCE rise/fall time                | 1    |     | 20  | ns    | Time required to transition from $V_{\text{OH-HPDB}}$ to $V_{\text{OL-HPDB}}$ or from $V_{\text{OL-HPDB}}$ to $V_{\text{OH-HPDB}}$ |

## **5.6 OE\* INPUT**

**Table 10: OE\* Input Characteristics**

| Symbol             | Description           | Min | Тур | Max | Units | Comments                                                               |

|--------------------|-----------------------|-----|-----|-----|-------|------------------------------------------------------------------------|

| V <sub>IH-EN</sub> | Input high level      | 2   |     | 4   | ٧     |                                                                        |

| V <sub>IL-EN</sub> | Input Low Level       | 0   |     | 0.8 | ٧     |                                                                        |

| I <sub>IN-EN</sub> | Input leakage current |     |     | 10  | μA    | Measured with OE* at V <sub>IH-EN</sub> max and V <sub>IL-EN</sub> min |

## 5.7 HPD Input Resistor

**Table 11: DDC Termination Resistors**

| Symbol           | Description                      |     | Min Typ |      | Units | Comments                                                  |  |

|------------------|----------------------------------|-----|---------|------|-------|-----------------------------------------------------------|--|

| R <sub>HPD</sub> | HPD_SINK input pulldown resistor | 80k | 100k    | 120k | Ω     | Guarantees HPD_SINK is LOW when no display is plugged in. |  |

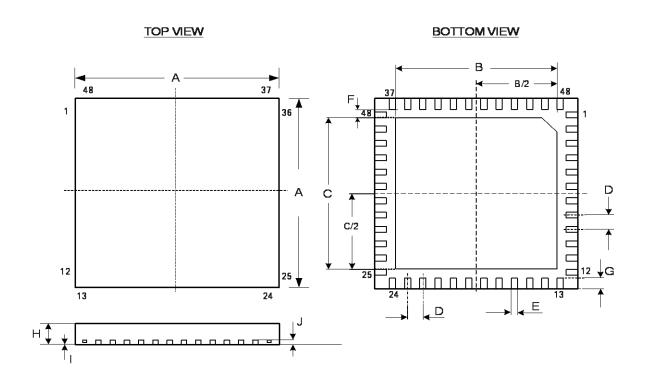

# **6.0 PACKAGE DIMENSIONS**

Figure 3: 48 Pin QFN Package

### **Table of Dimensions**

| No. of Leads  |     |   |      |      |     | SYM  | BOL |      |     |      |       |

|---------------|-----|---|------|------|-----|------|-----|------|-----|------|-------|

| 48 (7 X 7 mm) |     | A | В    | C    | D   | E    | F   | G    | Н   | I    | J     |

| Milli-        | MIN | 7 | 2.25 | 2.25 | 0.5 | 0.18 | 0.2 | 0.30 | 0.7 | 0    | 0.202 |

| meters        | MAX | / | 5.25 | 5.25 | 0.5 | 0.30 | 0.2 | 0.50 | 0.8 | 0.05 | 0.203 |

## **Notes:**

1. Conforms to JEDEC standard JESD-30 MO-220.

201-1000-006 Rev.2.5 03/13/2017

13

# 7.0 REVISION HISTORY

**Table 12: Revisions**

| Rev. # | Date       | Section  | Description                                        |

|--------|------------|----------|----------------------------------------------------|

| 1.0    | 1/23/2008  | All      | Initial release.                                   |

| 2.0    | 4/25/2008  | All      | Change to CH7318C.                                 |

|        |            | 3.0      | Add Pin 35 CCT2, Pin34 CCT1 and move TRIM to Pin3. |

|        |            | 3.2      | Update Table 1. Pin3, Pin34 and Pin35.             |

| 2.1    | 1/23/2009  | 5.1      | Update temperature range.                          |

| 2.2    | 10/01/2009 | 2.0, 5.2 | Correct temperature range / term                   |

| 2.3    | 6/01/2010  | All      | Update HDMI specification description              |

|        |            |          | Add the index table                                |

| 2.4    | 01/24/2014 | 5.1, 5.2 | Update temperature range.                          |

| 2.5    | 03/13/2017 | 1.2      | Update the Pin Description                         |

### **Disclaimer**

This document provides technical information for the user. Chrontel reserves the right to make changes at any time without notice to improve and supply the best possible product and is not responsible and does not assume any liability for misapplication or use outside the limits specified in this document. CHRONTEL warrants each part to be free from defects in material and workmanship for a period of one (1) year from date of shipment. Chrontel assumes no liability for errors contained within this document. The customer should make sure that they have the most recent data sheet version. Customers should take appropriate action to ensure their use of the products does not infringe upon any patents. Chrontel, Inc. respects valid patent rights of third parties and does not infringe upon or assist others to infringe upon such rights.

Chrontel PRODUCTS ARE NOT AUTHORIZED FOR AND SHOULD NOT BE USED WITHIN LIFE SUPPORT SYSTEMS OR NUCLEAR FACILITY APPLICATIONS WITHOUT THE SPECIFIC WRITTEN CONSENT OF Chrontel. Life support systems are those intended to support or sustain life and whose failure to perform when used as directed can reasonably expect to result in personal injury or death.

| ORDERING INFORMATION |                              |                |      |  |  |  |  |

|----------------------|------------------------------|----------------|------|--|--|--|--|

| Part Number          | Number of<br>Pins            | Voltage Supply |      |  |  |  |  |

| CH7318C-BF           | Lead-free QFN                | 48             | 3.3V |  |  |  |  |

| CH7318C-BF-TR        | Lead-free QFN in Tape & Reel | 48             | 3.3V |  |  |  |  |

# **Chrontel**

## **Chrontel International Limited**

129 Front Street, 5th floor, Hamilton, Bermuda HM12

www.chrontel.com E-mail: sales@chrontel.com

©2017 Chrontel - All Rights Reserved