# CA-IS3062 Isolated CAN Transceiver

# 1. Key Features

- Meets the ISO11898-2 Standard

- Isolation Rating up to 5.0kVrms

- 2.5V ~ 5V High Logical I/O Voltage Range

- High Data Rate: 1 Mbps

- High CMTI: ±150kV/μs (Typical)

- Bus Fault Protection Voltage: ±40V

- Low Loop Delay:

- 150 ns (Typical)

- 210 ns (Maximum)

- Driver Dominant Time Out (TXD)

- Thermal Shutdown Protection

- Maximum Number of Nodes: 110

- Unpowered Nodes do not Interfere with the Bus

- Wide Operating Temperature Range: -40°C to 125°C

- Safety-Related Certification (Pending):

- 61010-1 VDE Certification

- IEC 60950-1, IEC 61010-1 and IEC 60601-1 Certification

- TUV 5kV<sub>RMS</sub> Reinforced Insulation Approved to EN/UL/CSA 60950-1

- CQC Reinforced Insulation in accordance with GB4843.1-2011

### 2. Applications

- CAN Data Bus

- Industrial Field Network

- Building and Greenhouse Environmental Control Automation

- Security System

- Transport

- Medical

- Telecom

### 3. Description

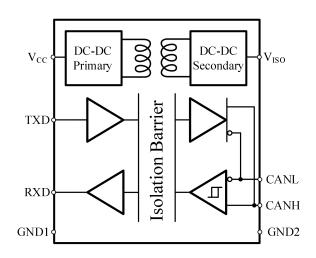

The CA-IS3062 device is a galvanically-isolated controller area network (CAN) Physical Layer Transceiver that meets the specifications of the ISO11898-2 standard. This device uses on-chip silicon dioxide (SiO2) capacitors as an isolation barrier to create a completely isolated interface between the CAN protocol controller and the physical layer bus. Used in conjunction with isolated power supplies, this device can prevent noises and interferences from the sensitive circuits.

The CA-IS3062 device can provide differential transmission and reception capabilities for CAN protocol controller and physical layer bus respectively, with a data rate of up to 1Mbps. This device also has the functions of overcurrent protection, overvoltage protection, ground loss protection (-40V to 40V), thermal shutdown and short-circuit protection. Normally, the common mode voltage should be between -12V and 12V.

The CA-IS3062 device supports a wide ambient temperature range of -40°C to 125°C The device is available in the wide-body SOIC16 packages.

### **Device Information**

| PART NUMBER | PACKAGE | BODY SIZE(NOM) |

|-------------|---------|----------------|

| IN4 2062    | SOIC16- | 10.30mm ×7.50  |

| JM 3062     | WB(W)   | mm             |

### Simplified Functional Block Diagram

### **Ordering Guide** 4.

**Table 4-1 Ordering Guide for Valid Ordering Part Number**

| Ordering Part Number | V <sub>cc</sub> (V) | Data Rate (kbps) | Isolation Rating (V <sub>RMS</sub> ) | Package   |

|----------------------|---------------------|------------------|--------------------------------------|-----------|

| CA-IS3062            | 4.5~5.5             | 1000             | 5000                                 | SOIC16-WB |

上海川土微电子有限公司

# Table of Contents

| 1. |      | Key Features                               | 1 |

|----|------|--------------------------------------------|---|

| 2. |      | Applications                               | 1 |

| 3. |      | Description                                | 1 |

| 4. |      | Ordering Guide                             | 2 |

| 5. |      | Revision History                           | 3 |

| 6. |      | PIN Descriptions and Functions             | 4 |

| 7. |      | Specifications                             | 5 |

|    | 7.1. | Absolute Maximum Ratings <sup>1</sup>      | 5 |

|    | 7.2. | ESD Ratings                                |   |

|    | 7.3. | Recommended Operating Conditions           | 5 |

|    | 7.4. | Thermal Information                        | 5 |

|    | 7.5. | Insulation Specifications                  | 6 |

|    | 7.6. | Safety-Related Certifications              | 7 |

|    | 7.7. | Electrical Characteristics                 | 8 |

|    | 7.8. | Timing Characteristics—Device              | 9 |

|    | 7.9. | Timing Characteristics—Driver and Receiver | 9 |

| 8.  |      | Parar  | neter ivieasurement information | 1 10 |

|-----|------|--------|---------------------------------|------|

| 9.  |      | Detai  | iled Description                | 13   |

|     | 9.1. | The    | eory of Operation               | 13   |

|     | 9.2. | Fur    | nctional Block Diagram          | 13   |

|     | 9.3. | Pro    | tection Features                | 13   |

|     |      | 9.3.1. | Signal Isolation                | 13   |

|     |      | 9.3.2. | Dominant Time-Out               | 13   |

|     |      | 9.3.3. | Thermal Shutdown                | 14   |

|     |      | 9.3.4. | Current Limiting                | 14   |

|     | 9.4. | Dev    | vice Function Modes             | 14   |

| 10. |      | Appli  | cation Information              | 16   |

| 11. |      | Packa  | age Information                 | 18   |

|     | SOI  | C16-WB | Package                         | 18   |

| 12. |      | TAPE   | AND REEL INFORMATION            | 19   |

| 13. |      | Orde   | ring Information                | 20   |

# 5. Revision History

**Preliminary Version**

# 6. PIN Descriptions and Functions

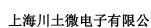

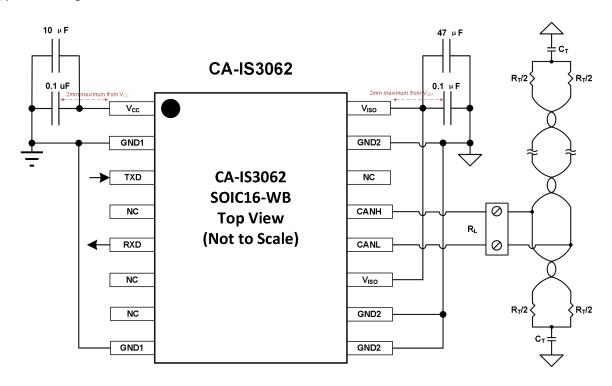

Figure 6-1 CA-IS3062 Pin Configuration

Table 6-1 CA-IS3062 Pin Description and Functions

| Die Name         | Pin Number | Туре           | Description                                                                    |

|------------------|------------|----------------|--------------------------------------------------------------------------------|

| Pin Name         | SOIC16     |                |                                                                                |

| V <sub>CC</sub>  | 1          | Supply         | Digital-side Power Supply, Side A                                              |

| GND1             | 2          | Ground         | Digital-side Ground Connection, Side A                                         |

| TXD              | 3          | Input          | CAN Transmit Data Input                                                        |

| NC               | 4          | -              | Not Connected                                                                  |

| RXD              | 5          | Output         | CAN Receive Data Output                                                        |

| NC               | 6          | -              | Not Connected                                                                  |

| NC               | 7          | -              | Not Connected                                                                  |

| GND1             | 8          | Ground         | Digital-side Ground Connection, Side A                                         |

| GND2             | 9          | Ground         | Transceiver-side Ground Connection, Side B                                     |

| GND2             | 10         | Ground         | Transceiver-side Ground Connection, Side B                                     |

| V <sub>ISO</sub> | 11         | Supply         | Transceiver-side Power Supply, Side B, Please connect pin11 and pin16 together |

| CANL             | 12         | Input / Output | Low-Level CAN Bus Line                                                         |

| CANH             | 13         | Input / Output | High-Level CAN Bus Line                                                        |

| NC               | 14         | -              | Not Connected                                                                  |

| GND2             | 15         | Ground         | Transceiver-side Ground Connection, Side B                                     |

| V <sub>ISO</sub> | 16         | Supply         | Transceiver-side Power Supply, Side B, Please connect pin11 and pin16 together |

# 7. Specifications

上海川土微电子有限公司

# 7.1. Absolute Maximum Ratings<sup>1</sup>

|                                        |                                         | MIN  | MAX            | UNIT |

|----------------------------------------|-----------------------------------------|------|----------------|------|

| V <sub>CC</sub> , V <sub>ISO</sub>     | Supply Voltage <sup>2</sup>             | -0.5 | 6.0            | V    |

| VI                                     | Digital-Side Input Voltage (TXD)        | -0.5 | $V_{CC}+0.5^3$ | V    |

| V <sub>CANH</sub> or V <sub>CANH</sub> | Transceiver-Side Voltage (CANH or CANL) | -40  | 40             | V    |

| Io                                     | Receiver Output Current                 | -15  | 15             | mA   |

| T <sub>J</sub>                         | Junction Temperature                    |      | 150            | °C   |

| T <sub>STG</sub>                       | Storage Temperature                     | -65  | 150            | °C   |

### NOTE:

- 1. Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under *Recommended Operating Conditions* is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- 2. All input/output digital voltage values are with respect to the digital-side ground terminal (GND1), and the differential I/O bus voltages are with respect to the transceiver-side ground terminal (GND2).

- 3. Maximum voltage must not exceed 6 V.

# 7.2. ESD Ratings

|                                          |                                                                                        | VALUE | UNIT |

|------------------------------------------|----------------------------------------------------------------------------------------|-------|------|

| V Floatroctatic discharge                | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>1</sup>              | ±5000 | V    |

| V <sub>ESD</sub> Electrostatic discharge | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins <sup>2</sup> | ±1500 | V    |

### NOTE:

- 1. JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- 2. JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 7.3. Recommended Operating Conditions

Operation beyond thermal shutdown temperature may affect device reliability

|                                   |                                           |                                                      | MIN  | TYP | MAX     | UNIT |

|-----------------------------------|-------------------------------------------|------------------------------------------------------|------|-----|---------|------|

| V <sub>CC</sub>                   | Transceiver-Side Supply Voltage           |                                                      | 4.5  | 5   | 5.5     | V    |

| V <sub>I</sub> or V <sub>IC</sub> | Transceiver-Side Bus Voltage              |                                                      | -12  |     | 12      | V    |

| V <sub>IH</sub>                   | High-Level Input Voltage                  | Driver (TXD)                                         | 2    |     | VCC+0.3 | V    |

| V <sub>IL</sub>                   | Low-Level Input Voltage                   | Driver (TXD)                                         | -0.3 |     | 0.8     | V    |

| V <sub>ID</sub>                   | Differential Input Voltage                |                                                      | -7   |     | 7       | V    |

| I <sub>OH</sub>                   | High-level Output Current                 | Driver                                               | -70  |     |         | mA   |

|                                   |                                           | Receiver                                             | -2   |     |         |      |

| I <sub>OL</sub> L                 | Low-level Output Current                  | Driver                                               |      |     | 70      | mA   |

|                                   |                                           | Receiver                                             |      |     | 2.5     |      |

| T <sub>A</sub>                    | Ambient Temperature                       |                                                      |      |     | 125     | °C   |

| Tı                                | Junction Temperature                      |                                                      |      |     | 150     | °C   |

|                                   |                                           | $V_{CC} = 5.5V$ , $T_A = 125$ °C, $R_L = 60\Omega$ , |      |     |         |      |

| $P_D$                             | <b>Total Power Consumption</b>            | TXD Input is a 500kHz Square                         |      |     | 900     | mW   |

|                                   |                                           | Wave (50% Duty)                                      |      |     |         |      |

| T <sub>J(shutdown)</sub>          | Thermal Shutdown Temperature <sup>1</sup> |                                                      |      | 165 |         | °C   |

### 7.4. Thermal Information

| THERMAL METRIC                                          | SOIC16-WB | UNIT |

|---------------------------------------------------------|-----------|------|

| R <sub>0JA</sub> Junction-to-ambient thermal resistance | 86.5      | °C/W |

# 7.5. Insulation Specifications

|                                                       | PARAMETR                                          | TEST CONDITIONS                                                                                                                                                                                                                         | VALUE<br>G/W     | UNIT             |

|-------------------------------------------------------|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------|

| CLR                                                   | External clearance <sup>1</sup>                   | Shortest terminal-to-terminal distance through air                                                                                                                                                                                      | 8                | mm               |

| CPG                                                   | External creepage <sup>1</sup>                    | Shortest terminal-to-terminal distance across the package surface                                                                                                                                                                       | 8                | mm               |

| DTI                                                   | Distance through the insulation                   | Minimum internal gap (internal clearance)                                                                                                                                                                                               | 21               | μm               |

| CTI                                                   | Comparative tracking index                        | DIN EN 60112 (VDE 0303-11); IEC 60112                                                                                                                                                                                                   | >400             | V                |

|                                                       | Material group                                    | According to IEC 60664-1                                                                                                                                                                                                                | I                | 1                |

|                                                       |                                                   | Rated mains voltage ≤ 300 V <sub>RMS</sub>                                                                                                                                                                                              | I-IV             | 1                |

|                                                       | Overvoltage category per IEC 60664-1              | Rated mains voltage ≤ 400 V <sub>RMS</sub>                                                                                                                                                                                              | I-IV             | 7                |

|                                                       |                                                   | Rated mains voltage ≤ 600 V <sub>RMS</sub>                                                                                                                                                                                              | 1-111            | 1                |

| DIN V VC                                              | DE V 0884-11:2017-01 <sup>2</sup>                 |                                                                                                                                                                                                                                         | ı                | ,                |

| V <sub>IORM</sub>                                     | Maximum repetitive peak isolation voltage         | AC voltage (bipolar)                                                                                                                                                                                                                    | 849              | V <sub>PK</sub>  |

| V <sub>IOWM</sub>                                     | Maximum working isolation voltage                 | AC voltage; Time dependent dielectric breakdown (TDDB) Test                                                                                                                                                                             | 600              | V <sub>RMS</sub> |

|                                                       |                                                   | DC voltage                                                                                                                                                                                                                              | 849              | V <sub>DC</sub>  |

|                                                       |                                                   | V <sub>TEST</sub> = V <sub>IOTM</sub> ,                                                                                                                                                                                                 |                  | - 50             |

| $V_{\text{IOTM}}$ Maximum transient isolation voltage |                                                   | t = 60 s (qualification);<br>V <sub>TEST</sub> = 1.2 × V <sub>IOTM</sub> ,<br>t= 1 s (100% production)                                                                                                                                  | 7070             | V <sub>PK</sub>  |

| V <sub>IOSM</sub>                                     | Maximum surge isolation voltage <sup>3</sup>      | Test method per IEC 60065, 1.2/50 $\mu$ s waveform, $V_{TEST} = 1.6 \times V_{IOSM}$ (qualification)                                                                                                                                    | 6250             | V <sub>PK</sub>  |

|                                                       |                                                   | Method a, After Input/Output safety test subgroup 2/3, $V_{ini} = V_{IOTM}$ , $t_{ini} = 60 \text{ s}$ ; $V_{pd(m)} = 1.2 \times V_{IORM}$ , $t_m = 10 \text{ s}$                                                                       | ≤5               |                  |

| $q_{pd}$                                              | Apparent charge <sup>4</sup>                      | Method a, After environmental tests subgroup 1, $V_{\text{ini}} = V_{\text{IOTM}},  t_{\text{ini}} = 60 \text{ s};$ $V_{\text{pd(m)}} = 1.6 \times V_{\text{IORM}},  t_{\text{m}} = 10 \text{ s}$                                       | ≤5               | pC               |

|                                                       |                                                   | Method b1, At routine test (100% production) and preconditioning (type test) $V_{\text{ini}} = 1.2 \times V_{\text{IOTM}}, t_{\text{ini}} = 1 \text{ s};$ $V_{\text{pd(m)}} = 1.875 \times V_{\text{IORM}}, t_{\text{m}} = 1 \text{ s}$ | ≤5               |                  |

| C <sub>IO</sub>                                       | Barrier capacitance, input to output <sup>5</sup> | $V_{10} = 0.4 \times \sin(2\pi ft), f = 1 \text{ MHz}$                                                                                                                                                                                  | ~0.5             | pF               |

|                                                       |                                                   | V <sub>IO</sub> = 500 V, T <sub>A</sub> = 25°C                                                                                                                                                                                          | >1012            | 1                |

| R <sub>IO</sub>                                       | Isolation resistance <sup>5</sup>                 | V <sub>IO</sub> = 500 V, 100°C ≤ T <sub>A</sub> ≤ 125°C                                                                                                                                                                                 | >1011            | Ω                |

|                                                       |                                                   | V <sub>IO</sub> = 500 V at T <sub>S</sub> = 150°C                                                                                                                                                                                       | >10 <sup>9</sup> | 7                |

|                                                       | Pollution degree                                  |                                                                                                                                                                                                                                         | 2                | 1                |

| UL 1577                                               | -                                                 |                                                                                                                                                                                                                                         |                  |                  |

| V <sub>ISO</sub>                                      | Maximum withstanding isolation voltage            | $V_{TEST} = V_{ISO}$ , $t = 60$ s (qualification),<br>$V_{TEST} = 1.2 \times V_{ISO}$ , $t = 1$ s (100% production)                                                                                                                     | 5000             | V <sub>RMS</sub> |

- 1. Creepage and clearance requirements should be applied according to the specific equipment isolation standards of an application. Care should be taken to maintain the creepage and clearance distance of a board design to ensure that the mounting pads of the isolator on the printed-circuit board do not reduce this distance. Creepage and clearance on a printed-circuit board become equal in certain cases. Techniques such as inserting grooves and/or ribs on a printed circuit board are used to help increase these specifications.

- 2. This coupler is suitable for safe electrical insulation only within the safety ratings. Compliance with the safety ratings shall be ensured by means of suitable protective circuits.

- 3. Testing is carried out in air or oil to determine the intrinsic surge immunity of the isolation barrier.

- 4. Apparent charge is electrical discharge caused by a partial discharge (pd).

- 5. All pins on each side of the barrier tied together creating a two-terminal device.

上海川土微电子有限公司

# 7.6. Safety-Related Certifications

| VDE(Pending)               | CSA(Pending)               | UL(Pending)         | CQC(Pending)           | TUV(Pending)              |

|----------------------------|----------------------------|---------------------|------------------------|---------------------------|

| Certified according to DIN | Certified according to IEC | Recognized under UL | Certified according to | Certified according to EN |

| V VDE V 0884-11:2017-01    | 60950-1, IEC 62368-1 and   | 1577 Component      | GB4843.1-2011          | 61010-1:2010 (3rd Ed)     |

|                            | IEC 60601-1                | Recognition Program |                        | and EN 60950-             |

|                            |                            |                     |                        | 1:2006/A2:2013            |

### 7.7. **Electrical Characteristics**

Unless otherwise specified, all voltages are referenced to their respective grounds, 4.5 V ≤ V<sub>CC</sub>≤ 5.5 V. All min / max specifications apply over the entire recommended working range. Unless otherwise specified, all typical specs are tested under  $T_A = -40$ °C $\sim$ 125°C,  $V_{CC} = 5$  V.

|                     | PARAMETER                                    |             | TEST CONDITIONS                                                            | MIN                   | TYP  | MAX  | UNIT     |

|---------------------|----------------------------------------------|-------------|----------------------------------------------------------------------------|-----------------------|------|------|----------|

| Supply C            | Current                                      |             |                                                                            |                       |      |      |          |

| I <sub>cc</sub>     | Digital-side Supply Current                  |             | $V_I = 0 \text{ V}$ , $R_L = 60 \Omega$<br>dominant timeout protection     | 14                    | 20   | 29   | mA       |

|                     |                                              |             | V <sub>I</sub> = V <sub>CC</sub>                                           | 14                    | 20   | 29   | 1        |

| Isolated            | Power Supply                                 |             |                                                                            |                       |      |      |          |

| V <sub>ISO</sub>    | Output voltage                               | No Load     | I <sub>ISO</sub> =0mA                                                      | 4.65                  | 5.05 | 5.47 | V        |

|                     |                                              |             |                                                                            |                       |      |      |          |

| Driver              |                                              |             |                                                                            |                       |      |      |          |

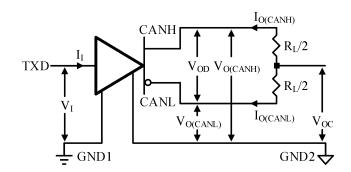

| V                   | Bus Output Voltage (Dominant)                | CANH        | $V_1 = 0 \text{ V}, R_L = 60 \Omega, See \text{ Figure 8- 1 Figure 8- 2}$  | 2.9                   | 3.4  | 4.5  | V        |

| V <sub>O(D)</sub>   | Bus Output Voltage (Dollillalit)             | CANL        | - V <sub>1</sub> = 0 V, K <sub>L</sub> = 60 Ω, See Figure 8- 1 Figure 8- 2 | 0.5                   |      | 2    | ]        |

| V <sub>O(R)</sub>   | Bus Output Voltage (Recessive)               |             | $V_1 = 2 \text{ V}$ , $R_L = 60 \Omega$ , See Figure 8- 1 Figure 8- 2      | 2                     | 2.5  | 3    | V        |

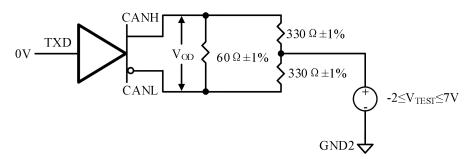

| .,                  | Differential Output Voltage (Dominant)       |             | $V_1 = 0$ V, $R_L = 60$ $\Omega$ , See Figure 8- 1 Figure 8- 2 Figure 8- 3 | 1.5                   |      | 3    | V        |

| $V_{OD(D)}$         |                                              |             | $V_1$ = 0 V, $R_L$ = 45 Ω, See Figure 8- 1 Figure 8- 2 Figure 8- 3         | 1.3                   |      | 3    | V        |

|                     |                                              |             | $V_1 = 3 \text{ V}$ , $R_L = 60 \Omega$ , See Figure 8- 1 Figure 8- 2      | -80                   |      | 80   | mV       |

| $V_{OD(R)}$         | Differential Output Voltage (Recessive)      |             | V <sub>I</sub> = 3 V, No Load                                              | -0.5                  |      | 0.05 | V        |

| V <sub>OC(D)</sub>  | Common Mode Output Voltage (Dominant)        |             |                                                                            | 2                     | 2.5  | 3    | V        |

| . ,                 | (pp) Common Mode Output Voltage Peak to Peak |             | See Figure 8- 7                                                            |                       | 60   |      | V        |

| I <sub>IH</sub>     | High-level Input Current, TXD Input          |             | V <sub>1</sub> = 2 V                                                       |                       |      | 20   | μА       |

| I <sub>IH</sub>     | Low-level Input Current, TXD Inpu            |             | V <sub>I</sub> = 0.8 V                                                     | -20                   |      |      | μΑ       |

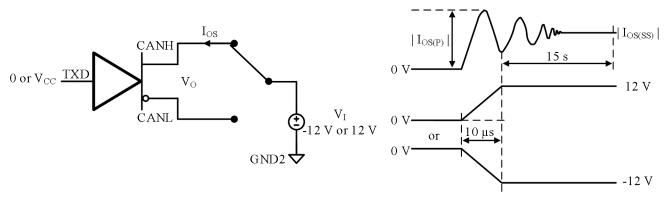

|                     |                                              |             | V <sub>CANH</sub> = -12 V, CANL = open, See Figure 8- 10                   | 105                   | -72  |      | <u> </u> |

| _                   |                                              |             | V <sub>CANH</sub> = 12 V, CANL = open, <i>See</i> Figure 8- 10             |                       | 0.36 | 2    | mA       |

| I <sub>OS(SS)</sub> | Short-Circuit Steady State Output            | Current     | V <sub>CANL</sub> = -12 V, CANH = open, See Figure 8- 10                   | -2                    | -0.5 |      |          |

|                     |                                              |             | V <sub>CANL</sub> = 12 V, CANH = open, <i>See</i> Figure 8- 10             |                       | 71   | 105  | 1        |

| CMTI                | Common Mode Transient Immuni                 | ty          | $V_1 = 0 \text{ V or } V_{CC}$ , See Figure 8- 11                          | 100                   | 150  |      | kV/μs    |

|                     |                                              |             | Receiver                                                                   |                       |      |      |          |

| V <sub>IT+</sub>    | Positive Input Threshold Voltage             |             |                                                                            |                       | 0.8  | 0.9  | V        |

| V <sub>IT-</sub>    | Negative Input Threshold Voltage             |             |                                                                            | 0.5                   | 0.65 |      | V        |

| V <sub>HYS</sub>    | Hysteresis Voltage for Input Voltag          | je          |                                                                            | 50                    | 125  |      | mV       |

|                     |                                              |             | I <sub>OH</sub> = –4 mA, <i>See</i> Figure 8- 6                            | V <sub>CC</sub> - 0.8 | 4.8  |      |          |

| V <sub>OH</sub>     | High-Level Output Voltage, $V_{CC} = 5$      | V           | $I_{OH} = -20 \mu\text{A}$ , See Figure 8- 6                               | V <sub>CC</sub> - 0.1 | 5    |      | \  \ \   |

|                     |                                              |             | I <sub>OH</sub> = -4 mA, <i>See</i> Figure 8- 6                            |                       | 0.2  | 0.4  |          |

| $V_{OL}$            | Low-Level Output Voltage                     |             | $I_{OH} = -20 \mu\text{A}$ , See Figure 8-6                                |                       | 0    | 0.1  | - V      |

| Cı                  | Input Capacitance to Ground (CAN             | IH or CANL) | TXD = 3V, VI = $0.4x\sin(2\pi ft) + 2.5 \text{ V}$ , f = 1MHz              |                       | 13   |      | pF       |

| C <sub>ID</sub>     | Differential Input Capacitance (CA           |             | TXD = 3V, VI = $0.4x\sin(2\pi ft)$ , f = 1MHz                              |                       | 5    |      | pF       |

| R <sub>IN</sub>     | Input Resistance (CANH or CANL)              | - ···-/     | TXD = 3V                                                                   | 28                    | 32   | 36   | kΩ       |

| R <sub>ID</sub>     | Differential Input Resistance (CAN           | H - CANL)   | TXD = 3V                                                                   | 56                    | 62   | 68   | kΩ       |

| R <sub>I(m)</sub>   | Input Resistance Matching                    | - ,         | V <sub>CANH</sub> = V <sub>CANL</sub>                                      | -5%                   | 0%   | 5%   |          |

|                     | $(1 - [R_{IN(CANH)} / R_{IN(CANL)}])$        |             |                                                                            |                       |      |      |          |

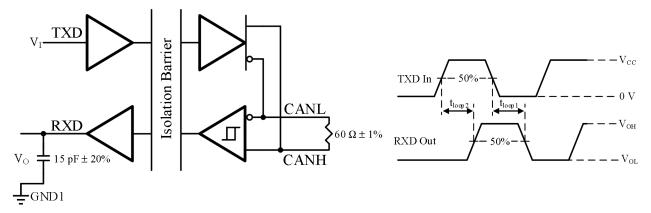

# 7.8. Timing Characteristics—Device

Unless otherwise specified, all voltages are referenced to their respective grounds,  $4.5 \text{ V} \le \text{V}_{CC} \le 5.5 \text{ V}$ . All min / max specifications apply over the entire recommended working range. Unless otherwise specified, all typical specs are tested under  $T_A = -40^{\circ}\text{C}^{-125^{\circ}\text{C}}$ ,  $V_{CC} = 5 \text{ V}$ .

|                    | PARAMETER                                                                 | TEST<br>CONDITIONS | MIN T | UNIT |     |    |

|--------------------|---------------------------------------------------------------------------|--------------------|-------|------|-----|----|

| t <sub>loop1</sub> | Total Loop Delay, Driver Input TXD to Receiver RXD, Recessive to Dominant | See Figure 8-8     | 110   | 150  | 210 | ns |

| t <sub>loop2</sub> | Total Loop Delay, Driver Input TXD to Receiver RXD, Dominant to Recessive | See Figure 0- 0    | 110   | 150  | 210 | ns |

# 7.9. Timing Characteristics—Driver and Receiver

Unless otherwise specified, all voltages are referenced to their respective grounds,  $4.5 \text{ V} \le \text{V}_{CC} \le 5.5 \text{ V}$ . All min / max specifications apply over the entire recommended working range. Unless otherwise specified, all typical specs are tested under  $T_A = -40^{\circ}\text{C}^{-1}25^{\circ}\text{C}$ ,  $V_{CC} = 5 \text{ V}$ .

|                                   | PARAMETER                                            | TEST CONDITIONS                                 | MIN | TYP MAX | <b>(</b> | UNIT |

|-----------------------------------|------------------------------------------------------|-------------------------------------------------|-----|---------|----------|------|

| Driver                            |                                                      |                                                 |     |         |          |      |

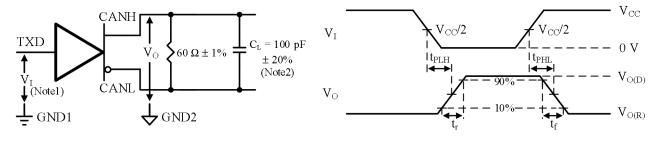

| t <sub>PLH</sub>                  | Propagation Delay Time, Output Recessive to Dominant |                                                 | 35  | 75      | 130      |      |

| t <sub>PHL</sub>                  | Propagation Delay Time, Output Dominant to Recessive | See Figure 8-4                                  | 35  | 55      | 100      | nc   |

| t <sub>r</sub>                    | Differential Output Signal Rise Time                 | See Figure 8- 4                                 |     | 40      | 60       | ns   |

| t <sub>f</sub>                    | Differential Output Signal Fall Time                 |                                                 |     | 40      | 60       |      |

| t <sub>TXD_DTO</sub> <sup>1</sup> | Dominant Time-Out                                    | C <sub>L</sub> = 100 pF, <i>See</i> Figure 8- 9 | 300 | 450     | 700      | μs   |

| Receiver                          |                                                      |                                                 |     |         |          |      |

| t <sub>PLH</sub>                  | Propagation Delay Time, Output Low to High           |                                                 | 55  | 110     | 140      |      |

| t <sub>PHL</sub>                  | Propagation Delay Time, Output High to Low           | See Figure 8- 6                                 | 55  | 80      | 140      | nc   |

| t <sub>r</sub>                    | Output Signal Rise Time                              | See Figure 6- 0                                 |     | 2.5     | 6        | ns   |

| t <sub>f</sub>                    | Output Signal Fall Time                              |                                                 |     | 2.5     | 6        |      |

Once the time that driver enters the dominant state is longer than t<sub>TXD\_DTO</sub>, the dominant timeout function will shut down the driver to

release the bus into recessive state, preventing the bus from being locked in the dominant state. The drive can recover the function of

transmitting only after entering the recessive state.

# 8. Parameter Measurement Information

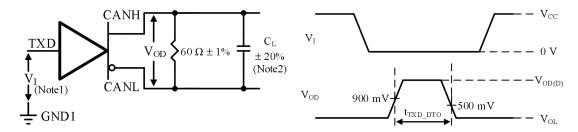

Figure 8- 1 Driver Voltage and Current Definition

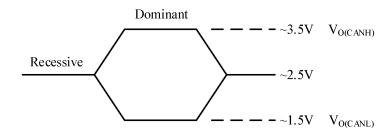

Figure 8-2 Bus Logic State Voltage Definitions

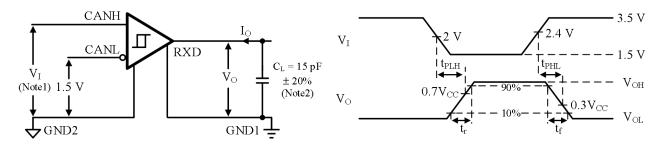

Figure 8- 3 Driver Output Voltage (VoD) Test Circuits (Common Mode Load)

- $1. \hspace{0.5cm} \text{A square wave generator generate the $V_{IN}$ input signal with the following constraints: $PRR \leqslant 125$ kHz, 50% duty cycle, $t_r \leqslant 6 ns, $t_f \leqslant 6 ns, $Z_0 = 50$ $\Omega$.}$

- 2.  $C_L$  is the load capacitance about 100pF together with the instrumentation capacitance and the parasitic capacitance of the fixture.

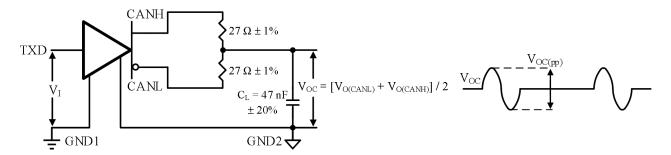

Figure 8-4 Driver Test Circuit and Voltage Waveform

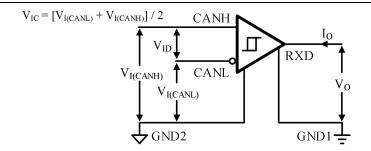

Figure 8-5 Receiver Voltage and Current Definitions

- 1. A square wave generator generate the  $V_{IN}$  input signal with the following constraints: PRR  $\leq$  125 kHz, 50% duty cycle,  $t_r \leq$  6ns,  $t_f \leq$  6ns,  $t_C =$  50  $t_C =$  50

- 2. C<sub>L</sub> is the load capacitance about 100pF together with the instrumentation capacitance and the parasitic capacitance of the fixture.

Figure 8-6 Receiver Test Circuit and Voltage Waveform

Figure 8-7 Common Mode Output Peak-to-Peak Voltage Test Circuit and Waveform

Figure 8-8 t<sub>loop</sub> Test Circuit and Voltage Waveform

Figure 8-9 Dominant Time-out Test Circuit and Voltage Waveforms

- 1. A square wave generator generate the  $V_{IN}$  input signal with the following constraints:  $t_r \le 6$ ns,  $t_f \le 6$ ns,  $Z_0 = 50 \Omega$ .

- 2. C<sub>L</sub> is the load capacitance about 100pF together with the instrumentation capacitance and the parasitic capacitance of the fixture.

Figure 8- 10 Driver Short-Circuit Current Test Circuit and Waveforms

Figure 8-11 CMTI Test Circuit

# 9. Detailed Description

### 9.1. Theory of Operation

The CA-IS3062 device is an isolated controller area network (CAN) physical layer transceiver that offers 5 kV<sub>RMS</sub> isolation rating and 150 kV /  $\mu$ s CMTI, integrated with the dominant timeout and thermal shutdown functions. The digital side of this device can be powered by a 5V power supply while the bus side is powered by internal integrated 5 V power supply, which is very suitable for harsh industrial control applications.

# 9.2. Functional Block Diagram

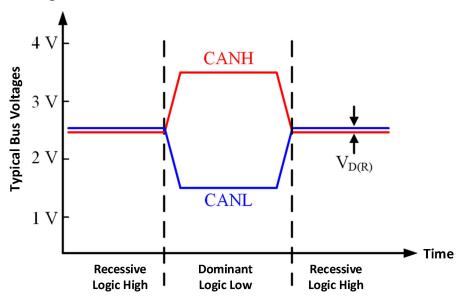

Figure 9-1 Typical Waveform of CAN Bus States

The CAN bus has two states during operation: dominant and recessive. When the differential voltage between CANH and CANL is greater than 0.9 V, the bus is in dominant state, and the CANH pin is logic high while the CANL pin is logic low. When the differential voltage between CANH and CANL is less than 0.5 V, the bus is in recessive state and the CANH and CANL pins are both in high impedance. A typical bus voltage waveform is shown in Figure 9-1.

### 9.3. Protection Features

### 9.3.1. Signal Isolation

Signal isolation in the CA-IS3062 device is achieved by a digital isolator with capacitive isolation. On the digital side, the input signal is modulated to a high frequency by on-off key (OOK) modulation, and this high frequency signal propagates to the transceiver side through an on-chip silicon dioxide capacitor which can operate at a high voltage. At last, the digital isolator on transceiver side recovers the signal and then converts it into a standard level output to the CAN bus. Similarly, the transceiver side signal can also be modulated to high frequency and received by the digital side then output to RXD after demodulation and recovery. The ground on the digital side and the transceiver side can be completely separated. The isolation rating is up to 5 kV<sub>RMS</sub>, ensuring the integrity and security of signal transmission between the microcontroller and the high-voltage bus in actual use.

### 9.3.2. Dominant Time-Out

司

The CA-IS3062 device has the dominant timeout function, which prevents TXD from being pulled down to a low level due to software or hardware failure. This failure may cause the bus to stuck in the dominant state and thus the whole network communication will be locked. The dominant timeout function is achieved by setting a counter, which counts the negative edge of the TXD input signal. When the low-level duration of TXD is longer than the dominant timeout time  $t_{TXD\_DTO}$ , the transceiver will be turned off, and then the bus is released to the recessive state. The counter is set during the positive edge of the TXD input signal.

### 9.3.3. Thermal Shutdown

The CA-IS3062 device has integrated thermal shutdown protection function, which can protect the internal circuit of the device under over-temperature conditions. If the junction temperature of the device exceeds the thermal shutdown temperature  $T_{J(shutdown)}$ , the driver will be disabled, thereby blocking the signal transmission path from TXD to the bus. The typical thermal shutdown temperature is 165 °C. When the device junction temperature is lower than the thermal shutdown temperature, the driver will be re-enabled.

### 9.3.4. Current Limiting

The CA-IS3062 device has integrated current limiting function, which can prevent the device from being damaged by the large current when the transceiver side short-circuit occurs. Note that once the current-limiting protection occurs, it will be a large current in the device, which results in a larger loss.

### 9.4. Device Function Modes

**Table 9-1 Function Table Abbreviation**

| Word | Description    |

|------|----------------|

| Н    | High-Level     |

| L    | Low-Level      |

| X    | Unrelated      |

| Z    | High Impedance |

| ?    | Uncertain      |

| Open | Open Circuit   |

**Table 9-2 Driver Function Table**

| Input     | Out  | Bus State |           |

|-----------|------|-----------|-----------|

| TXD       | CANH | CANL      | bus state |

| L         | Н    | L         | Dominant  |

| H or Open | Z    | Z         | Recessive |

**Table 9-3 Receiver Function Table**

| CAN Differential Inputs  VID = VCANH — VCANL | Bus State | RXD |

|----------------------------------------------|-----------|-----|

| 0.9 V ≤ V <sub>ID</sub>                      | Dominant  | L   |

| 0.5 V < V <sub>ID</sub> < 0.9 V              | ?         | ?   |

| V <sub>ID</sub> ≤ 0.5 V                      | Recessive | Н   |

| Open (V <sub>ID</sub> ≈ 0 V)                 | Open      | Н   |

上海川土微电子有限公司

# **Table 9-4 Transceiver Function Table**

|        | Dri                | ver |           | Receiver                                               |         |           |  |  |

|--------|--------------------|-----|-----------|--------------------------------------------------------|---------|-----------|--|--|

| Inputs | Outputs  CANH CANL |     | Bus State | Differential Inpus                                     | RXD     | Bus State |  |  |

| TXD    |                    |     | Dus State | $V_{ID} = V_{CANH} - V_{CANL}$                         | Outputs | bus State |  |  |

| L      | Н                  | L   | Dominant  | 0.9 V ≤ V <sub>ID</sub>                                | L       | Dominant  |  |  |

| Н      | Z                  | Z   | Recessive | $0.5 \text{ V} < \text{V}_{\text{ID}} < 0.9 \text{ V}$ | ?       | ?         |  |  |

| Open   | Z                  | Z   | Recessive | V <sub>ID</sub> ≤ 0.5 V                                | Н       | Recessive |  |  |

| Х      | Z                  | Z   | Recessive | Open                                                   | Н       | Recessive |  |  |

# 10. Application Information

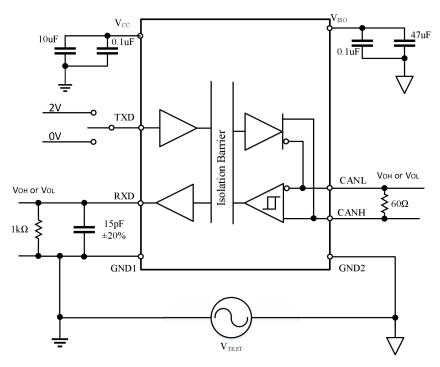

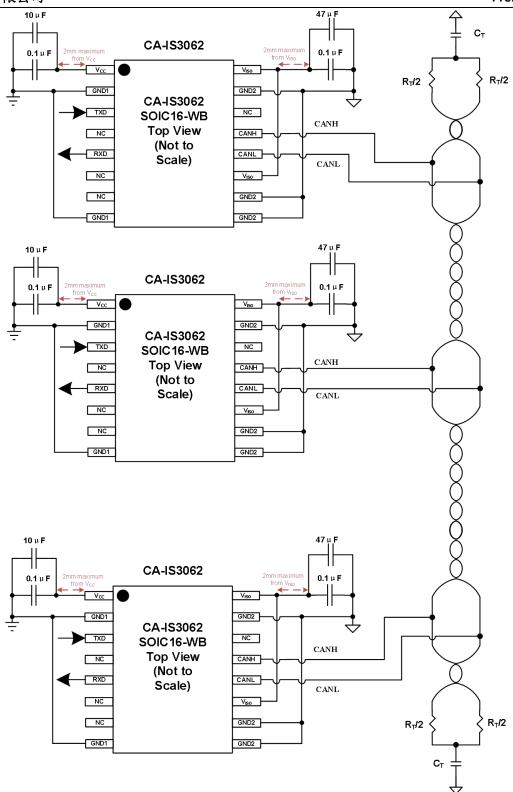

A  $10\mu F$  capacitor between  $V_{CC}$  and GND1, and a  $47\mu F$  capacitor between  $V_{ISO}$  and GND2, the CA-IS3062 can work normally. In the design the circuit, it is recommended to place a  $47\mu F$  capacitor between the  $V_{ISO}$  and GND2 . Figure 10-1 and Figure 10-2 are typical application diagrams of the CA-IS3062.

### Note:

1. Termination resistor R<sub>T</sub> should be equal to the characteristic impedance of the cable

Figure 10-1 CA-IS 3062 Typical CAN Node

CHIPANALOG

### Note:

- 1. Termination resistor R<sub>T</sub> should be equal to the characteristic impedance of the cable.

- 2. The CA-IS3062 device can support up to 110 nodes.

Figure 10-2 CA-IS 3062 Typical CAN Bus

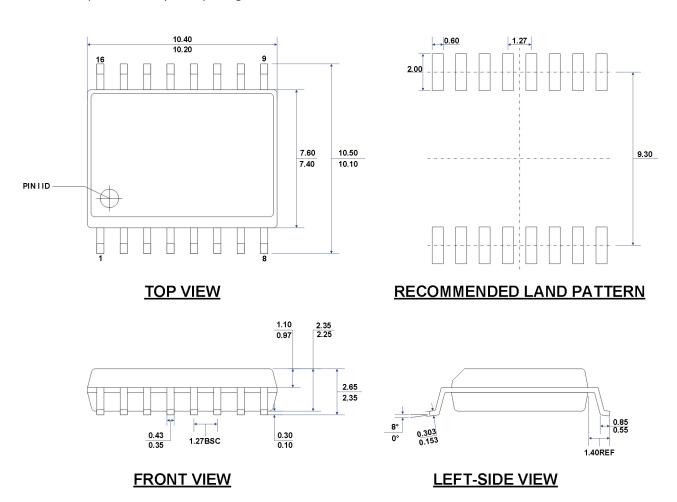

# 11. Package Information

# **SOIC16-WB Package**

The figure below illustrates the package details and the recommended land pattern details for the CA-IS3062 isolated CAN transceiver in a 16-pin wide-body SOIC package. The values for the dimensions are shown in millimeters.

Figure 11-1 CA-IS3062 SOIC16-WB Package

# 12. TAPE

# AND REEL INFORMATION

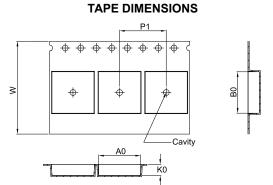

|    | · · · · · · · · · · · · · · · · · · ·                     |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

# Q1 Q2 Q1 Q2 Q3 Q4 Q3 Q4 Pocket Quadrants

\*All dimensions are nominal

| Device     | Package<br>Type | Package<br>Drawing | Pins | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width W1<br>(mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|------------|-----------------|--------------------|------|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| CA-IS3062W | SOIC            | W                  | 16   | 1000 | 330                      | 24.4                     | 10.8       | 10.7       | 2.9        | 12.0       | 24.0      | Q1               |

QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

# **Preliminary Version**

上海川土微电子有限公

言

# 13. Ordering Information

| Orderable<br>Device | Status <sup>1</sup> | Package<br>Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan | Lead/Ball<br>Finish | MSL Peak<br>Temp | Op<br>Temp(°C) | Device<br>Marking | Samples |

|---------------------|---------------------|-----------------|--------------------|------|----------------|----------|---------------------|------------------|----------------|-------------------|---------|

| CA-<br>IS3062W      | PREVIEW             | SOIC            | w                  | 16   | 1000           |          |                     |                  | -40 to 125     |                   |         |

<sup>1.</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY:CA has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but CA does not recommend using this part in new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

OBSOLETE:CA has discontinued the production of the device.

### **IMPORTANT NOTICE**

上海川土微电子有限公司

The above information is for reference only and is used to assist Chipanalog customers in design and development. Chipanalog reserves the right to change the above information due to technological innovation without prior notice.

Chipanalog products are all factory tested. The customers shall be responsible for self-assessment and determine whether it is applicable for their specific application. Chipanalog's authorization to use the resources is limited to the development of related applications that the Chipanalog products involved in. In addition, the resources shall not be copied or displayed. And Chipanalog shall not be liable for any claim, cost, and loss arising from the use of the resources.

# **Trademark Information**

Chipanalog Inc. ®, Chipanalog® are trademarks or registered trademarks of Chipanalog.

http://www.chipanalog.com