# **Microcomputer Components**

8-Bit CMOS Microcontroller

Data Sheet 08.94

# SIEMENS

# 8-Bit CMOS Microcontroller

C502

## Preliminary

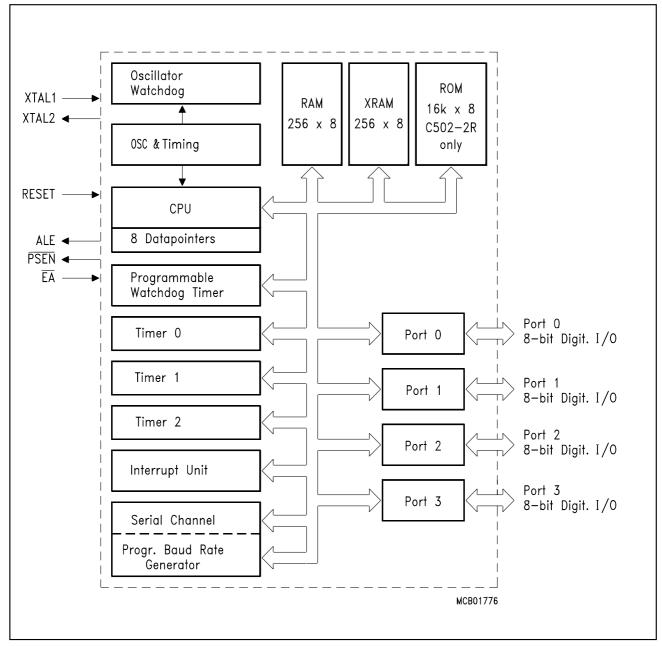

- Fully compatible to standard 8051 microcontroller

- Versions for 12 / 20 MHz operating frequency

- 16 K × 8 ROM (SAB-C502-2R only)

- 256 × 8 RAM

- 256 × 8 XRAM (additional on-chip RAM)

- Eight datapointers for indirect addressing of program and external data memory (including XRAM)

- Four 8-bit ports

- Three 16 -bit Timers / Counters (Timer 2 with Up/Down Counter feature)

- USART with programmable 10-bit Baudrate-Generator

- Six interrupt sources, two priority levels

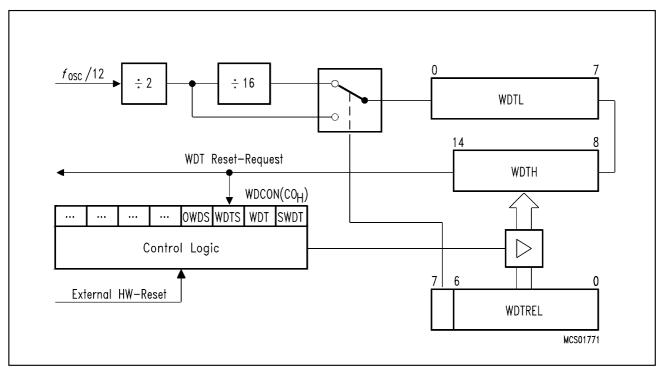

- Programmable 15-bit Watchdog Timer

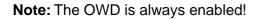

- Oscillator Watchdog

- Fast Power On Reset

- Power Saving Modes

- P-DIP-40 package and P-LCC-44 package

- Temperature ranges: SAB-C502

- SAF-C502

$T_{\text{A}}$ : 0 °C to 70 °C  $T_{\text{A}}$ : - 40 °C to 85 °C

The SAB-C502-L/C502-2R described in this document is compatible with the SAB 80C52 and can be used for all present SAB 80C52 applications.

The SAB-C502-2R contains a non-volatile 16 K  $\times$  8 read-only program memory, a volatile 256  $\times$  8 read/write data memory, four ports, three 16-bit timers/counters, a six source, two priority level interrupt structure, a serial port and versatile fail save mechanisms. The SAB-C502-L/C502-2R incorporates 256  $\times$  8 additional on-chip RAM called XRAM. For higher performance eight datapointers are implemented. The SAB-C502-L is identical, except that it lacks the program memory on chip. Therefore the term SAB-C502 refers to both versions within this specification unless otherwise noted.

# **Ordering Information**

| Туре           | Ordering<br>Code | Package  | Description<br>(8-Bit CMOS microcontroller)                     |

|----------------|------------------|----------|-----------------------------------------------------------------|

| SAB-C502-LN    | Q67120-C838      | P-LCC-44 | for external memory 12 MHz                                      |

| SAB-C502-LP    | Q67120-C889      | P-DIP-40 |                                                                 |

| SAB-C502-2RN   | Q67120-C839      | P-LCC-44 | with mask-programmable ROM, 12 MHz                              |

| SAB-C502-2RP   | Q67120-C890      | P-DIP-40 |                                                                 |

| SAB-C502-L20N  | Q67120-C885      | P-LCC-44 | for external memory 20 MHz                                      |

| SAB-C502-L20P  | Q67120-C891      | P-DIP-40 |                                                                 |

| SAB-C502-2R20N | Q67120-C884      | P-LCC-44 | with mask-programmable ROM, 20 MHz                              |

| SAB-C502-2R20P | Q67120-C892      | P-DIP-40 |                                                                 |

| SAF-C502-LN    | Q67120-C883      | P-LCC-44 | for external ROM, 12 MHz,                                       |

| SAF-C502-LP    | Q67120-C893      | P-DIP-40 | ext. temp. – 40 °C to 85 °C                                     |

| SAF-C502-2RN   | Q67120-C886      | P-LCC-44 | with mask-programmable ROM,                                     |

| SAF-C502-2RP   | Q67120-C894      | P-DIP-40 | 12 MHz, ext. temp. – 40 °C to 85 °C                             |

| SAF-C502-L20N  | Q67120-C887      | P-LCC-44 | for external memory, 20 MHz,                                    |

| SAF-C502-L20P  | Q67120-C895      | P-DIP-40 | ext. temp. – 40 °C to 85 °C                                     |

| SAF-C502-2R20N | Q67120-C888      | P-LCC-44 | with mask-programmable ROM, 20 MHz, ext. temp. – 40 °C to 85 °C |

| SAF-C502-2R20P | Q67120-C896      | P-DIP-40 |                                                                 |

Note: Extended temperature range – 40 °C to 110 °C (SAH-C502) on request.

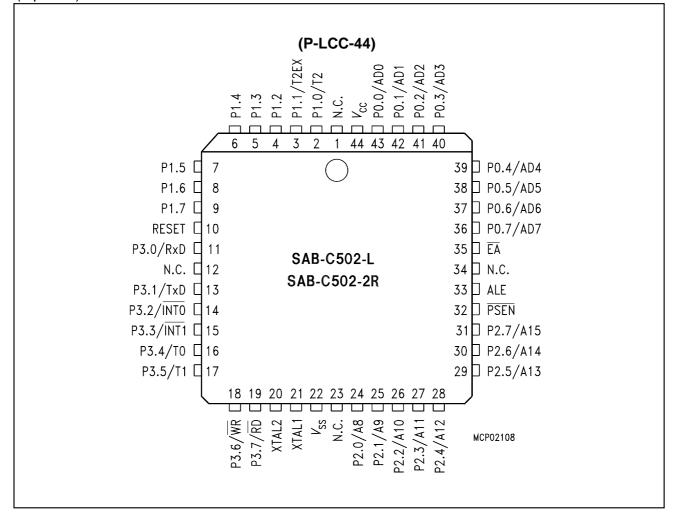

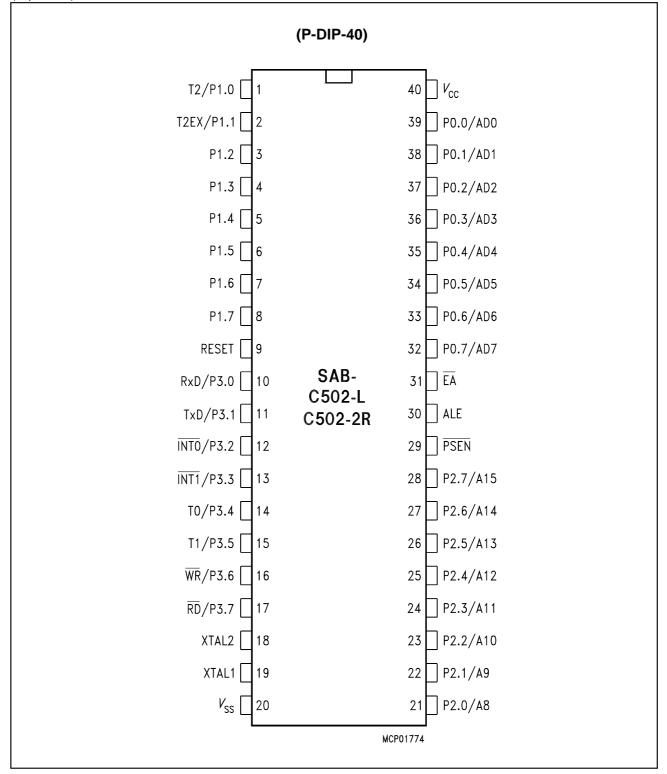

### Pin Configuration

(top view)

(top view)

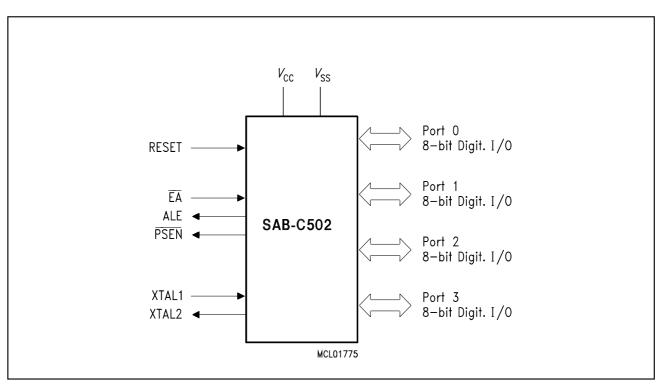

Logic Symbol

C502

# **Pin Definitions and Functions**

| Symbol      | Pin N    | umber    | I/O*) | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|-------------|----------|----------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|             | P-LCC-44 | P-DIP-40 |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| P1.7 – P1.0 | 9–2      | 8–1      | 1     | <b>Port 1</b><br>is a bidirectional I/O port with internal pull-up<br>resistors. Port 1 pins that have 1s written to<br>them are pulled high by the internal pull-up<br>resistors, and in that state can be used as<br>inputs. As inputs, port 1 pins being externally<br>pulled low will source current ( $I_{IL}$ , in the DC<br>characteristics) because of the internal pull-up<br>resistors. Port 1 also contains the timer 2 pins<br>as secondary function. The output latch corre-<br>sponding to a secondary function must be pro-<br>grammed to a one (1) for that function to<br>operate.<br>The secondary functions are assigned to the<br>pins of port 1, as follows: |  |  |  |  |

|             | 2<br>3   | 1<br>2   |       | P1.0 T2 Input to counter 2<br>P1.1 T2EX Capture - Reload trigger of<br>timer 2 / Up-Down count                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

\*) I = Input O = Output

# Pin Definitions and Functions (cont'd)

| Symbol      | Pin N     | umber    | I/O*) | Funct                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Function |                                                                                                                        |  |  |

|-------------|-----------|----------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------------------------------------------------------------------------------------------------------------|--|--|

|             | P-LCC-44  | P-DIP-40 |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |                                                                                                                        |  |  |

| P3.0 – P3.7 | 11, 13–19 | 10–17    | Ι/Ο   | <b>Port 3</b><br>is a bidirectional I/O port with internal pull-<br>resistors. Port 3 pins that have 1s written<br>them are pulled high by the internal pull-<br>resistors, and in that state can be used<br>inputs. As inputs, port 3 pins being externa<br>pulled low will source current ( $I_{IL}$ , in the I<br>characteristics) because of the internal pull-<br>resistors. Port 3 also contains the interru<br>timer, serial port 0 and external memory stro<br>pins that are used by various options. The o<br>put latch corresponding to a secondary fur<br>tion must be programmed to a one (1) for th<br>function to operate.<br>The secondary functions are assigned to t<br>pins of port 3, as follows: |          |                                                                                                                        |  |  |

|             | 11        | 10       |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | R×D      | receiver data input<br>(asynchronous) or data input/<br>output (synchronous) of serial                                 |  |  |

|             | 13        | 11       |       | P3.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | T×D      | interface 0<br>transmitter data output<br>(asynchronous) or clock output<br>(synchronous) of the serial<br>interface 0 |  |  |

|             | 14        | 12       |       | P3.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | INT0     | interrupt 0 input/timer 0 gate control                                                                                 |  |  |

|             | 15        | 13       |       | P3.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | INT1     | interrupt 1 input/timer 1 gate control                                                                                 |  |  |

|             | 16        | 14       |       | P3.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Т0       | counter 0 input                                                                                                        |  |  |

|             | 17        | 15       |       | P3.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | T1       | counter 1 input                                                                                                        |  |  |

|             | 18        | 16       |       | P3.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | WR       | the write control signal latches<br>the data byte from port 0 into the<br>external data memory                         |  |  |

|             | 19        | 17       |       | P3.7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | RD       | the read control signal enables<br>the external data memory to<br>port 0                                               |  |  |

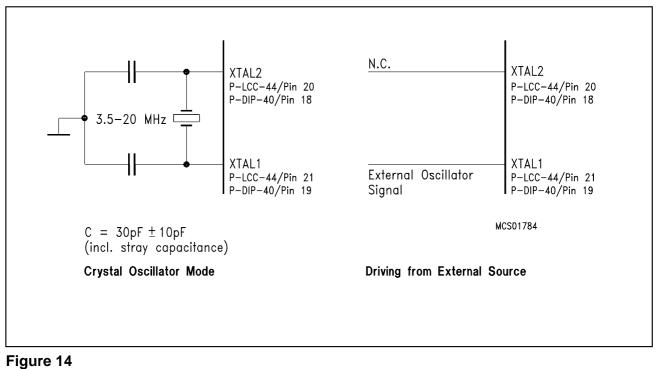

| XTAL2       | 20        | 18       | _     | XTAL:<br>Outpu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          | e inverting oscillator amplifier                                                                                       |  |  |

\*)I = Input O = Output

# Pin Definitions and Functions (cont'd)

| Symbol      | Pin N    | umber    | I/O*) | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|-------------|----------|----------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|             | P-LCC-44 | P-DIP-40 |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

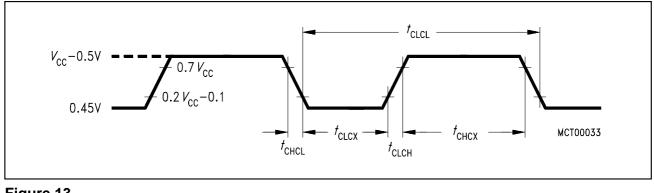

| XTAL1       | 21 19 –  |          | _     | XTAL1<br>Input to the inverting oscillator amplifier and<br>input to the internal clock generator circuits.<br>To drive the device from an external clock<br>source, XTAL1 should be driven, while XTAL2<br>is left unconnected. There are no requirement<br>on the duty cycle of the external clock signal,<br>since the input to the internal clocking circuitry<br>is divided down by a divide-by-two flip-flop.<br>Minimum and maximum high and low times as<br>well as rise fall times specified in the AC<br>characteristics must be observed.                                                                                                                                                                                                                                                                              |  |  |  |

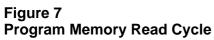

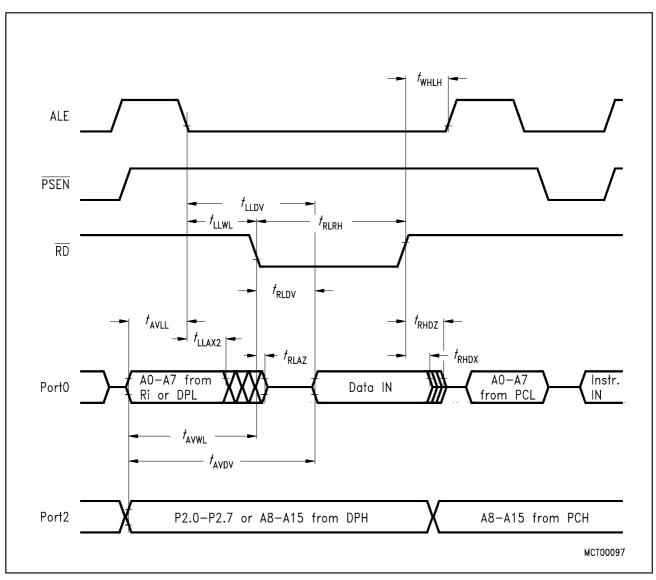

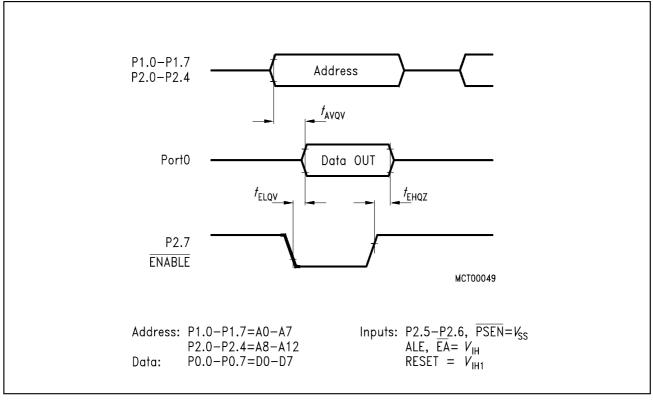

| P2.0 – P2.7 | 24–31    | 21–28    | I/O   | <b>Port 2</b><br>ia a bidirectional I/O port with internal pull-up<br>resistors. Port 2 pins that have 1s written to<br>them are pulled high by the internal pull-up<br>resistors, and in that state can be used as<br>inputs. As inputs, port 2 pins being externally<br>pulled low will source current ( $I_{IL}$ , in the DC<br>characteristics) because of the internal pull-up<br>resistors. Port 2 emits the high-order address<br>byte during fetches from external program<br>memory and during accesses to external data<br>memory that use 16-bit addresses (MOVX<br>@DPTR). In this application it uses strong<br>internal pull-up resistors when issuing 1s.<br>During accesses to external data memory that<br>use 8-bit addresses (MOVX @Ri), port 2<br>issues the contents of the P2 special function<br>register. |  |  |  |

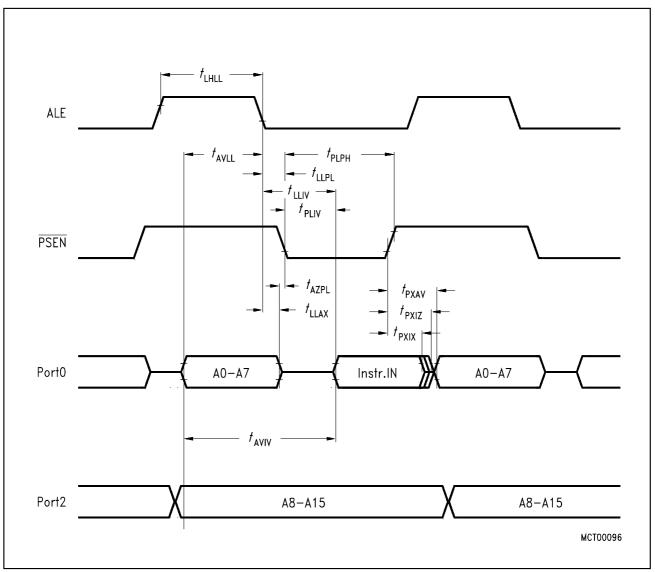

| PSEN        | 32       | 29       | 0     | The <b>Program Store Enable</b><br>output is a control signal that enables the<br>external program memory to the bus during<br>external fetch operations. It is activated every<br>six oscillator periodes except during external<br>data memory accesses. Remains high during<br>internal program execution.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

\*) I = Input O = Output

# Pin Definitions and Functions (cont'd)

| Symbol          | Pin N            | umber    | I/O*) | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

|-----------------|------------------|----------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                 | P-LCC-44         | P-DIP-40 |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| RESET           | 10 9 I           |          | 1     | <b>RESET</b><br>A high level on this pin for two machine cycle while the oscillator is running resets the device. An internal diffused resistor to $V_{ss}$ permits power-on reset using only an external capacitor to $V_{cc}$ .                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| ALE             | 33               | 30       | 0     | The Address Latch Enable<br>output is used for latching the low-byte of the<br>address into external memory during normal<br>operation. It is activated every six oscillator<br>periodes except during an external data<br>memory access.                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| ĒĀ              | 35               | 31       | 1     | <b>External Access Enable</b><br>When held at high level, instructions are<br>fetched from the internal ROM (SAB-C502-2R<br>only) when the PC is less than 4000 <sub>H</sub> . When<br>held at low level, the SAB-C502 fetches all<br>instructions from external program memory.<br>For the SAB-C502-L this pin must be tied low.                                                                                                                                                                                                                                  |  |  |  |  |

| P0.0 – P0.7     | 43–36            | 39–32    | I/O   | <b>Port 0</b><br>is an 8-bit open-drain bidirectional I/O port.<br>Port 0 pins that have 1s written to them float,<br>and in that state can be used as high-<br>impedance inputs. Port 0 is also the<br>multiplexed low-order address and data bus<br>during accesses to external program or data<br>memory. In this application it uses strong<br>internal pull-up resistors when issuing 1s.<br>Port 0 also outputs the code bytes during<br>program verification in the SAB-C502-2R.<br>External pull-up resistors are required during<br>program verification. |  |  |  |  |

| V <sub>SS</sub> | 22               | 20       | -     | Circuit ground potential                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| V <sub>cc</sub> | 44               | 40       | -     | Supply terminal for all operating modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| N.C.            | 1, 12,<br>23, 34 | -        | -     | No connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

\*) I = Input O = Output

### **Functional Description**

The SAB-C502 is fully compatible to the standard 8051 microcontroller family.

It is compatible with the SAB 80C52. While maintaining all architectural and operational characteristics of the SAB 80C52 the SAB-C502 incorporates some enhancements in the Timer2 and Fail Save Mechanism Unit.

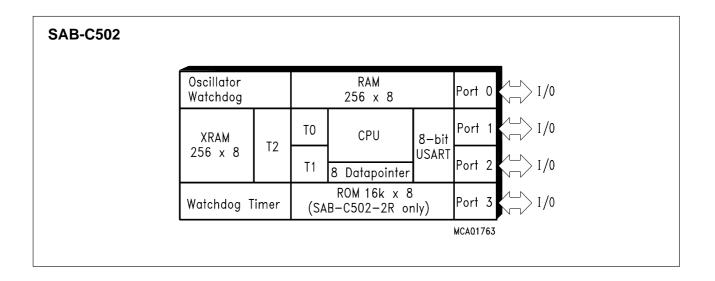

Figure 1 shows a block diagram of the SAB-C502.

# CPU

The SAB-C502 is efficient both as a controller and as an arithmetic processor. It has extensive facilities for binary and BCD arithmetic and excels in its bit-handling capabilities. Efficient use of program memory results from an instruction set consisting of 44 % one-byte, 41 % two-byte, and 15 % three-byte instructions. With a 12 MHz crystal, 58 % of the instructions execute in 1.0  $\mu$ s (18 MHz : 667 ns).

### **Special Function Register PSW**

|                       | MSB |    |    |     |     |    |    | LSB |     |

|-----------------------|-----|----|----|-----|-----|----|----|-----|-----|

| Bit No.               | 7   | 6  | 5  | 4   | 3   | 2  | 1  | 0   |     |

| Addr. D0 <sub>H</sub> | CY  | AC | F0 | RS1 | RS0 | OV | F1 | Р   | PSW |

| Bit | Function |                                                                                                                                                       |  |  |  |  |

|-----|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| СҮ  |          | Carry Flag                                                                                                                                            |  |  |  |  |

| AC  |          | Auxiliary Carry Flag (for BCD operations)                                                                                                             |  |  |  |  |

| F0  |          | General Purpose Flag                                                                                                                                  |  |  |  |  |

| RS1 | RS0      | Register Bank select control bits                                                                                                                     |  |  |  |  |

| 0   | 0        | Bank 0 selected, data address 00 <sub>H</sub> - 07 <sub>H</sub>                                                                                       |  |  |  |  |

| 0   | 1        | Bank 1 selected, data address 08 <sub>H</sub> - 0F <sub>H</sub>                                                                                       |  |  |  |  |

| 1   | 0        | Bank 2 selected, data address 10 <sub>H</sub> - 17 <sub>H</sub>                                                                                       |  |  |  |  |

| 1   | 1        | Bank 3 selected, data address 18 <sub>H</sub> - 1F <sub>H</sub>                                                                                       |  |  |  |  |

| ον  |          | Overflow Flag                                                                                                                                         |  |  |  |  |

| F1  |          | General Purpose Flag                                                                                                                                  |  |  |  |  |

| P   |          | Parity Flag.<br>Set/cleared by hardware each instruction cycle to indicate an odd/<br>even number of "one" bits in the accumulator, i.e. even parity. |  |  |  |  |

Reset value of PSW is 00H.

### **Special Function Registers**

All registers, except the program counter and the four general purpose register banks, reside in the special function register area.

The 36 special function register (SFR) include pointers and registers that provide an interface between the CPU and the other on-chip peripherals. There are also 128 directly addressable bits within the SFR area.

All SFRs are listed in **table 1**, **table 2** and **table 3**. In **table 1** they are organized in numeric order of their addresses. In **table 2** they are organized in groups which refer to the functional blocks of the SAB-C502. **Table 3** illustrates the contents of the SFRs.

| Address         | Register                | Contents<br>after Reset            | Address         | Register                | Contents<br>after Reset       |

|-----------------|-------------------------|------------------------------------|-----------------|-------------------------|-------------------------------|

| 80 <sub>H</sub> | <b>P0</b> <sup>1)</sup> | FF <sub>H</sub>                    | 98 <sub>H</sub> | SCON <sup>1)</sup>      | 00 <sub>H</sub>               |

| 81 <sub>H</sub> | SP                      | 07 <sub>H</sub>                    | 99 <sub>H</sub> | SBUF                    | XX <sub>H</sub> <sup>2)</sup> |

| 82 <sub>H</sub> | DPL                     | 00 <sub>H</sub>                    | 9A <sub>H</sub> | reserved                | XX <sub>H</sub> <sup>2)</sup> |

| 83 <sub>H</sub> | DPH                     | 00 <sub>H</sub>                    | 9B <sub>H</sub> | reserved                | XX <sub>H</sub> <sup>2)</sup> |

| <sup>84</sup> H | reserved                |                                    | 9CH             | reserved                | XX <sub>H</sub> <sup>2)</sup> |

| 85 <sub>H</sub> | reserved                |                                    | 9DH             | reserved                | XX <sub>H</sub> <sup>2)</sup> |

| 86 <sub>H</sub> | WDTREL                  | 00 <sub>H</sub>                    | 9E <sub>H</sub> | reserved                | XX <sub>H</sub> <sup>2)</sup> |

| 87 <sub>H</sub> | PCON                    | 000X0000 <sub>B<sup>2)</sup></sub> | 9F <sub>H</sub> | reserved                | XX <sub>H</sub> <sup>2)</sup> |

| 88 <sub>H</sub> | TCON <sup>1)</sup>      | 00 <sub>H</sub>                    | A0 <sub>H</sub> | <b>P2</b> <sup>1)</sup> | FFH                           |

| 89 <sub>H</sub> | TMOD                    | 00 <sub>H</sub>                    | A1 <sub>H</sub> | reserved                | XX <sub>H</sub> <sup>2)</sup> |

| 8A <sub>H</sub> | TL0                     | 00 <sub>H</sub>                    | A2 <sub>H</sub> | reserved                | XX <sub>H</sub> <sup>2)</sup> |

| 8B <sub>H</sub> | TL1                     | 00 <sub>H</sub>                    | A3 <sub>H</sub> | reserved                | XX <sub>H</sub> <sup>2)</sup> |

| 8C <sub>H</sub> | TH0                     | 00 <sub>H</sub>                    | A4 <sub>H</sub> | reserved                | XX <sub>H</sub> <sup>2)</sup> |

| 8D <sub>H</sub> | TH1                     | 00H                                | A5 <sub>H</sub> | reserved                | XX <sub>H</sub> <sup>2)</sup> |

| 8EH             | reserved                | XX <sub>H</sub> <sup>2)</sup>      | A6 <sub>H</sub> | reserved                | XX <sub>H</sub> <sup>2)</sup> |

| 8F <sub>H</sub> | reserved                | XX <sub>H</sub> <sup>2)</sup>      | A7 <sub>H</sub> | reserved                | XX <sub>H</sub> <sup>2)</sup> |

| 90 <sub>H</sub> | <b>P1</b> <sup>1)</sup> | FFH                                | A8 <sub>H</sub> | <b>IE</b> <sup>1)</sup> | 0X000000B <sup>2)</sup>       |

| 91 <sub>H</sub> | XPAGE                   | 00 <sub>H</sub>                    | A9 <sub>H</sub> | reserved                | XX <sub>H</sub> <sup>2)</sup> |

| 92 <sub>H</sub> | DPSEL                   | XXXXX000 <sub>B<sup>2)</sup></sub> | AAH             | SRELL                   | D9 <sub>H</sub>               |

| 93 <sub>H</sub> | reserved                | XX <sub>H<sup>2)</sup></sub>       | ABH             | reserved                | XX <sub>H</sub> <sup>2)</sup> |

| 94 <sub>H</sub> | XCON                    | F8 <sub>H</sub>                    | ACH             | reserved                | XX <sub>H</sub> <sup>2)</sup> |

| 95 <sub>H</sub> | reserved                | XX <sub>H</sub> <sup>2)</sup>      | ADH             | reserved                | XX <sub>H</sub> <sup>2)</sup> |

| 96 <sub>H</sub> | reserved                | XX <sub>H</sub> <sup>2)</sup>      | AEH             | reserved                | XX <sub>H</sub> <sup>2)</sup> |

| 97 <sub>H</sub> | reserved                | XX <sub>H</sub> <sup>2)</sup>      | AF <sub>H</sub> | reserved                | XX <sub>H</sub> <sup>2)</sup> |

# Table 1Special Function Register in Numeric Order of their Addresses

<sup>1)</sup>: Bit-addressable Special Function Register

<sup>2)</sup>: X means that the value is indeterminate and the location is reserved

# Table 1 Special Function Register in Numeric Order of their Addresses (cont'd)

| Address         | Register                   | Contents<br>after Reset             | Address         | Register                 | Contents<br>after Reset       |

|-----------------|----------------------------|-------------------------------------|-----------------|--------------------------|-------------------------------|

| B0 <sub>H</sub> | <b>P3</b> <sup>1)</sup>    | FF <sub>H</sub>                     | D8 <sub>H</sub> | BAUD                     | 0XXXXXXAB                     |

| B1 <sub>H</sub> | SYSCON                     | XXXXXX01B <sup>2)</sup>             | D9 <sub>H</sub> | reserved                 | XX <sub>H<sup>2)</sup></sub>  |

| B2 <sub>H</sub> | reserved                   | XX <sub>H<sup>2)</sup></sub>        | DAH             | reserved                 | XX <sub>H</sub> <sup>2)</sup> |

| B3 <sub>H</sub> | reserved                   | XX <sub>H</sub> <sup>2)</sup>       | DB <sub>H</sub> | reserved                 | XX <sub>H</sub> <sup>2)</sup> |

| B4 <sub>H</sub> | reserved                   | XX <sub>H</sub> <sup>2)</sup>       |                 | reserved                 | XX <sub>H</sub> <sup>2)</sup> |

| B5 <sub>H</sub> | reserved                   | XX <sub>H</sub> <sup>2)</sup>       | DD <sub>H</sub> | reserved                 | XX <sub>H</sub> <sup>2)</sup> |

| N6 <sub>H</sub> | reserved                   | XX <sub>H</sub> <sup>2)</sup>       | DEH             | reserved                 | XX <sub>H</sub> <sup>2)</sup> |

| в7 <sub>Н</sub> | reserved                   | XX <sub>H</sub> <sup>2)</sup>       | DF <sub>H</sub> | reserved                 | XX <sub>H</sub> <sup>2)</sup> |

| B8 <sub>H</sub> | <b>IP</b> <sup>1)</sup>    | X000000 <sub>B</sub> <sup>2)</sup>  | E0 <sub>H</sub> | <b>ACC</b> <sup>1)</sup> | 00 <sub>H</sub>               |

| B9 <sub>H</sub> | reserved                   | XX <sub>H</sub> <sup>2)</sup>       | E1 <sub>H</sub> | reserved                 | XX <sub>H</sub> <sup>2)</sup> |

| BAH             | SRELH                      | XXXXXX11 <sub>B<sup>2)</sup></sub>  | E2 <sub>H</sub> | reserved                 | XX <sub>H</sub> <sup>2)</sup> |

| BBH             | reserved                   | XX <sub>H<sup>2)</sup></sub>        | E3 <sub>H</sub> | reserved                 | XX <sub>H</sub> <sup>2)</sup> |

| BC <sub>H</sub> | reserved                   | XX <sub>H</sub> <sup>2)</sup>       | E4 <sub>H</sub> | reserved                 | XX <sub>H</sub> <sup>2)</sup> |

| BD <sub>H</sub> | reserved                   | XX <sub>H</sub> <sup>2)</sup>       | E5 <sub>H</sub> | reserved                 | XX <sub>H</sub> <sup>2)</sup> |

| BEH             | reserved                   | XX <sub>H</sub> <sup>2)</sup>       | E6 <sub>H</sub> | reserved                 | XX <sub>H</sub> <sup>2)</sup> |

| BFH             | reserved                   | XX <sub>H</sub> <sup>2)</sup>       | E7 <sub>H</sub> | reserved                 | XX <sub>H</sub> <sup>2)</sup> |

| C0H             | WDCON <sup>1)</sup>        | XXXX0000 <sub>B</sub> <sup>2)</sup> | E8 <sub>H</sub> | reserved                 | XX <sub>H</sub> <sup>2)</sup> |

| C1 <sub>H</sub> | reserved                   | XX <sub>H<sup>2)</sup></sub>        | E9 <sub>H</sub> | reserved                 | XX <sub>H</sub> <sup>2)</sup> |

| C2 <sub>H</sub> | reserved                   | XX <sub>H</sub> <sup>2)</sup>       | EAH             | reserved                 | XX <sub>H</sub> <sup>2)</sup> |

| C3 <sub>H</sub> | reserved                   | XX <sub>H</sub> <sup>2)</sup>       | EBH             | reserved                 | XX <sub>H</sub> <sup>2)</sup> |

| C4 <sub>H</sub> | reserved                   | XX <sub>H</sub> <sup>2)</sup>       | ECH             | reserved                 | XX <sub>H</sub> <sup>2)</sup> |

| C5 <sub>H</sub> | reserved                   | XX <sub>H</sub> <sup>2)</sup>       | EDH             | reserved                 | XX <sub>H</sub> <sup>2)</sup> |

| C6 <sub>H</sub> | reserved                   | XX <sub>H</sub> <sup>2)</sup>       | EEH             | reserved                 | XX <sub>H</sub> <sup>2)</sup> |

| C7 <sub>H</sub> | reserved                   | XX <sub>H</sub> <sup>2)</sup>       | EFH             | reserved                 | XX <sub>H</sub> <sup>2)</sup> |

| C8 <sub>H</sub> | <b>T2CON</b> <sup>1)</sup> | 00 <sub>H</sub>                     | F0 <sub>H</sub> | <b>B</b> <sup>1)</sup>   | 00 <sub>H</sub>               |

| C9H             | T2MOD                      | XXXXXXX0B <sup>2)</sup>             | F1 <sub>H</sub> | reserved                 | XX <sub>H</sub> <sup>2)</sup> |

| CAH             | RC2L                       | 00 <sub>H</sub>                     | F2 <sub>H</sub> | reserved                 | XX <sub>H</sub> <sup>2)</sup> |

| СВН             | RC2H                       | 00 <sub>H</sub>                     | F3 <sub>H</sub> | reserved                 | XX <sub>H</sub> <sup>2)</sup> |

| CCH             | TL2                        | 00 <sub>H</sub>                     | F4 <sub>H</sub> | reserved                 | XX <sub>H</sub> <sup>2)</sup> |

| CDH             | TH2                        | 00H                                 | F5 <sub>H</sub> | reserved                 | XX <sub>H</sub> <sup>2)</sup> |

| CEH             | reserved                   | XX <sub>H</sub> <sup>2)</sup>       | F6 <sub>H</sub> | reserved                 | XX <sub>H</sub> <sup>2)</sup> |

| CF <sub>H</sub> | reserved                   | XX <sub>H</sub> <sup>2)</sup>       | F7 <sub>H</sub> | reserved                 | XX <sub>H</sub> <sup>2)</sup> |

| D0 <sub>H</sub> | <b>PSW</b> <sup>1)</sup>   | 00 <sub>H</sub>                     | F8 <sub>H</sub> | reserved                 | XX <sub>H</sub> <sup>2)</sup> |

| D1 <sub>H</sub> | reserved                   | XX <sub>H</sub> <sup>2)</sup>       | F9 <sub>H</sub> | reserved                 | XX <sub>H</sub> <sup>2)</sup> |

| D2 <sub>H</sub> | reserved                   | XX <sub>H</sub> <sup>2)</sup>       | FAH             | reserved                 | XX <sub>H</sub> <sup>2)</sup> |

| D3 <sub>H</sub> | reserved                   | XX <sub>H</sub> <sup>2)</sup>       | FBH             | reserved                 | XX <sub>H</sub> <sup>2)</sup> |

| D4 <sub>H</sub> | reserved                   | XX <sub>H</sub> <sup>2)</sup>       | FCH             | reserved                 | XX <sub>H</sub> <sup>2)</sup> |

| D5 <sub>H</sub> | reserved                   | XX <sub>H</sub> <sup>2)</sup>       | FD <sub>H</sub> | reserved                 | XX <sub>H</sub> <sup>2)</sup> |

| D6 <sub>H</sub> | reserved                   | XX <sub>H</sub> <sup>2)</sup>       | FEH             | reserved                 | XX <sub>H</sub> <sup>2)</sup> |

| D7 <sub>H</sub> | reserved                   | XX <sub>H</sub> <sup>2)</sup>       | FFH             | reserved                 | XX <sub>H</sub> <sup>2)</sup> |

1): Bit-addressable Special Function Register2): X means that the value is indeterminate and the location is reserved

### Table 2 **Special Function Registers - Functional Blocks**

| Block               | Symbol                                                       | Name                                                                                                                                                                                                        | Address                                                                                                                                                                                                    | Contents<br>after Reset                                                                                                                     |

|---------------------|--------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| CPU                 | ACC<br>B<br>DPH<br>DPL<br>DPSEL<br>PSW<br>SP                 | Accumulator<br>B-Register<br>Data Pointer, High Byte<br>Data Pointer, Low Byte<br>Data pointer select register<br>Program Status Word Register<br>Stack Pointer                                             | $\begin{array}{c} \textbf{E0}_{\textbf{H}}^{1)} \\ \textbf{F0}_{\textbf{H}}^{1)} \\ 83_{\textbf{H}} \\ 82_{\textbf{H}} \\ 92_{\textbf{H}} \\ \textbf{D0}_{\textbf{H}}^{1)} \\ 81_{\textbf{H}} \end{array}$ | 00 <sub>H</sub><br>00 <sub>H</sub><br>00 <sub>H</sub><br>00 <sub>H</sub><br>XXXX X000 B <sup>3)</sup><br>00 <sub>H</sub><br>07 <sub>H</sub> |

| Interrupt<br>System | IE<br>IP                                                     | Interrupt Enable Register<br>Interrupt Priority Register                                                                                                                                                    | A8 <sub>H</sub> <sup>1)</sup><br>B8 <sub>H</sub> <sup>1)</sup>                                                                                                                                             | 0X00 0000 B <sup>3)</sup>                                                                                                                   |

| Ports               | P0<br>P1<br>P2<br>P3                                         | Port 0<br>Port 1<br>Port 2<br>Port 3                                                                                                                                                                        | 80H <sup>1)</sup><br>90H <sup>1)</sup><br>A0H <sup>1)</sup><br>B0H <sup>1)</sup>                                                                                                                           | FF <sub>H</sub><br>FF <sub>H</sub><br>FF <sub>H</sub><br>FF <sub>H</sub>                                                                    |

| XRAM                | XPAGE<br>XCON<br>SYSCON                                      | Page addr. reg. for XRAM<br>XRAM startaddress (highbyte)<br>XRAM control register                                                                                                                           | 91 <sub>H</sub><br>94 <sub>H</sub><br>B1 <sub>H</sub>                                                                                                                                                      | 00 <sub>H</sub><br>F8 <sub>H</sub><br>XXXX XX01 <sub>B</sub> <sup>3)</sup>                                                                  |

| Serial<br>Channels  | PCON <sup>2)</sup><br>SBUF<br>SCON<br>SRELL<br>SRELH<br>BAUD | Power Control Register<br>Serial Channel Buffer Reg.<br>Serial Channel Control Reg.<br>Baudrate Generator Reloadvalue, Lowbyte<br>Baudrate Generator Reloadvalue, Highbyte<br>Baudrate Generator Enable Bit | 87 <sub>H</sub><br>99 <sub>H</sub><br><b>98<sub>H</sub></b> <sup>1)</sup><br>AA <sub>H</sub><br>BA <sub>H</sub><br><b>D8<sub>H</sub></b> <sup>1)</sup>                                                     | $\begin{array}{c} 00_{H} \\ XX_{H}^{3)} \\ 00_{H} \\ D9_{H} \\ XXXX \ XX11_{B}^{3)} \\ 0XXX \ XXXX_{B}^{3)} \end{array}$                    |

| Timer 0/<br>Timer 1 | TCON<br>TH0<br>TH1<br>TL0<br>TL1<br>TMOD                     | Timer 0/1 Control Register<br>Timer 0, High Byte<br>Timer 1, High Byte<br>Timer 0, Low Byte<br>Timer 1, Low Byte<br>Timer Mode Register                                                                     | 88 <sub>H</sub> <sup>1)</sup><br>8C <sub>H</sub><br>8D <sub>H</sub><br>8A <sub>H</sub><br>8B <sub>H</sub><br>89 <sub>H</sub>                                                                               | 00 <sub>H</sub><br>00 <sub>H</sub><br>00 <sub>H</sub><br>00 <sub>H</sub><br>00 <sub>H</sub>                                                 |

| Timer 2             | T2CON<br>T2MOD<br>RC2L<br>RC2H<br>TH2<br>TL2                 | Timer 2 Control Register<br>Timer 2 Mode Register<br>Timer 2, Reload Capture Register, Low Byte<br>Timer 2, Reload Capture Register, High Byte<br>Timer 2, High Byte<br>Timer 2, Low Byte                   | С8 <sub>Н</sub> <sup>1)</sup><br>С9 <sub>Н</sub><br>СА <sub>Н</sub><br>СВ <sub>Н</sub><br>СD <sub>Н</sub><br>СС <sub>Н</sub>                                                                               | 00 <sub>H</sub><br>XXXX XXX0 B <sup>3)</sup><br>00 <sub>H</sub><br>00 <sub>H</sub><br>00 <sub>H</sub>                                       |

| Watchdog            | WDCON<br>WDTREL                                              | Watchdog Timer Control Register<br>Watchdog Timer Reload Reg.                                                                                                                                               | <b>C0<sub>H</sub><sup>1)</sup></b><br>86 <sub>H</sub>                                                                                                                                                      | XXXX 0000 <sub>B</sub> <sup>3)</sup><br>00 <sub>H</sub>                                                                                     |

| Pow. Sav.<br>Modes  | PCON <sup>2)</sup>                                           | Power Control Register                                                                                                                                                                                      | 87 <sub>H</sub>                                                                                                                                                                                            | 000X 0000 <sub>B<sup>3)</sup></sub>                                                                                                         |

<sup>1)</sup>: Bit-addressable special function registers

<sup>2)</sup>: This special function register is listed repeatedly since some bits of it also belong to other functional blocks. <sup>3)</sup>: X means that the value is indeterminate and the location is reserved

# Table 3

# Contents of SFR's, SFR's in Numeric Order

| Address         | Register | Bit 7 | 6   | 5    | 4      | 3    | 2   | 1    | 0    |

|-----------------|----------|-------|-----|------|--------|------|-----|------|------|

| <sup>80</sup> H | P0       |       |     |      |        |      |     |      |      |

| 81 <sub>H</sub> | SP       |       |     |      | <br>   |      |     |      |      |

| 82 <sub>H</sub> | DPL      |       |     |      | <br>   |      |     |      |      |

| 83 <sub>H</sub> | DPH      |       |     |      | I<br>I |      |     |      |      |

| 86 <sub>H</sub> | WDTREL   |       |     | <br> | I      | <br> |     |      | <br> |

| 87 <sub>H</sub> | PCON     | SMOD  | PDS | IDLS | · _    | GF1  | GF0 | PDE  | IDLE |

| <sup>88</sup> H | TCON     | TF1   | TR1 | TF0  | TR0    | IE1  | IT1 | IE0  | IT0  |

| <sup>89</sup> H | TMOD     | GATE  | C/T | M1   | MO     | GATE | C/T | M1   | MO   |

| 8A <sub>H</sub> | TL0      |       |     |      |        |      |     | <br> | <br> |

| 8BH             | TL1      |       |     |      |        |      |     | 1    |      |

| 8C <sub>H</sub> | TH0      |       |     |      |        |      |     | 1    |      |

| 8D <sub>H</sub> | TH1      |       |     |      |        |      |     |      |      |

| 90 <sub>H</sub> | P1       |       |     |      |        |      |     |      |      |

| 91 <sub>H</sub> | XPAGE    |       |     | <br> | <br>   | <br> |     | <br> |      |

| 92 <sub>H</sub> | DPSEL    | _     | _   | _    |        | _    | .2  | .1   | 0.   |

| 94 <sub>H</sub> | XCON     |       |     |      | I      | <br> |     | 1    |      |

| 98 <sub>H</sub> | SCON     | SM0   | SM1 | SM2  | REN    | TB8  | RB8 | TI   | RI   |

| 99 <sub>H</sub> | SBUF     |       |     | <br> | 1      |      |     | 1    | 1    |

| A0 <sub>H</sub> | P2       |       |     |      |        |      |     |      |      |

| A8 <sub>H</sub> | IE       | EA    | _   | ET2  | ES     | ET1  | EX1 | ETO  | EX0  |

| AAH             | SRELL    |       |     |      | <br>   |      |     | <br> |      |

bit and byte addressable

- = reserved

not bit addressable

# Table 3 Contents of SFRs, SFRs in Numeric Order (cont'd)

| Address         | Register | Bit 7 | 6        | 5    | 4    | 3     | 2    | 1     | 0      |

|-----------------|----------|-------|----------|------|------|-------|------|-------|--------|

| B0 <sub>H</sub> | P3       |       |          |      |      |       |      |       |        |

| B1 <sub>H</sub> | SYSCON   | _     | <u> </u> |      | _    | _     |      | XMAP1 | XMAP0  |

| B8 <sub>H</sub> | IP       | _     | PADC     | PT2  | PS   | PT1   | PX1  | PT0   | PX0    |

| BAH             | SRELH    |       |          |      | <br> |       |      |       |        |

| C0 <sub>H</sub> | WDCON    | _     | -        | -    | _    | OWDS  | WDTS | WDT   | SWDT   |

| C8 <sub>H</sub> | T2CON    | TF2   | EXF2     | RCLK | TCLK | EXEN2 | TR2  | C/T2  | CP/RL2 |

| C9 <sub>H</sub> | T2MOD    | -     | · _      |      | · _  | · _   | · _  | · _   | DCEN   |

| CAH             | RC2L     |       | 1        | 1    | 1    | 1     | 1    | 1     |        |

| СВ <sub>Н</sub> | RC2H     |       | 1        |      | 1    | 1     |      |       |        |

| сс <sub>Н</sub> | TL2      |       |          |      |      |       |      |       |        |

| CD <sub>H</sub> | TH2      |       |          |      |      |       |      |       |        |

| D0 <sub>H</sub> | PSW      | CY    | AC       | F0   | RS1  | RS0   | OV   | F1    | Р      |

| D8 <sub>H</sub> | BAUD     | BD    | -        | _    | _    | -     | _    | _     | -      |

| E0 <sub>H</sub> | ACC      |       |          |      |      |       |      |       |        |

| F0 <sub>H</sub> | В        |       |          |      |      |       |      |       |        |

bit and byte addressable

not bit addressable

- = reserved

### Timer/Counter 0 and 1

Timer/Counter 0 and 1 can be used in four operating modes as listed in table 4:

# Table 4

Timer/Counter 0 and 1 Operating Modes

| Mode | Description TMOI                                                                           |      |     |    |    | Inp                           | out Clock                         |  |

|------|--------------------------------------------------------------------------------------------|------|-----|----|----|-------------------------------|-----------------------------------|--|

|      |                                                                                            | Gate | C/T | M1 | MO | internal                      | external<br>(max)                 |  |

| 0    | 8-bit timer/counter with a divide-by-32 prescaler                                          | X    | Х   | 0  | 0  | $f_{\rm OSC}/_{12 \times 32}$ | $f_{\rm OSC}/_{\rm 24 \times 32}$ |  |

| 1    | 16-bit timer/counter                                                                       | X    | Х   | 0  | 1  | $f_{\rm OSC}/_{12}$           | $f_{\rm OSC}/_{\rm 24}$           |  |

| 2    | 8-bit timer/counter with<br>8-bit auto-reload                                              | Х    | Х   | 1  | 0  | $f_{\rm OSC}/_{12}$           | $f_{\rm OSC}/_{\rm 24}$           |  |

| 3    | Timer/counter 0 used as one<br>8-bit timer/counter and one<br>8-bit timer<br>Timer 1 stops | X    | Х   | 1  | 1  | fosc/12                       | fosc/24                           |  |

In "timer" function (C/ $\overline{T}$  = '0') the register is incremented every machine cycle. Therefore the count rate is  $f_{OSC}/12$ .

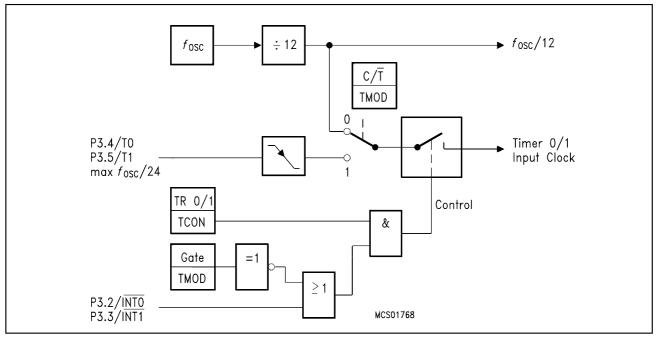

In "counter" function the register is incremented in response to a 1-to-0 transition at its corresponding external input pin (P3.4/T0, P3.5/T1). Since it takes two machine cycles to detect a falling edge the max. count rate is  $f_{OSC}/24$ . External inputs  $\overline{INT0}$  and  $\overline{INT1}$  (P3.2, P3.3) can be programmed to function as a gate to facilitate pulse width measurements. **Figure 2** illustrates the input clock logic.

Figure 2 Timer/Counter 0 and 1 Input Clock Logic

# Timer 2

Timer 2 is a 16-bit Timer/Counter with up/down count feature. It can operate either as timer or as an event counter which is selected by bit  $C/\overline{T2}$  (T2CON.1). It has three operating modes as shown in **table 5**.

# Table 5Timer/Counter 2 Operating Modes

|                        | T                    | 2CON       |     | T2MOD | T2CON |               |                                                 | Input                       | Clock                      |

|------------------------|----------------------|------------|-----|-------|-------|---------------|-------------------------------------------------|-----------------------------|----------------------------|

| Mode                   | R×CLK<br>or<br>T×CLK | CP/<br>RL2 | TR2 | DCEN  | EXEN  | P1.1/<br>T2EX | Remarks                                         | internal                    | external<br>(P1.0/T2)      |

| 16-bit<br>Auto-        | 0                    | 0          | 1   | 0     | 0     | Х             | reload upon<br>overflow                         |                             |                            |

| reload                 | 0                    | 0          | 1   | 0     | 1     | $\downarrow$  | reload trigger<br>(falling edge)                | <i>f</i> <sub>OSC</sub> /12 | max<br><sub>fosc</sub> /24 |

|                        | 0                    | 0          | 1   | 1     | Х     | 0             | Down counting                                   |                             | 0                          |

|                        | 0                    | 0          | 1   | 1     | Х     | 1             | Up counting                                     |                             |                            |

| 16-bit<br>Cap-<br>ture | 0                    | 1          | 1   | Х     | 0     | Х             | 16-bit Timer/<br>Counter (only<br>up-counting)  |                             | max                        |

|                        | 0                    | 1          | 1   | X     | 1     | Ļ             | capture TH2,<br>TL2 $\rightarrow$ RC2H,<br>RC2L | f <sub>osc</sub> /12        | $f_{\rm OSC}/24$           |

| Baud<br>Rate<br>Gene-  | 1                    | Х          | 1   | Х     | 0     | Х             | no overflow<br>interrupt<br>request (TF2)       | 6 10                        | max                        |

| rator                  | 1                    | Х          | 1   | X     | 1     | Ļ             | extra external<br>interrupt<br>("Timer 2")      | f <sub>osc</sub> /2         | f <sub>osc</sub> /24       |

| off                    | Х                    | Х          | 0   | Х     | Х     | Х             | Timer 2 stops                                   | _                           | _                          |

Note:  $\downarrow =$  falling edge

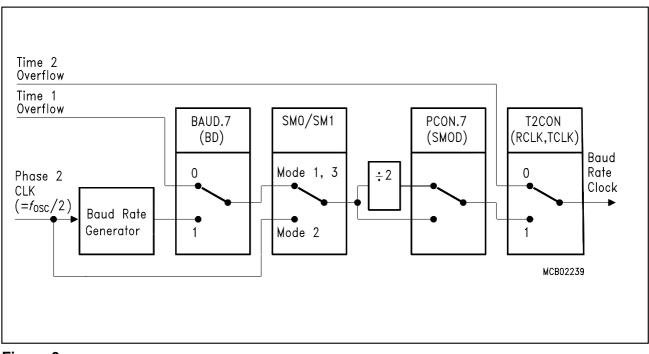

The serial port is full duplex and can operate in four modes (one synchronous mode, three asynchronous modes) as illustrated in **table 6**. **Figure 3** illustrates the block diagram of Baudrate generation for the serial interface.

### Table 6 USART Operating Modes

| Mede | SCON |     | Baudrate                                            | Description                                                                                                             |

|------|------|-----|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| Mode | SM0  | SM1 |                                                     |                                                                                                                         |

| 0    | 0    | 0   | f <sub>osc</sub> /12                                | Serial data enters and exits through R×D.<br>T×D outputs the shift clock. 8-bit are<br>transmitted/received (LSB first) |

| 1    | 0    | 1   | Timer 1/2 overflow rate<br>or<br>Baudrate Generator | 8-bit UART<br>10 bits are transmitted (through T×D) or<br>received (R×D)                                                |

| 2    | 1    | 0   | $f_{\rm OSC}/32$ or $f_{\rm OSC}/64$                | 9-bit UART<br>11 bits are transmitted (T×D) or<br>received (R×D)                                                        |

| 3    | 1    | 1   | Timer 1/2 overflow rate<br>or<br>Baudrate Generator | 9-bit UART<br>Like mode 2 except the variable<br>baud rate                                                              |

#### Figure 3 Block Diagram of Baud Rate Generation for Serial Interface

The possible baudrate can be calculated using the formulas given in **table 7**.

#### Table 7 Baudrates

| Baud Rate<br>derived from                                        | Interface Mode | Baudrate                                                                                                                                    |

|------------------------------------------------------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Oscillator                                                       | 0<br>2         | $f_{\rm OSC}$ /12<br>(2 <sup>SMOD</sup> × $f_{\rm OSC}$ )/64                                                                                |

| Timer 1 (16-bit timer)<br>(8-bit timer with<br>8-bit autoreload) | 1,3<br>1,3     | $(2^{\text{SMOD}} \times \text{timer 1 overflow rate})/32$ $(2^{\text{SMOD}} \times f_{\text{OSC}})/(32 \times 12 \times (256\text{-TH1}))$ |

| Timer 2                                                          | 1,3            | $f_{\rm OSC}/(32 \times (65536-(RC2H, RC2L)))$                                                                                              |

| Baudrate<br>Generator                                            | 1,3            | $(2^{\text{SMOD}} \times f_{\text{OSC}})/(64 \times (2^{10}-\text{SREL}))$                                                                  |

The internal baudrate generator consists of a free running 10-bit timer with  $f_{OSC}/2$  input frequency. The internal baudrate generator is selected by setting bit BD in SFR BAUD.

### Additional On-Chip RAM - XRAM

The SAB-C502 contains another 256byte of On-Chip RAM additional to the 256bytes internal RAM. This RAM is called XRAM ('eXtended RAM') in this document.

The additional ON-Chip RAM is logically located in the external data memory range. The highbyte of the XRAM address range startaddress is programmable by SFR XCON (94<sub>H</sub>). The reset value of XCON is 0F8<sub>H</sub> (that is, XRAM address range F800H<sub>H</sub> ... F8FF<sub>H</sub>).

The contents of the XRAM is not affected by a reset. After power up the contents is undefined, while it remains unchanged during and after reset as long as the power supply is not turned off. The XRAM is controlled by SFR SYSCON as shown in **table 8**.

| SFR S | YSCON | Description                                                                                                       |

|-------|-------|-------------------------------------------------------------------------------------------------------------------|

| XMAP1 | XMAP0 |                                                                                                                   |

| 0     | 1     | Resetvalue. Access to XRAM is disabled. When cleared it can be set again only by a reset                          |

| 0     | 0     | XRAM enabled                                                                                                      |

| 1     | 0     | XRAM enabled. The signals $\overline{\text{RD}}$ and $\overline{\text{WR}}$ are activated during accesses to XRAM |

#### Table 8 Control of the XRAM

Because of the XRAM is used in the same way as external data memory the same instruction types must be used for accessing the XRAM. A general overview gives **table 9**.

### Table 9 Accessing the XRAM

| Instruction<br>using | Instruction                   | Remarks                                                                                                                                                                                                                                                                                   |

|----------------------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DPTR                 | MOVX A @DPTR<br>MOVX @ DPTR,A | Normally the use of these instructions would use a physically external memory. However, in the SAB-C502 the XRAM is accessed if it is enabled.                                                                                                                                            |

| R0/R1<br>(page mode) | MOVX A, @Ri<br>MOVX@Ri,A      | Normally Port 2 serves as page register. However, the distinction, whether Port 2 is as general purpose I/O or as "page address" is made by the external design.<br>Hence a special SFR XPAGE is implemented the serve the same function for the XRAM as Port 2 for external data memory. |

**Note:** When writing the page address (in page mode) at Port2 the value is also written in XPAGE. However when writing XPAGE the value at PORT2 is not changed!

The behaviour of Port0/Port2 and RD/WR during MOVX accesses is shown in table 10.

|       |                                                             |                                                                                                                         | <b>EA</b> = 0                                                                                                         |                                                                                                               |                                                                                                               | <b>EA</b> = 1                                                                                                         |                                                                                                               |

|-------|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

|       |                                                             | XMAP1, XMAP0                                                                                                            |                                                                                                                       |                                                                                                               | XMAP1, XMAP0                                                                                                  |                                                                                                                       |                                                                                                               |

|       |                                                             | 00                                                                                                                      | 10                                                                                                                    | X1                                                                                                            | 00                                                                                                            | 10                                                                                                                    | X1                                                                                                            |

| MOVX  | DPTR outside<br>XRAM address<br>range<br>(DPH ≠ XCON)       | <ul> <li>a) P0/P2 → Bus</li> <li>b) RD/WR</li> <li>active</li> <li>c) ext. memory</li> <li>is used</li> </ul>           | <ul> <li>a) P0/P2 → Bus</li> <li>b) RD/WR</li> <li>active</li> <li>c) ext. memory</li> <li>is used</li> </ul>         | <ul> <li>a) P0/P2 → Bus</li> <li>b) RD/WR</li> <li>active</li> <li>c) ext. memory</li> <li>is used</li> </ul> | <ul> <li>a) P0/P2 → Bus</li> <li>b) RD/WR</li> <li>active</li> <li>c) ext. memory</li> <li>is used</li> </ul> | <ul> <li>a) P0/P2 → Bus</li> <li>b) RD/WR</li> <li>active</li> <li>c) ext. memory</li> <li>is used</li> </ul>         | <ul> <li>a) P0/P2 → Bus</li> <li>b) RD/WR</li> <li>active</li> <li>c) ext. memory</li> <li>is used</li> </ul> |

| @DPTR | DPTR within<br>XRAM address<br>range<br>(DPH = XCON)        | <ul> <li>a) P0/P2 → Bus</li> <li>(WR-Data only)</li> <li>b) RD/WR</li> <li>inactive</li> <li>c) XRAM is used</li> </ul> | <ul> <li>a) P0/P2 → Bus</li> <li>(WR-Data only)</li> <li>b) RD/WR</li> <li>active</li> <li>c) XRAM is used</li> </ul> | a) P0/P2 → Bus<br>b) RD/WR<br>active<br>c) ext. memory<br>is used                                             | <ul> <li>a) P0/P2 → I/O</li> <li>b) RD/WR</li> <li>inactive</li> <li>c) XRAM is used</li> </ul>               | <ul> <li>a) P0/P2 → Bus</li> <li>(WR-Data only)</li> <li>b) RD/WR</li> <li>active</li> <li>c) XRAM is used</li> </ul> | <ul> <li>a) P0/P2 → Bus</li> <li>b) RD/WR</li> <li>active</li> <li>c) ext. memory</li> <li>is used</li> </ul> |

| MOVX  | XPAGE outside<br>XRAM addr. page<br>range<br>(XPAGE ≠ XCON) | a) P0 → Bus<br>P2 → I/O<br>b) RD/WR<br>active<br>c) ext. memory<br>is used                                              | a) P0 → Bus<br>P2 → I/O<br>b) RD/WR<br>active<br>c) ext. memory<br>is used                                            | a) P0 → Bus<br>P2 → I/O<br>b) RD/WR<br>active<br>c) ext. memory<br>is used                                    | a) P0 → Bus<br>P2 → I/O<br>b) RD/WR<br>active<br>c) ext. memory<br>is used                                    | a) P0 → Bus<br>P2 → I/O<br>b) RD/WR<br>active<br>c) ext. memory<br>is used                                            | a) P0 → Bus<br>P2 → I/O<br>b) RD/WR<br>active<br>c) ext. memory<br>is used                                    |

| @Ri   | XPAGE within<br>XRAM addr. page<br>range<br>(XPAGE = XCON)  | a) P0 → Bus<br>(WR-Data only)<br>P2 → I/O<br>b) RD/WR<br>inactive<br>c) XRAM is used                                    | a) P0 → Bus<br>(WR-Data only)<br>P2 → I/O<br>b) RD/WR<br>active<br>c) XRAM is used                                    | a) P0 → Bus<br>P2 → I/O<br>b) RD/WR<br>active<br>c) ext. memory<br>is used                                    | <ul> <li>a) P0/P2 → I/O</li> <li>b) RD/WR</li> <li>inactive</li> <li>c) XRAM is used</li> </ul>               | a) P0 → Bus<br>(WR-Data only)<br>P2 → I/O<br>b) RD/WR<br>active<br>c) XRAM is used                                    | a) P0 → Bus<br>P2 → I/O<br>b) RD/WR<br>active<br>c) ext. memory<br>is used                                    |

modes compatible to the standard 8051-family

SIEMENS

## **Eight Datapointers for Faster External Bus Access**

The SAB-C502 contains a set of eight 16-bit-Datapointer (DPTR) from which the actual DPTR can be selected.

This means that the user's program may keep up to eight 16-bit addresses resident in these registers, but only one register at the time is selected to be the datapointer. Thus the DPTR in turn is accessed (or selected) via indirect addressing. This indirect addressing is done through a special function register (SFR) called DPSEL (data pointer select register, Bits 0 to 2). All instructions of the SAB-C502 which handle the DPTR therefore affect only one of the eight pointers which is addressed by DPSEL at that very moment.

A 3-bit field in SFR DPSEL points to the currently used DPTRx:

| DPSI | ΞL |    | selected<br>DPTR |

|------|----|----|------------------|

| .2   | .1 | .0 |                  |

| 0    | 0  | 0  | DPTR 0           |

| 0    | 0  | 1  | DPTR 1           |

| 0    | 1  | 0  | DPTR 2           |

| 0    | 1  | 1  | DPTR 3           |

| 1    | 0  | 0  | DPTR 4           |

| 1    | 0  | 1  | DPTR 5           |

| 1    | 1  | 0  | DPTR 6           |

| 1    | 1  | 1  | DPTR 7           |

|      |    |    | 1                |

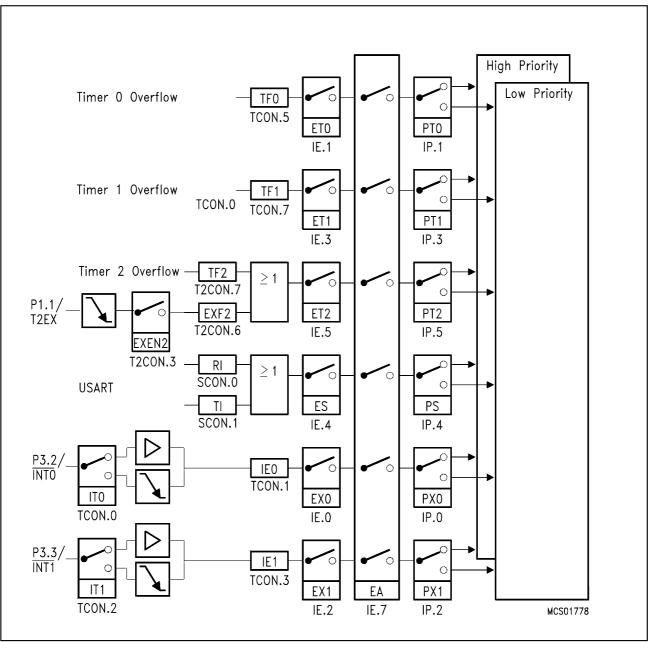

### Interrupt System

The SAB-C502 provides 6 interrupt sources with two priority levels. **Figure 4** gives a general overview of the interrupt sources and illustrates the request and control flags.

Figure 4 Interrupt Request Sources

| Source (Request Flags) | Vector                | Vector Address    |

|------------------------|-----------------------|-------------------|

| IE0                    | External interrupt 0  | 0003 <sub>H</sub> |

| TF0                    | Timer 0 interrupt     | 000BH             |

| IE1                    | External interrupt 1  | 0013 <sub>H</sub> |

| TF1                    | Timer 1 interrupt     | 001BH             |

| RI + TI                | Serial port interrupt | 0023 <sub>H</sub> |

| TF2 + EXF2             | Timer 2 interrupt     | 002BH             |

A low-priority interrupt can itself be interrupted by a high-priority interrupt, but not by another lowpriority interrupt. A high-priority interrupt cannot be interrupted by any other interrupt source.