#### Advance Information

This document contains information on a product under development. The parametric and functional information are target parameters and are subject to change without notice. Please consult Brooktree for the most recent data-sheet before design.

#### Distinguishing Features

- 275 MHz Operation

- Phase Lock Loop (PLL) Capability

- Pixel Clock 8x, 16x, 20x, 32x Crystal

- Differential ECL Clock Generation

- Divide by 4 of the Clock

- Resets Pipeline Delay of the RAMDAC

- 1.2 V Voltage Reference Output

- Single +5 V Power Supply

- 28-pin PLCC Package

- Typical Power Dissipation: 800 mW

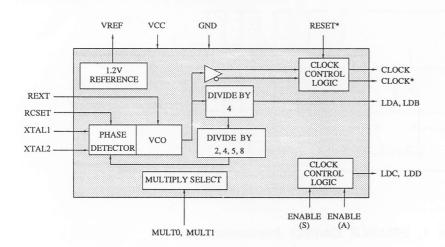

#### Functional Block Diagram

Brooktree Corporation • 9950 Barnes Canyon Rd. • San Diego, CA 92121 (619) 452-7580 • (800) VIDEO IC • TLX: 383 596 • FAX (619) 452-1249 L440001 Rev. A

#### **Customer Benefits**

- Reduces PC Board Area

- Simplifies RAMDAC Design

- Cost Reduction over Discretes

- Increases System Reliability

- · Easy to Implement

# **Bt440**

### 275 MHz PLL Clock Generator for CMOS RAMDACs<sup>™</sup>

#### **Product Description**

The Bt440 is a clock generator for the highspeed Brooktree CMOS RAMDACs. It interfaces to a low-frequency quartz crystal and multiplies the crystal frequency by 8x, 16x, 20x, and 32x to generate the pixel clock signals that drive the RAMDAC.

The Bt440 requires no coils or variable capacitors for operation. Frequency range is set through an external resistor. The Bt440 loop filter utilizes standard RC components.

The pixel clock output is divided by four to generate the load signal.

A second load signal may be synchronously or asynchronously controlled to enable starting and stopping the clocking of the video DRAMs.

The Bt440 can also configure the pipeline delay of the RAMDAC to a fixed pipeline delay.

An on-chip 1.2 V voltage reference is also provided, and may be used to provide the reference voltage for one to four RAMDACs.

The Bt440 is designed to interface to low-frequency crystal and generate the clock signals required by the RAMDACs. The XTAL1 and XTAL2 inputs interface to a quartz crystal, yielding a cost-effective clock generation system.

The CLOCK and CLOCK\* outputs interface directly to the CLOCK and CLOCK\* inputs of the RAM-DACs. The output levels are compatible with 10KH ECL logic operating from a single +5 V power supply.

MULT0 and MULT1 determine the multiplication factor for the pixel clock. The input oscillator frequency is multiplied by 8, 16, 20, or 32, depending on the MULT0 and MULT1 settings. See Table 1.

When using the MULT0 and MULT1 to change to a different multiplication factor, RESET is not required. A phase lock loop will lock into the new frequency after a minimum time.

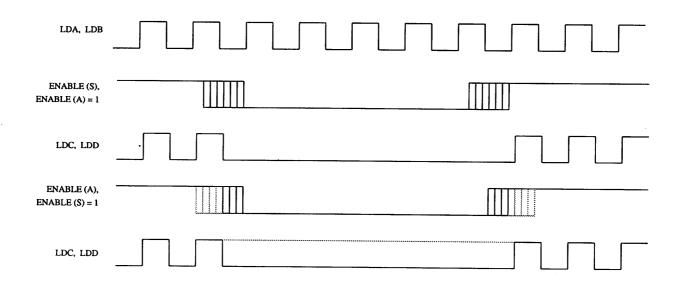

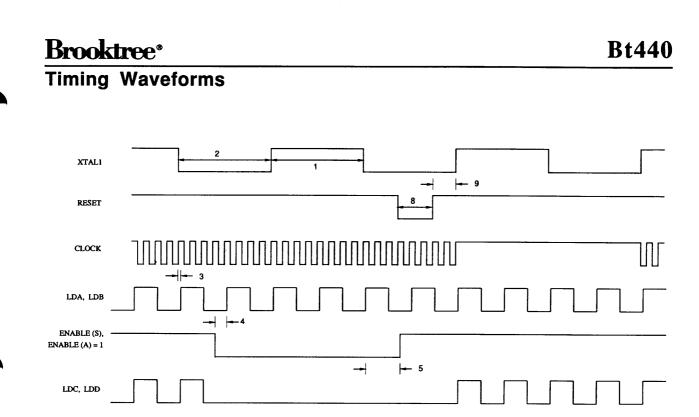

The LDA and LDB signals are generated by the pixel clock divided by 4. The LDA signal will interface directly to the LD\* signal of the RAMDAC. The LDB, LDC, and LDD interface to the VRAMs. For all frequencies, LDA, LDB, LDC, and LDD maintain the same CLOCK/4 relationship.

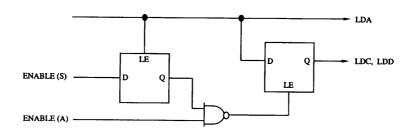

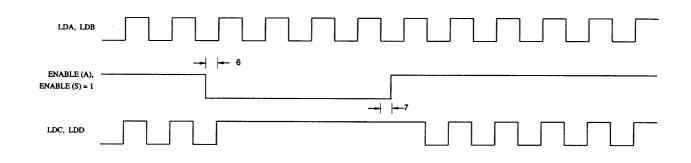

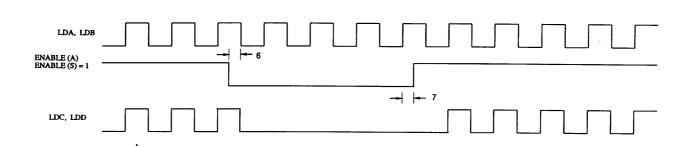

ENABLE (S) is internally synchronized to LDA and may be used to synchronously start and stop the LDC and LDD outputs. While ENABLE (S) is a logical zero, LDC and LDD will be a logical zero.

ENABLE (A) is used to asynchronously start and stop the LDC and LDD outputs. While ENABLE (A) is a logical zero, the LDC and LDD outputs will remain in the same state. While both ENABLE (S) and ENABLE (A) are a logical one, LDC and LDD will be free-running and in phase with LDA and LDB. This architecture allows the shift registers of the video DRAMs to be optionally non-clocked during the retrace intervals. Figure 1 illustrates the ENABLE implementation within the Bt440, while Figure 2 shows the load output timing.

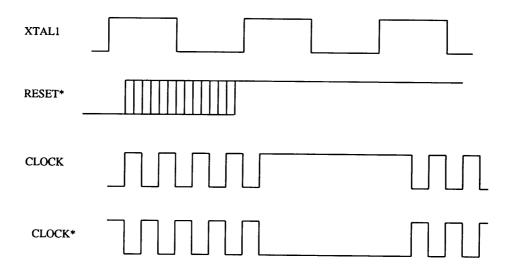

The RESET\* input is designed to enable the Bt440 to set the pipeline delay of the RAMDACs to a specified number of clock cycles (the exact number is dependent on the RAMDAC). Following the first rising edge of XTAL1 after the rising edge of RESET\*, the CLOCK and CLOCK\* outputs are stopped in the high and low states, respectively. At the next rising edge of XTAL1, the CLOCK and CLOCK\* outputs are restarted. Figure 3 shows the operation of the RESET\* input.

The Bt440 also generates a 1.2 V (typical) voltage reference, which may be used to drive the VREF input of one to four RAMDACs.

| MULT1 | MULTO | Pixel<br>Clock |

|-------|-------|----------------|

| 0     | 0     | x8             |

| 0     | 1     | x16            |

| 1     | 0     | x20            |

| 1     | 1     | x32            |

Table 1. Pixel Clock Multiplication Frequency.

Figure 1. ENABLE Control Implementation.

**Bt440**

### Circuit Description (continued)

# **Pin Descriptions**

| Pin Name         | Description                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VREF             | Voltage reference output. This output provides a 1.2 V (typical) reference, and may be used to drive the VREF input of one to four RAMDACs.                                                                                                                                                                                                                                                                                     |

| XTAL1            | Quartz crystal input. This input provides the base frequency for multiplication by the PLL circuitry.                                                                                                                                                                                                                                                                                                                           |

| XTAL2            | Quartz crystal output.                                                                                                                                                                                                                                                                                                                                                                                                          |

| CLOCK,<br>CLOCK* | Differential clock outputs. These outputs connect directly to the CLOCK and CLOCK* inputs of the RAMDAC. The clock rate is equal to the crystal oscillator input rate times the multiplication factor. The multiplication factor is determined by MULT0 and MULT1. CLOCK AND CLOCK* are capable of driving up to four RAMDACs directly. The output levels are equivalent to 10KH ECL logic operating from a single +5 V supply. |

| MULTO,<br>MULT1  | Multiply control inputs (TTL compatible). These inputs determine the multiplication factors for the pixel clock.                                                                                                                                                                                                                                                                                                                |

| LDA, LDB         | Load outputs (TTL compatible). LDA and LDB are generated by dividing CLOCK by 4. Each output may drive up to 20 pF without external buffering.                                                                                                                                                                                                                                                                                  |

| LDC, LDD         | Load outputs (TTL compatible). When both ENABLE inputs are a logical one, these outputs have the same timing as the LDA and LDB outputs. Each output may drive up to 20 pF without external buffering.                                                                                                                                                                                                                          |

| REXT             | External Resistor. Sets the frequency range of the voltage control oscillator (VCO).                                                                                                                                                                                                                                                                                                                                            |

| RCSET            | RC Network. Filters the control voltage to the VCO. Consists of two capacitors and one resistor.                                                                                                                                                                                                                                                                                                                                |

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                 |

# **Brooktree**<sup>®</sup>

# Pin Descriptions (continued)

| Description                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Synchronous load enable control input (TTL compatible). ENABLE (S) is internally synchron-<br>ized to LDA and is used to synchronously start and stop the LDC and LDD outputs. While ENA-<br>BLE (S) is a logical zero, LDC and LDD will be a logical zero. While both ENABLE (A) and<br>ENABLE (S) are a logical one, LDC and LDD are free-running and in phase with the LDA and<br>LDB outputs. |                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| ously start and and LDD outp                                                                                                                                                                                                                                                                                                                                                                      | t stop the LDC and<br>outs will remain in                                                                                                                                                                                                   | d LDD outputs. When the same state. When the same state is the same state is the same state.                                                                                                                                                                                                                                                                                                                                                                                   | Vhile ENABLE (A)<br>hile both ENABLE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | is a logical a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | zero, the LDC<br>BLE (S) are a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| edge of RESE<br>the next rising                                                                                                                                                                                                                                                                                                                                                                   | T*, CLOCK and C g edge of XTAL1,                                                                                                                                                                                                            | CLOCK* are stopp<br>the CLOCK and                                                                                                                                                                                                                                                                                                                                                                                                                                              | cLOCK* outputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | low states, re                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | spectively. At                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Analog Device                                                                                                                                                                                                                                                                                                                                                                                     | e power. All AVC                                                                                                                                                                                                                            | C pins must be con                                                                                                                                                                                                                                                                                                                                                                                                                                                             | nnected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Digital Device                                                                                                                                                                                                                                                                                                                                                                                    | power. All DVCC                                                                                                                                                                                                                             | C pins must be cor                                                                                                                                                                                                                                                                                                                                                                                                                                                             | nnected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Analog Device                                                                                                                                                                                                                                                                                                                                                                                     | e ground. All AGN                                                                                                                                                                                                                           | D pins must be co                                                                                                                                                                                                                                                                                                                                                                                                                                                              | onnected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Digital Device                                                                                                                                                                                                                                                                                                                                                                                    | ground. All DGN                                                                                                                                                                                                                             | D pins must be co                                                                                                                                                                                                                                                                                                                                                                                                                                                              | nnected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                   | ized to LDA a<br>BLE (S) is a l<br>ENABLE (S)<br>LDB outputs.<br>Asynchronous<br>ously start and<br>and LDD outp<br>logical one, Ll<br>Reset control<br>edge of RESE<br>the next rising<br>Care must be t<br>Analog Device<br>Analog Device | ized to LDA and is used to synch<br>BLE (S) is a logical zero, LDC<br>ENABLE (S) are a logical one,<br>LDB outputs.<br>Asynchronous load enable contro<br>ously start and stop the LDC an<br>and LDD outputs will remain in<br>logical one, LDC and LDD are for<br>Reset control input (TTL compared<br>edge of RESET*, CLOCK and C<br>the next rising edge of XTAL1,<br>Care must be taken to avoid glitch<br>Analog Device power. All AVCC<br>Digital Device ground. All AGN | Synchronous load enable control input (TTL com-<br>ized to LDA and is used to synchronously start and<br>BLE (S) is a logical zero, LDC and LDD will be<br>ENABLE (S) are a logical one, LDC and LDD ar<br>LDB outputs.<br>Asynchronous load enable control input (TTL con-<br>ously start and stop the LDC and LDD outputs. V<br>and LDD outputs will remain in the same state. We<br>logical one, LDC and LDD are free-running and in<br>Reset control input (TTL compatible). Following<br>edge of RESET*, CLOCK and CLOCK* are stopp<br>the next rising edge of XTAL1, the CLOCK and<br>Care must be taken to avoid glitches on this edge-t<br>Analog Device power. All AVCC pins must be con-<br>Digital Device ground. All AGND pins must be con- | Synchronous load enable control input (TTL compatible). ENABLE<br>ized to LDA and is used to synchronously start and stop the LDC and<br>BLE (S) is a logical zero, LDC and LDD will be a logical zero. Wh<br>ENABLE (S) are a logical one, LDC and LDD are free-running and i<br>LDB outputs.<br>Asynchronous load enable control input (TTL compatible). ENABLE<br>ously start and stop the LDC and LDD outputs. While ENABLE (A)<br>and LDD outputs will remain in the same state. While both ENABLE (A)<br>and LDD outputs will remain in the same state. While both ENABLE (A)<br>Reset control input (TTL compatible). Following the first rising edge<br>edge of RESET*, CLOCK and CLOCK* are stopped in the high and I | Synchronous load enable control input (TTL compatible). ENABLE (S) is internatized to LDA and is used to synchronously start and stop the LDC and LDD outputs BLE (S) is a logical zero, LDC and LDD will be a logical zero. While both ENAENABLE (S) are a logical one, LDC and LDD are free-running and in phase with LDB outputs.<br>Asynchronous load enable control input (TTL compatible). ENABLE (A) is used ously start and stop the LDC and LDD outputs. While ENABLE (A) is a logical z and LDD outputs will remain in the same state. While both ENABLE (A) and ENA logical one, LDC and LDD are free-running and in phase with the LDA and LDB outputs will remain in the same state. While both ENABLE (A) and ENA logical one, LDC and LDD are free-running and in phase with the LDA and LDB or Reset control input (TTL compatible). Following the first rising edge of XTAL1 a edge of RESET*, CLOCK and CLOCK* are stopped in the high and low states, re the next rising edge of XTAL1, the CLOCK and CLOCK* outputs are set to be Care must be taken to avoid glitches on this edge-triggered input.<br>Analog Device power. All AVCC pins must be connected.<br>Digital Device power. All AGND pins must be connected. |

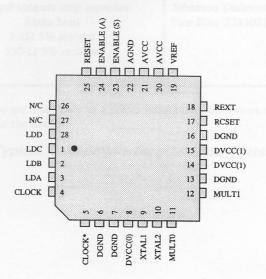

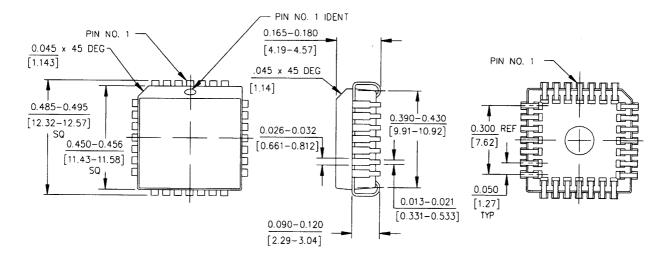

28-pin Plastic J-Lead (PLCC) Package with Internal Heatspreader

### PC Board Layout Considerations

#### **Power Planes**

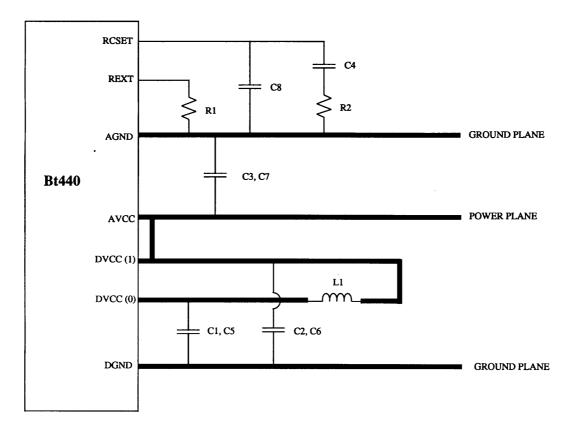

A single heavy ground plane should be used.

All of the VCC pins should be decoupled on the top PCB layer next to the device. A parallel 0.1 and 0.01 uF chip capacitor is recommended. See Figure 4.

Due to the large transient response of the TTL outputs, the DVCC(0), should be isolated through a ferrite bead to the PCB power plane.

#### External Loop Components

All of the external loop components (REXT and RCSET) should be placed on the top PCB layer in close proximity of the device. See Table 2 for REXT versus Pixel Clock rates.

High stability and ultra low-leakage components should be used (chip capacitors and chip resistors are recommended).

#### **Pixel Clock Outputs**

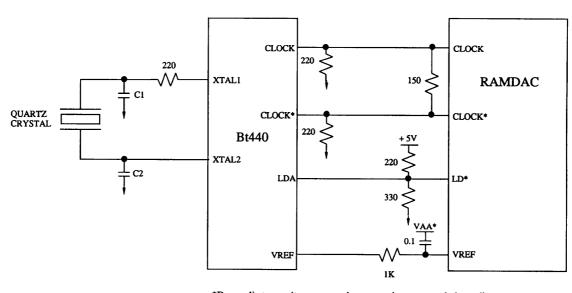

The CLOCK and CLOCK\* outputs should be terminated on the top PCB layer at the Bt440 with 220  $\Omega$ chip resistors and then cross-terminated with 150  $\Omega$  as close as possible to the RAMDAC. See Figure 5.

The clock traces should be of equal length and continuous on one trace layer. Through-holes, 90 degree angles, and stubs should be avoided to reduce any signal reflections.

#### General

Unused TTL outputs should be left floating.

The Bt440 should not be located on the board where large transient currents, or large electric or magnetic fields are expected.

The Bt440 should not be socketed.

Wire-wrapped boards will not work.

If the LDC and LDD TTL outputs are not used, they should be disabled by tying E(s) to GND. This will reduce the CLOCK jitter and increase the stability of the Bt440.

| REXT | Minimum   | Maximum   | Minimum     | Maximum     |

|------|-----------|-----------|-------------|-------------|

|      | Crystal   | Crystal   | Pixel Clock | Pixel Clock |

|      | Frequency | Frequency | Rate        | Rate        |

| 2 kΩ | 5 MHz     | 15 MHz    | 80 MHz      | 275 MHz     |

Table 2. REXT versus Pixel Clock Rates.

### PC Board Layout Considerations (continued)

Note: Connect the decoupling capacitors as close as possible to the power pins.

| Location                         | Description                                                                                                              | Vendor Part Number                                                                                     |

|----------------------------------|--------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| C1-C4<br>C5-C8<br>L1<br>R1<br>R2 | 0.1 uF ceramic chip capacitor<br>0.01 μF ceramic chip capacitor<br>ferrite bead<br>2-kΩ 5% resistor<br>330-Ω 5% resistor | Johanson Dielectrics X7R-500S41W104KP<br>Johanson Dielectrics X7R-500S41W103KP<br>Fair-Rite 2743001111 |

*Note*: The vendor numbers above are listed only as a guide. Substitution of devices with similar characteristics will not affect the performance of the Bt440.

;

### Bt440 Application Information

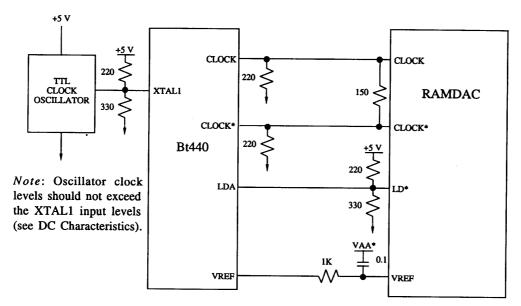

#### Interfacing to the RAMDAC

Figure 5 illustrates the interfacing of the Bt440 to the RAMDAC when using a quartz crystal oscillator. Figure 6 illustrates the interfacing of the Bt440 to a TTL clock oscillator. The Bt440 should be located as close as possible to the RAMDAC.

Termination resistors are required on the CLOCK and CLOCK\* lines, located as close as possible to the Bt440.

The Bt440 may drive the CLOCK and CLOCK\* inputs of one to four RAMDACs if they are located as close as possible to each other. Due to the inability to ensure proper synchronization between Bt440s, multiple devices should not be used in applications where multiple RAMDACs drive the same monitor.

A  $1k-\Omega$  (typical) resistor must be used to isolate the VREF output of the Bt440 from the VREF input of the RAMDAC. This isolates Bt440 voltage reference noise from being coupled onto the RAMDAC VREF pin. The VREF input of the RAMDAC must still have a decoupling capacitor, as specified in its datasheet.

\*Decoupling capacitor may require connection to ground, depending on VAA noise level.

C1 min = 20 pf C2 min = 100 pf

C2 > C1 by 30 pf

High stability and ultra low-leakage components should be used (chip capacitors and chip resistors are recommended).

Figure 5. Interfacing to a Quartz Crystal.

\*Decoupling capacitor may require connection to ground, depending on VAA noise level.

Figure 6. Interfacing to a TTL Clock Oscillator.

### **Recommended Operating Conditions**

| Parameter                     | Symbol | Min  | Тур  | Max  | Units |

|-------------------------------|--------|------|------|------|-------|

| Power Supply                  | VCC    | 4.75 | 5.00 | 5.25 | v     |

| Ambient Operating Temperature | TA     | 0    |      | + 70 | °C    |

|                               |        |      |      |      |       |

| •                             |        |      |      |      |       |

|                               |        |      |      |      |       |

### **Absolute Maximum Ratings**

| Parameter                                                                                                                           | Symbol                 | Min        | Тур | Max                            | Units          |

|-------------------------------------------------------------------------------------------------------------------------------------|------------------------|------------|-----|--------------------------------|----------------|

| VCC (measured to GND)                                                                                                               |                        |            |     | 7.0                            | v              |

| Voltage on any Pin                                                                                                                  |                        | GND-0.5    |     | VCC + 0.5                      | v              |

| CLOCK, CLOCK* Output Current                                                                                                        |                        |            |     | 30                             | mA             |

| Ambient Operating Temperature<br>Storage Temperature<br>Junction Temperature<br>Soldering Temperature<br>(5 seconds, 1/4" from pin) | TA<br>TS<br>TJ<br>TSOL | -55<br>-65 |     | + 125<br>+ 150<br>+ 175<br>260 | °C<br>°C<br>°C |

*Note:* Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those listed in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# **DC** Characteristics

| Parameter                                                                                                                                                                     | Symbol                          | Min            | Тур          | Max                            | Units                    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|----------------|--------------|--------------------------------|--------------------------|

| TTL Inputs<br>Input High Voltage<br>Input Low Voltage<br>Input High Current (Vin = 2.4 V)<br>Input Low Current (Vin = 0.4 V)<br>Input Capacitance<br>(f = 1 MHz, Vin = 2.4 V) | VIH<br>VIL<br>IIH<br>IIL<br>CIN | 2.0<br>GND-0.5 | 4            | VCC + 0.5<br>0.8<br>10<br>-0.7 | V<br>V<br>μA<br>mA<br>pF |

| XTAL1 (at 25 °C)<br>Input Voltage                                                                                                                                             | VIH<br>VIL                      | 2<br>GND-0.5   |              | 4<br>0.8                       | v<br>v                   |

| Load Outputs<br>Output High Voltage<br>(IOH = -2 mA)<br>Output Low Voltage<br>(IOL = 24 mA)                                                                                   | VOH<br>VOL                      | 2.4            |              | 0.5                            | v<br>v                   |

| Output Capacitance                                                                                                                                                            |                                 |                | 10           |                                | pF                       |

| Clock Outputs (at 25° C)<br>Differential Output Voltage                                                                                                                       | Δνουτ                           | .6             |              |                                | v                        |

| Output Capacitance                                                                                                                                                            | COUT                            |                | 7            |                                | pF                       |

| Voltage Reference<br>Output Voltage<br>Output Current                                                                                                                         | VREF<br>IREF                    | 1.2            | 1.235<br>100 | 1.26                           | V<br>μA                  |

| VCC Supply Current                                                                                                                                                            | ICC                             |                | 150          | 185                            | mA                       |

Test conditions (unless otherwise specified): "Recommended Operating Conditions." CLOCK and CLOCK\* have 50  $\Omega$  to VCC - 2 V.

<u>Bt440</u>

### Bt440 AC Characteristics

| Parameter                       | Symbol  | Min | Тур | Max | Units |

|---------------------------------|---------|-----|-----|-----|-------|

| Pixel Clock Rate                | Fmax    | 80  |     | 275 | MHz   |

| Crystal Frequency               | XTALmax | 5   |     | 15  | MHz   |

| LDA, LDB, LDC, LDD (Note 1)     | LDmax   |     |     | 70  | MHz   |

| XTAL1 High Time (Note 2)        | 1       | 40  |     |     | %     |

| XTAL1 Low Time (Note 2)         | 2       | 40  |     |     | %     |

| CLOCK to LDA Skew (Note 3)      | 3       |     | 4   |     | ns    |

| LDA, LDB Pulse Width Low        |         | tbd |     |     | ns    |

| LDA to LDB Output Skew (Note 3) |         |     | tbd |     | ns    |

| LDA to LDC Output Skew (Note 3) |         |     | tbd |     | ns    |

| LDC to LDD Output Skew (Note 3) |         |     | tbd |     | ns    |

| PLL Acquire time                |         | tbd | tbd | tbd | ms    |

| E(S) Setup                      | 4       | tbd |     |     | ns    |

| E(S) Hold                       | 5       | tbd |     |     | ns    |

| E(A) Setup                      | 6       | tbd |     |     | ns    |

| E(A) Hold                       | 7       | tbd |     |     | ns    |

| RESET* Active Low Time          | 8       | tbd |     |     | ns    |

| RESET* Setup Time               | 9       | tbd |     |     | ns    |

| Pixel Clock Jitter (Note 4)     |         |     |     | 1   | ns    |

Test conditions (unless otherwise specified): "Recommended Operating Conditions." TTL input values are 0-3 V, with input rise/fall times  $\leq 3$  ns, measured between 10 percent and 90 percent points. ECL input values are 3.2-4.2 V, with input rise/fall times  $\leq 1$  ns, measured between 20 percent and 80 percent points. Timing reference points at 50 percent for inputs and outputs.

Note 1: For load frequencies greater than 35 MHz, a termination scheme of 220  $\Omega$  pull-up to VCC and 330  $\Omega$  pull-down to ground is required.

- Note 2: Applies to the use of TTL clock oscillators

- Note 3: LD outputs equally loaded with 20 pF. Unequal loading may result in additional output skew.

Note 4: Jitter is measured as the worst case spread from shortest to longest cycle time after sampling at 30 MHz for 10,000 pixel clocks.

Figure 7. Synchronous Enable Operation.

Figure 8. Asynchronous Enable Operation (16x Mode). Enable (A) Operation Pulled High Coincident When LDA and LDB are Low. Timing Waveforms (continued)

Figure 9. Asynchronous Enable Operation (16x Mode). Enable (A) Operation Pulled High Coincident When LDA and LDB are High.

# Package Drawing—28-pin Plastic J-Lead (PLCC) with Internal Heat Spreader

NOTES-Unless otherwise specified:

- 1. Dimensions are in inches [millimeters].

- 2. Tolerances are:  $.xxx \pm 0.005$  [0.127].

- 3. PLCC packages are intended for surface mounting on solder lands on 0.050 [1.27] centers.

# Brooktree® Ordering Information

| Model Number | Package                                       | Ambient<br>Temperature<br>Range |

|--------------|-----------------------------------------------|---------------------------------|

| Bt440KHJ     | 28-pin PLCC with<br>internal heat<br>spreader | 0° to +70° C                    |

### **Revision History**

### Revision Change from Previous Revision

A Advance Release.

Information furnished by Brooktree Corporation is believed to be accurate and reliable. However, no responsibility is assumed for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Brooktree Corporation.

Brooktree Corporation 9950 Barnes Canyon Rd. San Diego, CA 92121-2790 (619) 452-7580 (800) VIDEO IC TLX: 383 596 FAX: (619) 452-1249 L440001 Rev. A

Copyright © 1992, Brooktree Corporation. Specifications are subject to change without notice. Print date 2/18/92

ESD-sensitive device. Permanent damage may occur on unconnected devices subjected to highenergy electrostatic fields. Unused devices must be stored in conductive foam or shunts.

Do not insert this device into powered sockets.

Remove power before insertion or removal.