### 60 GHz radar sensor with antennas in package

### **Features**

- Integrated state machine for low-power and real time operation

- Broadcast mode to trigger and configure multiple devices

- Single 50 MHz SPI for chip configuration and data transfer

- 60 GHz radar with 5.6 GHz bandwidth and a chirp slope of up to 400 MHz/µs

- 4 MSps ADC

- Antenna in package (AIP) with ±60° FoV

## **Potential applications**

- Presence detection and range zones segmentation for smart home and doorbell applications

- · Vital sign tracking for health care devices, such as sleep trackers and baby monitors

- 1D gesture sensing for smart appliances such as kitchen machines or thermostats

- · Distance measurement and level sensing

### **Product validation**

Qualified for applications listed above based on the test conditions in the relevant tests of JEDEC20/22.

### **Description**

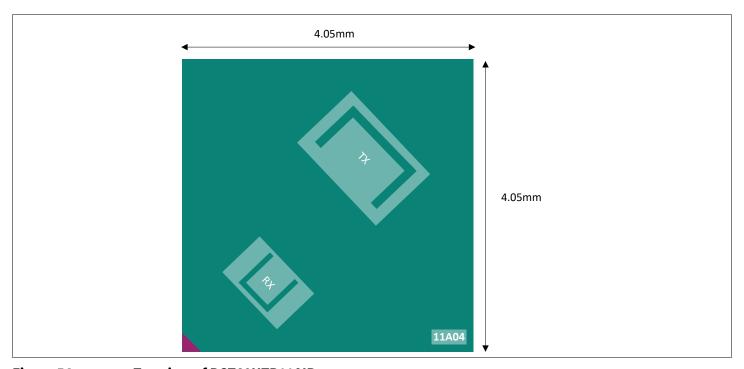

The BGT60UTR11AIP is a 60 GHz radar sensor with 1 transmitting and 1 receiving U-slotted patch antennas in package. The 5.6 GHz ultra-wide bandwidth allows FMCW operations with extremely high resolution. This enables precise range measurements, 1D gestures and also the measurement of vital signs such as breathing rate or heart rate.

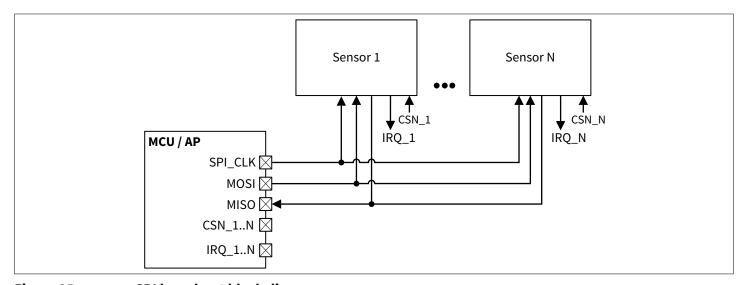

Sensor configuration and data transfer are enabled with a single digital interface. Multiple devices connected to the same bus can be configured and triggered together by using the implemented broadcast mode. Device specific programmable wake-up times allow time domain multiplexed radar frames.

The integrated state machine enables independent and real time data acquisition without interaction to the processor. Three possible power mode options give the user full flexibility between performance and power consumption optimizations.

| Product Name   | Package        | Marking type |  |  |

|----------------|----------------|--------------|--|--|

| BGT 60UTR11AIP | PG-VF2BGA-28-1 | 611A         |  |  |

## **Datasheet**

# **Table of contents**

|         | Features                                                     |

|---------|--------------------------------------------------------------|

|         | Potential applications                                       |

|         | Product validation                                           |

|         | Description                                                  |

|         | Table of contents                                            |

| 1       | Introduction                                                 |

| 1.1     | Product overview                                             |

| 1.2     | BGT60UTR11AIP block diagram                                  |

| 1.3     | BGT60UTR11AIP pin definition and function                    |

| 1.3.1   | IO and supply pins                                           |

| 1.4     | BGT60UTR11AIP functional block diagram11                     |

| 2       | General product specification                                |

| 2.1     | Absolute maximum ratings                                     |

| 2.2     | Range of functionality                                       |

| 2.3     | Current consumption                                          |

| 2.4     | ESD integrity                                                |

| 2.5     | Thermal resistance                                           |

| 3       | Shapes, frames and channel set definition                    |

| 3.1     | Shapes and frames                                            |

| 3.2     | Channel set18                                                |

| 3.3     | Power modes                                                  |

| 3.3.1   | Mode descriptions                                            |

| 3.3.2   | Wake-up phase from "deep sleep" to "idle"                    |

| 3.3.3   | Idle to interchirp then active                               |

| 3.3.4   | Saw-tooth shape timing                                       |

| 3.3.5   | Different power modes after shapes and shape groups          |

| 3.3.5.1 | Idle after shape or shape groups                             |

| 3.3.5.2 | Interchirp in-between shapes                                 |

| 3.3.5.3 | Deep sleep continuous + idle wake-up after shape groups      |

| 3.4     | System constraints                                           |

| 3.4.1   | MADC sampling timing conditions and calculations             |

| 3.4.2   | PLL frequency ramp setup                                     |

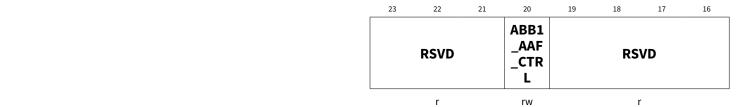

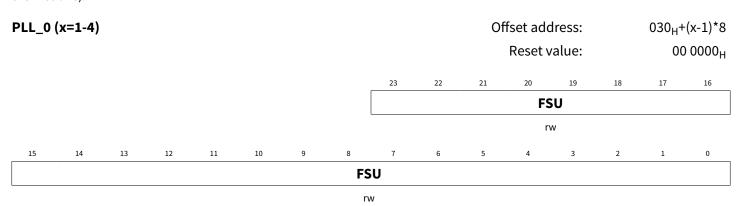

| 4       | BGT60UTR11AIP registers                                      |

| 4.1     | Abbreviations                                                |

| 4.2     | Register overview - BGT60UTR11AIP (ascending offset address) |

| 4.3     | Main register                                                |

| 4.4     | ADC control register                                         |

## **Datasheet**

# Table of contents

| 4.5  | Digital and RF version register         | 42 |

|------|-----------------------------------------|----|

| 4.6  | Status register 1                       | 43 |

| 4.7  | PLL analog control register 1           | 43 |

| 4.8  | PLL analog control register 2           | 45 |

| 4.9  | SPI and FIFO control register           | 47 |

| 4.10 | Channel set idle register 0             | 48 |

| 4.11 | Channel set idle register 1             | 49 |

| 4.12 | Channel set idle register 2             | 50 |

| 4.13 | Channel set control idle register       | 51 |

| 4.14 | Channel set deep sleep register 0       | 52 |

| 4.15 | Channel set deep sleep register 1       | 54 |

| 4.16 | Channel set deep sleep register 2       | 55 |

| 4.17 | Channel set control deep sleep register | 56 |

| 4.18 | Channel set up x register 0             | 57 |

| 4.19 | Channel set up x register 1             | 58 |

| 4.20 | Channel set up x register 2             | 59 |

| 4.21 | Channel set down x register 0           | 60 |

| 4.22 | Channel set down x register 1           | 61 |

| 4.23 | Channel set down x register 2           |    |

| 4.24 | Channel set control x register          |    |

| 4.25 | Chirp control register 0                |    |

| 4.26 | Chirp control register 1                | 65 |

| 4.27 | Chirp control register 2                | 66 |

| 4.28 | Chirp control register 3                |    |

| 4.29 | PLL shape x register 0                  | 68 |

| 4.30 | PLL shape x register 1                  | 68 |

| 4.31 | PLL shape x register 2                  | 69 |

| 4.32 | PLL shape x register 3                  |    |

| 4.33 | PLL shape x register 4                  |    |

| 4.34 | PLL shape x register 5                  |    |

| 4.35 | PLL shape x register 6                  |    |

| 4.36 | PLL shape x register 7                  |    |

| 4.37 | Sensor ADC register                     |    |

| 4.38 | RF test register 0                      |    |

| 4.39 | EFUSE register 0                        |    |

| 4.40 | EFUSE register 1                        |    |

| 4.41 | PLL test register 0                     |    |

| 4.42 | Chip ID register 0                      |    |

| 4.43 | Chip ID register 1                      |    |

| 4.44 | Clock input register                    |    |

| 4.45 | Wake up register                        |    |

| 4.46 | Status register 0                       |    |

| 5    |                                         |    |

3

## **Datasheet**

Table of contents

| 4.47  | Sensor ADC result register                   | . 80  |

|-------|----------------------------------------------|-------|

| 4.48  | FIFO status register                         | . 81  |

| 4.49  | Global status register                       | 82    |

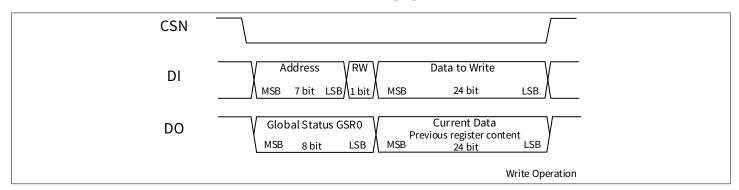

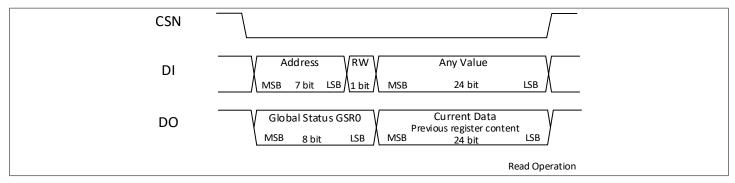

| 5     | Data organization and SPI interface          | 84    |

| 5.1   | Data header                                  | 84    |

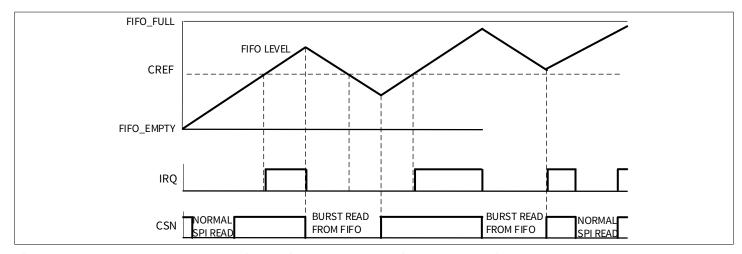

| 5.2   | FIFO and data flow                           | 84    |

| 5.3   | SPI – Serial Peripheral Interface module     | 85    |

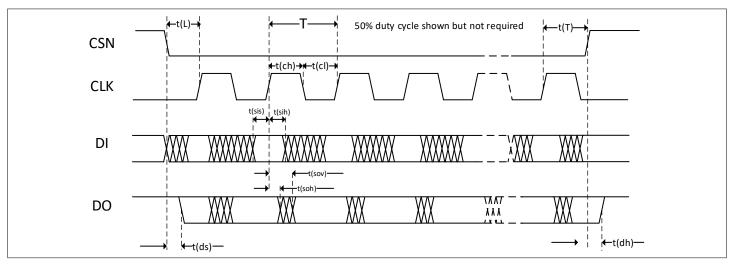

| 5.3.1 | Standard SPI timing                          | 86    |

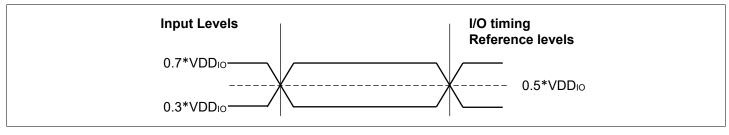

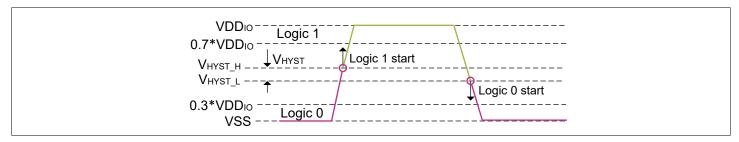

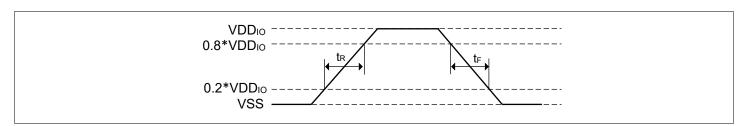

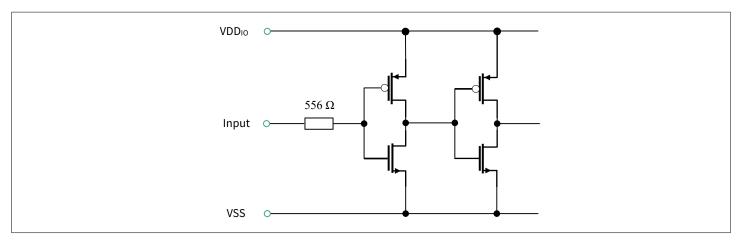

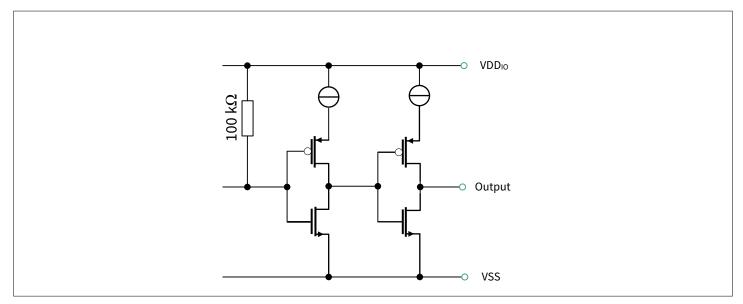

| 5.3.2 | Logic levels                                 | 88    |

| 5.3.3 | Overshoot and undershoot waveform definition | . 90  |

| 5.3.4 | IBIS model                                   | 91    |

| 5.3.5 | SPI functionality                            | 91    |

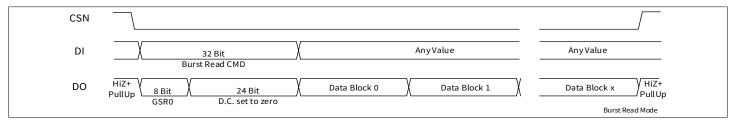

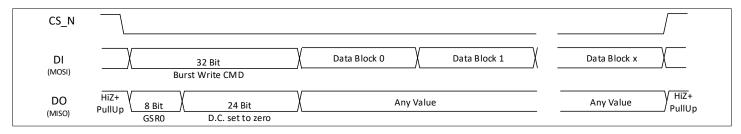

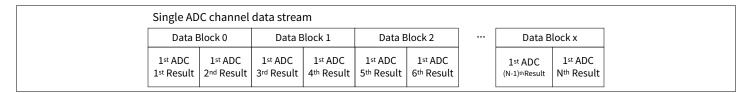

| 5.3.6 | SPI burst mode                               | . 92  |

| 5.3.7 | SPI error detection                          | 94    |

| 5.3.8 | SPI broadcast mode                           | 94    |

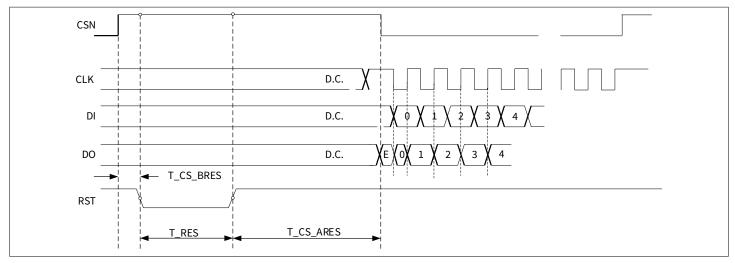

| 5.4   | Hardware reset sequence                      | 95    |

| 5.5   | Software triggered resets                    | 96    |

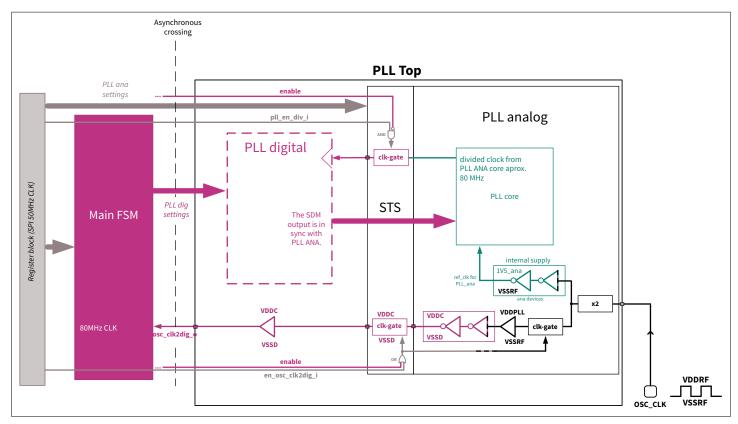

| 6     | PLL domain functional specification          | 97    |

| 6.1   | PLL interfaces and clock distribution        | . 97  |

| 6.1.1 | Reference clock distribution                 | 97    |

| 6.1.2 | Interfaces to the PLL                        | 98    |

| 6.2   | PLL parameters and specification             | . 98  |

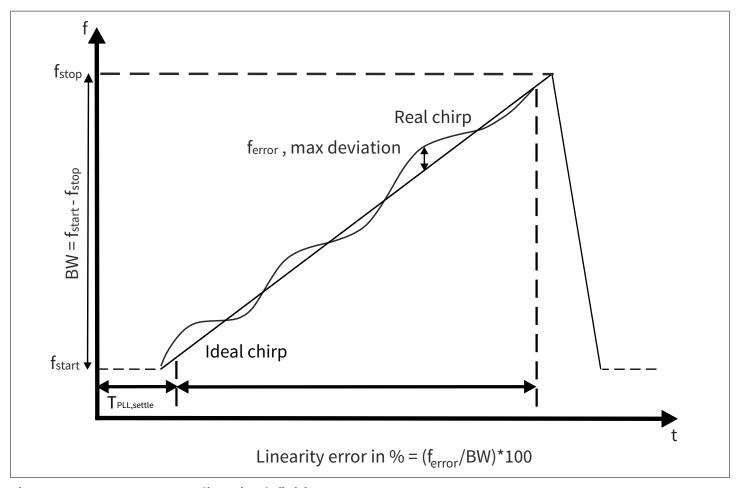

| 6.2.1 | Frequency ramp linearity definition:         | . 99  |

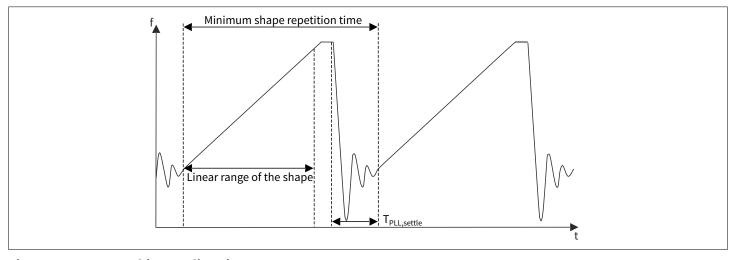

| 6.2.2 | Frequency ramp settling time                 | . 100 |

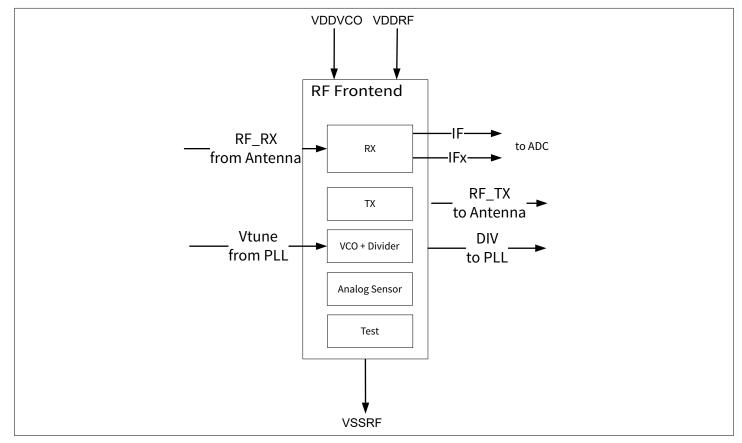

| 7     | Analog-RF domain functional specification    | 101   |

| 7.1   | RF frontend (RF FE)                          | 101   |

| 7.1.1 | On-chip analog sensor output                 | .101  |

| 7.1.2 | RF FE specifications                         | . 102 |

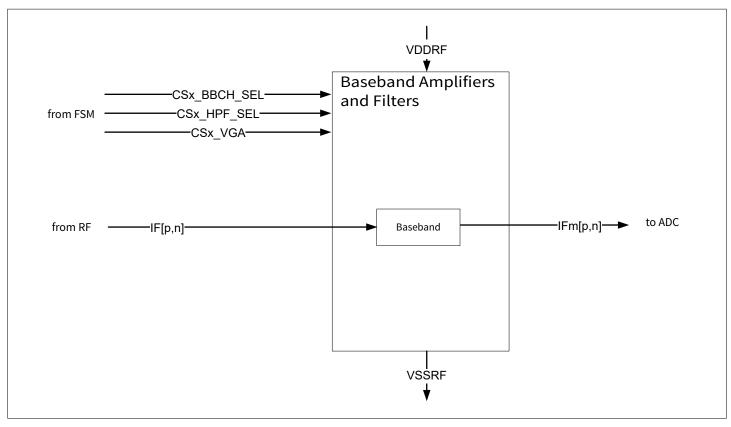

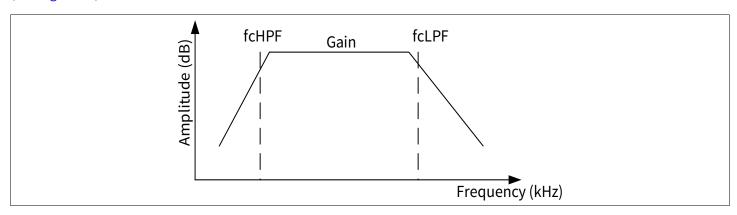

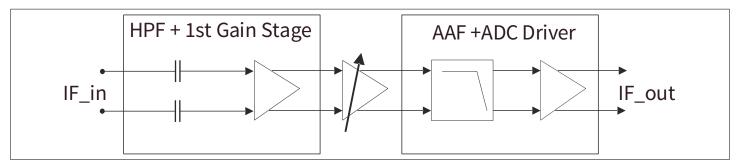

| 7.2   | Analog baseband: amplifiers and filters      | . 103 |

| 7.2.1 | Baseband characteristics                     | . 104 |

| 7.2.2 | Baseband requirements                        | . 104 |

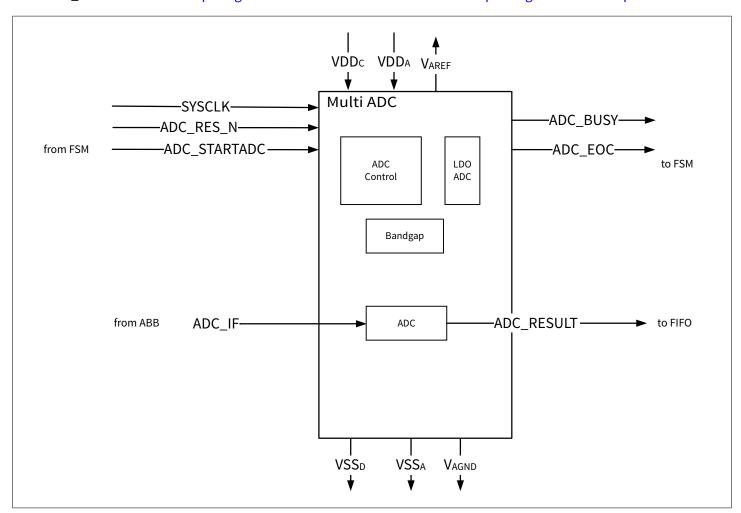

| 8     | MADC domain functional specification         | . 107 |

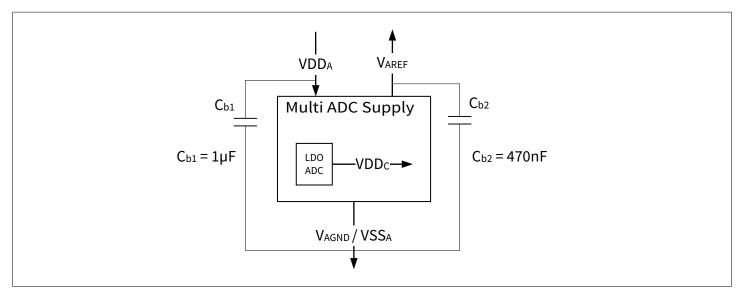

| 8.1   | MADC supply voltage requirements             | .107  |

| 8.2   | MADC specifications                          | 108   |

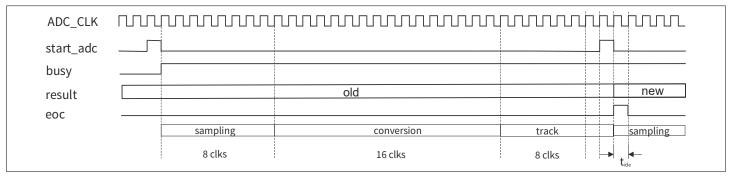

| 8.3   | MADC timing diagrams                         | . 110 |

| 8.4   | MADC start-up sequence                       | .110  |

| 8.5   | MADC conversion rate                         | . 111 |

| 8.5.1 | Sampling                                     | .111  |

| 8.5.2 | Conversion                                   | . 111 |

| 8.5.3 | Tracking                                     | 112   |

| 8.5.4 | ADC conversion rate                          | 112   |

4

# **Datasheet**

## Table of contents

| 8.5.5  | ADC sampling rate               | 112 |

|--------|---------------------------------|-----|

| 9      | On chip analog sensor           | 113 |

| 9.1    | Power sensor                    | 113 |

| 9.2    | Temperature sensor              |     |

| 9.3    | Manual sensor conversion        | 113 |

| 10     | Enhanced functions              | 115 |

| 10.1   | CHIP ID readout                 |     |

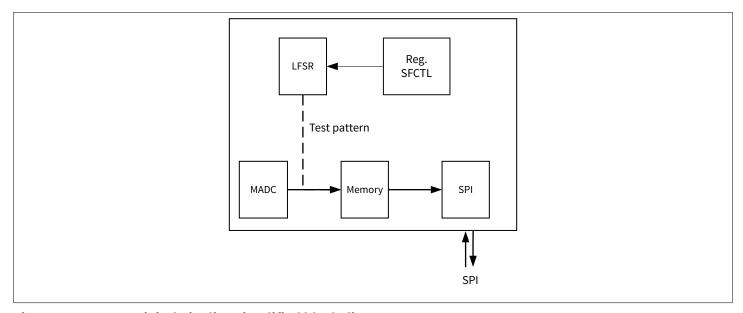

| 10.2   | Data test mode                  | 115 |

| 10.3   | CW mode                         | 115 |

| 10.3.1 | Enabling the CW mode            | 116 |

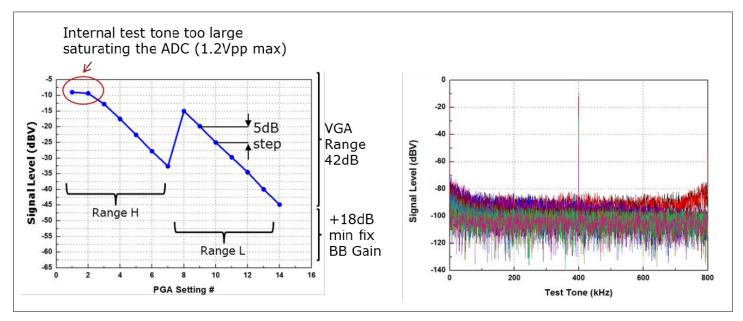

| 10.3.2 | Baseband and ADC test mode      | 117 |

| 10.4   | IRQ output                      | 118 |

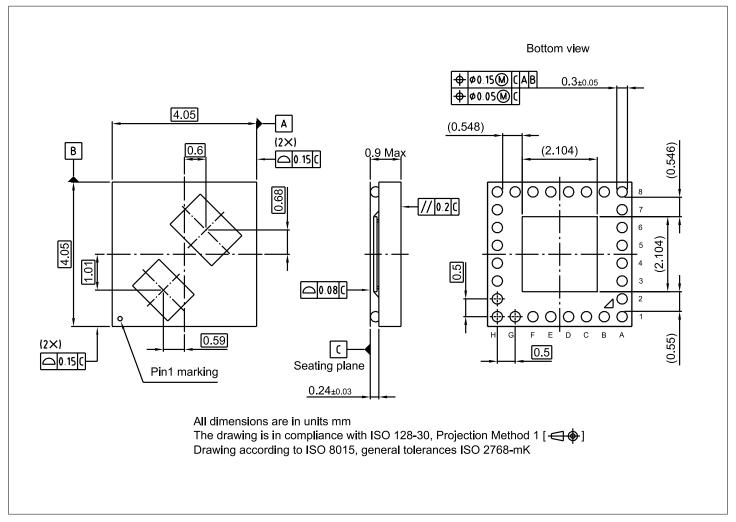

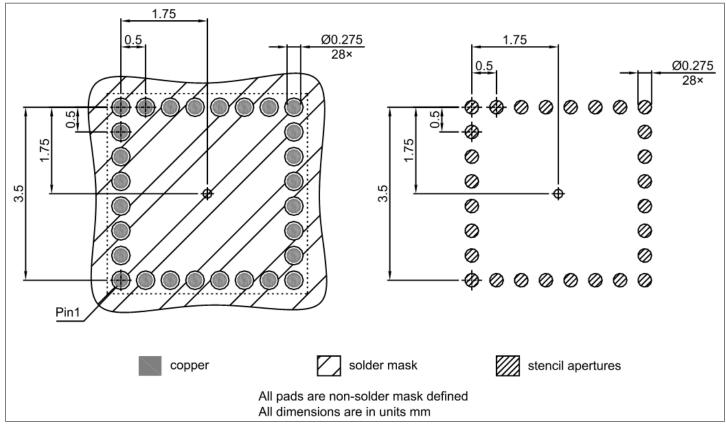

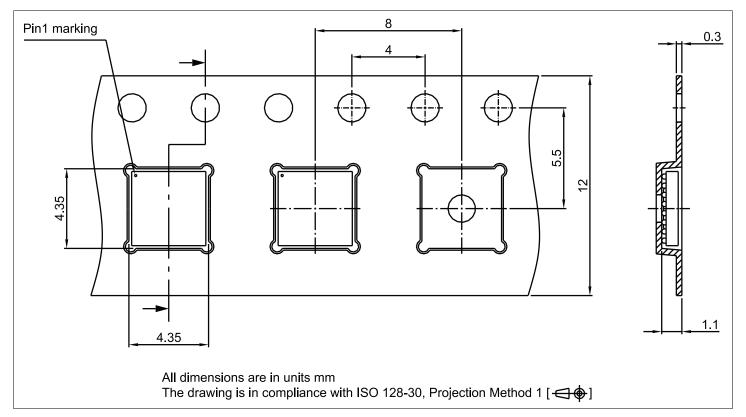

| 11     | Package                         | 120 |

| 11.1   | Built-in antenna specifications | 123 |

|        | Glossary                        | 125 |

|        | Revision history                |     |

|        | Disclaimer                      | 120 |

## 1 Introduction

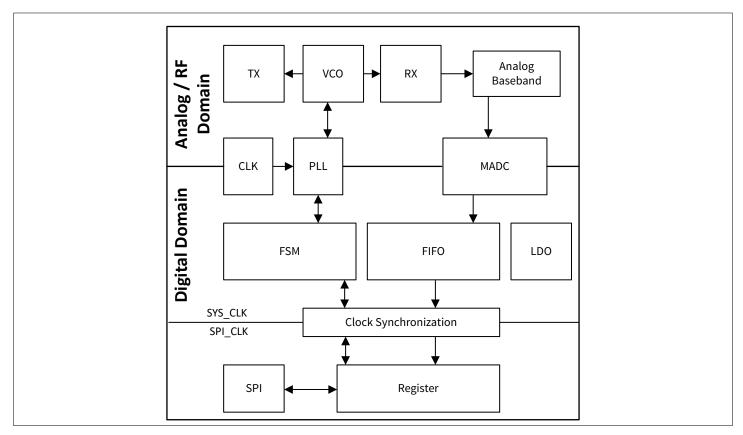

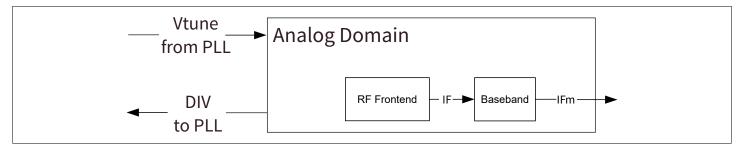

Smart sensors can be based on radar systems, in special case, frequency-modulated continuous wave (FMCW) radars. Those systems can comprise several blocks: radio frequency (RF) front-end, analog base band (ABB), analog-to-digital converter (ADC), phase-locked loop (PLL), memory (first in first out (FIFO)), serial peripheral interface (SPI) and antennas. Smart sensors require a high level of integration, thus, the components listed above should be integrated in a single chip solution. BGT60UTR11AIP offers this level of integration in a single chip.

### 1.1 Product overview

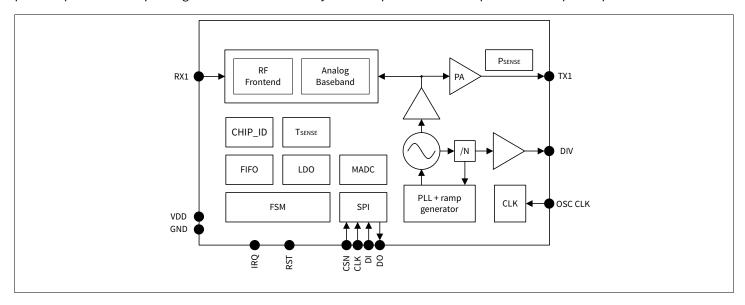

The core functionality of BGT60UTR11AIP is to transmit frequency-modulated continuous wave signal through the *transmitter (TX)* channel and receive the echo signal from the target object on the *receiver (RX)* channel. The receiver path includes a baseband filtering, a *variable gain amplifier (VGA)*, as well as an *ADC*. The digitized output is stored in a *FIFO* based memory. The data are transferred to an external host, *microcontroller unit (MCU)* or *application processor (AP)*, to run radar signal processing. A typical implementation of a sensor system consists of two main blocks:

- Radar sensor (BGT60UTR11AIP) handles the RF signals and provides the sampled intermediate frequency (IF) signals

- AP or microcontroller unit which captures and processes the digital radar signals

Figure 2 Data flow in the complete radar sensor system

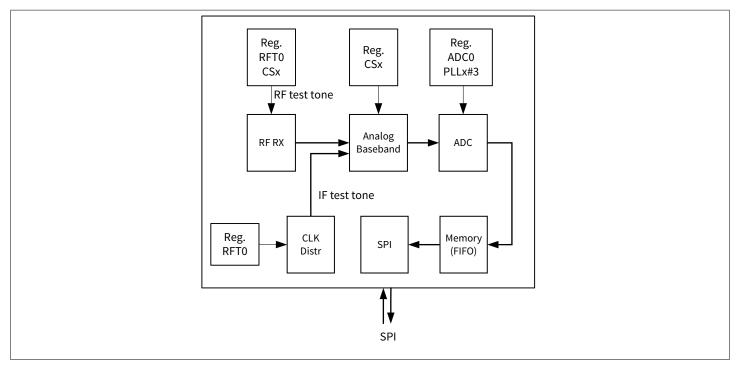

# 1.2 BGT60UTR11AIP block diagram

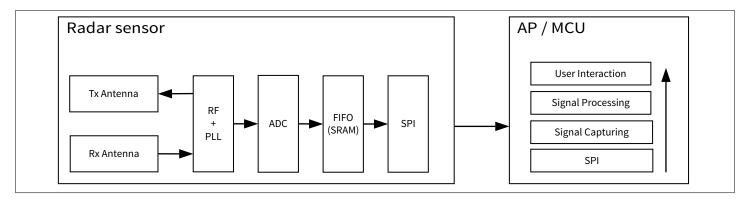

BGT60UTR11AIP block diagram is presented in the following figure.

Figure 3 BGT60UTR11AIP block diagram

### Feature list:

- Single supply voltage level of 1.8 V for both, digital and analog domains

- Integrated low-dropout voltage regulator (LDO) to supply the digital domain

- Separated 3.3 V supply for loop filter

- RF-Frontend at 60 GHz covering frequencies from 57.4 to 63.0 GHz with 1 TX and 1 RX channels

- Baseband chain consisting of high-pass filter (HPF), low noise VGA, and anti-aliasing filter (AAF)

- 1 ADC channel with 12 bits resolution and up to 4 MSps sampling rate to sample the RX-IF channel

- Integrated RF *PLL*, timers, counters and a *finite state machine (FSM)* to run sets of frames in standalone mode (no communication with *AP* or microcontroller unit required except first trigger and raw data transfer)

- Full duplex FIFO structure as data buffer (49 kbit = 2048 words x 24 bits)

- Standard *SPI* mode for configuration and status register read accesses

- Dedicated power modes for power reduction

- An external 38.4/40/76.8/80 MHz reference oscillator can be used as a system clock source

- An internal frequency doubler is used in case the input clock is 38.4/40 MHz

- built-in test equipment (BITE) for end of line (EOL) test in production at Infineon to verify RF performance

- linear feedback shift register (LFSR) test pattern generator on chip for data transfer check

- Fabricated with BiCMOS Infineon process technology

- Housed in a laminate package

- Antennas integrated in the package

- 48 bits for unique CHIP ID for each device

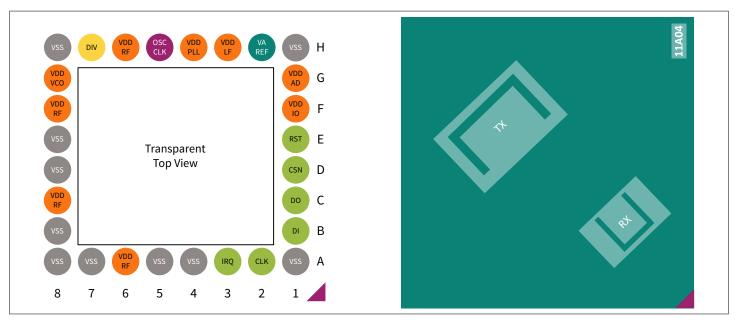

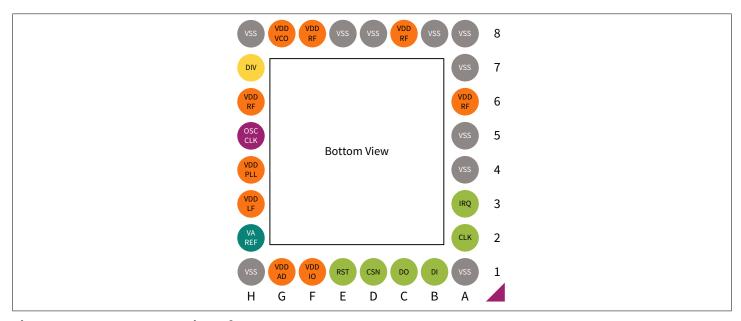

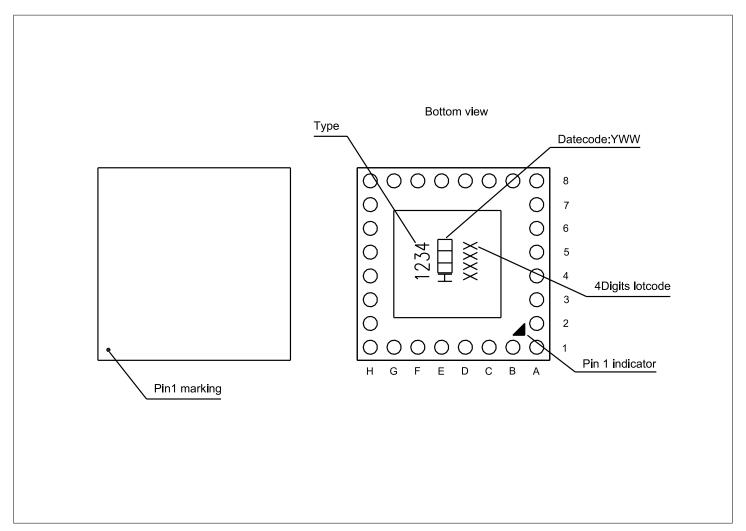

# 1.3 BGT60UTR11AIP pin definition and function

The following figure shows the transparent top view of the BGT60UTR11AIP laminate package with the pin and antenna number assignment.

Figure 4 BGT60UTR11AIP pin and antenna number assignment

The function of each pin is described in the following tables.

Table 1 Ball definition

| Ball                                   | Function                                                |

|----------------------------------------|---------------------------------------------------------|

| A1, A4, A5, A7, A8, B8, D8, E8, H1, H8 | VSS <sub>RF</sub> , VSS <sub>A</sub> , VSS <sub>D</sub> |

| A2                                     | CLK                                                     |

| A3                                     | IRQ                                                     |

| B1                                     | DI                                                      |

| C1                                     | DO                                                      |

| D1                                     | CSN                                                     |

| E1                                     | RST                                                     |

| F1                                     | VDD <sub>IO</sub>                                       |

| A6, C8, F8, H6                         | <i>VDD</i> <sub>RF</sub>                                |

| G1                                     | <i>VDD</i> <sub>AD</sub>                                |

| G8                                     | $VDD_{VCO}$                                             |

| H2                                     | $V_{AREF}$                                              |

| H3                                     | <i>VDD</i> <sub>LF</sub>                                |

| H4                                     | VDD <sub>PLL</sub>                                      |

| H5                                     | OSC_CLK                                                 |

| H7                                     | DIV                                                     |

### **Datasheet**

1 Introduction

#### Table 2 **Antenna definition**

| Antenna | Function      |

|---------|---------------|

| TX1     | Transmitter 1 |

| RX1     | Receiver 1    |

### **IO and supply pins** 1.3.1

The following table gives an overview on the input/output pins of BGT60UTR11AIP.

### **Abbreviations:**

- V<sub>IN</sub>: voltage input pin

- V<sub>OUT</sub>: voltage output pin

- D<sub>IN</sub>: digital input pin

- D<sub>OUT</sub>: digital output pin

- A<sub>IN</sub>: analog input pin

- A<sub>OUT</sub>: analog output pin

- GND<sub>D</sub>: digital ground connection

- GND<sub>A</sub>: analog ground connection

### Table 3 **BGT60UTR11AIP** input/output pins

| Symbol  | Туре             | Domain                   | Description                            | Туре    |

|---------|------------------|--------------------------|----------------------------------------|---------|

| DIV     | A <sub>OUT</sub> | <i>VDD</i> <sub>RF</sub> | VCO divided by 16 output               | Analog  |

| OSC_CLK | A <sub>IN</sub>  | <i>VDD</i> <sub>RF</sub> | Oscillator input                       | Analog  |

| CLK     | D <sub>IN</sub>  | VDD <sub>IO</sub>        | SPI clock input                        | Digital |

| CSN     | D <sub>IN</sub>  | <i>VDD</i> <sub>IO</sub> | SPI chip select input, active low      | Digital |

| DI      | D <sub>IN</sub>  | VDD <sub>IO</sub>        | SPI signal from the host output (MOSI) | Digital |

| DO      | D <sub>OUT</sub> | <i>VDD</i> <sub>IO</sub> | SPI signal to the host input (MISO)    | Digital |

| RST     | D <sub>IN</sub>  | VDD <sub>IO</sub>        | Hardware reset pin                     | Digital |

| IRQ     | D <sub>OUT</sub> | VDD <sub>IO</sub>        | Interrupt output                       | Digital |

The power supply pins are described in the following table.

Table 4 **BGT60UTR11AIP** supply pins

| Domain                   | Туре             | Value | Description                                       | Domain                 |

|--------------------------|------------------|-------|---------------------------------------------------|------------------------|

| VDD <sub>AD</sub>        | V <sub>IN</sub>  | 1.8 V | Analog and digital supply voltage                 | Analog-ADC,<br>Digital |

| VDD <sub>IO</sub>        | V <sub>IN</sub>  | 1.2 V | IO pad supply voltage                             | 10                     |

|                          |                  | 1.8 V |                                                   |                        |

| $V_{AREF}$               | V <sub>OUT</sub> | 1.2 V | Positive reference voltage output; for bypass cap | Analog-ADC             |

| VDD <sub>VCO</sub>       | V <sub>IN</sub>  | 1.8 V | Analog supply voltage to the VCO                  | Analog-RF              |

| <i>VDD</i> <sub>RF</sub> | V <sub>IN</sub>  | 1.8 V | Analog supply voltage                             | Analog-RF              |

(table continues...)

## **Datasheet**

# Table 4 (continued) BGT60UTR11AIP supply pins

| Domain             | Туре             | Value | Description                                                         | Domain     |

|--------------------|------------------|-------|---------------------------------------------------------------------|------------|

| VDD <sub>LF</sub>  | V <sub>IN</sub>  | 3.3 V | Analog supply voltage for the level shifter for the PLL loop filter | Analog-RF  |

| VDD <sub>PLL</sub> | V <sub>IN</sub>  | 1.8 V | Analog supply voltage to the PLL                                    | Analog-RF  |

| VSS <sub>RF</sub>  | GND <sub>A</sub> | 0 V   | Analog ground connection                                            | Analog-RF  |

| VSS <sub>A</sub>   | GND <sub>A</sub> | 0 V   | Analog ground connection                                            | Analog-ADC |

| VSS <sub>D</sub>   | $GND_D$          | 0 V   | Digital ground connection                                           | Digital    |

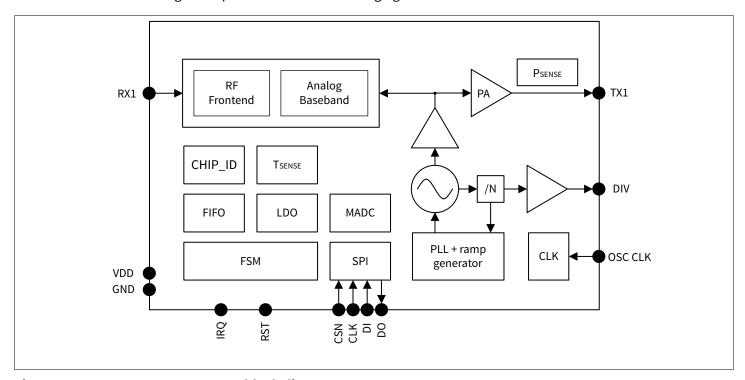

# 1.4 BGT60UTR11AIP functional block diagram

BGT60UTR11AIP consists of some main functional blocks:

- FSM which manages the complete chip

- Register banks, see Chapter 4

- FIFO, 49 kbit = 2048 words x 24 bits

- SPI, up to 50 MHz clock

- Two clock domains

- system clock domain for example 38.4/40/76.8/80 MHz for PLL, ADC and FIFO

- SPI clock for example 50 MHz

- PLL, 3<sup>rd</sup> order sigma-delta based to perform *FMCW* ramp

- RF frontend consisting of 1 RX channel, 1 TX channel, local oscillator (LO) generation and divider by 4/5, see Chapter 7.1

- ABB consisting of HPF, VGA and AAF, see Chapter 7.2

- 1 channel multi ADC, 12 bits differential SAR ADC interfaced to the ABB via a driver and to the FIFO via a multiplexer, see Chapter 8

- Antenna built in package, see Chapter 11

Figure 5 BGT60UTR11AIP functional overview

### **Datasheet**

2 General product specification

## 2 General product specification

The reference for all specified data is the Infineon application board, available on request.

# 2.1 Absolute maximum ratings

### Table 5 Absolute maximum ratings

$T_b$  = -40 °C to 105 °C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified). Parameters not subject to production test.

| Parameter            | Symbol                    |      | Value |      |     | Condition                 |

|----------------------|---------------------------|------|-------|------|-----|---------------------------|

|                      |                           | Min. | Тур.  | Max. |     |                           |

| Supply Voltage       | <i>VDD</i> <sub>AD</sub>  | -0.3 | -     | +2.0 | V   | -                         |

| Supply Voltage       | <i>VDD</i> <sub>IO</sub>  | -0.3 | -     | +2.0 | V   | -                         |

| Supply Voltage       | <i>VDD</i> <sub>RF</sub>  | -0.3 | -     | +2.0 | V   | -                         |

| Supply Voltage       | <i>VDD</i> <sub>VCO</sub> | -0.3 | -     | +2.0 | V   | -                         |

| Supply Voltage       | <i>VDD</i> <sub>PLL</sub> | -0.3 | -     | +2.0 | V   | -                         |

| Supply Voltage       | <i>VDD</i> <sub>LF</sub>  | -0.3 | -     | +3.7 | V   | -                         |

| RF Input Power Level | $P_{RF}$                  | -    | -     | +10  | dBm | At the RX input pad (die) |

| Junction Temperature | $T_{\rm j}$               | -40  | -     | +125 | °C  | -                         |

| Storage Temperature  | $T_{\rm stg}$             | -40  | -     | +150 | °C  | -                         |

### Warning:

Stresses above the maximum values listed here may cause permanent damage to the device. Maximum ratings are absolute ratings; exceeding only one of these values may cause irreversible damage to the integrated circuit. Exposure to conditions at or below absolute maximum rating but above the specified maximum operation conditions may affect device reliability and lifetime. Functionality of the device might not be given under these conditions.

# 2.2 Range of functionality

Table 6 Range of functionality

| Parameter      | Symbol                    |      | Value             |      |   | Condition                             |

|----------------|---------------------------|------|-------------------|------|---|---------------------------------------|

|                |                           | Min. | Тур.              | Max. |   |                                       |

| Supply Voltage | <i>VDD</i> <sub>AD</sub>  | 1.71 | 1.8               | 1.89 | V | Noise on each                         |

| Supply Voltage | VDD <sub>IO</sub>         | 1.14 | 1.2               | 1.26 | V | supply domain should not exceed       |

|                |                           | 1.71 | 1.8               | 1.89 |   | the level of 20 µVpp                  |

| Supply Voltage | <i>VDD</i> <sub>RF</sub>  | 1.71 | 1.8               | 1.89 | V | in the frequency                      |

| Supply Voltage | <i>VDD</i> <sub>VCO</sub> | 1.71 | 1.8               | 1.89 | V | range 20 kHz -<br>1 MHz <sup>1)</sup> |

| Supply Voltage | VDD <sub>PLL</sub>        | 1.71 | 1.8               | 1.89 | V |                                       |

| Supply Voltage | <i>VDD</i> <sub>LF</sub>  | 2.5  | 3.3 <sup>2)</sup> | 3.63 | V |                                       |

(table continues...)

### **Datasheet**

2 General product specification

### Table 6 (continued) Range of functionality

| Parameter                            | Symbol                                                                                                                                                                                                                                                                                                                                                                                                                                |                                              | Value |      | Unit | Condition                                                                 |

|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|-------|------|------|---------------------------------------------------------------------------|

|                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                       | Min.                                         | Тур.  | Max. |      |                                                                           |

| Chip Backside Temperature            | Min.         Typ.         Max.           erature $T_{\rm b}$ -20         -         70         °C $f_{\rm RF}$ 57.4         -         63.0         GHz           k Frequency $f_{\rm OSC\_CLK}\#1$ 75         80         85         MHz $f_{\rm OSC\_CLK}\#2^{3}$ 37.5         40         42.5         MHz $f_{\rm DUTOSC}$ 45         50         55         % $f_{\rm OSC\_CLK}$ $f_{\rm RS,FS,SYS}$ -         2         6         ns | Measured with the on-chip temperature sensor |       |      |      |                                                                           |

| Frequency Range                      | $f_{RF}$                                                                                                                                                                                                                                                                                                                                                                                                                              | 57.4                                         | -     | 63.0 | GHz  | -                                                                         |

| Oscillator Input Clock Frequency     | f <sub>OSC_CLK</sub> #1                                                                                                                                                                                                                                                                                                                                                                                                               | 75                                           | 80    | 85   | MHz  | 1.8 V CMOS clock<br>78 MHz not allowed<br>(frequency doubler<br>disabled) |

|                                      | f <sub>osc_clk</sub> #2 <sup>3)</sup>                                                                                                                                                                                                                                                                                                                                                                                                 | 37.5                                         | 40    | 42.5 | MHz  | 1.8 V CMOS clock<br>39 MHz not allowed<br>(frequency doubler<br>enabled)  |

| Duty cycle of f <sub>OSC_CLK</sub>   | $f_{DUTOSC}$                                                                                                                                                                                                                                                                                                                                                                                                                          | 45                                           | 50    | 55   | %    | -                                                                         |

| Rise and Fall Time of $f_{OSC\_CLK}$ | t <sub>RS,FS,SYS</sub>                                                                                                                                                                                                                                                                                                                                                                                                                | -                                            | 2     | 6    | ns   | -                                                                         |

| Phase Jitter of $f_{ m OSC\_CLK}$    | J <sub>PHOSC</sub>                                                                                                                                                                                                                                                                                                                                                                                                                    | -                                            | 1     | -    | ps   | <i>BW</i> : 12 kHz to 20 MHz                                              |

<sup>1)</sup> This value will ensure no artifact/false target in the Range-Doppler map when it is calculated with a minimum of 8 chirps.

# 2.3 Current consumption

## Table 7 Overall current consumption

$VDD_X$ = 1.71 V to 1.89 V,  $VDD_{LF}$ = 2.5 V to 3.3 V and  $T_b$  = -20 °C to +70 °C.

| Parameter                           | Symbol                |      | Value |                     |    | Condition |

|-------------------------------------|-----------------------|------|-------|---------------------|----|-----------|

|                                     |                       | Min. | Тур.  | Max.                |    |           |

| Idd Deep Sleep <sup>1)</sup>        | Idd <sub>DS</sub>     | 0.05 | 0.178 | 0.555 <sup>2)</sup> | mA |           |

| Idd Idle <sup>3)</sup>              | Idd <sub>Idle</sub>   | -    | 1.8   | -                   | mA | -         |

| Idd Init0, 1RX + 1TX                | Idd <sub>Init0</sub>  | -    | 3.2   | -                   | mA | -         |

| Idd Init1, 1RX + 1TX <sup>4)</sup>  | Idd <sub>Init1</sub>  | -    | 149   | -                   | mA | -         |

| Idd Active, 1RX + 1TX <sup>5)</sup> | Idd <sub>Active</sub> | 110  | 174   | 220                 | mA | -         |

<sup>1)</sup> All registers in reset mode,  $f_{SYS\_CLK}$  clock path disabled.

<sup>2)</sup> Specified maximum bandwidth requires at least  $VDD_{LF} = 3.3 \text{ V}$ .

<sup>3)</sup> In case  $f_{OSC\_CLK}$ #2 is used as input clock, an internal doubler will be used to multiply the input frequency by two. The doubler duty-cycle can be calibrated. See PLL interfaces and clock distribution, Reference clock distribution.

<sup>2)</sup> The value at maximum refers to the maximum temperature, +70 °C, and the maximum supply, 1.89 V.

<sup>3)</sup> MADC band gap running.

<sup>4)</sup> Idd for the rest of interchirp similar to Init1.

Device set in radar mode; DAC TX set to 31<sub>D</sub>.

### 2 General product specification

## Table 8 VDD<sub>AD</sub> domain current consumption

$VDD_X$ = 1.71 V to 1.89 V,  $VDD_{LF}$ = 2.5 V to 3.3 V,  $VDD_{IO}$ = 1.14 V to 1.26 V and  $T_b$  = -20 °C to +70 °C.

| Parameter                           | Symbol                 |      | Value |                     |    | Condition |

|-------------------------------------|------------------------|------|-------|---------------------|----|-----------|

|                                     |                        | Min. | Тур.  | Max.                |    |           |

| Idd Deep Sleep <sup>1)</sup>        | ADIdd <sub>DS</sub>    | 0.05 | 0.147 | 0.490 <sup>2)</sup> | mA | -         |

| Idd Idle <sup>3)</sup>              | ADIdd <sub>Idle</sub>  | -    | 2.0   | -                   | mA | -         |

| Idd Init0, 1RX + 1TX                | ADIdd <sub>Init0</sub> | -    | 2.5   | -                   | mA | -         |

| Idd Init1, 1RX + 1TX <sup>4)</sup>  | ADIdd <sub>Init1</sub> | -    | 3.3   | -                   | mA | -         |

| Idd Active, 1RX + 1TX <sup>5)</sup> | $ADIdd_{Active}$       | 2.1  | 3.3   | 6.2                 | mA | -         |

- 1) All registers in reset mode,  $f_{SYS\_CLK}$  clock path disabled.

- 2) The value at maximum refers to the maximum temperature, +70 °C, and the maximum supply, 1.89 V.

- 3) MADC band-gap running.

- 4) Idd for the rest of interchirp similar to Init1.

- 5) Device set in radar mode, FIFO in low power mode, DAC TX set to 31<sub>D</sub> for an output power of +5 dBm.

## Table 9 VDD<sub>PLL</sub> domain current consumption

$VDD_X$ = 1.71 V to 1.89 V,  $VDD_{LF}$ = 2.5 V to 3.3 V and  $T_b$  = -20 °C to +70 °C.

| Parameter                           | Symbol                   | Value |        |      | Unit | Condition |  |

|-------------------------------------|--------------------------|-------|--------|------|------|-----------|--|

|                                     |                          | Min.  | Тур.   | Max. |      |           |  |

| Idd Deep Sleep <sup>1)</sup>        | PLLIdd <sub>DS</sub>     | 0     | 0.0002 | 0.01 | mA   | -         |  |

| Idd Idle <sup>2)</sup>              | PLLIdd <sub>Idle</sub>   | -     | 0.0002 | -    | mA   | -         |  |

| Idd Init0, 1RX + 1TX                | PLLIdd <sub>Init0</sub>  | -     | 0.9    | -    | mA   | -         |  |

| Idd Init1, 1RX + 1TX <sup>3)</sup>  | PLLIdd <sub>Init1</sub>  | -     | 7.9    | -    | mA   | -         |  |

| Idd Active, 1RX + 1TX <sup>4)</sup> | PLLIdd <sub>Active</sub> | 5     | 8      | 10   | mA   | -         |  |

- 1) All registers in reset mode,  $f_{SYS\_CLK}$  clock path disabled.

- 2) MADC band-gap running.

- 3) Idd for the rest of interchirp similar to Init1.

- 4) Device set in radar mode, DAC TX set to 31<sub>D</sub>.

### Table 10 VDD<sub>LF</sub> domain current consumption

$VDD_X$ = 1.71 V to 1.89 V,  $VDD_{LF}$ = 2.5 V to 3.3 V and  $T_b$  = -20 °C to +70 °C.

| Parameter                           | Symbol                  |      | Value  |      |    | Condition |

|-------------------------------------|-------------------------|------|--------|------|----|-----------|

|                                     |                         | Min. | Тур.   | Max. |    |           |

| Idd Deep Sleep <sup>1)</sup>        | LFIdd <sub>DS</sub>     | 0    | 0.0002 | 0.01 | mA | -         |

| Idd Idle <sup>2)</sup>              | LFIdd <sub>Idle</sub>   | -    | 0.0002 | -    | mA | -         |

| Idd Init0, 1RX + 1TX                | LFIdd <sub>Init0</sub>  | -    | 0.39   | -    | mA | -         |

| Idd Init1, 1RX + 1TX <sup>3)</sup>  | LFIdd <sub>Init1</sub>  | -    | 0.39   | -    | mA | -         |

| Idd Active, 1RX + 1TX <sup>4)</sup> | LFIdd <sub>Active</sub> | 0.2  | 0.39   | 0.53 | mA | -         |

- 1) All registers in reset mode,  $f_{SYS\_CLK}$  clock path disabled.

- 2) MADC band-gap running.

- 3) Idd for the rest of interchirp similar to Init1.

### **Datasheet**

### 2 General product specification

4) Device set in radar mode, DAC TX set to 31<sub>D</sub>.

## Table 11 VDD<sub>RF</sub> + VDD<sub>VCO</sub> domain current consumption

$VDD_X$ = 1.71 V to 1.89 V,  $VDD_{LF}$ = 2.5 V to 3.3 V and  $T_b$  = -20 °C to +70 °C.

| Parameter                           | Symbol                  |      | Value |       | Unit | Condition |

|-------------------------------------|-------------------------|------|-------|-------|------|-----------|

|                                     |                         | Min. | Тур.  | Max.  |      |           |

| Idd Deep Sleep <sup>1)</sup>        | RFIdd <sub>DS</sub>     | 0    | 0.003 | 0.045 | mA   | -         |

| Idd Idle <sup>2)</sup>              | RFIdd <sub>Idle</sub>   | -    | 0.005 | -     | mA   | -         |

| Idd Init0, 1RX + 1TX                | RFIdd <sub>Init0</sub>  | -    | 0.005 | -     | mA   | -         |

| Idd Init1, 1RX + 1TX <sup>3)</sup>  | RFIdd <sub>Init1</sub>  | -    | 137   | -     | mA   | -         |

| Idd Active, 1RX + 1TX <sup>4)</sup> | RFIdd <sub>Active</sub> | 100  | 162   | 220   | mA   | -         |

- 1) All registers in reset mode,  $f_{SYS\_CLK}$  clock path disabled.

- 2) MADC band-gap running.

- 3) Idd for the rest of interchirp similar to Init1.

- 4) Device set in radar mode, DAC TX set to 31<sub>D</sub>.

### Table 12 VDD<sub>IO</sub> domain current consumption

$VDD_{IO}$ = 1.71 V to 1.89 V and  $T_b$  = -20 °C to +70 °C.

| Parameter                    | Symbol                  |      | Value |                   | Unit | Condition    |

|------------------------------|-------------------------|------|-------|-------------------|------|--------------|

|                              |                         | Min. | Тур.  | Max.              |      |              |

| Idd Deep Sleep <sup>1)</sup> | IOIdd <sub>DS</sub>     | 0    | -     | 0.1 <sup>2)</sup> | mA   | Standard SPI |

| Idd Active <sup>3)</sup>     | IOIdd <sub>Active</sub> | 0    | -     | 0.17              | mA   | Standard SPI |

- 1) All registers in reset mode,  $f_{SYS\_CLK}$  clock path disabled.

- 2) The value at maximum refers to the maximum temperature, +70°C, and the maximum supply, 1.89 V.

- 3) Activity on SPI MISO and MOSI line.

# 2.4 ESD integrity

### Table 13 ESD integrity

Datasheet

$VDD_X$ = 1.71 V to 1.89 V,  $VDD_{LF}$ = 2.5 V to 3.3 V,  $VDD_{IO}$ = 1.08 V to 1.32 V and  $T_b$  = -20 °C to +70 °C.

| Parameter                                         | Symbol               |       | Value |       |   | Condition                      |

|---------------------------------------------------|----------------------|-------|-------|-------|---|--------------------------------|

|                                                   |                      | Min.  | Тур.  | Max.  |   |                                |

| ESD robustness, human body model (HBM)            | V <sub>ESD-HBM</sub> | -2000 | -     | +2000 | V | According to JS-001. All pins. |

| ESD robustness, <i>charged device</i> model (CDM) | V <sub>ESD-CDM</sub> | -500  | -     | +500  | V | According to JS-002.           |

charged device model: Field-Induced Charged-Device Model ANSI/ESDA/JEDEC JS-002. Simulates charging/discharging events that occur in production equipment and processes. Potential for CDM ESD events occurs whenever there is metal-to-metal contact in manufacturing.

human body model: Human Body Model ANSI/ESDA/JEDEC JS-001 ( $R = 1.5 \text{ k}\Omega$ , C = 100 pF).

15

## **Datasheet**

2 General product specification

# 2.5 Thermal resistance

## Table 14 Thermal resistance

$VDD_X$ = 1.71 V to 1.89 V,  $VDD_{LF}$ = 2.5 V to 3.3 V,  $VDD_{IO}$ = 1.08 V to 1.32 V and  $T_b$  = -20 °C to +70 °C.

| Parameter                  | Symbol          |      | Value |      | Value |                                      | Value |  | Value |  | Unit | Condition |

|----------------------------|-----------------|------|-------|------|-------|--------------------------------------|-------|--|-------|--|------|-----------|

|                            |                 | Min. | Тур.  | Max. |       |                                      |       |  |       |  |      |           |

| Package thermal resistance | R <sub>th</sub> | -    | 35    | -    | K/W   | Chip backside to ambient temperature |       |  |       |  |      |           |

3 Shapes, frames and channel set definition

### Shapes, frames and channel set definition 3

This section is intended to provide the user with an overview on the overall modulation and power modes capabilities of BGT60UTR11AIP. Specifically, the structure of timers, counters, shapes, channel set and frames will be presented. The section also gives a description of how the FSM is setting and controlling the PLL for the expected modulation shapes and sequences programmed by the host.

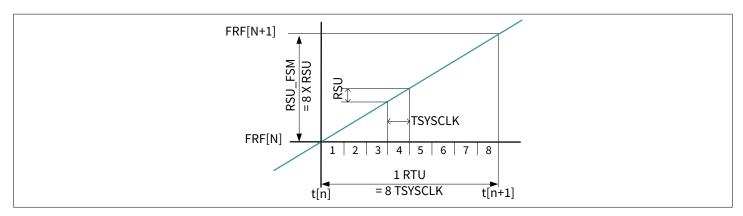

### 3.1 **Shapes and frames**

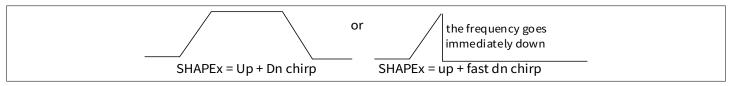

The shape is the modulation chirp that should be performed by the PLL. Two basic shapes are allowed (see Shape definition):

- Triangular shape: consisting of a frequency upchirp and a frequency downchirp

- Saw-tooth shape: consisting of a frequency upchirp followed by a fast downchirp

The shapes are set and enabled in the PLLx[0..7] registers (see PLL shape x register 0 and PLL shape x register 7) by the bit PLLx7:SH EN. Up to four different shapes can be programmed. If more than one shape is used, the lower shapes must be programmed (e.g. if 3 shapes are needed by the application, then x = 1...3).

N SHAPE EN is the number of shapes enabled.

Figure 6 **Shape definition**

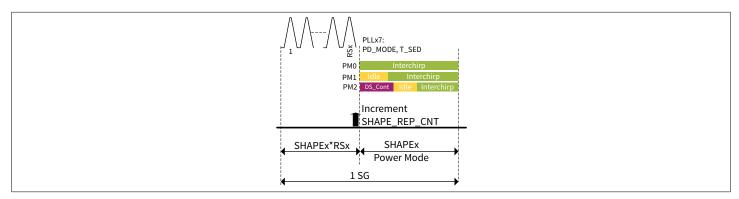

### Shape group

Each shape defined above can be repeated several times (see Shape group). The same shape repeated several times represents a shape group (SG). The repetition factor for the shape x is called REPSx and described in PLL shape x register 7. Each shape is repeated RSx = 2<sup>REPSx</sup> times.

Figure 7 Shape group

After the last repetitions the FSM will enter, for a period PLLx7:T\_SED (see PLL shape x register 7), the power mode programmed according to what is specified in PLLx7:PD\_MODE (see PLL shape x register 7).

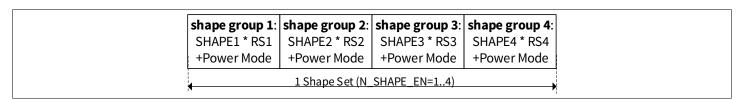

After a shape group, the shape groups counter STAT1: SHAPE GRP CNT is incremented (see Status register 1). In Shape set an example of four programmed shape groups is shown. It represents a shape set.

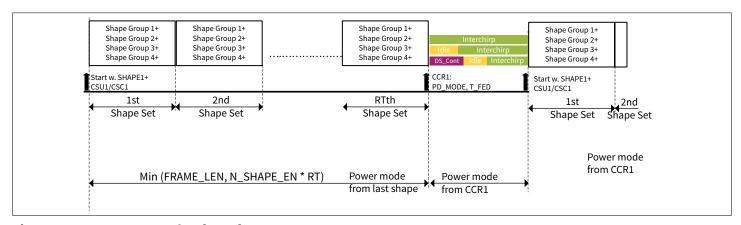

Figure 8 Shape set

### **Datasheet**

3 Shapes, frames and channel set definition

### **Frame**

A frame, as shown in Example of one frame, is a sequence of shape sets followed by a specific power mode. Each shape set can be repeated several times. The repetition factor for the shape set x is called REPTx and described in Chirp control register 0. Each shape set is repeated RTx =  $2^{REPTx}$  times.

The length of a frame is defined through CCR2: FRAME\_LEN (see Chirp control register 2), which is the number of shape groups to be executed.

At each start of a frame, the first shape SHAPE1 together with the first channel set, CSU1+CSC1, is loaded.

The number of frame groups the FSM will execute will be:

• min(CCR2:FRAME\_LEN, N\_SHAPE\_EN \* RT)

With RT ≤ (4096/shape groups) and CCR2:FRAME\_LEN < 4096.

After the last shape group in a frame, the power mode from CCR1:PD\_MODE is used for the period programmed in CCR1:T FED instead of PPLx7:MODE for period PLLx7:T SED.

Figure 9 Example of one frame

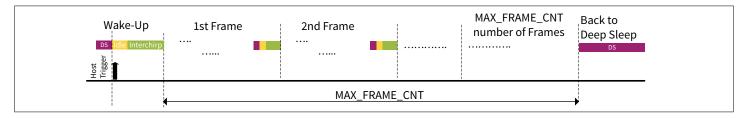

### **Maximum number of frames**

- The overall frame generation starts after the wake-up period with the first frame

- After the last frame CCR2: MAX\_FRAME\_CNT (see Chirp control register 2) is reached, the FSM will enter the deep sleep mode instead of the power mode defined at the end of the last but one frame

- In order to trigger the chip again, a FSM reset is required

Figure 10 Maximum number of frames

### 3.2 Channel set

A channel set is a set of registers to control the configurations of the available transmit and receive channels. Each channel set can be repeated several times. The repetition factor for the channel set x is called REPCx and described in Channel set control x register. Each channel set is repeated RCx = 2^REPCx times. There are in total 10 channel sets of 3 different types acting in the specific "modes". 8 channel sets relate to the shapes (4 shapes x "up" and "down" segment settings) and two to the power modes, idle and deep sleep, respectively:

- Deep sleep power mode is related to channel set CSDS and CSCDS

- Idle mode is related to channel set CSI and CSCI.

### **Datasheet**

# infineon

### 3 Shapes, frames and channel set definition

- 8 channel sets are defined for the shapes:

- CSU1 ... CSU4 registers for up-chirp

- CSD1 ... CSD4 registers for down-chirp

- CSC1 ... CSC4 channel set configuration registers for up- and down-chirp

- Each shape from above has up to 2 channel sets CSUx and CSDx

- In case triangular shape is used, CSUx and CSDx are applied

- In case sawtooth shape is used, CSDx is skipped

- Channel sets are repeated independent of the shapes

- Channel set repetition factor tells how often a single channel set is repeated until the next channel set is loaded

- On the channel set sequence:

- The lower channel set number is followed by the next higher channel set number

- In case the highest channel set number is reached, the next channel set loaded is channel set 1

- On the enabling sequence of channel sets:

- In case not all channel sets are used, the lower number channel sets have to be used

- In between the enabled channel sets must not be a disabled channel set

- E.g.: 2 channel sets expected: use only CS1 and CS2. In case 3 channel sets are expected, use only CS1, CS2, and CS3

- Start and end of channel set sequences:

- After reset, the first channel set loaded is CS1

- After a frame starts the first channel set loaded will be CS1

**Note**: It would be preferable to have REPS = REPC.

### **Datasheet**

3 Shapes, frames and channel set definition

### 3.3 Power modes

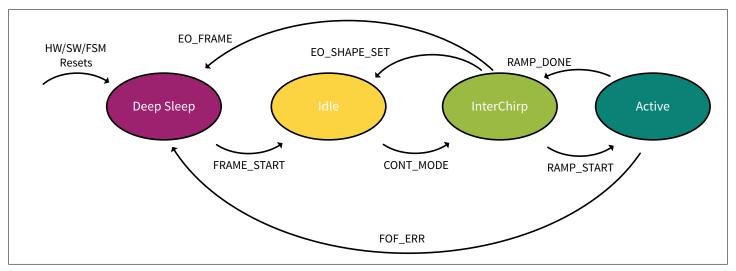

The following figure shows the flow chart on all possible power modes for the FSM.

Figure 11 FSM flow chart

### Power Management through the power modes

The power modes enable the host to have full flexibility on power consumption during each state of radar frame generation. A set of isolation registers (see Channel set control x register) enables/disables the different blocks of the chip. The power modes are managed by the FSM.

## 3.3.1 Mode descriptions

In active, idle, and deep sleep mode the power mode can be defined in the CSCx register, Channel set control x register, for all channel sets: CSC1..4, CSI, CSCDS (CSUx = Channel Set Upchirp, CSDx = Channel Set Deep Sleep).

### **Active mode definition:**

- During a shape: PLLx7:PD\_MODE = 0<sub>D</sub>

- Power mode defined through registers CSx (CHS1..CHS4), same mode for up-/downchirp

- Default Setting: all expected settings are enabled by the host

### Interchirp mode definition:

- During a shape: PLLx7:PD\_MODE = 0<sub>D</sub>

- Power mode basically the same as active mode, exception: TX1 off (PAOFF)

### Idle mode definition:

- After a shape: PLLx7:PD\_MODE = 1<sub>D</sub>

- After a frame: CCR1:PD\_MODE = 1<sub>D</sub>

- Idle mode is defined through CSCI

- Wake-up from deep sleep for TR\_WKUP

The idle mode can be used as a low-power mode in between interchirp modes or after deep sleep mode to further reduce the overall power consumption while not entering the deep sleep mode. The wake-up times after Idle mode are faster compared to the ones after deep sleep mode.

### **Datasheet**

3 Shapes, frames and channel set definition

### **Entering deep sleep mode:**

- After a frame: CCR1:PD\_MODE = 2<sub>D</sub> and CCR0:CONT\_MODE = 0<sub>B</sub>

- Deep sleep mode is defined through CSCDS register (see Channel set control x register)

- · All blocks can be turned off

- Internal system clock is also turned off to achieve extra power saving when CONT\_MODE =  $0_B$  otherwise (CONT\_MODE =  $1_B$ ) the clock is kept up to count the internal timer T\_FED/T\_SED during the deep sleep

- In order to wake up the FSM from the deep sleep, the host has to program:

- PACR1:OSCCLKEN = 1<sub>B</sub> to enable the clock gating

- Then the first trigger can be applied via FRAME\_START

**Note**: No re-configuration need to be performed as the register content is retained in deep sleep mode.

### Entering deep sleep continuous mode:

- After a shape: PLLx7: PD\_MODE = 2<sub>D</sub> and PLLx7:CONT\_MODE = 1<sub>B</sub>

- After a frame: CCR1:PD\_MODE = 2<sub>D</sub> and CCR0:CONT\_MODE = 1<sub>B</sub>

In case CCR0:CONT\_MODE =  $\mathbf{1}_B$  is enabled, the wake-up from deep sleep is done automatically. The internal system clock is kept running.

### In case of errors:

If a FIFO overflow condition occurs, the FSM will bring the radar sensor into the deep sleep power mode even if the internal counters are holding the previous value, i.e., the FSM is not reset and a reset is required. In order to reset the FIFO, the host should send at least a MAIN:FIFO\_RESET command (see Main register).

If the FIFO overflow occurs, the event is reported in FSTAT:FOF\_ERR (see FIFO status register) or in GSR0:FOF\_ERR (see Chapter 4.49).

In this case, the data inside a FIFO can be read from the host as long as no reset occurs.

The flags FSTAT:FOF\_ERR and GSR0:FOF\_ERR are cleared after a reset.

**Note**: Each time the SPI will access the chip, the system clock will be enabled internally for synchronization reasons.

### 3 Shapes, frames and channel set definition

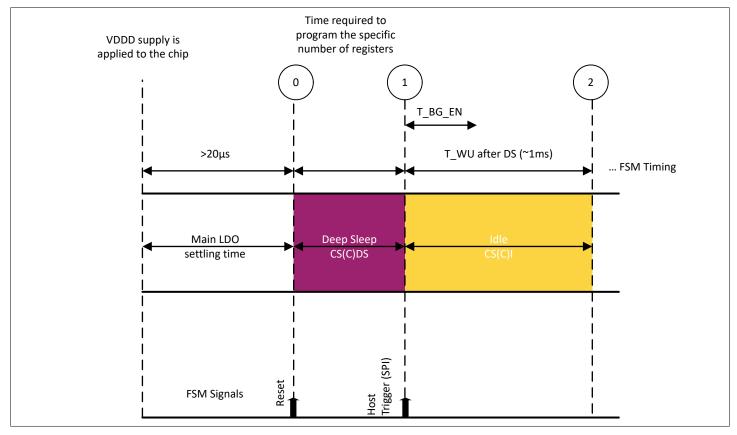

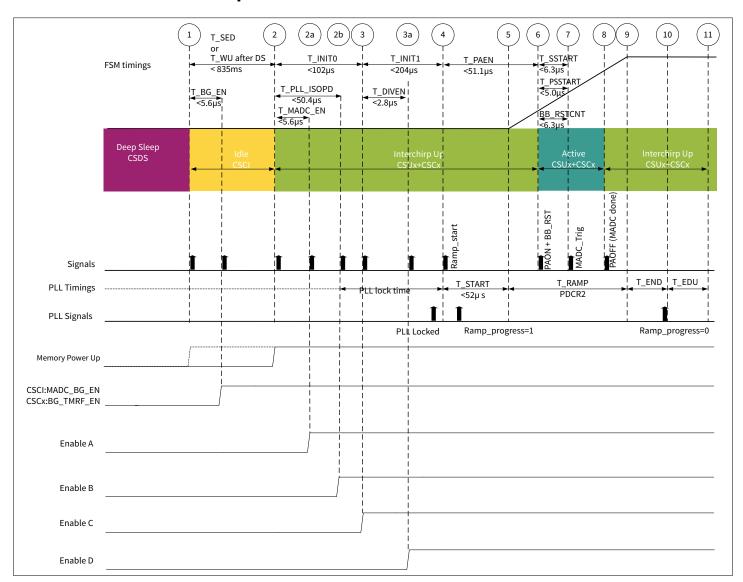

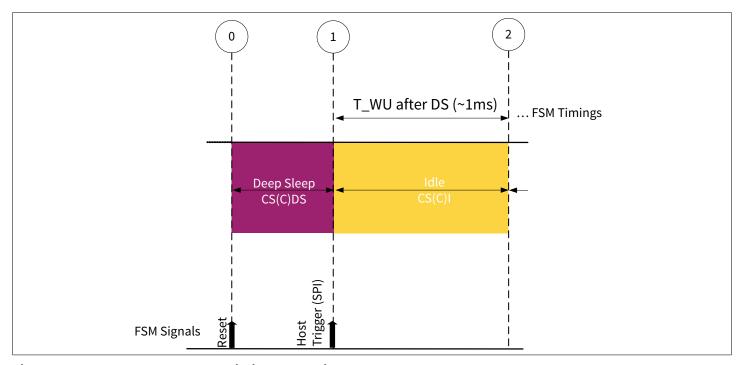

# 3.3.2 Wake-up phase from "deep sleep" to "idle"

After  $VDD_D$  is powered up, the main LDO will require 20  $\mu$ s to settle the internal generated core voltage  $VDD_C$ . Subsequently, the host has to perform a hardware reset to set the chip to the reset state (deep sleep). The following figure describes the timing for waking up the chip.

Figure 12 Deep sleep to idle transition

Table 15 Transitions from deep sleep into idle

| From # | To# | Description                                                                              | Signals  | Related time |

|--------|-----|------------------------------------------------------------------------------------------|----------|--------------|

| #0     |     | Chip is reset by host (see Hardware reset sequence)                                      |          |              |

| #0     | #1  | Host programs all registers needed for expected functionality                            |          |              |

| #1     |     | Host enables the oscillator: PACR1:OSCCLKEN= $1_{\mathrm{B}}$ to enable the clock gating |          |              |

| #1     |     | Host starts the first trigger; it can be applied through MAIN:FRAME_START                |          |              |

| #1     |     | Activate bandgap for MADC                                                                |          |              |

| #1     | #2  | Time required to settle the ADC BG (charge of external cap)                              |          | T_WU         |

| #2     |     | Enable PLL, MADC, and SADC                                                               |          |              |

| #2     |     | MADC sends ready signal to FSM                                                           | madc_rdy |              |

22

### 3 Shapes, frames and channel set definition

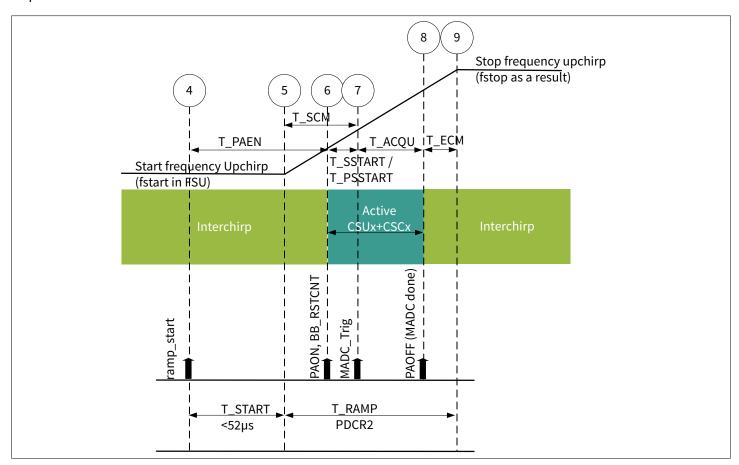

# 3.3.3 Idle to interchirp then active

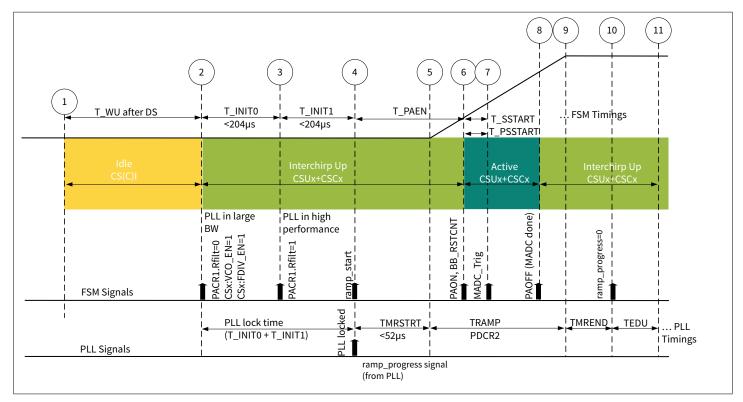

Figure 13 Transition from idle to interchirp to active to interchirp again

# Table 16 Transition from idle to interchirp to active to interchirp

| From<br># | To # | Description                                                                                                                                                                                                       | Signals | Related time |

|-----------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------------|

| #1        |      | Idle mode is activated                                                                                                                                                                                            |         |              |

| #1        |      | The user has to enable the bandgap (CSCI:BG_EN= 1 <sub>B</sub> in Channel set control x register)                                                                                                                 |         |              |

| #1        |      | In the case the memory is powered up after DS (SFCTL:FIFO_PD_MODE = $1_D$ ) the bandgap should be enabled delayed. This can be done by the user by programming CSCI:TR_BGEN                                       |         | T_BG_EN      |

| #1        | #2   | If Idle mode comes after a deep sleep (see transition from deep sleep to idle). Wake up time can be used as offset for chirps in case multiple devices are triggered together by <i>SPI</i> broadcast for example |         | T_WU         |

(table continues...)

## **Datasheet**

3 Shapes, frames and channel set definition

Table 16 (continued) Transition from idle to interchirp to active to interchirp

| From<br># | To # | Description                                                                                                                                                                           | Signals    | Related<br>time  |

|-----------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------------|

| #1        | #2   | If Idle mode comes after an interchirp mode, the bandgap is already running                                                                                                           |            | T_SED            |

| #2        |      | Interchirp Up mode is activated by selecting CSUx + CSCx register depending on the actual channel set (see Channel set up x register 0)                                               |            |                  |

| #2        |      | Host already enabled the blocks required by the PLL:                                                                                                                                  |            |                  |

| #2        |      | FSM sets power mode from CSUx + CSCx                                                                                                                                                  |            |                  |

| #2        |      | FSM sets PACR1.RFILTSEL = 0 <sub>B</sub>                                                                                                                                              |            |                  |

| #2        | #2a  | In the case the memory is powered up after Idle (SFCTL:FIFO_PD_MODE = 2 <sub>D</sub> ) the MADC should be enabled delayed. This can be done by the user by programming CSCI:TR_MADCEN |            | T_MADC_EN        |

| #2a       |      | After T_MADC_EN is over, enable A gets active which gates CSxx_1:MADC_BBCHx_EN                                                                                                        |            |                  |

| #2        | #2b  | To save power there is the option to keep the PLL in reset state and enable the PLL delayed                                                                                           |            | T_PLL_ISOP<br>D  |

| #2b       |      | After T_PLL_ISOPD is over, enable B gets active which gates CSCx:PLL_ISOPD                                                                                                            |            |                  |

| #2        | #3   | The PLL needs some time to initialize the filter settings (see Chirp control register 3)                                                                                              |            | T_INIT0          |

| #3        |      | Enable C gets active which gates following signals: PACR1.RFILTSEL, CSxx_0:VCO_EN, CSxx_0:FDIV_EN, CSCx:ABB_ISOPD, CSCx:RF_ISOPD                                                      |            |                  |

| #3        | #3a  | To save power there is the option to close the feedback loop within the PLL delayed                                                                                                   |            | T_DIVEN          |

| #3a       |      | After T_DIVEN is over, enable D gets active which gates PACR2:TR_DIVEN                                                                                                                |            |                  |

| #3        | #4   | The PLL needs again some time to settle the mode (see Chirp control register 0)                                                                                                       |            | T_INIT1          |

| #4        |      | PLL sends lock signal to FSM                                                                                                                                                          | PLL_lock   |                  |

| #4        |      | FSM triggers ramp start of PLL                                                                                                                                                        | RAMP_START |                  |

| #4        | #5   | PLL needs some settling time before chirp can start. The PLL timer is running in parallel to the FSM timer. T_START will be evaluated during system testing                           |            | T_START<br>(PLL) |

| #5        | #9   | PLL will run the frequency chirp                                                                                                                                                      |            | T_RAMP<br>(PLL)  |

| #4        | #6   | Delay PA enable                                                                                                                                                                       |            | T_PAEN           |

| #6        |      | Active mode starts here                                                                                                                                                               |            |                  |

(table continues...)

## **Datasheet**

3 Shapes, frames and channel set definition

# Table 16 (continued) Transition from idle to interchirp to active to interchirp

| From<br># | To # | Description                                                                                                                       | Signals       | Related<br>time |

|-----------|------|-----------------------------------------------------------------------------------------------------------------------------------|---------------|-----------------|

| #6        |      | PA is enabled (PAON).                                                                                                             | PAON          |                 |

|           |      | Host makes sure that PA is not ON before the chirp starts (>#5)                                                                   |               |                 |

| #6        |      | Baseband reset timer is enabled here based on the CSx:BB_RSTCNT value                                                             |               |                 |

| #6        | #7   | Delay after PA is enabled before the power measurement is started (if activated in CSx)                                           |               | T_PSSTART       |

| #6        | #7   | During this phase, the baseband can settle                                                                                        |               | T_SSTART        |

| #7        |      | MADC is triggered for the active segment (Up)                                                                                     | MADC_TRIG     |                 |

| #7        | #8   | MADC starts acquiring the given number of samples (PLLx:APU in PLL shape x register 3).                                           |               | T_ACQUx         |

| #8        |      | MADC has completed the acquisition of the expected number of samples                                                              | MADC_<br>DONE |                 |

| #8        |      | PA is disabled (PAOFF) This condition must be reached before #9 The condition is: T_PAEN + T_SSTART + T_ACQUx > T_START + T_RAMPx | PAOFF         |                 |

| #8        |      | Interchirp up mode is activated again here (CSUx + CSCx)                                                                          |               |                 |

| #9        |      | PLL has completed the up-chirp                                                                                                    |               |                 |

| #9        | #10  | Programmable delay time (e.g. 3 μs)                                                                                               |               | T_END           |

| #10       |      | Ramp completed                                                                                                                    | RAMP_DONE     |                 |

| #10       | #11  | Programmable delay time (e.g. 1 μs)                                                                                               |               | T_EDU           |

| #11       |      | Interchirp up mode ends here                                                                                                      |               |                 |

| #11       |      | Interchirp down mode is programmed here                                                                                           |               |                 |

3 Shapes, frames and channel set definition

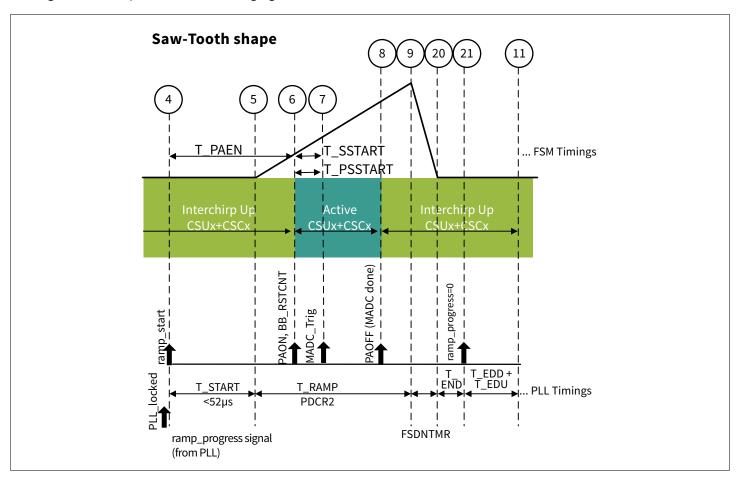

## 3.3.4 Saw-tooth shape timing

In the saw-tooth mode, after a normal upchirp segment there will be a fast ramp down segment. The saw-tooth shape should be enabled in the bitfield PACR2:FSTDNEN (see PLL analog control register 2). For the sawtooth only CSU (Upchirp) is used (see Channel set up x register 0). The time T\_EDU (see PLL shape x register 2, PLLx2#) is applied after the segment is completed. See following figure.

Figure 14 Saw-tooth shape timing

## 3.3.5 Different power modes after shapes and shape groups

After the downchirp shape, the chip can enter different power modes based on the settings (PLLx, CSx, CSCx):

- Interchirp mode in-between shapes for fast chirp repetitions

- Idle mode after shape groups in case of longer delay between shape groups and max power saving is required

- Deep sleep + idle mode after shape groups in case if very long delays are expected

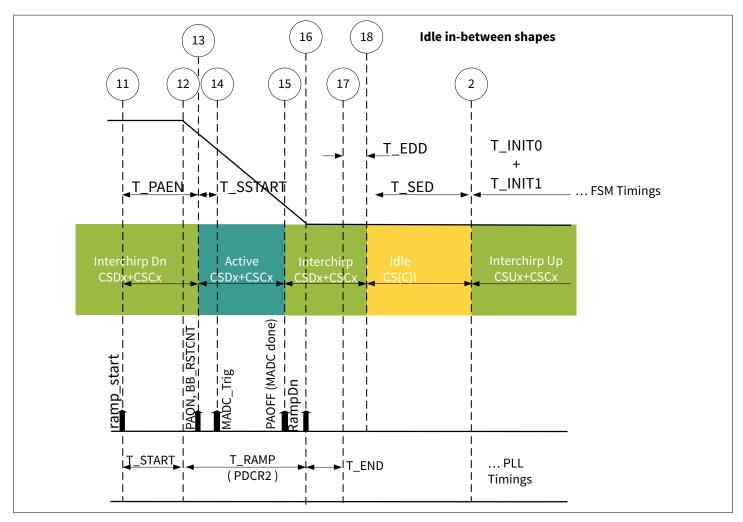

## 3.3.5.1 Idle after shape or shape groups

The idle mode after a shape or shape groups can be set when a long time in low power mode between shapes is required. The following figure represents a time behavior continuation of what is presented in Figure 13.

### **Datasheet**

3 Shapes, frames and channel set definition

Figure 15 Idle mode after shape groups

Table 17 End of shape and interchirp in-between shapes

| From<br># | To #   | Description                                                                       | Signals    | Related time |

|-----------|--------|-----------------------------------------------------------------------------------|------------|--------------|

| #11       |        | Interchirp Dn mode is programmed here (CSDx + CSCx)                               |            |              |

| #11       |        | FSM generates ramp_start signal                                                   | Ramp_start |              |

| PLL re    | ated:  |                                                                                   |            |              |

| #11       | #12    | Preparation for downchirp                                                         |            | T_START      |

| #12       | #16    | downchirp time                                                                    |            | T_RAMP       |

| #16       | #17    | Some delay after downchirp is completed                                           |            | T_END        |

| FSM re    | lated: |                                                                                   |            |              |

| #11       | #13    | Some delay (see above T_PAEN)                                                     |            | T_PAEN       |

| #13       |        | Active mode is entered with settings from previous interchirp Dn mode (CSDx+CSCx) |            |              |

| #13       |        | PA is enabled (PAON)                                                              | PAON       |              |

|           |        | Host makes sure that PA is not on before the chirp starts (>#12)                  |            |              |

(table continues...)

### **Datasheet**

3 Shapes, frames and channel set definition

Table 17 (continued) End of shape and interchirp in-between shapes

| From<br># | To # | Description                                                                                                                         | Signals       | Related time |

|-----------|------|-------------------------------------------------------------------------------------------------------------------------------------|---------------|--------------|

| #13       |      | Baseband reset timer is enabled here based on the CSx:BB_RSTCNT value                                                               |               |              |

| #13       | #14  | During this phase, the baseband can settle                                                                                          |               | T_SSTART     |

| #14       | #15  | MADC starts acquiring the given number of samples (PLLx:APD in PLL shape x register 3).                                             | MADC_TRIG     | T_ACQDx      |

| #15       |      | MADC has completed the acquisition of the expected number of samples                                                                | MADC_<br>DONE |              |

| #15       |      | PA is disabled (PAOFF) This condition must be reached before #16 The condition is: T_PAEN + T_SSTART + T_ACQDx > T_START + T_RAMPx. | PAOFF         |              |

| #15       |      | Interchirp Dn mode is activated again here (CSDx + CSCx)                                                                            |               |              |

| #14       | #16  | FSM waits for PLL if ramp down to calculate #17 (TMREND)                                                                            |               |              |

| #16       |      | PLL signals the end of the downchirp (ramp progress)                                                                                | RampDN        |              |

| #17       |      | Temperature measurement is started (if activated in CSx).                                                                           |               |              |

| #17       | #18  | Time delay programmed by the host                                                                                                   |               | T_EDD        |

| #18       | #2   | Time programmed by the host to stay in Idle mode                                                                                    |               | T_SED        |

| #2        |      | Same state #2 as in Figure 13 starts here                                                                                           |               |              |

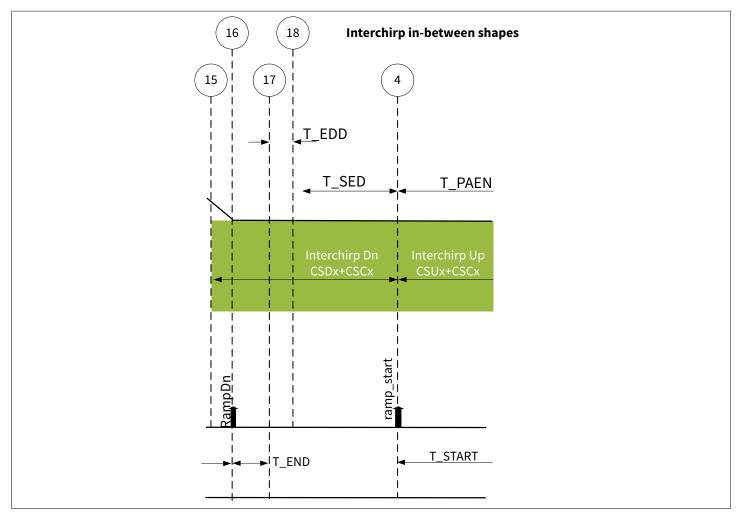

# 3.3.5.2 Interchirp in-between shapes

Interchirp between shapes can be set when the required gap between two shapes is relatively small (< 25  $\mu$ s).

### **Datasheet**

3 Shapes, frames and channel set definition

Figure 16 Interchirp in-between shapes

Table 18 Interchirp in-between shapes

| From # | To # | Description                                                                                     | Signals | Related time |

|--------|------|-------------------------------------------------------------------------------------------------|---------|--------------|

| #15    |      | Interchirp Dn (CSDx + CSCx) is activated after active mode                                      |         |              |

| #16    |      | PLL signals the end of the downchirp (ramp progress)                                            | RampDN  |              |

| #16    | #17  | Some delay after downchirp is completed                                                         |         | T_END        |

| #17    |      | PLL has completed its action                                                                    |         |              |

| #17    |      | Temperature measurement is started (if activated in CSx).                                       |         |              |

| #17    | #18  | Time delay programmed by the host                                                               |         | T_EDD        |

| #18    | #4   | The chip will remain in the same interchirp power state for the provided amount of time (T_EDD) |         | T_SED        |

| #4     |      | Same state #4 as in Figure 13 starts here                                                       |         |              |

| #4     |      | Interchirp up mode programed by FSM here (CSUx + CSCx)                                          |         |              |

## 3 Shapes, frames and channel set definition

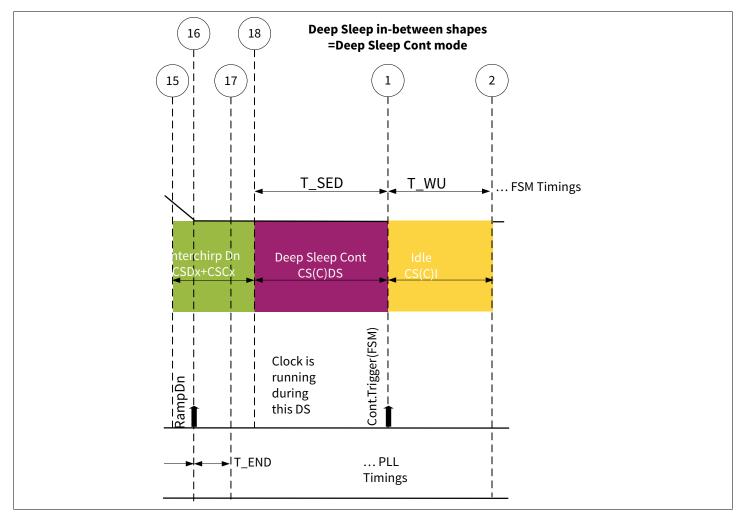

# 3.3.5.3 Deep sleep continuous + idle wake-up after shape groups

In deep sleep cont(inuous) mode after the shape group is completed, the FSM wakes up automatically after the programed time T\_SED. The internal clock is kept running during this time. Deep sleep cont is the only deep sleep power mode possible between shape groups.

Figure 17 Deep sleep + idle wake-up after shape groups

### Table 19 Deep sleep cont + idle wake-up after shape groups

| From # | To # | Description                                                                                                                                           | Signals | Related time |

|--------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------------|

| #16    | #17  | Some delay after downchirp is completed                                                                                                               |         | T_END        |

| #17    |      | PLL is completed its action                                                                                                                           |         |              |

| #17    |      | Temperature measurement is started (if activated in CSx).                                                                                             |         |              |

| #17    |      | Deep sleep cont mode is enabled. The difference to the normal deep sleep mode is, the $f_{\rm SYS\_CLK}$ is kept running to count the internal timers |         |              |

| #17    |      | The internal system clock $f_{ m SYS\_CLK}$ is kept running                                                                                           |         |              |

| #17    | #18  | Time delay programmed by the host                                                                                                                     |         | T_EDD        |

| #18    | #1   | The chip will be in deep sleep cont mode                                                                                                              |         | T_SED        |

30

(table continues...)

## **Datasheet**

3 Shapes, frames and channel set definition

# Table 19 (continued) Deep sleep cont + idle wake-up after shape groups

| From # | To # | Description                                      | Signals | Related time |

|--------|------|--------------------------------------------------|---------|--------------|

| #1     |      | Continuous trigger coming from the FSM           |         |              |

| #1     |      | Same start-up procedure as Figure 13 starts here |         |              |

### **Datasheet**

3 Shapes, frames and channel set definition

# 3.4 System constraints

# 3.4.1 MADC sampling timing conditions and calculations

The number of MADC samples during a frequency chirp (up or down segment of the shape) should fulfill some specific requirements.

Figure 18 T\_RAMP timing conditions

## Table 20 T\_RAMP timing conditions

| From<br># | To # | Description                                                                             | Signals | Related time        |

|-----------|------|-----------------------------------------------------------------------------------------|---------|---------------------|

| #4        |      | PLL starts counting                                                                     |         |                     |

| #4        | #5   | PLL starts                                                                              |         | T_START             |

| #5        | #9   | PLL performs the frequency upchirp, chirp from fstart (PLLx[1]:FSU) to fstop            |         | T_RAMP              |

| #6        | #8   | Active phase                                                                            |         |                     |

| #4        | #7   | Time to start the MADC                                                                  |         | T_PAEN+T_S<br>START |

| #6        | #7   | Delay after PA is enabled before the power measurement is started (if activated in CSx) |         | T_PSSTART           |

| #7        | #8   | MADC sampling time for upchirp raw data                                                 |         | T_ACQUX             |

(table continues...)

### **Datasheet**

3 Shapes, frames and channel set definition

Table 20 (continued) T\_RAMP timing conditions

| From<br># | To # | Description                                                                                         | Signals | Related<br>time |

|-----------|------|-----------------------------------------------------------------------------------------------------|---------|-----------------|

| #8        | #9   | End chirp margin T_ECM is needed to avoid transmission out of band. Empirically derived in system   |         | T_ECM           |

| #5        | #7   | Start chirp margin T_SCM is needed to avoid transmission out of band. Empirically derived in system |         | T_SCM           |

### **Summary:**

ADC sampling rate  $f_{ADC}$  SAMP (see Chapter 8.5.5):

•  $f_{ADC SAMP} = f_{ADC CLK}/ADC_DIV$

ADC acquisition time for Upchirp T\_ACQUx:

•  $T_ACQUx = APUx/f_{ADC\ SAMP}$

Where APU is the number of samples.

End chirp margin T\_ECM is tested in system but assumed to be more than 0 µs:

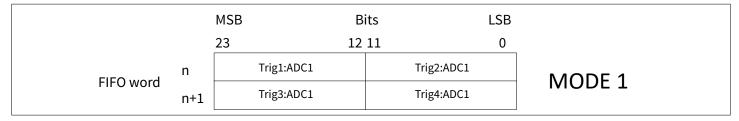

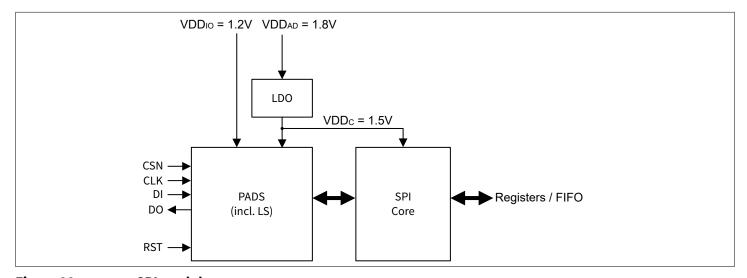

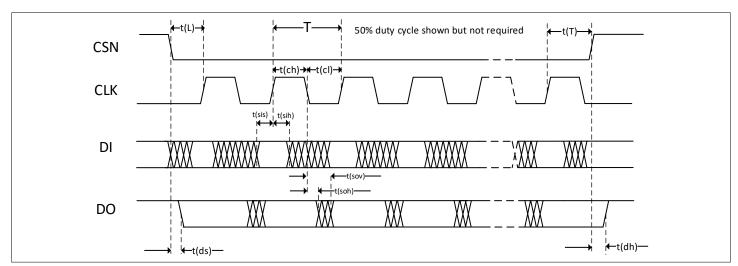

• T\_ECM > 0 μs, T\_SCM > 0 μs