# BC3601 Sub-1GHz FSK/GFSK RF Transceiver

#### **Features**

Frequency band: 315/433/470/868/915MHz

• FSK/GFSK modulation

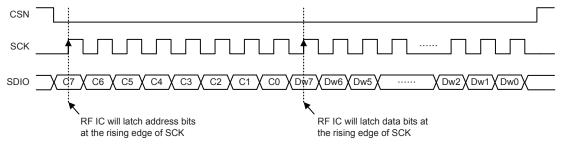

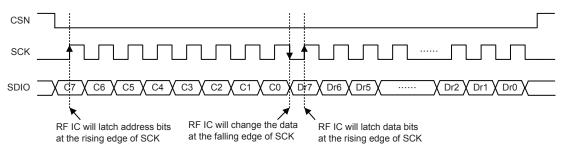

• Supports 3-wire or 4-wire SPI interface

• Low sleep current: 0.5μA

• TX output power: 0dBm~17dBm

• TX current consumption (433MHz): 31mA@10dBm, 54mA@17dBm

• TX current consumption (868MHz): 34.5mA@10dBm, 45mA@13dBm

RX current consumption (AGC off): 13.5mA@433MHz, 14mA@868MHz

On-chip regulator supports input voltage of 2.0V~3.6V

• Programmable data rate: 2Kbps~250Kbps

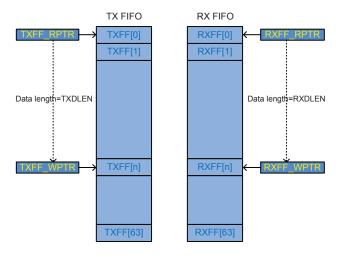

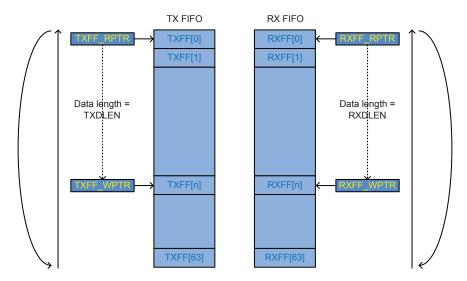

• Physical TX/RX FIFO buffers: TX 64 bytes, RX 64 bytes

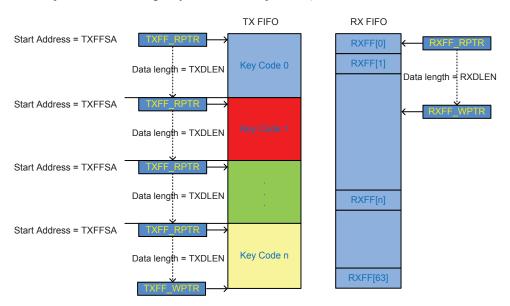

Simple FIFO/Block FIFO/Extend FIFO (up to 255 bytes)/Infinite FIFO modes

• High RX sensitivity (433.92MHz)

• -121dBm at 2Kbps on-air data rate

• -114.5dBm at 10Kbps on-air data rate

• -112dBm at 50Kbps on-air data rate

• -108dBm at 125Kbps on-air data rate

• -105.5dBm at 250Kbps on-air data rate

On-chip VCO and Fractional-N synthesizer with internal loop filter

• Fast PLL synthesizer settling time (35μs)

• On-chip low power RC oscillator for WOR (Wake-on-RX) and WOT (Wake-on-TX) functions

• AFC (Auto Frequency Compensation) for frequency drift due to X'tal aging

• Supports low cost crystal: 16/19.2MHz

On-chip 8-bit RSSI (Received Signal Strength Indicator)

Programmable complex band pass filter bandwidth: 125/200kHz

Digital channel filter for optimum performance at various data rates

· Programmable threshold for carrier detection

Frame synchronization recognition for both FIFO mode and Direct mode

· Packet handling

• FEC (Forward Error Correction)

Data whitening

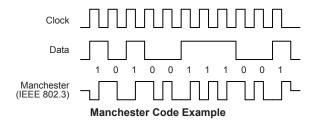

Manchester encoding

CRC-16 checking

• ATR (Auto-Transmit-Receive)

Auto-resend

• Auto-acknowledgment

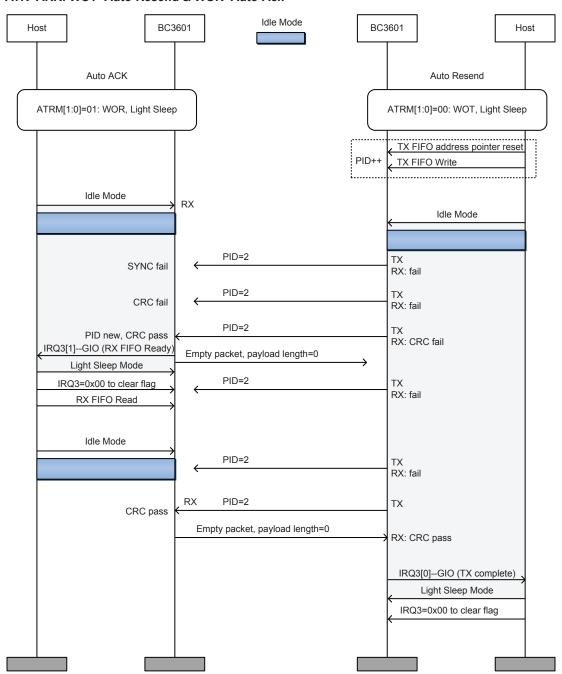

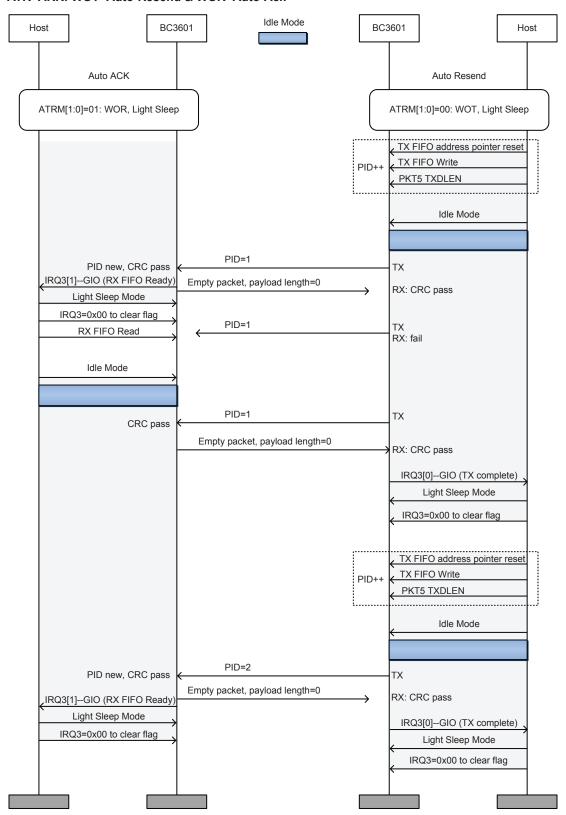

• WOT + Auto-resend

WOR + Auto-acknowledgment

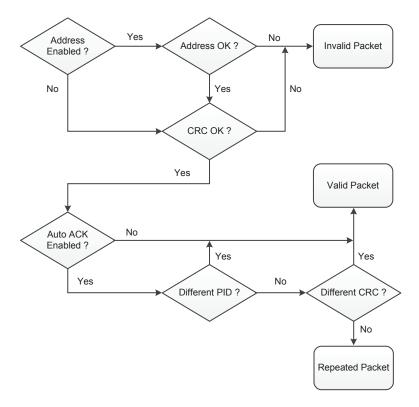

· Packet filtering

· CRC filtering

Address filtering

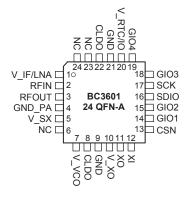

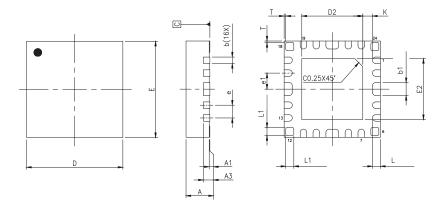

• Package type: 24-pin QFN

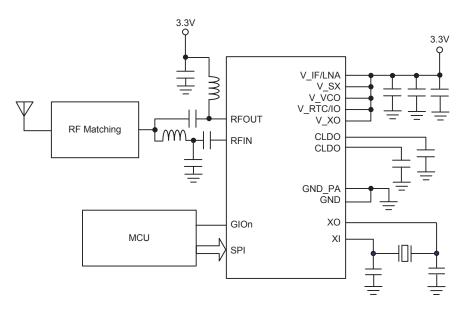

## **General Description**

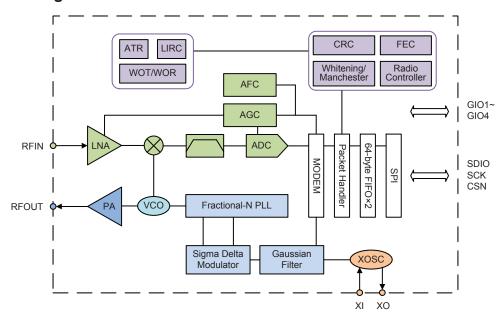

The BC3601 is a high performance and low cost CMOS RF FSK/GFSK transceiver for wireless applications in the 315MHz, 433MHz, 470MHz, 868MHz and 915MHz ISM (Industrial, Scientific and Medical) frequency bands. It incorporates a baseband modem with a programmable data rate from 2Kbps to 250Kbps. Data handling features include 64-byte TX/RX FIFO, packet handling, CRC generation, Forward Error Correction and data whitening, Manshester encoding.

The BC3601 supports short standby settling time, X'tal settling time and on-chip regulator settling time to meet low average power consumption requirements. The integrated high performance 17dBm TX PA and high sensitivity receiver make the device suitable for long range wireless communication.

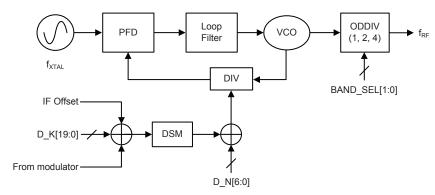

All critical RF function blocks are integrated in the device to minimise the external component requirements. The RF synthesizer contains a VCO (Voltage Controlled Oscillator), an internal loop filter and a low noise fractional-N PLL with high channel frequency resolution. In the RX mode, two IF (Intermedia Frequency)/complex bandpass filter bandwidth combinations are selectable for optimum performance between low and high (≥100K) data rate applications.

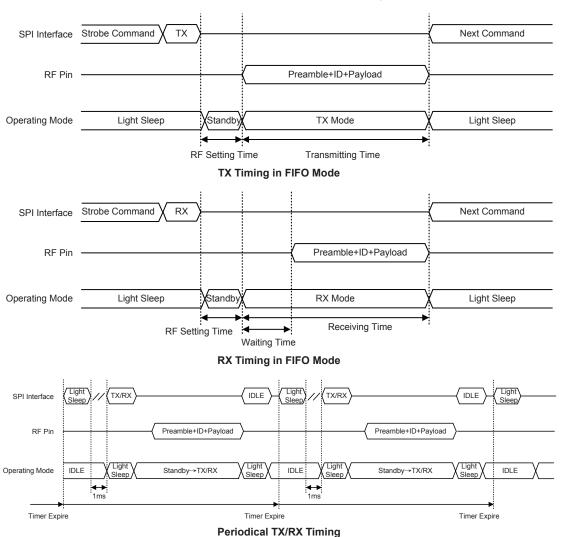

External host MCU can access the BC3601 through a 3-wire or 4-wire SPI interface. The device supports short strobe commands to reduce the loading of the host MCU while maintaining wireless communication link

Additional link layer features like RSSI for channel assessment, auto-acknowledgement and auto-resend, WOT and WOR, etc., facilitate microcontroller based ISM bands wireless link applications.

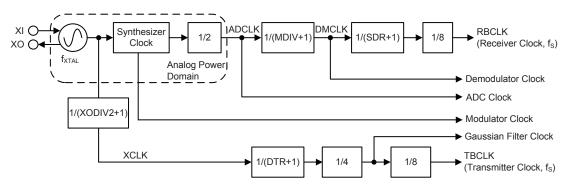

# **Block Diagram**

# **Pin Assignment**

# **Pin Description**

| Pin No. | Pin Name | Туре | Description                                                                                                |  |

|---------|----------|------|------------------------------------------------------------------------------------------------------------|--|

| 1       | V_IF/LNA | PWR  | IF/LNA power input                                                                                         |  |

| 2       | RFIN     | I    | RF input, connected to the matching circuit                                                                |  |

| 3       | RFOUT    | 0    | RF output, connected to the matching circuit (It is recommended to be powered by V <sub>DD</sub> directly) |  |

| 4       | GND_PA   | PWR  | RF PA ground                                                                                               |  |

| 5       | V_SX     | PWR  | Synthesizer power input                                                                                    |  |

| 6       | NC       | _    | Not connected                                                                                              |  |

| 7       | V_VCO    | PWR  | VCO power input                                                                                            |  |

| 8       | CLDO     | PWR  | LDO output                                                                                                 |  |

| 9       | GND      | PWR  | Ground                                                                                                     |  |

| 10      | V_XO     | PWR  | Crystal oscillator supply voltage input                                                                    |  |

| 11      | XO       | 0    | Crystal oscillator output                                                                                  |  |

| 12      | XI       | I    | Crystal oscillator input                                                                                   |  |

| 13      | CSN      | I    | SPI chip select input, low active                                                                          |  |

| 14      | GIO1     | I/O  | Multi-function I/O 1                                                                                       |  |

| 15      | GIO2     | I/O  | Multi-function I/O 2                                                                                       |  |

| 16      | SDIO     | I/O  | SPI data input/output                                                                                      |  |

| 17      | SCK      | I    | SPI clock input                                                                                            |  |

| 18      | GIO3     | I/O  | Multi-function I/O 3                                                                                       |  |

| 19      | GIO4     | I/O  | Multi-function I/O 4                                                                                       |  |

| 20      | V_RTC/IO | PWR  | RTC, digital I/O power input                                                                               |  |

| 21      | GND      | PWR  | Ground                                                                                                     |  |

| 22      | CLDO     | PWR  | LDO output                                                                                                 |  |

| 23      | NC       | _    | Not connected                                                                                              |  |

| 24      | NC       | _    | Not connected                                                                                              |  |

| EP      | GND      | PWR  | Ground                                                                                                     |  |

Legend: I: Digital Input; O: Digital Output; I/O: Digital Input/Output; PWR: Power

The backside plate of EP shall be well soldered to ground on PCB, otherwise it will downgrade RF performance.

# **Absolute Maximum Ratings**

| Supply Voltage $V_{SS}$ -0.3V to $V_{SS}$ +3.6V                          | Operating Temperature40°C to 85°C |

|--------------------------------------------------------------------------|-----------------------------------|

| Voltage on I/O Ports $V_{\text{SS}}0.3V$ to $V_{\text{DD}}\text{+-}0.3V$ | ESD HBM±2kV                       |

| Storage Temperature50°C to 125°C                                         |                                   |

The device is ESD sensitive. HBM (Human Body Mode) is based on MIL-STD-883.

Note: These are stress ratings only. Stresses exceeding the range specified under "Absolute Maximum Ratings" may cause substantial damage to the device. Functional operation of this device at other conditions beyond those listed in the specification is not implied and prolonged exposure to extreme conditions may affect device reliability.

Rev. 1.10 3 May 02, 2018

# **D.C. Characteristics**

Ta=25°C,  $V_{DD}$ =3.3V,  $f_{XTAL}$ =16MHz, FSK modulation with matching circuit and low/high pass filter, RFOUT is powered by  $V_{DD}$  (3.3V), unless otherwise specified

| Parameter                                   | Test Conditions             | Min.                | Тур. | Max.                | Unit |

|---------------------------------------------|-----------------------------|---------------------|------|---------------------|------|

| Operating Temperature                       | _                           | -40                 | _    | 85                  | °C   |

| Supply Voltage                              | _                           | 2                   | 3.3  | 3.6                 | V    |

| Digital I/Os                                |                             |                     |      |                     |      |

| High Level Input Voltage (V <sub>IH</sub> ) | _                           | 0.7×V <sub>DD</sub> | _    | $V_{DD}$            | V    |

| Low Level Input Voltage (V <sub>I</sub> L)  | _                           | 0                   | _    | 0.3×V <sub>DD</sub> | V    |

| High Level Output Voltage (Vон)             | I <sub>OH</sub> =-5mA       | 0.8×V <sub>DD</sub> | -    | V <sub>DD</sub>     | V    |

| Low Level Output Voltage (VoL)              | I <sub>OL</sub> =5mA        | 0                   | _    | 0.2×V <sub>DD</sub> | V    |

| Current Consumption                         |                             |                     |      |                     |      |

|                                             | Deep Sleep mode             | _                   | 0.5  | _                   | μA   |

|                                             | Idle mode (X'tal off)       | _                   | 1.8  | _                   | μΑ   |

|                                             | Light Sleep mode (X'tal on) | _                   | 0.7  | _                   | mA   |

|                                             | Standby mode                | _                   | 5.5  | _                   | mA   |

|                                             | RX mode@2Kbps               | _                   | 13.5 | _                   |      |

|                                             | RX mode@250Kbps             | _                   | 14.5 | _                   |      |

|                                             | TX 0dBM                     | _                   | 19   | _                   |      |

| 315MHz Band Current Consumption             | TX 5dBM                     | _                   | 25.5 | _                   | mA   |

|                                             | TX 10dBM                    | _                   | 33.5 | _                   |      |

|                                             | TX 13dBM                    | _                   | 41   | _                   |      |

|                                             | TX 17dBM                    | _                   | 62   | _                   |      |

|                                             | RX mode@2Kbps               | _                   | 13   | _                   |      |

|                                             | RX mode@250Kbps             | _                   | 13.5 | _                   |      |

|                                             | TX 0dBM                     | _                   | 20   | _                   |      |

| 433MHz Band Current Consumption             | TX 5dBM                     | _                   | 24.5 | _                   | mA   |

|                                             | TX 10dBM                    | _                   | 31   | _                   |      |

|                                             | TX 13dBM                    | _                   | 39   | _                   |      |

|                                             | TX 17dBM                    | _                   | 54   | _                   |      |

|                                             | RX mode@2Kbps               | _                   | 13.5 | _                   |      |

|                                             | RX mode@250Kbps             |                     | 14   |                     |      |

|                                             | TX 0dBM                     | _                   | 20   | _                   |      |

| 868MHz Band Current Consumption             | TX 5dBM                     | _                   | 24.5 | _                   | mA   |

|                                             | TX 10dBM                    | _                   | 34.5 | _                   |      |

|                                             | TX 13dBM                    | _                   | 45   | _                   |      |

|                                             | TX 17dBM                    | _                   | 61.5 | _                   |      |

|                                             | RX mode@2Kbps               | _                   | 13.5 | _                   |      |

|                                             | RX mode@250Kbps             | _                   | 14.5 | _                   |      |

|                                             | TX 0dBM                     | _                   | 21   | _                   |      |

| 915MHz Band Current Consumption             | ion TX 5dBM — 24.5 —        |                     |      |                     | mA   |

|                                             | TX 10dBM                    | _                   | 32   |                     |      |

|                                             | TX 13dBM                    | _                   | 41   |                     |      |

|                                             | TX 17dBM                    |                     | 60.5 | _                   |      |

# A.C. Characteristics

Ta=25°C

| Parameter                                   | Test Conditions                            | Min. | Тур.     | Max. | Unit    |  |

|---------------------------------------------|--------------------------------------------|------|----------|------|---------|--|

| RF Characteristic                           | •                                          | '    |          |      |         |  |

|                                             |                                            | 300  | 315      | 350  |         |  |

| DE Conseille a Fancier De Conseil           |                                            | 390  | 433      | 450  |         |  |

| RF Operating Frequency Range                | _                                          | 470  | _        | 510  | MHz     |  |

|                                             |                                            | 780  | 868      | 930  | 1       |  |

| Phase Locked Loop                           |                                            |      |          |      |         |  |

| X'tal Settling Time                         | Idle to Light Sleep                        | _    | 0.5      | _    | ms      |  |

|                                             | General cases                              | _    | 16       | _    |         |  |

| X'tal Frequency                             | General cases                              | _    | 19.2     | _    | MHz     |  |

|                                             | Data Rate=250Kbps                          | _    | 16       | _    |         |  |

| X'tal ESR                                   | _                                          | _    | _        | 100  | Ω       |  |

| X'tal Capacitor Load (CLOAD)                | _                                          | _    | 20       | _    | pF      |  |

| 315MHz Phase Noise                          | @ 100kHz offset                            | _    | -94      | _    | dBc/Hz  |  |

| 3 ISIMITZ FITASE NOISE                      | @ 1MHz offset                              | _    | -117.5   | _    | UBC/HZ  |  |

| 433MHz Phase Noise                          | @ 100kHz offset                            | _    | -93      | _    | dBc/Hz  |  |

| 433WIIIZ FIIASE NOISE                       | @ 1MHz offset                              | -    | -117.5   | _    | UDC/112 |  |

| 868MHz Phase Noise                          | @ 100kHz offset                            | _    | -88.5    | _    | dBc/Hz  |  |

| obowinz Priase Noise                        | @ 1MHz offset                              | _    | -111.5   | _    | UBC/HZ  |  |

| 915MHz Phase Noise                          | @ 100kHz offset                            | _    | -88.5    | _    | dBc/Hz  |  |

| 9 13 WILL FILASE INCISE                     | @ 1MHz offset                              | _    | -111.5   | _    | UDC/11Z |  |

| Transmitter                                 |                                            |      |          |      |         |  |

| TX Power Range                              | 433MHz band                                | 0    | 13       | 17   | dBm     |  |

| TX Tower Range                              | 868MHz band                                | 0    | 13       | 17   | ubiii   |  |

| TX Settling Time                            | Standby to TX                              | _    | 20       |      | μs      |  |

|                                             | f < 1GHz                                   | _    | _        | -36  |         |  |

|                                             | 47MHz < f < 74MHz                          |      |          |      |         |  |

| TX Spurious Emission                        | 87.5MHz < f < 118MHz                       |      | _        | -54  | dBm     |  |

| (P <sub>OUT</sub> =10dBm, with LPF and HPF) | 174MHz < f < 230MHz                        |      | _        | -04  | ubili   |  |

|                                             | 470MHz < f < 790MHz                        |      |          |      |         |  |

|                                             | 2 <sup>nd</sup> , 3 <sup>rd</sup> Harmonic | -    | —        | -30  |         |  |

| Receiver                                    |                                            |      |          |      |         |  |

| RX Settling Time                            | Standby to RX                              | _    | 40       | _    | μs      |  |

| TOX Octaining Time                          | Deep Sleep to RX, @ 16MHz X'tal            | -    | 450      |      | μs      |  |

|                                             | 2Kbps (f <sub>dev</sub> =8kHz)             |      | -121     |      |         |  |

| 24 FM II DV Canaith it. @                   | 10Kbps (f <sub>dev</sub> =40kHz)           |      | -114.5   |      |         |  |

| 315MHz RX Sensitivity @ BER=0.1%            | 50Kbps (f <sub>dev</sub> =18.75kHz)        | _    | -112     | _    | dBm     |  |

| BEIX 0.170                                  | 125Kbps (f <sub>dev</sub> =46.875kHz)      | _    | — -108 — |      | ]       |  |

|                                             | 250Kbps (f <sub>dev</sub> =93.75kHz)       | -    | -105.5   | _    |         |  |

|                                             | 2Kbps (f <sub>dev</sub> =8kHz)             | _    | -121     | _    |         |  |

| 400441 5740                                 | 10Kbps (f <sub>dev</sub> =40kHz)           | _    | -114.5   | _    |         |  |

| 433MHz RX Sensitivity @ BER=0.1%            | 50Kbps (f <sub>dev</sub> =18.75kHz)        |      | -112     | _    | dBm     |  |

| DEN-0.170                                   | 125Kbps (f <sub>dev</sub> =46.875kHz)      | T —  | -108     | _    |         |  |

|                                             | 250Kbps (f <sub>dev</sub> =93.75kHz)       | _    | -105.5   | _    | 1       |  |

| Parameter                        | Test Conditions                       | Min. | Тур.   | Max. | Unit  |

|----------------------------------|---------------------------------------|------|--------|------|-------|

|                                  | 2Kbps (f <sub>dev</sub> =8kHz)        | _    | -121   | _    |       |

| COOM I - DV O - reithit A        | 10Kbps (f <sub>dev</sub> =40kHz)      | _    | -114   | _    |       |

| 868MHz RX Sensitivity @ BER=0.1% | 50Kbps (f <sub>dev</sub> =18.75kHz)   | _    | -111   | _    | dBm   |

| BER 6.170                        | 125Kbps (f <sub>dev</sub> =46.875kHz) | _    | -107.5 | _    |       |

|                                  | 250Kbps (f <sub>dev</sub> =93.75kHz)  | _    | -105   | _    |       |

|                                  | 2Kbps (f <sub>dev</sub> =8kHz)        | _    | -121   | _    |       |

| 0.451411 DV 0                    | 10Kbps (f <sub>dev</sub> =40kHz)      |      | -114   |      |       |

| 915MHz RX Sensitivity @ BER=0.1% | 50Kbps (f <sub>dev</sub> =18.75kHz)   | _    | -111   | _    | dBm   |

| BER 6.170                        | 125Kbps (f <sub>dev</sub> =46.875kHz) | _    | -107.5 | _    |       |

|                                  | 250Kbps (f <sub>dev</sub> =93.75kHz)  | _    | -105   | _    |       |

| Image Rejection                  | _                                     | _    | 25     | _    | dB    |

| DV Caurious                      | 25MHz~1GHz                            | _    | _      | -57  | dBm   |

| RX Spurious                      | Above 1GHz                            | _    | _      | -47  | UBIII |

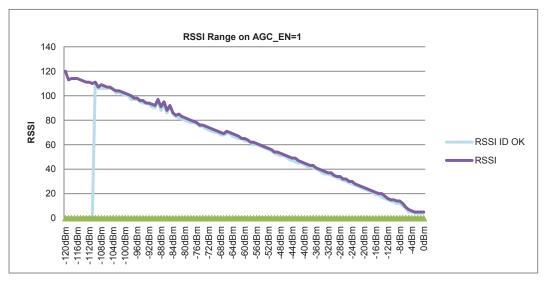

| RSSI Range                       | AGC on                                | -110 | _      | -10  | dBm   |

| Maxmum Operation Input Power     | @ RF input (BER=0.1%)                 | _    | _      | 10   | dBm   |

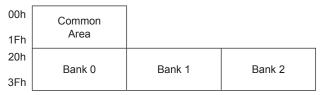

# **Memory Mepping**

Comman Area: It contains 32 bytes space. Accessing addresses 00h~1Fh always means to access the Common Area regardless of Bank Pointer configuration.

Bank 0~2: Each bank contains 32 bytes space. They are selected by the Bank Pointer.

The Bank Pointer, BANK[1:0], which is defined in the Common Area, can be set directly by the Set Register Bank command and read/written by the Control Register command.

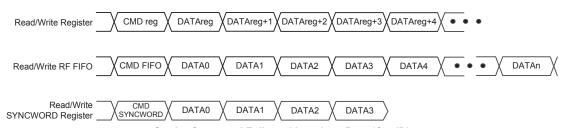

#### **Control Register Access**

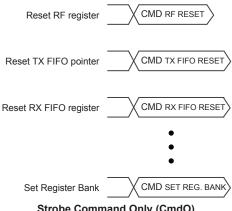

Strobe Command Followed by n-byte Data (CmdD)

Rev. 1.10 6 May 02, 2018

## Strobe Command Only (CmdO)

# **SFR Mapping and Bit Definition**

## **Command Area Control Register**

All control registers will be set to their initial value by power-on reset (POR). The software reset will set the control registers to their initial value except the FSYCK EN, FSYCK DIV[1:0], PWRON, GIO1S[2:0], GIO2S[2:0], PADDS[1:0], GIO3S[3:0], GIO4S[3:0], GIOPU[5:0], SPIPU, SDO\_TEN bits in the RC1, IO1, IO2 and IO3 registers. These bits keep unchanged after software reset.

| Addr. | Name  |                      |                      |                                   | Bit          |                  |          |              |         |

|-------|-------|----------------------|----------------------|-----------------------------------|--------------|------------------|----------|--------------|---------|

| Addr. | Name  | 7                    | 6                    | 5                                 | 4            | 3                | 2        | 1            | 0       |

| 00h   | CFG1  | _                    | AGC_EN               | RXCON_EN                          | DIR_EN       | _                | _        | BANK         | [1:0]   |

| 01h   | RC1   | PWRON                | FSYCK_RDY            | XCLK_RDY                          | XCLK_EN      | FSYCK_           | DIV[1:0] | FSYCK_EN     | RST_LL  |

| 02h   | IRQ1  | RXTO                 | RXFFOW               | _                                 | RXCRCF       | RXDE.            | TS[1:0]  | IRQCPOR      | IRQPOR  |

| 03h   | IRQ2  | ARKTFIE              | ATRCTIE              | FIFOLTIE                          | RXERRIE      | RXDETIE CALCMPIE |          | RXCMPIE      | TXCMPIE |

| 04h   | IRQ3  | ARKTFIF              | ATRCTIF              | FIFOLTIF RXERRIF RXDETIF CALCMPIF |              |                  |          | RXCMPIF      | TXCMPIF |

| 06h   | IO1   | PADD                 | S[1:0]               | GIO2S[2:0] GIO1S[2:0]             |              |                  |          |              |         |

| 07h   | IO2   |                      | GIO45                | S[3:0]                            |              |                  | GIO35    | S[3:0]       |         |

| 08h   | IO3   | SDO_TEN              | SPIPU                |                                   |              | GIOPU            | [5:0]    |              |         |

| 09h   | FIFO1 | _                    | _                    |                                   |              | TXFFSA           | N[5:0]   |              |         |

| 0Ah   | FIFO2 | _                    | _                    | _                                 | RXPL2F_EN    | FFINF_EN         | FFMG_EN  | FFMG         | [1:0]   |

| 0Bh   | PKT1  |                      |                      |                                   | TXPMLEN      | [7:0]            |          |              |         |

| 0Ch   | PKT2  | PID[1:0]             |                      | — SYNCLEN[1:0] RXPMLEN[1          |              |                  |          | EN[1:0]      |         |

| 0Dh   | PKT3  | MCH_EN               | FEC_EN               | CRC_EN                            | CRCFMT       | PLLEN_EN         | PLHAC_EN | PLHLEN       | PLH_EN  |

| 0Eh   | PKT4  | WHT_EN               |                      |                                   | W            | /HTSD[6:0]       |          |              |         |

| 0Fh   | PKT5  |                      |                      |                                   | TXDLEN[      | 7:0]             |          |              |         |

| 10h   | PKT6  |                      |                      |                                   | RXDLEN[      | 7:0]             |          |              |         |

| 11h   | PKT7  | RXPII                | D[1:0]               |                                   | DLY_RXS[2:0] |                  | [        | DLY_TXS[2:0] |         |

| 12h   | PKT8  | -                    | _                    |                                   |              | PLHA[            | 5:0]     |              |         |

| 13h   | PKT9  |                      |                      |                                   | PLHEA[7      | ':0]             |          |              |         |

| 14h   | MOD1  |                      |                      |                                   | DTR[7:0      | 0]               |          |              |         |

| 15h   | MOD2  |                      | RXIFOS               | S[11:8]                           |              | DITHE            | R[1:0]   | _            | DTR[8]  |

| 16h   | MOD3  |                      |                      |                                   | RXIFOS[7     | 7:0]             |          |              |         |

| 17h   | DM1   | _                    | _                    |                                   |              | MDIV[            | 5:0]     |              |         |

| 18h   | DM2   | PREAMBLE_<br>CFO_EN1 | PREAMBLE_<br>CFO_EN0 | SDR[5:0]                          |              |                  |          |              |         |

| 19h   | DM3   | CSF_SW_EN            |                      |                                   | FC           | D_MOD[6:0]       |          |              |         |

| 1Ah   | DM4   |                      | THOLE                | D[3:0]                            |              | CFO_DSEL         | CFO_     | OFFSET_EN    | [2:0]   |

| 1Bh   | DM5   |                      |                      | ·                                 | FD_HOLD      | [7:0]            |          |              |         |

7 Rev. 1.10 May 02, 2018

| Addr. | Name | Bit |                   |   |          |      |   |   |   |  |  |  |

|-------|------|-----|-------------------|---|----------|------|---|---|---|--|--|--|

| Addi. | Name | 7   | 6                 | 5 | 4        | 3    | 2 | 1 | 0 |  |  |  |

| 1Ch   | DM6  | _   | PH_DIFF_<br>MOD   |   |          |      |   |   |   |  |  |  |

| 1Dh   | DM7  |     | PH_DIFF_STEP[7:0] |   |          |      |   |   |   |  |  |  |

| 1Eh   | DM8  |     |                   |   | M_RATIO[ | 7:0] |   |   |   |  |  |  |

Note: Addresses 05h and 1Fh which are not listed in this table are reserved for future use, it is suggested not to change their initial values by any methods.

The reset value shown in the following register description tables means the software reset results of strobe command.

## • CFG1: Configuration Control Register 1

| Bit   | 7 | 6      | 5        | 4      | 3 | 2 | 1         | 0 |

|-------|---|--------|----------|--------|---|---|-----------|---|

| Name  | _ | AGC_EN | RXCON_EN | DIR_EN | _ | _ | BANK[1:0] |   |

| R/W   | _ | R/W    | R/W      | R/W    | _ | _ | R/W       |   |

| Reset | 0 | 0      | 0        | 0      | 0 | 0 | 0         | 0 |

Bit 7 Reserved, must be "0"

Bit 6 **AGC\_EN**: AGC enable

0: Disable 1: Enable

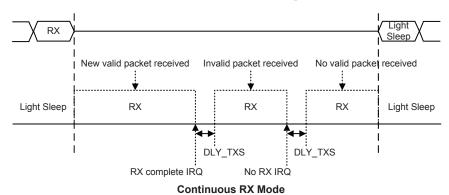

Bit 5 **RXCON\_EN**: RX continue mode enable

0: Disable1: Enable

Note that this bit only affects normal RX mode and ATR RX mode without ARK function.

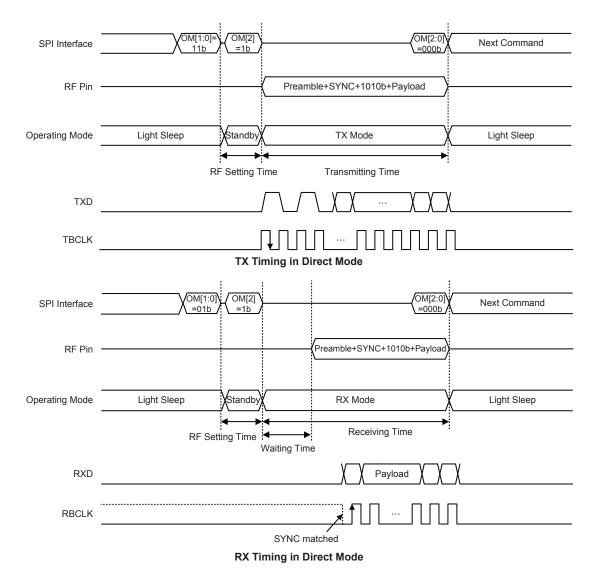

Bit 4 **DIR\_EN**: Direct mode enable

0: TX/RX data from packet handling hardware

1: TX/RX data from/to external MCU directly

Bit 3~2 Reserved, must be "00"

Bit 1~0 BANK[1:0]: Control register bank selection

00: Bank 0 01: Bank 1 10: Bank 2 11: Reserved

This selection can be set by both the Set Register Bank command and Control Register command.

#### • RC1: Reset/Clock Control Register 1

| Bit   | 7     | 6         | 5        | 4       | 3      | 2              | 1 | 0      |

|-------|-------|-----------|----------|---------|--------|----------------|---|--------|

| Name  | PWRON | FSYCK_RDY | XCLK_RDY | XCLK_EN | FSYCK_ | FSYCK_DIV[1:0] |   | RST_LL |

| R/W   | R/W   | R         | R        | R/W     | R/     | R/W            |   | R/W    |

| POR   | 1     | _         | _        | _       | 0      | 0              | 0 | _      |

| Reset | _     | 0         | 0        | 1       | _      | _              | _ | 0      |

#### Bit 7 **PWRON**: 3.3V power on flag

This bit is only set to 1 by power on reset and not affected by software reset of strobe command. After being set high, this bit should be cleared by software. The firmware can check this flag status and determine whether to execute auto calibration in the Light Sleep mode.

## Bit 6 FSYCK\_RDY: FSYCK clock ready flag (ready only)

0: Not ready

1: Ready

This bit is used to indicate that whether the FSYCK clock is ready for operation. This bit will be automatically cleared when FSYCK\_EN=0, when power on reset occurs or when a Deep Sleep command or an Idle command is received.

#### Bit 5 XCLK\_RDY: XCLK clock ready flag (ready only)

0: Not ready

1: Ready

This bit is used to indicate whether the XCLK debounce counter is full and XCLK is ready for operation. Note that when exiting the Deep Sleep state, this flag may need a certain period before being set high. This bit will be automatically cleared to zero when XCLK\_EN=0, when RST\_LL=1, when power on reset or when a software reset command, a Deep Sleep command or an Idle command is received.

#### Bit 4 XCLK\_EN: XCLK clock enable

0: Disable

1: Enable

Setting this bit high will enable the XCLK path to the baseband block while clearing this bit to zero can save power if required. The XCLK clock should be enabled when writing data to the FIFO.

## Bit 3~2 FSYCK\_DIV[1:0]: FSYCK clock (XCLK division) selection

00: 1/1 XCLK

01: 1/2 XCLK

10: 1/4 XCLK

11: 1/8 XCLK

## Bit 1 FSYCK\_EN: FSYCK clock enable

0: Disable

1: Enable

## Bit 0 RST\_LL: Low voltage (1.2V) logic reset control

0: Release reset

1: Reset

#### • IRQ1: Interrupt Control Register 1

| Bit   | 7    | 6      | 5 | 4      | 3           | 2 | 1       | 0      |

|-------|------|--------|---|--------|-------------|---|---------|--------|

| Name  | RXTO | RXFFOW | _ | RXCRCF | RXDETS[1:0] |   | IRQCPOR | IRQPOR |

| R/W   | R    | R      | _ | R      | R/W         |   | R/W     | R/W    |

| Reset | 0    | 0      | 0 | 0      | 1           | 0 | 0       | 1      |

#### Bit 7 **RXTO**: RX time-out flag

0: RX time-out does not occur

1: RX time-out occurs

This flag will be set high by hardware when the RX time-out condition occurs and automatically cleared when a Light Sleep strobe command is received, when the device enters the RX continuous mode, when WOR/WOT wake up occurs or when the device enters the ARK TX/RX mode.

#### Bit 6 **RXFFOW**: RX FIFO overwrite flag

0: RX FIFO overwrite does not occur

1: RX FIFO overwrite occurs

This flag will be set high by hardware when the RX FIFO overwrite condition occurs and automatically cleared when a RX FIFO reset strobe command or a RX strobe command is received.

## Bit 5 Reserved, must be "0"

#### Bit 4 **RXCRCF**: RX CRC failure flag

0: RX CRC failure does not occur

1: RX CRC failure occurs

This flag will be set high by hardware when the RX CRC failure condition occurs and automatically cleared when the RX strobe command is received.

#### Bit 3~2 **RXDETS[1:0]**: RX detect selection

00: Detect carry

01: Detect preamble

1x: Detect SYNCWORD

#### Bit 1 IRQCPOR: IRQ flags clearing polarity selection

0: IRQ flags are cleared by writing 0 to the corresponding bits

1: IRQ flags are cleared by writing 1 to the corresponding bits

#### Bit 0 IRQPOR: IRQ signal polarity selection

0: Active low

1: Active high

When an IRQ flag in the IRQ3 register is set high and the corresponding IRQ function is enabled, then the active level of the IRQ signal is determined by this configuration.

## • IRQ2: Interrupt Control Register 2

| Bit   | 7       | 6       | 5        | 4       | 3       | 2        | 1       | 0       |

|-------|---------|---------|----------|---------|---------|----------|---------|---------|

| Name  | ARKTFIE | ATRCTIE | FIFOLTIE | RXERRIE | RXDETIE | CALCMPIE | RXCMPIE | TXCMPIE |

| R/W   | R/W     | R/W     | R/W      | R/W     | R/W     | R/W      | R/W     | R/W     |

| Reset | 0       | 0       | 0        | 0       | 0       | 0        | 0       | 0       |

Bit 7 ARKTFIE: ARK TX Failure IRQ Enable

0: Disable

1: Enable

Bit 6 ATRCTIE: ATR Cycle Timer IRQ Enable

0: Disable

1: Enable

Bit 5 FIFOLTIE: FIFO Low Threshold IRQ Enable

0: Disable

1: Enable

Bit 4 **RXERRIE**: RX Error IRQ Enable

0: Disable

1: Enable

Bit 3 RXDETIE: RX Event Detected IRQ Enable

0: Disable

1: Enable

Bit 2 CALCMPIE: Calibration Complete IRQ Enable

0: Disable

1: Enable

Bit 1 **RXCMPIE**: RX Complete IRQ Enable

0: Disable

1: Enable

Bit 0 **TXCMPIE**: TX Complete IRQ Enable

0: Disable

1: Enable

### • IRQ3: Interrupt Control Register 3

| Bit   | 7       | 6       | 5        | 4       | 3       | 2        | 1       | 0       |

|-------|---------|---------|----------|---------|---------|----------|---------|---------|

| Name  | ARKTFIF | ATRCTIF | FIFOLTIF | RXERRIF | RXDETIF | CALCMPIF | RXCMPIF | TXCMPIF |

| R/W   | R/W     | R/W     | R/W      | R/W     | R/W     | R/W      | R/W     | R/W     |

| Reset | 0       | 0       | 0        | 0       | 0       | 0        | 0       | 0       |

When the individual flag within this register is set high by the hardware, the corresponding IRQ will be generated. These flags can be cleared by writing 0 or 1 to the corresponding flag which is determined by the IRQCPOR bit configuration.

Bit 7 ARKTFIF: ARK TX Failure IRQ Flag

0: No request

1: Interrupt request

Bit 6 ATRCTIF: ATR Cycle Timer IRQ Flag

0: No request

1: Interrupt request

This flag will be set high when the ATRCT timer is full.

Bit 5 FIFOLTIF: FIFO Low Threshold IRQ Flag

0: No request

1: Interrupt request

When in the Burst TX mode, if this flag is set high, it means that TX FIFO data length is less than FFMG setting threshold and there are TX data to be written into the FIFO. When in the Burst RX mode, if this flag is set high, it means that RX FIFO remaining space is less than FFMG setting threshold and the remaining RX data length is longer than FFMG setting threshold.

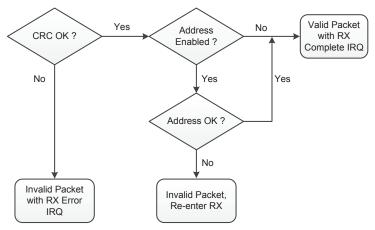

Bit 4 RXERRIF: RX Error IRQ Flag

0: No request

1: Interrupt request

The RX error conditions include CRC failure (CRC EN=1) or RX FIFO overwrite.

Bit 3 **RXDETIF**: RX Event Detected IRQ Flag

0: No request

1: Interrupt request

The RX events include carry, preamble and syncword and the actual trigger source is determined by the RXDETS[1:0] configuration.

Bit 2 CALCMPIF: Calibration Complete IRQ Flag

0: No request

1: Interrupt request

If ACAL\_EN=0, the LIRC calibration is enabled by its individual calibration enable bit and the calibration completion will trigger IRQ. If ACAL\_EN=1, VCO and RC calibrations are enabled and both completion will trigger IRQ.

Bit 1 RXCMPIF: RX Complete IRQ Flag

0: No request

1: Interrupt request

When the RX operation is completed without any error, this flag will be set high by hardware.

Bit 0 **TXCMPIF**: TX Complete IRQ Flag

0: No request

1: Interrupt request

## • IO1: I/O Control Register 1

| Bit  | 7    | 6      | 5                     | 4   | 3 | 2   | 1 | 0 |

|------|------|--------|-----------------------|-----|---|-----|---|---|

| Name | PADD | S[1:0] | GIO2S[2:0] GIO1S[2:0] |     |   |     |   |   |

| R/W  | R/   | W      |                       | R/W |   | R/W |   |   |

| POR  | 0    | 1      | 0                     | 0   | 0 | 0   | 0 | 0 |

Bit 7~6 **PADDS[1:0]**: PAD driving strength selection (only reset by POR)

00: 0.5mA 01: 1mA 10: 5mA 11: 10mA

Bit 5~3 GIO2S[2:0]: GIO2 pin function selection (only reset by POR)

000/111: No function, input

001: SDO, 4-wire SPI data, output

010: TRXD, direct mode TXD/RXD, input/output

011: TXD, direct mode TXD, input 100: RXD, direct mode RXD, output 101: IRQ, interrupt request, output 110: ROSCi, ATR clock external input

Bit 2~0 GIO1S[2:0]: GIO1 pin function selection (only reset by POR)

000/111: No function, input

001: SDO, 4-wire SPI data, output

010: TRXD, direct mode TXD/RXD, input/output

011: TXD, direct mode TXD, intput 100: RXD, direct mode RXD, output 101: IRQ, interrupt request, output 110: ROSCi, ATR clock external input

### • IO2: I/O Control Register 2

| Bit  | 7          | 6   | 5 | 4 | 3 | 2    | 1      | 0 |

|------|------------|-----|---|---|---|------|--------|---|

| Name | GIO4S[3:0] |     |   |   |   | GIO3 | S[3:0] |   |

| R/W  |            | R/W |   |   |   | R/   | W      |   |

| POR  | 0          | 0   | 0 | 0 | 0 | 0    | 0      | 0 |

Bit 7~4 GIO4S[3:0]: GIO4 pin function selection (only reset by POR)

0000/0111/1111: No function, input 0001: SDO, 4-wire SPI data, output

0010: TRXD, direct mode TXD/RXD, input/output

0011: TXD, direct mode TXD, input 0100: RXD, direct mode RXD, output 0101: IRQ, interrupt request, output 0110: ROSCi, ATR clock external input 1000: TBCLK, TX bit (data) clock, output

1001: RBCLK, RX bit (recovery) clock, output 1010: FSYCK, i.e. XCLK 1/1, 1/2, 1/4, 1/8 output

1011: LIRCCLK, internal LIRC clock with debounce, output

1100: EPA\_EN, external PA enable, output

1101: ELAN EN, external LNA enable, output

1110: TRBCLK, TBCLK in TX mode or RBCLK in RX mode, output

Bit 3~0 GIO3S[3:0]: GIO3 pin function selection (only reset by POR)

0000/0111/1111: No function, input

0001: SDO, 4-wire SPI data, output

0010: TRXD, direct mode TXD/RXD, input/output

0011: TXD, direct mode TXD, input

0100: RXD, direct mode RXD, output

0101: IRQ, interrupt request, output

0110: ROSCi, ATR clock external input

1000: TBCLK, TX bit (data) clock, output

1001: RBCLK, RX bit (recovery) clock, output

1010: FSYCK, i.e. XCLK 1/1, 1/2, 1/4, 1/8 output

1011: LIRCCLK, internal LIRC clock with debounce, output

1100: EPA EN, external PA enable, output

1101: ELAN EN, external LNA enable, output

1110: TRBCLK, TBCLK in TX mode or RBCLK in RX mode, output

## • IO3: I/O Control Register 3

| Bit  | 7       | 6     | 5 | 4 | 3   | 2 | 1 | 0 |

|------|---------|-------|---|---|-----|---|---|---|

| Name | SDO_TEN | SPIPU | _ |   | _   |   |   |   |

| R/W  | R/W     | R/W   | _ |   | R/W |   |   |   |

| POR  | 0       | 1     | 1 | 1 | 1   | 1 | 1 | 1 |

Bit 7 **SDO\_TEN**: SDO tri-state enable (only reset by POR)

0: Disable 1: Enable

Bit 6 SPIPU: 3-wire SPI pull-up enable (only reset by POR)

0: Disable 1: Enable

When this bit is set high, it only controls the pull-up function for the CSN, SCK and SDIO pins. Note that the pull-up function disable of the SDO pin for the 4-wire SPI is configured using the GIOPU[4:1] bits.

Bit 5 Reserved, must be "0"

Bit 4~1 **GIOPU[4:1**]: GIO pin function pull-up enable control (only reset by POR)

These bits control the pull-high function of the GIO4~GIO1 pins respectively.

Bit 0 Reserved, must be "0"

#### • FIFO1: FIFO Control Register 1

| Bit   | 7 | 6 | 5 | 4           | 3 | 2 | 1 | 0 |  |

|-------|---|---|---|-------------|---|---|---|---|--|

| Name  | _ | _ |   | TXFFSA[5:0] |   |   |   |   |  |

| R/W   | _ | _ |   | R/W         |   |   |   |   |  |

| Reset | 0 | 0 | 0 | 0           | 0 | 0 | 0 | 0 |  |

Bit 7~6 Reserved, must be "00"

Bit 5~0 TXFFSA[5:0]: TX FIFO start address, used for Block FIFO mode

#### • FIFO2: FIFO Control Regsiter 2

| Bit   | 7 | 6 | 5 | 4         | 3        | 2       | 1    | 0      |

|-------|---|---|---|-----------|----------|---------|------|--------|

| Name  | _ | _ | _ | RXPL2F_EN | FFINF_EN | FFMG_EN | FFMC | G[1:0] |

| R/W   | _ | _ | _ | R/W       | R/W      | R/W     | R/   | W      |

| Reset | 0 | 0 | 0 | 0         | 0        | 0       | 0    | 1      |

Bit 7~5 Reserved, must be "000"

Bit 4 **RXPL2F\_EN**: RX payload length byte to FIFO enable

0: Disable 1: Enable

Setting this bit high will place the payload length byte in the packet to RX FIFO. In the RX continue mode (RXCON\_EN=1), this bit should be set to 1 to support multiple payload in single RX FIFO.

Bit 3 **FFINF\_EN**: FIFO infinite length mode enable

0: Disable 1: Enable

Bit 2 **FFMG\_EN**: FIFO length margin detect enable

0: Disable 1: Enable

Bit 1~0 **FFMG[1:0**]: FIFO length margin selection

Threshold of remaining data in TX FIFO:

00: 4 bytes01: 8 bytes10: 16 bytes11: 32 bytes

Threshold of remaining space in RX FIFO:

00: 4 bytes 01: 8 bytes 10: 16 bytes 11: 32 bytes

After the FIFO length margin detect function has been enabled by setting the FFMG\_EN bit high and the required FIFO length margin has been selected by setting these bits, when the selected condition occurs the FIFOLTIF flag will be set high. In this case, an interrupt signal will also be gemerated if the corresponding interrrpt function has been enabled.

## PKT1: Packet Control Register 1

| Bit   | 7 | 6            | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|---|--------------|---|---|---|---|---|---|--|--|

| Name  |   | TXPMLEN[7:0] |   |   |   |   |   |   |  |  |

| R/W   |   | R/W          |   |   |   |   |   |   |  |  |

| Reset | 0 | 0            | 0 | 0 | 0 | 0 | 0 | 1 |  |  |

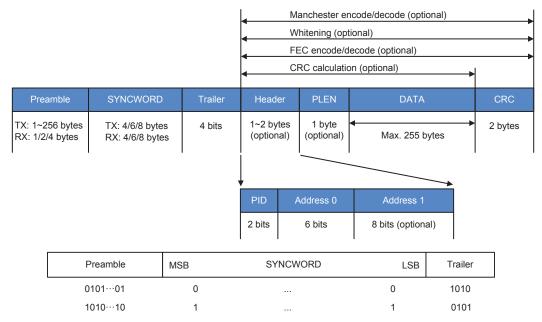

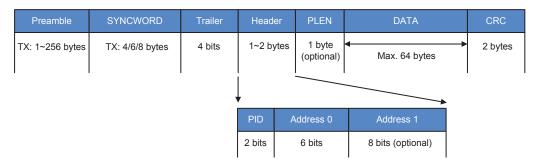

Bit 7~0 **TXPMLEN[7:0]**: TX preamble length

Transmit preamble length=(TXPMLEN[7:0]+1) bytes

### • PKT2: Packet Control Register 2

| Bit   | 7   | 6     | 5 | 4 | 3     | 2       | 1            | 0 |

|-------|-----|-------|---|---|-------|---------|--------------|---|

| Name  | PID | [1:0] | _ | _ | SYNCL | EN[1:0] | RXPMLEN[1:0] |   |

| R/W   | R/  | W     | _ | _ | R/    | W       | R/           | W |

| Reset | 0   | 0     | 0 | 0 | 0     | 1       | 1            | 0 |

Bit 7~6 **PID[1:0]**: Packet ID

This ID will be placed in the highest two bits of the payload header field when the header option is enabled using the PLH EN bits.

Bit 5~4 Reserved, must be "00"

Bit 3~2 **SYNCLEN[1:0]**: TX/RX mode SYNCWORD length selection

00: Reserved

01: 4 bytes

10: 6 bytes

11: 8 bytes

Bit 1~0 **RXPMLEN[1:0]**: RX preamble detection length selection

00: 0 byte - no preamble detection

01: 1 byte

10: 2 bytes

11: 4 bytes

## • PKT3: Packet Control Register 3

| Bit   | 7      | 6      | 5      | 4      | 3        | 2        | 1      | 0      |

|-------|--------|--------|--------|--------|----------|----------|--------|--------|

| Name  | MCH_EN | FEC_EN | CRC_EN | CRCFMT | PLLEN_EN | PLHAC_EN | PLHLEN | PLH_EN |

| R/W   | R/W    | R/W    | R/W    | R/W    | R/W      | R/W      | R/W    | R/W    |

| Reset | 0      | 0      | 1      | 0      | 0        | 0        | 0      | 0      |

Bit 7 MCH\_EN: Manchester code enable

0: Disable

1: Enable

Bit 6 **FEC\_EN**: FEC enable

0: Disable

1: Enable

Bit 5 CRC\_EN: CRC field enable

0: Disable

1: Enable

Bit 4 **CRCFMT**: CRC format selection

0: CCITT-16-CRC  $G(X)=X^{16}+X^{12}+X^5+1$

1: IBC-16\_CRC  $G(X)=X^{16}+X^{15}+X^2+1$

Bit 3 **PLLEN\_EN**: Payload length field enable

0: Disable

1: Enable

Bit 2 PLHAC\_EN: Payload header address correction enable control

0: Disable, PLHA[5:0] in the PKT8 register can be used as software flags defined by users

1: Enable, PLHA[5:0] of TX/RX devices must include the same address, otherwise the packet will be regarded as a failed packet.

Bit 1 **PLHLEN**: Payload header length

0: 1 byte 1: 2 bytes

Bit 0 **PLH\_EN**: Payload header field enable

0: Disable1: Enable

## • PKT4: Packet Control Register 4

| Bit   | 7      | 6 | 5          | 4 | 3 | 2 | 1 | 0 |  |

|-------|--------|---|------------|---|---|---|---|---|--|

| Name  | WHT_EN |   | WHTSD[6:0] |   |   |   |   |   |  |

| R/W   | R/W    |   | R/W        |   |   |   |   |   |  |

| Reset | 0      | 0 | 1          | 1 | 0 | 1 | 1 | 0 |  |

Bit 7 WHT\_EN: Data whitening enable

0: Disable 1: Enable

Bit 6~0 WHTSD[6:0]: Data whitening seed

#### • PKT5: Packet Control Register 5

| Bit   | 7 | 6           | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|---|-------------|---|---|---|---|---|---|--|--|

| Name  |   | TXDLEN[7:0] |   |   |   |   |   |   |  |  |

| R/W   |   | R/W         |   |   |   |   |   |   |  |  |

| Reset | 0 | 1           | 0 | 0 | 0 | 0 | 0 | 0 |  |  |

Bit 7~0 **TXDLEN[7:0]**: TX data length (unit: byte, used in burst mode only)

## • PKT6: Packet Control Register 6

| Bit   | 7 | 6           | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|---|-------------|---|---|---|---|---|---|--|--|

| Name  |   | RXDLEN[7:0] |   |   |   |   |   |   |  |  |

| R/W   |   | R/W         |   |   |   |   |   |   |  |  |

| Reset | 0 | 1           | 0 | 0 | 0 | 0 | 0 | 0 |  |  |

Bit 7~0 **RXDLEN[7:0]**: RX data length (unit: byte; used in burst mode only)

When the PLLEN EN bit is cleared to 0, the received data length is determined by this field.

When this register is read, the read value indicates the RX data length in FIFO. The default read value is 00h.

## • PKT7: Packet Control Register 7

| Bit   | 7     | 6      | 5            | 4 | 3 | 2 | 1           | 0                 |  |  |

|-------|-------|--------|--------------|---|---|---|-------------|-------------------|--|--|

| Name  | RXPII | D[1:0] | DLY_RXS[2:0] |   |   | [ | DLY_TXS[2:0 | Y_TXS[2:0]<br>R/W |  |  |

| R/W   | F     | ₹      | R/W          |   |   |   | R/W         |                   |  |  |

| Reset | 0     | 0      | 1            | 0 | 0 | 0 | 0           | 0                 |  |  |

Bit 7~6 **RXPID[1:0]**: Received packet PID (read only)

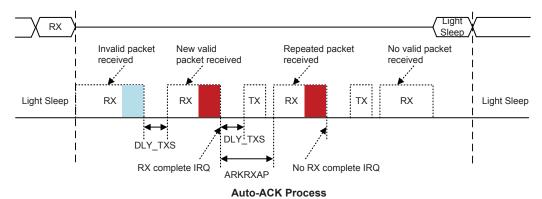

Bit 5~3 **DLY\_RXS[2:0]**: RX block stable time after RX is enabled

000: 4μs 001: 8μs 010: 12μs 011: 16μs 100: 20μs

101: 32μs 110: 64μs 111: 100μs

These bits are used to select the waiting time between RX enable and RX stable. This time should be configured to a value greater than the default RX DCOC turbo mode delay time of 6µs.

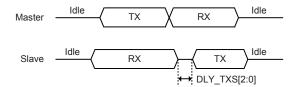

## Bit 2~0 DLY\_TXS[2:0]: TX start (delay) time before entering the TX mode

000: 0μs 001: 10μs 010: 20μs 011: 40μs 100: 60μs 101: 80μs 110: 100μs 111: 120μs

It is used to align the timing between transmitter and receiver in ARK mode.

#### • PKT8: Packet Control Register 8

| Bit   | 7 | 6 | 5         | 4   | 3 | 2 | 1 | 0 |

|-------|---|---|-----------|-----|---|---|---|---|

| Name  | _ | _ | PLHA[5:0] |     |   |   |   |   |

| R/W   | _ | _ |           | R/W |   |   |   |   |

| Reset | 0 | 0 | 0         | 0   | 0 | 0 | 0 | 0 |

Bit 7~6 Reserved, must be "00"

## Bit 5~0 PLHA[5:0]: Payload header address to support broadcast

Address=0 in RX mode means not doing correction check.

Write: write data to TX PLHA[5:0]. Read: read data from RX PLHA[5:0].

## • PKT9: Packet Control Register 9

| Bit   | 7 | 6          | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|---|------------|---|---|---|---|---|---|--|

| Name  |   | PLHEA[7:0] |   |   |   |   |   |   |  |

| R/W   |   | R/W        |   |   |   |   |   |   |  |

| Reset | 0 | 0          | 0 | 0 | 0 | 0 | 0 | 0 |  |

#### Bit 7~0 PLHEA[7:0]: Payload header extended address to support broadcast

Address=0 means not doing correction check.

Write: write data to TX PLHEA[7:0]. Read: read data from RX PLHEA[7:0].

## • MOD1: Modulator Control Register 1

| Bit   | 7 | 6        | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|---|----------|---|---|---|---|---|---|

| Name  |   | DTR[7:0] |   |   |   |   |   |   |

| R/W   |   | RW       |   |   |   |   |   |   |

| Reset | 0 | 0        | 0 | 0 | 0 | 0 | 0 | 1 |

#### Bit 7~0 **DTR[7:0]**:

DTR[8:0]: Data rate divider, DTR[8] is located in the MOD2 register.

Data Rate={FXTAL/[(XODIV2+1)×32×(DTR[8:0]+1)]}, XODIV2=0, here data rate indicates TBCLK. Note that DTR[8:0] can only be an odd number.

#### • MOD2: Modulator Control Register 2

| Bit   | 7 | 6     | 5       | 4 | 3     | 2      | 1 | 0      |

|-------|---|-------|---------|---|-------|--------|---|--------|

| Name  |   | RXIFO | S[11:8] |   | DITHE | R[1:0] | _ | DTR[8] |

| R/W   |   | R/    | W       |   | R/    | W      | _ | R/W    |

| Reset | 1 | 0     | 0       | 1 | 0     | 0      | 0 | 0      |

#### Bit 7~4 **RXIFOS[11:8]**:

RXIFOS[11:0]: RX intermediate frequency offset, RXIFOS[7:0] is located in the MOD3 register.

Write RXIFOS[11:8] first and then write RXIFOS[7:0] to fully update RXIFOS[11:0].

RXIFOS[11:0]=Floor  $((f_{IF}/f_{XTAL}/(XODIV2+1))\times 2^{17})$

#### Bit 3~2 **DITHER[1:0]**: Dither value

Bit 1 Reserved, must be "0"

#### Bit 0 **DTR[8]**:

DTR[8:0]: Data rate divider, DTR[7:0] is loaced in the MOD1 register.

Data Rate= $f_{XTAL}/(XODIV2+1)/32/(DTR[8:0]+1)$ , here data rate indicates TBCLK. Note that DTR[8:0] can only be an odd number.

## • MOD3: Modulator Control Register 3

| Bit   | 7 | 6           | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|---|-------------|---|---|---|---|---|---|

| Name  |   | RXIFOS[7:0] |   |   |   |   |   |   |

| R/W   |   | R/W         |   |   |   |   |   |   |

| Reset | 1 | 0           | 0 | 1 | 1 | 0 | 1 | 0 |

#### Bit 7~0 **RXIFOS[7:0]**:

RXIFOS[11:0]: RX intermediate frequency offset, RXIFOS[11:8] is located in the MOD2 register.

Write RXIFOS[11:8] first and then write RXIFOS[7:0] to fully update RXIFOS[11:0].

RXIFOS[11:0]= Floor  $((f_{IF}/f_{XTAL}/(XODIV2+1))\times 2^{17})$

#### • DM1: Demodulator Control Register 1

| Bit   | 7 | 6 | 5         | 4   | 3 | 2 | 1 | 0 |

|-------|---|---|-----------|-----|---|---|---|---|

| Name  | _ | _ | MDIV[5:0] |     |   |   |   |   |

| R/W   | _ | _ |           | R/W |   |   |   |   |

| Reset | 0 | 0 | 0         | 0   | 0 | 0 | 1 | 1 |

Bit 7~6 Reserved, must be "00"

Bit 5~0 MDIV[5:0]: Demodulator operation clock divider

DMCLK=ADCLK/(MDIV[5:0]+1)

### • DM2: Demodulator Control Register 2

| Bit   | 7                    | 6                    | 5        | 4 | 3 | 2 | 1 | 0 |

|-------|----------------------|----------------------|----------|---|---|---|---|---|

| Name  | PREAMBLE_<br>CFO_EN1 | PREAMBLE_<br>CFO_EN0 | SDR[5:0] |   |   |   |   |   |

| R/W   | R/W                  | R/W                  | R/W      |   |   |   |   |   |

| Reset | 0                    | 1                    | 0        | 0 | 0 | 0 | 0 | 0 |

Bit 7 **PREAMBLE\_CFO\_EN1**: Enable 2<sup>nd</sup> stage CFO correction in preamble

0: Disable1: Enable

Note that this bit can only be set if the preamble length is 4 bytes, i.e, RXPMLEN[1:0]=11b.

Bit 6 **PREAMBLE\_CFO\_EN0**: Enable 1st stage CFO correction in preamble

0: Disable

1: Enable

Bit 5~0 **SDR[5:0]**: Decimator operation clock after phase extract

SDR[5:0]+1=DMCLK/(8×DATA RATE), here DATA RATE indicates RBCLK.

#### • DM3: Demodulator Control Register 3

| Bit   | 7         | 6 | 5           | 4 | 3 | 2 | 1 | 0 |  |

|-------|-----------|---|-------------|---|---|---|---|---|--|

| Name  | CSF_SW_EN |   | FD_MOD[6:0] |   |   |   |   |   |  |

| R/W   | R/W       |   | R/W         |   |   |   |   |   |  |

| Reset | 1         | 1 | 1           | 0 | 0 | 0 | 0 | 0 |  |

Bit 7 CSF\_SW\_EN: Channel selection filter and auto bandwidth switch enable

0: Disable

1: Enable

Bit 6~0 **FD\_MOD[6:0**]: Frequency deviation modifier

FD\_MOD=Round ((h/(SDR[5:0]+1))×128)

h=modulation index

SDR[5:0]+1=DMCLK/(8×DATA RATE)

### • DM4: Demodulator Control Register 4

| Bit   | 7 | 6    | 5      | 4 | 3        | 2    | 1        | 0      |

|-------|---|------|--------|---|----------|------|----------|--------|

| Name  |   | THOL | D[3:0] |   | CFO_DSEL | CFO_ | OFFSET_E | N[2:0] |

| R/W   |   | R/   | W      |   | R/W      |      | R/W      |        |

| Reset | 0 | 0    | 0      | 1 | 1        | 0    | 0        | 0      |

Bit 7~4 **THOLD[3:0]**: Detection errors threshold

THOLD[3:2]: Preamble detection errors bit number threshold

THOLD[1:0]: SYNCWORD detection errors bit number

Bit 3 CFO DSEL: CFO correction domain selection

0: Analog domain

1: Digital domain

Bit 2~0 CFO\_OFFSET\_EN[2:0]: Enable extra CFO offset on the CFO estimate value by the CFO detect hardware

000: No CFO offset, default value

001: Extra 1/16 CFO estimate offset

010: Extra 1/8 CFO\_estimate offset

011: Reserved

100: Extra 1/4 CFO\_estimate offset

101: Reserved110: Reserved111: Reserved

Note that the extra CFO offset is only used for ultra-low data rate ( $\leq 10$ K) cases.

## • DM5: Demodulator Control Register 5

| Bit   | 7 | 6            | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|---|--------------|---|---|---|---|---|---|--|

| Name  |   | FD_HOLD[7:0] |   |   |   |   |   |   |  |

| R/W   |   | R/W          |   |   |   |   |   |   |  |

| Reset | 0 | 0            | 1 | 1 | 0 | 0 | 0 | 0 |  |

Bit 7~0 **FD\_HOLD[7:0]**: Frequency deviation threshold for preamble detection

#### • DM6: Demodulator Control Register 6

| Bit   | 7 | 6               | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|---|-----------------|---|---|---|---|---|---|

| Name  | _ | PH_DIFF_<br>MOD | _ | _ | _ | _ | _ | _ |

| R/W   | _ | R/W             | _ | _ | _ | _ | _ | _ |

| Reset | 0 | 0               | 0 | 0 | 0 | 0 | 0 | 0 |

Bit 7 Reserved, must be "0"

Bit 6 PH\_DIFF\_MOD: Phase difference extract mode setting

0: Phase extract range [-pi/2, pi/2]

1: Phase extract range [-pi, pi]

Bit 5~0 Reserved, must be "000000"

## • DM7: Demodulator Control Register 7

| Bit   | 7 | 6                 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|---|-------------------|---|---|---|---|---|---|--|

| Name  |   | PH_DIFF_STEP[7:0] |   |   |   |   |   |   |  |

| R/W   |   | R/W               |   |   |   |   |   |   |  |

| Reset | 1 | 0                 | 0 | 1 | 1 | 0 | 1 | 0 |  |

Bit 7~0 PH\_DIFF\_STEP[7:0]: Incremental phase step per ADCLK for IF digital clock synthesizer

For different data rates, different ADCLK clocks are used.

If (Data rate < 200K)

Fif=200kHz;

Else Fif=300kHz;

Phase\_diff\_step=round ((Fif×8/Fadclk)×29);

## • DM8: Demodulator Control Register 8

| Bit   | 7 | 6             | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|---|---------------|---|---|---|---|---|---|--|--|

| Name  |   | M_RATIO[7:0]  |   |   |   |   |   |   |  |  |

| R/W   |   | R/W           |   |   |   |   |   |   |  |  |

| Reset | 0 | 0 1 0 0 0 0 0 |   |   |   |   |   |   |  |  |

Bit 7~0 **M\_RATIO[7:0]**: For CFO calulation

$M\_RATIO = round(1/(MDIV + 1) \times 2^8)$

## **Bank 0 Control Registers**

All control registers will be set to their initial value by power-on reset (POR). The software reset will set the control registers to their initial value except the LIRC\_EN, LIRC\_OP[4:0], LIRC\_OW and LIRCCAL\_EN bits in the XO3 register. These bits keep unchanged after software reset.

| A al al a | Name  |                  |                    |          | Bit     |            |        |           |         |  |  |

|-----------|-------|------------------|--------------------|----------|---------|------------|--------|-----------|---------|--|--|

| Addr.     | Name  | 7                | 6                  | 5        | 4       | 3          | 2      | 1         | 0       |  |  |

| 20h       | OM    | PWR_SOFT         | BAND_S             | SEL[1:0] | _       | ACAL_EN    | RTX_EN | RTX_SEL   | SX_EN   |  |  |

| 22h       | SX1   | _                | — D_N[6:0]         |          |         |            |        |           |         |  |  |

| 23h       | SX2   |                  |                    |          | D_K[7   | :0]        |        |           |         |  |  |

| 24h       | SX3   |                  |                    |          | D_K[15  | 5:8]       |        |           |         |  |  |

| 25h       | SX4   | _                | _                  | _        | _       |            | D_K[   | 19:16]    |         |  |  |

| 26h       | STA1  | _                | _                  | _        | CD_FLAG | _          |        | OMST[2:0] |         |  |  |

| 28h       | RSSI2 |                  | _                  |          |         |            | RSSI_C | THD[3:0]  |         |  |  |

| 29h       | RSSI3 |                  | RSSI_NEGDB[7:0]    |          |         |            |        |           |         |  |  |

| 2Ah       | RSSI4 |                  | RSSI_SYNC_OK[7:0]  |          |         |            |        |           |         |  |  |

| 2Bh       | ATR1  | ATRCLK_D         | )IV[1:0]           | ATRCLKS  | ATRTU   | ATRCTM     | ATRI   | M[1:0]    | ATR_EN  |  |  |

| 2Ch       | ATR2  |                  |                    |          | ATRCYC  | [7:0]      |        |           |         |  |  |

| 2Dh       | ATR3  |                  |                    |          | ATRCYC  | [15:8]     |        |           |         |  |  |

| 2Eh       | ATR4  |                  |                    |          | ATRRXA  | P[7:0]     |        |           |         |  |  |

| 2Fh       | ATR5  |                  |                    |          | ATRRXE  | P[7:0]     |        |           |         |  |  |

| 30h       | ATR6  |                  |                    |          | ATRRXEF | P[15:8]    |        |           |         |  |  |

| 31h       | ATR7  |                  | ARKNM              | [3:0]    |         | _          | ATR_W  | DLY[1:0]  | ARK_EN  |  |  |

| 32h       | ATR8  |                  |                    |          | ARKRXA  | P[7:0]     |        |           |         |  |  |

| 33h       | ATR9  |                  |                    |          | ATRCT   |            |        |           |         |  |  |

| 34h       | ATR10 |                  |                    |          | ATRCT[  | 15:8]      |        |           |         |  |  |

| 35h       | ATR11 | — ATRRXAP[9:8]   |                    |          |         |            |        |           |         |  |  |

| 3Ch       | XO1   | — — XO_TRIM[4:0] |                    |          |         |            |        |           |         |  |  |

| 3Dh       | XO2   |                  | XODIV2 XO_SEL[2:0] |          |         |            |        |           |         |  |  |

| 3Eh       | XO3   | LIRCCAL_EN       | LIRC_OW            |          | L       | IRC_OP[4:0 | )]     |           | LIRC_EN |  |  |

| 3Fh       | TX2   |                  |                    |          | CT_PAD  | [7:0]      |        |           |         |  |  |

Note: Addresses 21h, 27h and 36h~3Bh which are not listed in this table are reserved for future use, it is suggested not to change their initial values by any methods.

The reset value shown in the following register description tables means the software reset results of strobe command.

## • OM: Operation Mode Control Register

| Bit   | 7        | 6             | 5   | 4 | 3       | 2      | 1       | 0     |

|-------|----------|---------------|-----|---|---------|--------|---------|-------|

| Name  | PWR_SOFT | BAND_SEL[1:0] |     | _ | ACAL_EN | RTX_EN | RTX_SEL | SX_EN |

| R/W   | R/W      | R/            | R/W |   | R/W     | R/W    | R/W     | R/W   |

| Reset | 0        | 0             | 1   | 0 | 0       | 0      | 0       | 0     |

Bit 7 **PWR\_SOFT**: RF operation mode selection, this bit must be kept as "0"

0: RF normal operation mode

1: Reserved

Bit 6~5 **BAND\_SEL[1:0]**: Band selection (when PWR\_SOFT=0)

00: 315MHz band, ODDIV=4 01: 433MHz band, ODDIV=2

10: 470~510MHz band, ODDIV=2 11: 868/915MHz band, ODDIV=1

Bit 4 Reserved, must be "0"

Bit 3 ACAL\_EN: Auto calibration enable

0: Disable1: Enable

When this bit is set high, both the VCO and RC calibrations will be enabled. When the VCO and RC calibrations are completed, this bit will be cleared to zero by hardware.

Bit 2 **RTX\_EN**: RX or TX mode enable

0: Disable

1: Enable

After the RX or TX mode has been selected by the RTX\_SEL bit, setting this bit high will enable the selected mode.

Bit 1 RTX\_SEL: RX or TX mode selection

0: RX mode

1: TX mode

Bit 0 **SX\_EN**: Synthesizer enable (standby mode enable control)

0: Disable

1: Enable

Setting this bit high will enable the PFD, CP and VCO functions.

## • SX1: Fractional-N Synthesizer Control Register 1

| Bit   | 7 | 6 | 5        | 4 | 3 | 2 | 1 | 0 |  |

|-------|---|---|----------|---|---|---|---|---|--|

| Name  | _ |   | D_N[6:0] |   |   |   |   |   |  |

| R/W   | _ |   | R/W      |   |   |   |   |   |  |

| Reset | 0 | 0 | 1        | 1 | 0 | 1 | 1 | 0 |  |

Bit 7 Reserved, must be "0"

Bit 6~0 **D\_N[6:0]**: RF channel integer number code

D N[6:0]=floor  $(f_{RF} \times ODDIV/f_{XTAL}/(XODIV2+1))$

For example, XO=16MHz and RF band=433.92MHz which are initial setup:

- $\rightarrow$  (433.92MHz×2)/16MHz=54.24

- $\rightarrow$  D N=54

- $\rightarrow$  Dec2Hex(54)=36

- $\rightarrow$  Dec2Bin(54)=011 0110

### • SX2: Fractional-N Synthesizer Control Register 2

| Bit   | 7 | 6        | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|-------|---|----------|---|---|---|---|---|---|--|--|--|

| Name  |   | D_K[7:0] |   |   |   |   |   |   |  |  |  |

| R/W   |   | R/W      |   |   |   |   |   |   |  |  |  |

| Reset | 0 | 0        | 0 | 0 | 1 | 0 | 1 | 0 |  |  |  |

Bit 7~0 **D\_K[7:0]**: RF channel fractional number code lowest byte

### • SX3: Fractional-N Synthesizer Control Register 3

| Bit   | 7 | 6         | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|---|-----------|---|---|---|---|---|---|--|--|

| Name  |   | D_K[15:8] |   |   |   |   |   |   |  |  |

| R/W   |   | R/W       |   |   |   |   |   |   |  |  |

| Reset | 1 | 1         | 0 | 1 | 0 | 1 | 1 | 1 |  |  |

Bit 7~0 **D\_K[15:8]**: RF channel fractional number code medium byte

#### • SX4: Fractional-N Synthesizer Control Register 4

| Bit   | 7 | 6 | 5 | 4 | 3          | 2 | 1 | 0 |  |

|-------|---|---|---|---|------------|---|---|---|--|

| Name  | _ | _ | _ | _ | D_K[19:16] |   |   |   |  |

| R/W   | _ | _ | _ | _ | R/W        |   |   |   |  |

| Reset | 0 | 0 | 0 | 0 | 0          | 0 | 1 | 1 |  |

Bit 7~4 Reserved, must be "0000"

Bit 3~0 **D** K[19:16]: RF channel fractional number code highest byte

$D_K[19:0]$ =floor ( $f_{RF} \times ODDIV/f_{XTAL}$ - $D_N) \times 2^{20}$ )

For example, XO=16MHz and RF band=433.92MHz which are initial setup:

- $\rightarrow$  (433.92MHz×2)/16MHz=54.24

- $\rightarrow$  D K=0.24×2<sup>20</sup>=251658

- → Dec2Hex (251658)=3D70A

- → Dec2Bin (251658)=0111 1101 0111 0000 1010

#### • STA1: Status Control Register 1

| Bit   | 7 | 6 | 5 | 4       | 3 | 2 | 1         | 0 |

|-------|---|---|---|---------|---|---|-----------|---|

| Name  | _ | _ | _ | CD_FLAG | _ |   | OMST[2:0] |   |

| R/W   | _ | _ | _ | R       | _ | R |           |   |

| Reset | 0 | 0 | 0 | 0       | 0 | 0 | 0         | 0 |

Bit 7~5 Reserved, must be "000"

#### Bit 4 **CD FLAG**: Carrier detection flag

This flag will be set high by hardware when carrier detection is okey after pulling DEMOD\_EN high. Here DEMOD\_EN high level is an internal signal which is generated by the internal state machine when in the Direct mode (DIR\_EN=1) or after the RX strobe command is received when in the Burst mode (DIR\_EN=0). The flag will be automatically cleared when RX\_EN rising edge occurs. Here RX\_EN rising edge is generated after setting RTX\_SEL=0 and RTX\_EN=1 when in the Direct mode or by the internal state machine after the RX strobe command is received when in the Burst mode.

Bit 3 Reserved, must be "0"

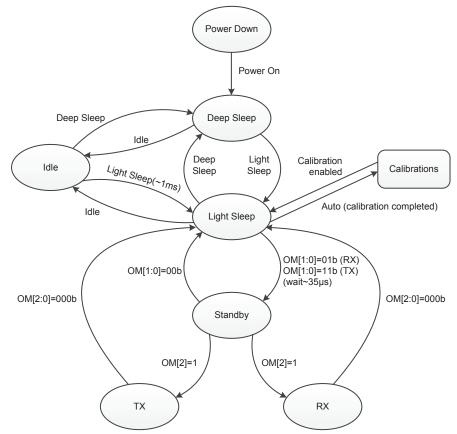

Bit 2~0 **OMST[2:0]**: Operation mode state indication (read only)

000: Deep Sleep mode

001: Idle mode

010: Light Sleep mode

011: Standby mode

100: TX mode

101: RX mode

110: VCO calibration mode

111: Undefined

#### • RSSI2: RSSI Control Register 2

| Bit   | 7 | 6 | 5 | 4 | 3              | 2 | 1 | 0 |  |

|-------|---|---|---|---|----------------|---|---|---|--|

| Name  | _ | _ | _ | _ | RSSI_CTHD[3:0] |   |   |   |  |

| R/W   | _ | _ | _ | _ | R/W            |   |   |   |  |

| Reset | 0 | 0 | 0 | 0 | 1              | 0 | 1 | 0 |  |

Bit 7~4 Reserved, must be "0000"

#### Bit 3~0 RSSI\_CTHD[3:0]: RSSI threshold for carrier detection

(RSSI\_CTHD×2+1)+74=RSSI threshold for carrier detection

#### • RSSI3: RSSI Control Register 3

| Bit   | 7 | 6               | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|---|-----------------|---|---|---|---|---|---|--|--|

| Name  |   | RSSI_NEGDB[7:0] |   |   |   |   |   |   |  |  |

| R/W   |   | R               |   |   |   |   |   |   |  |  |

| Reset | 0 | 0               | 0 | 0 | 0 | 0 | 0 | 0 |  |  |

#### Bit 7~0 **RSSI\_NEGDB[7:0]**: RSSI value (unit: -dB)

It is a real time measurement value.

### • RSSI4: RSSI Control Register 4

| Bit   | 7 | 6                 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|---|-------------------|---|---|---|---|---|---|--|--|

| Name  |   | RSSI_SYNC_OK[7:0] |   |   |   |   |   |   |  |  |

| R/W   |   | R                 |   |   |   |   |   |   |  |  |

| Reset | 0 | 0                 | 0 | 0 | 0 | 0 | 0 | 0 |  |  |

Bit 7~0 RSSI\_SYNC\_OK[7:0]: RSSI snapshot when SYNCWORD is detected OK

#### • ATR1: Auto TX/RX Control Register 1

| Bit   | 7               | 6 | 5       | 4     | 3      | 2         | 1 | 0      |

|-------|-----------------|---|---------|-------|--------|-----------|---|--------|

| Name  | ATRCLK_DIV[1:0] |   | ATRCLKS | ATRTU | ATRCTM | ATRM[1:0] |   | ATR_EN |

| R/W   | R/W             |   | R/W     | R/W   | R/W    | R/        | W | R/W    |

| Reset | 1               | 1 | 0       | 0     | 1      | 0         | 0 | 0      |

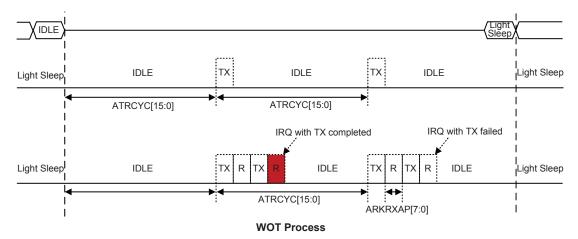

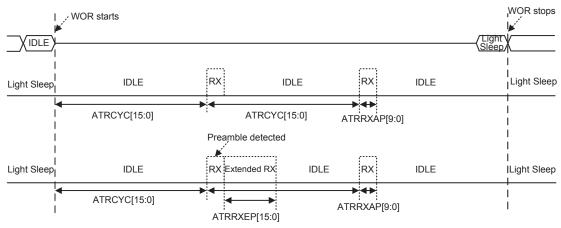

### Bit 7~6 ATRCLK\_DIV[1:0]: ATR clock frequency division

00: 1/1, ATRCLK=32768Hz

01: 1/4, ATRCLK=8192Hz

10: 1/8, ATRCLK=4096Hz

11: 1/16, ATRCLK=2048Hz

## Bit 5 ATRCLKS: ATRCLK clock source selection

0: From the internal LIRC clock

1: From the external ROSCi clock input on PAD GIOx pin

#### Bit 4 ATRTU: Auto TRX unit time selection

0: 250µs

1: 1ms, used to support low data rate applications

This bit is used to select the unit time for the ATR RX active period (ATRRXAP[9:0]), ATR RX extended period (ATRRXEP[15:0]) and ARK RX active period (ARKRXAP[7:0]).

#### Bit 3 ATRCTM: Auto TRX timer mode selection

0: Single mode, restart ATRCT timer when every ATR transation occurs

1: Continuous mode, start ATRCT timer upon receiving Idle command, stop ATRCT timer when ATR\_EN=0 or ATRCTM=0

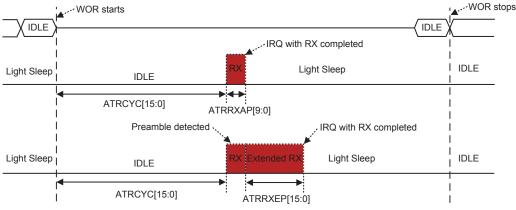

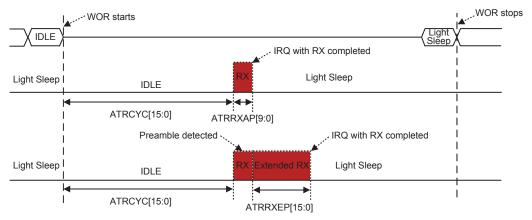

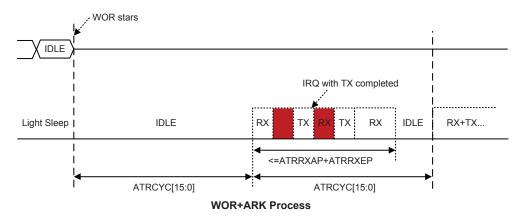

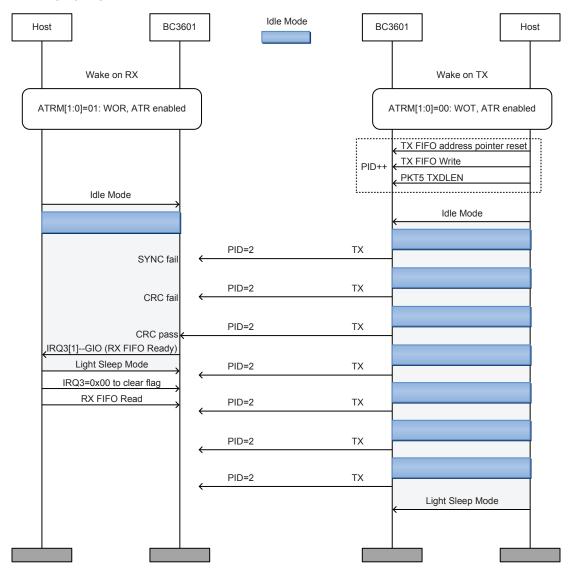

Bit 2~1 ATRM[1:0]: Auto TRX mode selection

00: ATR WOT mode 01: ATR WOR mode 10: ATR WTM mode 11: ATR WTM mode

Bit 0 ATR\_EN: Auto TRX enable

0: Disable 1: Enable

Note that the ATR functions are activated by operation state transition from standby/sleep mode to Idle mode.

## • ATR2: Auto TX/RX Control Register 2

| Bit   | 7 | 6           | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|---|-------------|---|---|---|---|---|---|--|

| Name  |   | ATRCYC[7:0] |   |   |   |   |   |   |  |

| R/W   |   |             |   | R | W |   |   |   |  |

| Reset | 1 | 1           | 1 | 1 | 1 | 1 | 1 | 1 |  |

Bit 7~0 ATRCYC[7:0]: ATRCT timer expire value low byte

#### ATR3: Auto TX/RX Control Register 3

| Bit   | 7 | 6            | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|---|--------------|---|---|---|---|---|---|--|

| Name  |   | ATRCYC[15:8] |   |   |   |   |   |   |  |

| R/W   |   | R/W          |   |   |   |   |   |   |  |

| Reset | 0 | 0            | 0 | 0 | 1 | 1 | 1 | 1 |  |

Bit 7~0 ATRCYC[15:8]: ATRCT timer expire value high byte

Wake up period=ATRCLK×(ATRCYC[15:0]+1). Default period is 1s.

## • ATR4: Auto TX/RX Control Register 4

| Bit   | 7 | 6            | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|---|--------------|---|---|---|---|---|---|--|

| Name  |   | ATRRXAP[7:0] |   |   |   |   |   |   |  |

| R/W   |   | R/W          |   |   |   |   |   |   |  |

| Reset | 0 | 0            | 1 | 0 | 0 | 1 | 1 | 1 |  |

## Bit 7~0 ATRRXAP[7:0]: ATR RX active period low byte

ATR RX active period high byte ATRRXAP[9:8] is located in the ATR11 register.

Active period=unit time×(ATRRXAP[9:0]+1); the unit time can be 250μs or 1ms which is determined by the ATRTU bit. The default ATR RX active period is 10ms with a default time unit of 250μs.

## • ATR5: Auto TX/RX Control Register 5

| Bit   | 7 | 6            | 5 | 4  | 3 | 2 | 1 | 0 |  |

|-------|---|--------------|---|----|---|---|---|---|--|

| Name  |   | ATRRXEP[7:0] |   |    |   |   |   |   |  |

| R/W   |   |              |   | R/ | W |   |   |   |  |

| Reset | 1 | 0            | 0 | 0  | 1 | 1 | 1 | 1 |  |

Bit 7~0 ATRRXEP[7:0]: ATR RX extend period low byte

### • ATR6: Auto TX/RX Control Register 6

| Bit   | 7 | 6             | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|---|---------------|---|---|---|---|---|---|--|

| Name  |   | ATRRXEP[15:8] |   |   |   |   |   |   |  |

| R/W   |   | RW            |   |   |   |   |   |   |  |

| Reset | 0 | 0             | 0 | 0 | 0 | 0 | 0 | 1 |  |

#### Bit 7~0 ATRRXEP[15:8]: ATR RX extended period high byte

Extend period=unit time×(ATRRXEP[15:0]+1); the unit time can be 250µs or 1ms which is determined by the ATRTU bit. The default ATR RX extended period is 100ms with a default time unit of 250µs.

### • ATR7: Auto TX/RX Control Register 7

| Bit   | 7 | 6          | 5 | 4 | 3 | 2      | 1        | 0      |

|-------|---|------------|---|---|---|--------|----------|--------|

| Name  |   | ARKNM[3:0] |   |   |   | ATR_WI | DLY[1:0] | ARK_EN |

| R/W   |   | R/W        |   |   |   | R/     | W        | R/W    |

| Reset | 0 | 1          | 1 | 1 | 0 | 0      | 1        | 0      |

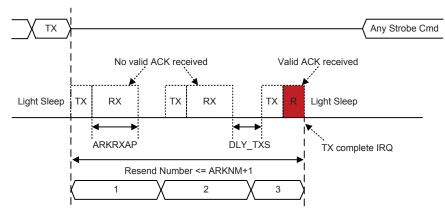

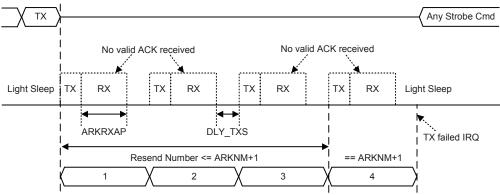

## Bit 7~4 **ARKNM[3:0]**: ARK repeat cycle number

Maximum repeat cycle number=ARKNM[3:0]+1

Bit 3 Reserved, must be "0"

#### Bit 2~1 ATR\_WDLY[1:0]: Auto wake up delay time

00: 244μs 01: 488μs 10: 732μs 11: 976μs

#### Bit 0 ARK\_EN: Auto Resend/ACK enable

0: Disable 1: Enable

#### ATR8: Auto TX/RX Control Register 8

| Bit   | 7 | 6            | 5 | 4  | 3 | 2 | 1 | 0 |  |

|-------|---|--------------|---|----|---|---|---|---|--|

| Name  |   | ARKRXAP[7:0] |   |    |   |   |   |   |  |

| R/W   |   |              |   | R/ | W |   |   |   |  |

| Reset | 0 | 0            | 1 | 0  | 0 | 1 | 1 | 1 |  |

#### Bit 7~0 **ARKRXAP[7:0]**: ARK RX active period

Active period=unit time $\times$ (ARKRXAP[7:0]+1); the unit time can be 250 $\mu$ s or 1ms which is determined by the ATRTU bit. The default ARK RX active period is 10ms with a default time unit of 250 $\mu$ s.

#### ATR9: Auto TX/RX Control Register 9

| Bit   | 7 | 6               | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|---|-----------------|---|---|---|---|---|---|--|

| Name  |   | ATRCT[7:0]      |   |   |   |   |   |   |  |

| R/W   |   | RW              |   |   |   |   |   |   |  |

| Reset | 0 | 0 0 0 0 0 0 0 0 |   |   |   |   |   |   |  |

Bit 7~0 ATRCT[7:0]: ATR cycle timer low byte

## • ATR10: Auto TX/RX Control Register 10

| Bit   | 7 | 6           | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|---|-------------|---|---|---|---|---|---|--|

| Name  |   | ATRCT[15:8] |   |   |   |   |   |   |  |

| R/W   |   | R/W         |   |   |   |   |   |   |  |

| Reset | 0 | 0           | 0 | 0 | 0 | 0 | 0 | 0 |  |

#### Bit 7~0 ATRCT[15:8]: ATR cycle timer high byte

Reading ATRCT[15:0] will get the current count value. Due to the limitation of SPI 8-bit data length, reading the ATR9 register will take a snapshot of the whole 16-bit data into the read register buffer. Users should read ATR9 and ATR10 in series (non-interrupted) to get correct data.

Writing to ATRCT[15:0] will update the count value. Write to ATR9 first and then write to ATR10 to trigger the ATRCT write function. This timer update mechanism is used to align the time slot for the master and slave in a two-way RF system.

#### • ATR11: Auto TX/RX Control Register 11

| Bit   | 7 | 6 | 5 | 4 | 3 | 2 | 1     | 0       |

|-------|---|---|---|---|---|---|-------|---------|

| Name  | _ | _ | _ | _ | _ | _ | ATRRX | AP[9:8] |

| R/W   | _ | _ | _ | _ | _ | _ | R/W   |         |

| Reset | 0 | 0 | 0 | 0 | 0 | 0 | 0     | 0       |

### Bit 7~0 ATRRXAP[9:8]: ATR RX active period high byte

ATR RX active period low byte ATRRXAP[7:0] is located in the ATR4 register.

Active period=unit time $\times$ (ATRRXAP[9:0]+1); the unit time can be 250 $\mu$ s or 1ms which is determined by the ATRTU bit. The default ATR RX active period is 10ms with a default time unit of 250 $\mu$ s.

#### • XO1: XO Control Register 1

| Bit   | 7 | 6 | 5 | 4            | 3 | 2   | 1 | 0 |  |

|-------|---|---|---|--------------|---|-----|---|---|--|

| Name  | _ | _ | _ | XO_TRIM[4:0] |   |     |   |   |  |

| R/W   | _ | _ | _ |              |   | R/W |   |   |  |

| Reset | 0 | 0 | 0 | 1            | 0 | 0   | 0 | 0 |  |

Bit 7~5 Reserved, must be "000"

Bit 4~1 XO\_TRIM[4:0]: Trim value for the internal capacitor load for the crystal

Default setting=2.4pF, step=0.15pF. The larger the trim value is the larger the capacitor load will be, vice versa.

#### • XO2: XO Control Register 2

| Bit   | 7 | 6 | 5 | 4 | 3      | 2           | 1 | 0 |

|-------|---|---|---|---|--------|-------------|---|---|