# **AmZ8148**

### Chip Select Address Decoder With Acknowledge

#### DISTINCTIVE CHARACTERISTICS

- One-of-Eight Decoder provides eight chip select outputs

- Acknowledge output responds to enables and acknowledge input command

- Open-collector Acknowledge output for wired-OR application

- Inverting and non-inverting enable inputs for upper address decoding

- 100% product assurance screening to MIL-STD-883 requirements

#### **FUNCTIONAL DESCRIPTION**

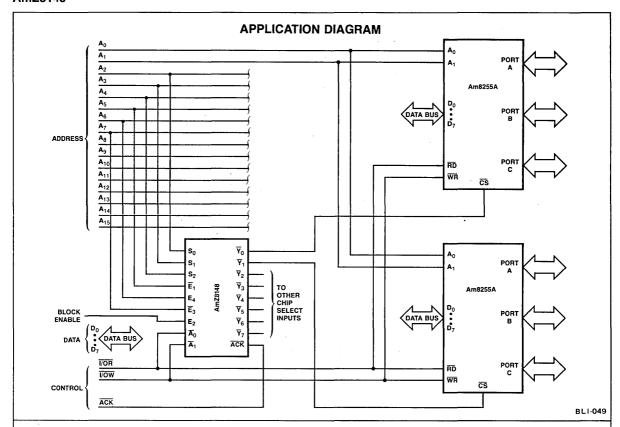

The AmZ8148 Address Decoder combines a three-line to eight-line decoder with four qualifying enable inputs (two active HIGH and two active LOW) and the acknowledge output required for "ready" or "wait state" control of all popular MOS microprocessors.

The acknowledge output, ACK, is active LOW and responds to the combination of all enables and an acknowledge active, input command.

The eight chip select outputs are individually active LOW in response to the combination of all enables active and the corresponding 3-bit input code at the S inputs.

The AmZ8148 is intended for chip select decoding in small, medium or large systems where multiple chip selects must be generated and address space must be allocated conservatively.

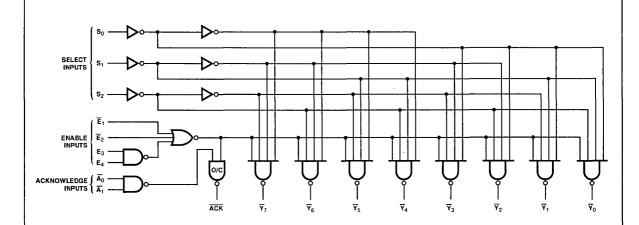

#### **LOGIC DIAGRAM**

BL 1-045

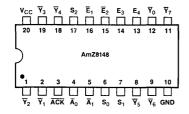

## CONNECTION DIAGRAM Top View

Note: Pin 1 is marked for orientation.

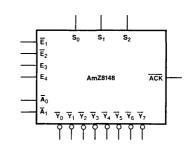

#### LOGIC SYMBOL

BLI-047

BLI-046

#### **ELECTRICAL CHARACTERISTICS**

$V_{CC} = 5.0V \pm 5\%$  (MIN. = 4.75V MAX. = 5.25V)  $V_{CC} = 5.0V \pm 10\%$  (MIN. = 4.50V MAX. = 5.50V)

#### DC CHARACTERISTICS OVER OPERATING RANGE

| Parameters      | Description                           | Test Cond                                                                      | <b>ditions</b> (Not      | e 1) | Min.  | <b>Typ.</b> (Note 2) | Max.        | Units |

|-----------------|---------------------------------------|--------------------------------------------------------------------------------|--------------------------|------|-------|----------------------|-------------|-------|

| V <sub>OH</sub> | Output HIGH Voltage                   | V <sub>CC</sub> = MIN.<br>V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub> | I <sub>OH</sub> = -440μA |      | 2.4   | 3.4                  |             | Volts |

| V <sub>OL</sub> | Output LOW Voltage                    | V <sub>CC</sub> = MIN.<br>V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub> | I <sub>OL</sub> = 4.0mA  |      |       |                      | 0.4<br>0.45 | Volts |

| V <sub>IH</sub> | Input HIGH Level                      | Guaranteed input log<br>voltage for all inputs                                 | -                        |      | 2.0   |                      |             | Volts |

| VIL             | Input LOW Level                       | Guaranteed input logical LOW MIL voltage for all inputs COM'L                  |                          |      |       |                      | 0.7<br>0.8  | Volts |

| VI              | Input Clamp Voltage                   | V <sub>CC</sub> = MIN., I <sub>IN</sub> =                                      |                          |      | -1.5  | Volts                |             |       |

| I <sub>IL</sub> | Input LOW Current                     | V <sub>CC</sub> = MAX., V <sub>IN</sub> =                                      |                          |      | -0.36 | mA                   |             |       |

| Iн              | Input HIGH Current                    | V <sub>CC</sub> = MAX., V <sub>IN</sub> =                                      |                          |      |       | 20                   | μΑ          |       |

| lı              | Input HIGH Current                    | V <sub>CC</sub> = MAX., V <sub>IN</sub> =                                      |                          |      | 0.1   | mA                   |             |       |

| Isc             | Output Short Circuit Current (Note 3) | V <sub>CC</sub> = MAX.                                                         | -15                      |      | -85   | mA                   |             |       |

| lcc             | Power Supply Current (Note 4)         | V <sub>CC</sub> = MAX.                                                         |                          |      |       | 15                   | 20          | mA    |

Notes: 1. For conditions shown as MIN. or MAX., use the appropriate value specified under Electrical Characteristics for the applicable device type.

2. Typical limits are at  $V_{CC} = 5.0V$ , 25°C ambient and maximum loading.

3. Not more than one output should be shorted at a time. Duration of the short circuit test should not exceed one second. 4. TEST CONDITIONS:  $S_0 = S_1 = S_2 = \overline{E}_1 = \overline{E}_2 = GND$ :  $\overline{A}_0 = \overline{A}_1 = E_3 = E_4 = 4.5V$ .

#### MAXIMUM RATINGS (Above which the useful life may be impaired)

| Storage Temperature                                 | −65°C to +150°C                |

|-----------------------------------------------------|--------------------------------|

| Temperature (Ambient) Under Bias                    | −55°C to +125°C                |

| Supply Voltage to Ground Potential Continuous       | -0.5V to +7.0V                 |

| DC Voltage Applied to Outputs for High Output State | -0.5V to +V <sub>CC</sub> max. |

| DC Input Voltage                                    | -0.5V to +7.0V                 |

| DC Output Current Into Outputs                      | 30mA                           |

| DC Input Current                                    | -30mA to +5.0mA                |

### AmZ8148

## **SWITCHING CHARACTERISTICS**

$(T_A = +25^{\circ}C, V_{CC} = 5.0V)$

| Parameters       | Description                                             | Min. | Тур. | Max. | Units | <b>Test Conditions</b>          |

|------------------|---------------------------------------------------------|------|------|------|-------|---------------------------------|

| t <sub>PLH</sub> | $S_i$ to $\overline{Y}_i$ (Three Level Delay)           |      | 14   | 20   | ns    |                                 |

| t <sub>PHL</sub> | S; to Y; (Three Level Delay)                            |      | 19   | 27   | ns    |                                 |

| t <sub>PLH</sub> | S. to V. (True Level Delevi)                            |      | 13   | 18   | ns    |                                 |

| t <sub>PHL</sub> | S <sub>i</sub> to Y <sub>i</sub> (Two Level Delay)      |      | 15   | 21   | ns    |                                 |

| t <sub>PLH</sub> | $\overline{E}_1$ , $\overline{E}_2$ to $\overline{Y}_i$ |      | 13   | 18   | ns    |                                 |

| tPHL             | E <sub>1</sub> , E <sub>2</sub> to T <sub>1</sub>       |      | 16   | 23   | ns    |                                 |

| t <sub>PLH</sub> | F F A W                                                 |      | 15   | 21   | ns    | $C_1 = 15pF$                    |

| t <sub>PHL</sub> | $E_3$ , $E_4$ to $\overline{Y}_i$                       |      | 19   | 27   | ns    | $C_L = 15pF$ $R_L = 2.0k\Omega$ |

| t <sub>PLH</sub> | Ā <sub>i</sub> to ACK                                   |      | 25   | 35   | ns    |                                 |

| t <sub>PHL</sub> | A; to ACK                                               | -    | 16   | 22   | ns    |                                 |

| t <sub>PLH</sub> | E <sub>1</sub> , E <sub>2</sub> to ACK                  |      | 29   | 40   | ns    |                                 |

| t <sub>PHL</sub> | E1, E2 10 ACK                                           |      | 25   | 35   | ns    |                                 |

| t <sub>PLH</sub> |                                                         |      | 29   | 40   | ns    |                                 |

| t <sub>PHL</sub> | E <sub>3</sub> , E <sub>4</sub> to ACK                  |      | 25   | 35   | ns    |                                 |

SWITCHING CHARACTERISTICS OVER OPERATING RANGE

| OVER OPERATING HANGE |                                                            | CC                                                          | M'L  | М                                                                                        | IL   |       |                        |

|----------------------|------------------------------------------------------------|-------------------------------------------------------------|------|------------------------------------------------------------------------------------------|------|-------|------------------------|

|                      |                                                            | T <sub>A</sub> = 0°C to +70°C<br>V <sub>CC</sub> = 5.0V ±5% |      | $T_A = -55^{\circ}\text{C to } +125^{\circ}\text{C}$<br>$V_{CC} = 5.0\text{V } \pm 10\%$ |      |       |                        |

| Parameters           | Description                                                | Min.                                                        | Max. | Min.                                                                                     | Max. | Units | <b>Test Conditions</b> |

| t <sub>PLH</sub>     | O As V (Three Level Balan)                                 |                                                             | 27   |                                                                                          | 30   | ns    |                        |

| t <sub>PHL</sub>     | S <sub>i</sub> to Y <sub>i</sub> (Three Level Delay)       |                                                             | 34   |                                                                                          | 36   | ns    |                        |

| t <sub>PLH</sub>     | S. to V. (Two Level Delev)                                 |                                                             | 23   |                                                                                          | 25   | ns    |                        |

| t <sub>PHL</sub>     | S <sub>i</sub> to Y <sub>i</sub> (Two Level Delay)         |                                                             | 28   |                                                                                          | 31   | ns    |                        |

| t <sub>PLH</sub>     | $\overline{E}_{1}, \overline{E}_{2}$ to $\overline{Y}_{i}$ |                                                             | 23   |                                                                                          | 25   | ns    |                        |

| t <sub>PHL</sub>     | E1, E2 10 Ti                                               |                                                             | 29   |                                                                                          | 31   | ns    |                        |

| tpLH                 | E <sub>3</sub> , E <sub>4</sub> to $\overline{Y}_i$        |                                                             | 27   |                                                                                          | 28   | ns    | C <sub>L</sub> = 50pF  |

| tpHL                 | E3, E4 to 1;                                               |                                                             | 34   |                                                                                          | 36   | ns    | $R_L = 2.0k\Omega$     |

| t <sub>PLH</sub>     | A <sub>i</sub> to ACK                                      |                                                             | 45   |                                                                                          | 45   | ns    |                        |

| t <sub>PHL</sub>     | A; 10 ACK                                                  |                                                             | 31   |                                                                                          | 35   | ns    |                        |

| t <sub>PLH</sub>     | $\overline{E}_1$ , $\overline{E}_2$ to $\overline{ACK}$    |                                                             | 45   |                                                                                          | 45   | ns    |                        |

| t <sub>PHĹ</sub>     | E1, E2 10 ACK                                              |                                                             | 39   |                                                                                          | 40   | ns    |                        |

| t <sub>PLH</sub>     | E <sub>3</sub> , E <sub>4</sub> to ACK                     |                                                             | 45   |                                                                                          | 45   | ns    |                        |

| tpHL                 | E3, E4 10 ACK                                              |                                                             | 39   |                                                                                          | 40   | ns    | 1                      |

#### **DEFINITION OF FUNCTIONAL TERMS**

- $S_0$ ,  $S_1$ ,  $S_2$  Three-line to eight-line chip select decoder inputs.

- $\overline{\mathbf{E}}_1, \overline{\mathbf{E}}_2$  The active LOW enable inputs. A HIGH on either the  $\overline{\mathbf{E}}_1$  or  $\overline{\mathbf{E}}_2$  input forces all decoded functions to be disabled, and forces  $\overline{\mathsf{ACK}}$  HIGH.

- ${\sf E_3}, {\sf E_4}$  The active HIGH enable inputs. A LOW on either  ${\sf E_3}$  or  ${\sf E_4}$  inputs forces all the decoded functions to be inhibited, and forces  $\overline{\sf ACK}$  HIGH.

- ${\bf A_0}, {\bf A_1}$  The acknowledge inputs,  ${\bf A_0}$  and  ${\bf A_1},$  are active LOW inputs used as conditions for an active LOW output at the acknowledge,  $\overline{{\sf ACK}}$ , output.

- $\begin{tabular}{lll} \hline \textbf{ACK} & The acknowledge output, $\overline{ACK}$, is an active LOW output used to signal the microprocessor that specific devices have been selected. $\overline{ACK}$ goes LOW only when $\overline{E}_1$ and $\overline{E}_2$ are LOW, $E_3$ and $E_4$ are HIGH and $\overline{A}_0$ or $\overline{A}_1$ is LOW. \\ \end{tabular}$

- $\overline{\mathbf{Y}}_{\mathbf{i}}$  The eight active LOW chip select outputs.

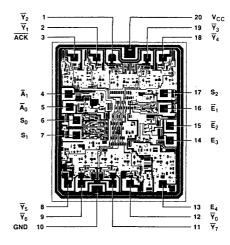

#### **METALLIZATION AND PAD LAYOUT**

DIE SIZE: 0.081" X 0.096"

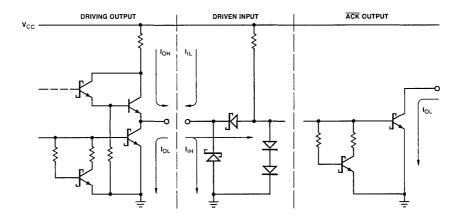

# LOW-POWER SCHOTTKY INPUT/OUTPUT CURRENT INTERFACE CONDITIONS

Note: Actual current flow direction shown.

BL1-048

# FUNCTION TABLES CHIP SELECT OUTPUTS Y<sub>i</sub>

| s <sub>2</sub> | S <sub>1</sub> | S <sub>0</sub> | Ē <sub>1</sub> | Ē <sub>2</sub> | E <sub>3</sub> | E <sub>4</sub> | <u> </u> | <u>Y</u> 1 | <u>¥</u> 2 | $\overline{Y}_3$ | <b>Y</b> <sub>4</sub> | <b>7</b> <sub>5</sub> | $\overline{\mathbf{Y}}_{6}$ | <b>T</b> <sub>7</sub> |

|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------|------------|------------|------------------|-----------------------|-----------------------|-----------------------------|-----------------------|

| L              | L              | L              | L              | L              | Н              | н              | L        | Н          | Н          | Н                | Н                     | н                     | Н                           | Н                     |

| L              | L              | Н              | L              | L              | Н              | Н              | Н        | L          | Н          | Н                | Н                     | Н                     | Н                           | Н                     |

| L              | Н              | L              | L              | L              | Н              | н              | Н        | Н          | L          | Н                | Н                     | Н                     | Н                           | Н                     |

| L              | Н              | Н              | L              | L              | Н              | Н              | Н        | Н          | Н          | L                | Н                     | Н                     | Н                           | Н                     |

| Н              | L              | L              | L              | L              | Н              | Н              | Н        | Н          | Н          | Н                | L                     | Н                     | Н                           | Н                     |

| Н              | L              | Н              | L              | L              | Н              | Н              | Н        | Н          | Н          | Н                | Н                     | L                     | Н                           | Н                     |

| Н              | Н              | L              | L              | L              | Н              | н              | Н        | Н          | Н          | Н                | Н                     | Н                     | L                           | Н                     |

| Н              | Н              | Н              | L              | L              | Н              | н              | Н        | Н          | Н          | Н                | Н                     | Н                     | Н                           | L                     |

| Х              | Х              | Х              | Н              | Х              | Х              | Х              | Н        | Н          | н          | Н                | Н                     | Н                     | Н                           | Н                     |

| Х              | Х              | Х              | х              | Н              | Х              | Х              | Н        | н          | Н          | Н                | Н                     | H,                    | Н                           | Н                     |

| Х              | Х              | Х              | х              | Х              | L              | Х              | Н        | Н          | н          | Н                | Н                     | Н                     | Н                           | Н                     |

| X              | Х              | Х              | х              | Х              | Х              | L              | Н        | Н          | Н          | Н                | Н                     | Н                     | Н                           | Н                     |

#### ACKNOWLEDGE OUTPUT ACK

| Ē₁ | E <sub>2</sub> | E <sub>3</sub> | E <sub>4</sub> | Ā <sub>0</sub> | <b>A</b> <sub>1</sub> | ACK |

|----|----------------|----------------|----------------|----------------|-----------------------|-----|

| Н  | Х              | Х              | х              | X              | Х                     | Н   |

| Х  | Н              | Х              | X              | X              | Х                     | Н   |

| Х  | X              | L              | Х              | X              | х                     | Н   |

| Х  | X              | Х              | L              | X              | Х                     | Н   |

| L  | L              | н              | Н              | L              | Х                     | L   |

| L  | L              | Н              | н              | Х              | L                     | L   |