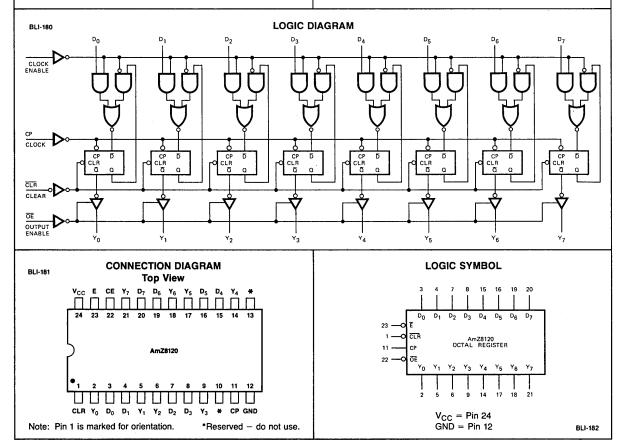

# **AmZ8120**

# Octal D-Type Flip-Flop with Clear, Clock Enable and 3-State Control

#### DISTINCTIVE CHARACTERISTICS

- Buffered common clock enable input

- Buffered common asynchronous clear input

- Three-state outputs

- 8-bit, high-speed parallel register with positive edge-triggered, D-type flip-flops

- 100% product assurance screening to MIL-STD-883 requirements

#### FUNCTIONAL DESCRIPTION

The AmZ8120 is an 8-bit register built using advanced Low-Power Schottky technology. The register consists of eight D-type flip-flops with a buffered common clock, a buffered common clock enable, a buffered asynchronous clear input, and three-state outputs.

When the clear input is LOW, the internal flip-flops of the register are reset to logic 0 (LOW), independent of all other inputs. When the clear input is HIGH, the register operates in the normal fashion.

When the three-state output enable ( $\overline{OE}$ ) input is LOW, the Y outputs are enabled and appear as normal TTL outputs. When the output enable ( $\overline{OE}$ ) input is HIGH, the Y outputs are in the high impedance (three-state) condition. This does not affect the internal state of the flip-flop Q output.

The clock enable input  $(\overline{E})$  is used to selectively load data into the register. When the  $\overline{E}$  input is HIGH, the register will retain its current data. When the  $\overline{E}$  is LOW, new data is entered into the register on the LOW-to-HIGH transition of the clock input.

This device is packaged in a slim 24-pin package (0.3 inch row spacing).

**T**....

## **ELECTRICAL CHARACTERISTICS**

The Following Conditions Apply Unless Otherwise Specified:

COM'L  $T_A = 0^{\circ}C$  to +70°C  $V_{CC} = 5.0 V \pm 5\%$  MIN. = 4.75 V MAX. = 5.25 V

## MIL $T_A = -55^{\circ}C$ to $+125^{\circ}C$ $V_{CC} = 5.0V \pm 10\%$ MIN. = 4.50V MAX. = 5.50V

## DC CHARACTERISTICS OVER OPERATING RANGE

| Parameters      | Description                                  | Test Conditions (Note 1)                                                             |                               |       | Min. | Typ.<br>(Note 2) | Max.  | Units |

|-----------------|----------------------------------------------|--------------------------------------------------------------------------------------|-------------------------------|-------|------|------------------|-------|-------|

|                 |                                              | V <sub>CC</sub> = MIN.                                                               | MIL, I <sub>OH</sub> = -1.0mA |       | 2.4  | 3.4              |       | N/-1  |

| v <sub>он</sub> | Output HIGH Voltage                          | V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub> COM'L, I <sub>OH</sub> = -2.6mA |                               | 2.4   | 3.4  |                  | Volts |       |

|                 | Output LOW Voltage                           | V <sub>CC</sub> = MIN.                                                               | I <sub>OL</sub> = 4.0mA       |       |      |                  | 0.4   | Volts |

| VOL             |                                              | VIN = VIH or VIL                                                                     | I <sub>OL</sub> = 8.0mA       |       |      |                  | 0.45  |       |

| v <sub>iH</sub> | Input HIGH Level                             | Guaranteed input logical HIGH voltage for all inputs                                 |                               |       | 2.0  |                  |       | Volts |

|                 |                                              | Guaranteed input logical LOW                                                         |                               | MIL   |      |                  | 0.7   | Malas |

| VIL             | Input LOW Level                              | voltage for all inputs                                                               |                               | COM'L |      |                  | 0.8   | Volts |

| vı              | Input Clamp Voltage                          | V <sub>CC</sub> = MIN., I <sub>IN</sub> = -18mA                                      |                               |       |      |                  | 1.5   | Volts |

| ЧĻ              | Input LOW Current                            | V <sub>CC</sub> = MAX., V <sub>IN</sub> = 0.4 V                                      |                               |       |      |                  | -0.36 | mA    |

| ι <sub>н</sub>  | Input HIGH Current                           | V <sub>CC</sub> = MAX., V <sub>IN</sub> = 2.7 V                                      |                               |       |      |                  | 20    | μA    |

| II.             | Input HIGH Current                           | V <sub>CC</sub> = MAX., V <sub>IN</sub> = 7.0V                                       |                               |       |      |                  | 0.1   | mA    |

| 10              | Off-State (High-Impedance)<br>Output Current | Vcc = MAX.                                                                           | V <sub>O</sub> = 0.4 V        |       |      | · · · · · ·      | -20   |       |

| lo              |                                              | V <sub>CC</sub> - MAX.                                                               |                               |       |      |                  | 20    | μA    |

| I <sub>SC</sub> | Output Short Circuit Current<br>(Note 3)     | V <sub>CC</sub> = MAX.                                                               |                               |       | -15  |                  | 85    | mA    |

| 'cc             | Power Supply Current<br>(Note 4)             | V <sub>CC</sub> = MAX.                                                               |                               |       |      | 24               | 37    | mA    |

Notes: 1. For conditions shown as MIN, or MAX,, use the appropriate value specified under Electrical Characteristics for the applicable device type,

2. Typical limits are at V\_CC = 5.0 V, 25  $^{\circ}$ C ambient and maximum loading.

3. Not more than one output should be shorted at a time. Duration of the short circuit test should not exceed one second.

4. All outputs open,  $\vec{E}$  = GND, Di inputs = CLR =  $\overline{OE}$  = 4.5V. Apply momentary ground, then 4.5V to clock input.

### MAXIMUM RATINGS (Above which the useful life may be impaired)

| –65°C to +150°C                |

|--------------------------------|

| –55°C to +125°C                |

| –0.5V to +7.0V                 |

| –0.5V to +V <sub>CC</sub> max. |

| -0.5 V to +7.0 V               |

| 30 mA                          |

| -30mA to +5.0mA                |

|                                |

## AmZ8120

## SWITCHING CHARACTERISTICS

$(T_A = +25^{\circ}C, V_{CC} = 5.0 V)$

| Parameters       | Desc                                  | Min.     | Тур. | Max. | Units | <b>Test Conditions</b> |                          |

|------------------|---------------------------------------|----------|------|------|-------|------------------------|--------------------------|

| tPLH             | Clock to $Y_i$ ( $\overline{OE}$ LOW) |          |      | 18   | 27    |                        |                          |

| tPHL             |                                       |          |      | 24   | 36    | ns                     |                          |

| tphL             | Clear to Y                            |          |      | 22   | 35    | ns                     |                          |

| ts               | Data (D <sub>i</sub> )                |          | 10   | 3    |       | ns                     |                          |

| t <sub>h</sub>   | Data (D <sub>i</sub> )                |          | 10   | 3    |       | ns                     |                          |

|                  | Enable (Ē)                            | Active   | 15   | 10   |       | ns                     | ՝CL = 15pF<br>RL = 2.0kΩ |

| ts               |                                       | Inactive | 20   | 12   |       |                        |                          |

| th               | Enable (Ē)                            |          | 0    | 0    |       | ns                     | HL = 2.0kΩ               |

| ts               | Clear Recovery (In-Active) to Clock   |          | 11   | 7    |       | ns                     |                          |

|                  | Clock                                 | HIGH     | 20   | 14   |       | - ns                   |                          |

| t <sub>pw</sub>  |                                       | LOW      | 25   | 13   |       |                        |                          |

| tpw              | Clear                                 |          | 20   | 13   |       | ns                     |                          |

| <sup>t</sup> ZH  | DE to Y <sub>i</sub>                  |          |      | 9    | 13    | ns                     | ~                        |

| †ZL              |                                       |          |      | 14   | 21    |                        |                          |

| tнz              | - OE to Y <sub>i</sub>                |          |      | 20   | 30    |                        | C <sub>L</sub> = 5.0pF   |

| tLZ              |                                       |          |      | 24   | 36    | ns                     | $R_L = 2.0 k\Omega$      |

| f <sub>max</sub> | Maximum Clock Fre                     |          | 40   |      | MHz   |                        |                          |

Note 1. Per industry convention, f<sub>max</sub> is the worst case value of the maximum device operating frequency with no constraints on t<sub>r</sub>, t<sub>f</sub>, pulse width or duty cycle.

| SWITCHING CHARACTERISTICS |                                     |          | COM'L<br>$T_A = 0^{\circ}C \text{ to } +70^{\circ}C$<br>$V_{CC} = 5.0V \pm 5\%$ |      | MIL<br>T <sub>A</sub> = -55°C to +125°C<br>V <sub>CC</sub> = 5.0V ± 10% |      |       |                         |

|---------------------------|-------------------------------------|----------|---------------------------------------------------------------------------------|------|-------------------------------------------------------------------------|------|-------|-------------------------|

| OVER OPERATING RANGE*     |                                     |          |                                                                                 |      |                                                                         |      |       |                         |

| Parameters                | Parameters Description              |          | Min.                                                                            | Max. | Min.                                                                    | Max. | Units | Test Conditions         |

| <b>t</b> PLH              | Clock to Y <sub>i</sub> (OE LOW)    |          |                                                                                 | 33   |                                                                         | 39   |       |                         |

| <sup>t</sup> PHL          |                                     |          |                                                                                 | 45   |                                                                         | 54   | ns    |                         |

| tPHL                      | Clear to Y                          |          |                                                                                 | 43   |                                                                         | 51   | ns    |                         |

| ts                        | Data (D <sub>i</sub> )              |          | 12                                                                              |      | 15                                                                      |      | ns    |                         |

| th                        | Data (D <sub>i</sub> )              |          | 12                                                                              |      | 15                                                                      |      | ns    |                         |

|                           | Enable (E)                          | Active   | 17                                                                              |      | 20                                                                      |      | ns    | С <sub>L</sub> = 50рF   |

| ts                        |                                     | Inactive | 20                                                                              |      | 23                                                                      |      |       |                         |

| t <sub>h</sub>            | Enable (Ē)                          |          | 0                                                                               |      | 0                                                                       |      | ns    | R <sub>L</sub> = 2.0kΩ  |

| ts                        | Clear Recovery (In-Active) to Clock |          | 13                                                                              |      | 15                                                                      |      | ns    |                         |

|                           | <u></u>                             | HIGH     | 25                                                                              |      | 30                                                                      |      |       |                         |

| tpw                       | Clock                               | LOW      | 30                                                                              |      | 35                                                                      |      | ns    |                         |

| tpw                       | Clear                               |          | 22                                                                              |      | 25                                                                      |      | ns    |                         |

| tzH                       | OE to Yi                            |          |                                                                                 | 19   |                                                                         | 25   | ns    |                         |

| tZL                       |                                     |          |                                                                                 | 30   |                                                                         | 39   | 113   |                         |

| tHZ                       | DE to Yi                            |          |                                                                                 | 35   |                                                                         | 40   | ns    | C <sub>L</sub> = 5.0 pF |

| tLZ                       |                                     |          |                                                                                 | 39   |                                                                         | 42   |       | R <sub>L</sub> = 2.0 kΩ |

| f <sub>max</sub>          | Maximum Clock Frequency (Note 1)    |          | 25                                                                              |      | 20                                                                      |      | MHz   |                         |

\*AC performance over the operating temperature range is guaranteed by testing defined in Group A, Subgroup 9.

### **DEFINITION OF FUNCTIONAL TERMS**

- CLR When the clear input is LOW, the  $Q_i$  outputs are LOW, regardless of the other inputs. When the clear input is HIGH, data can be entered into the register.

- СР Clock Pulse for the Register; enters data into the register on the LOW-to-HIGH transition.

- Yi The register three-state outputs.

Ē

Clock Enable, When the clock enable is LOW, data on the D<sub>i</sub> input is transferred to the Q<sub>i</sub> output on the LOW-to-HIGH clock transition. When the clock enable is HIGH, the  $\boldsymbol{Q}_{j}$  outputs do not change state, regardless of the data or clock input transitions.

OE Output Control. When the OE input is HIGH, the  $Y_i$  outputs are in the high impedance state. When the OE input is LOW, the TRUE register data is present at the  $\mathbf{Y}_{i}$  outputs.

| FUN | ICTIO | N TA | BLE |

|-----|-------|------|-----|

|-----|-------|------|-----|

|          | Inputs |     |   |    |        | Internal  | Outputs |

|----------|--------|-----|---|----|--------|-----------|---------|

| Function | ŌE     | CLR | Ĕ | Di | СР     | Qi        | Yi      |

| Hi-Z     | н      | х   | х | х  | x      | x         | Z       |

| Clear    | н      | L   | x | x  | X      | L.        | z       |

|          | L      | L   | x | ×  | ×      | L         | L       |

| Hold     | н      | н   | н | ×  | x      | NC        | Z       |

|          | L      | н   | н | x  | x      | NC        | NC      |

| Load     | н      | н   | L | L  | 1      | L         | z       |

|          | н      | н   | L | н  | t      | н         | .z      |

|          | L      | н   | L | L  | 1      | L         | L       |

|          | L      | н   | Ŀ | н  | 1      | н         | н       |

| H ≈ HIGH |        |     |   | I  | NC = 1 | No Change |         |

L = LOW

X = Don't Care

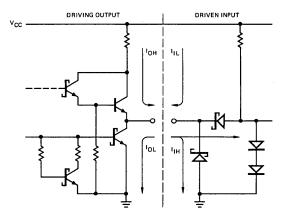

#### LOW-POWER SCHOTTKY INPUT/OUTPUT CURRENT INTERFACE CONDITIONS

Note: Actual current flow direction shown.

NC = No Change

<sup>1 =</sup> LOW-to-HIGH Transition Z = High Impedance