# Am9140 • Am91L40

4096 x1 Static R/W Random Access Memories

## DISTINCTIVE CHARACTERISTICS

- 4k x 1 organization

- Fully static data storage no refreshing

- Single +5V power supply

- High-speed access times down to 200ns max.

- Low operating power

- 578mW max., 9140

- 368mW max., 91L40

- Interface logic levels identical to TTL

- High noise immunity 400mV worst-case

- High output drive two standard TTL loads

- DC power-down mode reduces power by >80%

- Single phase, low voltage, low capacitance clock

- Static clock may be stopped in either state

- Data register on-chip

- · Address register on-chip

- Steady power drain no large surges

- Unique Memory Status signal

- improves performance

self clocking operation

- Full MIL temperature range available

- 100% MIL-STD-883 reliability assurance testing

#### **GENERAL DESCRIPTION**

The Am9140 and Am91L40 products are high performance, adaptive, low-power, 4k-bit, static, read/write random access memories. They are implemented as 4096 words by 1 bits per word. Only a single  $\pm$ 5V power supply is required for normal operation. A DC power-down mode reduces power while retaining data with a supply voltage as low as 1.5V.

All interface signal levels are identical to TTL specifications, providing good noise immunity and simplified system design. All inputs are purely capacitive MOS loads. The outputs will drive two full TTL loads or more than eight low-power Schottky loads.

Operational cycles are initiated when the Chip Enable clock goes HIGH. When the read or write is complete, Chip Enable goes LOW to preset the memory for the next cycle. Address and Chip Select signals are latched on-chip to simplify system timing. Output data is also latched and is available until the next operating cycle. The WE signal is HIGH for all read operations and is LOW during the Chip Enable time to perform a write.

Memory Status is an output signal that indicates when data is actually valid and when the preset interval is complete. It can be used to generate the CE input and to improve the memory performance.

## ORDERING INFORMATION

| Package  | Power                                        |      | Access Time |            |            |            |           |  |  |  |  |  |  |

|----------|----------------------------------------------|------|-------------|------------|------------|------------|-----------|--|--|--|--|--|--|

| Туре     | Ambient Temperature                          | Туре | 500ns       | 400ns      | 300ns      | 250ns      | 200ns     |  |  |  |  |  |  |

| Molded   | 0°C ≤ T₄ ≤ +70°C                             | STD  | AM9140APC   | AM9140BPC  | AM9140CPC  | AM9140DPC  | AM9140EPC |  |  |  |  |  |  |

| Molded   | $0 C \leq T_A \leq +70 C$                    | LOW  | AM91L40APC  | AM91L40BPC | AM91L40CPC | AM91L40DPC |           |  |  |  |  |  |  |

|          | 0°C - T - 170°C                              | STD  | AM9140ADC   | AM9140BDC  | AM9140CDC  | AM9140DDC  | AM9140EDC |  |  |  |  |  |  |

| Hermetic | $0^{\circ}C \leq T_{A} \leq +70^{\circ}C$    | LOW  | AM91L40ADC  | AM91L40BDC | AM91L40CDC | AM91L40DDC |           |  |  |  |  |  |  |

| DIP      | $-55^{\circ}C \leq T_{A} \leq +125^{\circ}C$ | STD  | AM9140ADM   | AM9140BDM  | AM9140CDM  |            |           |  |  |  |  |  |  |

|          |                                              | LOW  | AM91L40ADM  | AM91L40BDM | AM91L40CDM |            |           |  |  |  |  |  |  |

## Am9140 • Am91L40

MAXIMUM RATINGS above which the useful life may be impaired

| Storage Temperature                                 | -65°C to +150°C |

|-----------------------------------------------------|-----------------|

| Ambient Temperature Under Bias                      | 55°C to +125°C  |

| V <sub>CC</sub> with Respect to V <sub>SS</sub>     | -0.5V to +7.0V  |

| All Signal Voltages with Respect to V <sub>SS</sub> | -0.5V to +7.0V  |

| Power Dissipation                                   | 1.25W           |

The products described by this specification include internal circuitry designed to protect input devices from damaging accumulations of static charge. It is suggested, nevertheless, that conventional precautions be observed during storage, handling and use in order to avoid exposure to excessive voltages.

| OPERATING RAN                   | IGE             | POWER DOWN RA                  | NGE             |                                             |             |

|---------------------------------|-----------------|--------------------------------|-----------------|---------------------------------------------|-------------|

| V <sub>CC</sub>                 | V <sub>SS</sub> | V <sub>CC</sub>                | V <sub>SS</sub> | Ambient Temperature                         | Part Number |

| 4.75V ≤ V <sub>CC</sub> ≤ 5.25V | 0V              | 1.5V ≤ V <sub>CC</sub> ≤ 5.25V | ov              | $0^{\circ} C \leq T_{A} \leq +70^{\circ} C$ | AM91X40XDC  |

| $4.50V \leq V_{CC} \leq 5.50V$  | 0V              | 1.5V ≤ V <sub>CC</sub> ≤ 5.50V | 0V              | -55°C ≤ T <sub>A</sub> ≤ +125°C             | AM91X40XDM  |

Am9140

Am91L40

## ELECTRICAL CHARACTERISTICS over operating range (Note 1)

| Parameters       | Description                    | Test Con                                             | Min.                     | Тур. | Max. | Min. | Min. Typ. |     | Units |       |  |

|------------------|--------------------------------|------------------------------------------------------|--------------------------|------|------|------|-----------|-----|-------|-------|--|

| Maria            | Output HIGH Voltage            |                                                      | V <sub>CC</sub> = 4.75 V | 2.4  |      |      | 2.4       |     | Τ     | Volts |  |

| v <sub>он</sub>  | Output HIGH Voltage            | 1 <sub>OH</sub> = -200μA                             | V <sub>CC</sub> = 4.5 V  | 2.2  |      |      | 2.2       |     |       | VOILS |  |

| VOL              | Output LOW Voltage             | I <sub>OL</sub> = 3.2mA                              |                          |      |      | 0.4  |           |     | 0.4   | Volts |  |

| V <sub>IH</sub>  | Input HIGH Voltage             |                                                      |                          | 2.0  |      | Vcc  | 2.0       |     | Vcc   | Volts |  |

| VIL              | Input LOW Voltage              |                                                      |                          | -0.5 |      | 0.8  | -0.5      |     | 0.8   | Volts |  |

| 1 <sub>L1</sub>  | Input Load Current             | $V_{SS} \leq V_{IN} \leq V_{CC}$                     |                          |      | 10   |      |           | 10  | μA    |       |  |

| LO               | Output Leakage Current         | V <sub>SS</sub> < V <sub>OUT</sub> < V <sub>CO</sub> | c, Output disabled       |      |      | 10   |           |     | 10    | μA    |  |

|                  |                                | AA                                                   | T <sub>A</sub> = 25°C    |      | 50   | 100  |           | 40  | 65    |       |  |

| ICC              | V <sub>CC</sub> Supply Current | Max. V <sub>CC</sub><br>Output disabled              | $T_A = 0^\circ C$        |      |      | 110  |           |     | 70    | mA    |  |

|                  |                                | Output disabled                                      | T <sub>A</sub> =55°C     |      |      | 125  |           |     | 80    |       |  |

| CIA              | Input Capacitance (Address)    | Test frequency = 1N                                  | IHz                      |      | 3.0  | 6.0  |           | 3.0 | 6.0   | pF    |  |

| с <sub>оит</sub> | Output Capacitance             | T <sub>A</sub> = 25°C                                |                          |      | 4.0  | 7.0  |           | 4.0 | 7.0   | pF    |  |

| CIC              | Input Capacitance (Control)    | All pins at 0V                                       |                          |      | 6.0  | 9.0  |           | 6.0 | 9.0   | pF    |  |

| OWER D   | OWN CHARACTERIS                |                        | Am9140                |      |      | נ    |      |      |      |      |

|----------|--------------------------------|------------------------|-----------------------|------|------|------|------|------|------|------|

| arameter | Description                    | Test Co                | Min.                  | Typ. | Max. | Min. | Typ. | Max. | Unit |      |

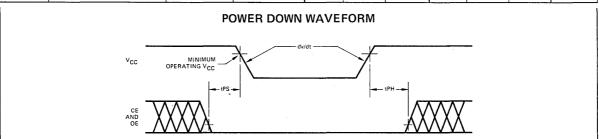

| dv/dt    | V <sub>CC</sub> Rate of Change |                        |                       |      |      | 3.0  |      |      | 3.0  | V/μs |

| tPS      | Power Down Set-Up Time         |                        |                       | tEL  |      |      | tEL  |      |      | ns   |

| tPH      | Power Up Hold Time             |                        |                       | tEL  |      |      | tEL  |      |      | ns   |

|          | I <sub>CC</sub> in Standby     | V <sub>CC</sub> = 2.0V | T <sub>A</sub> = 25°C |      | 36   | 72   |      | 28   | 55   | mA   |

|          |                                |                        | $T_A = 0^{\circ}C$    |      |      | 78   |      |      | 60   | mA   |

| 1        |                                |                        | T <sub>A</sub> =55°   |      |      | 89   |      |      | 68   | mA   |

| IPD      | (Note 2)                       |                        | T <sub>A</sub> = 25°C |      | 20   | 52   |      | 16   | 45   | mA   |

|          |                                | V <sub>CC</sub> = 1.5V | T <sub>A</sub> = 0°C  |      |      | 56   |      |      | 48   | mA   |

|          |                                |                        | T <sub>A</sub> =55°C  |      |      | 64   |      |      | 55   | mA   |

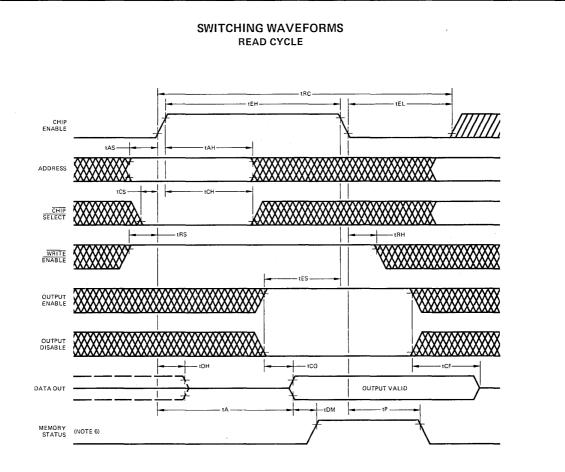

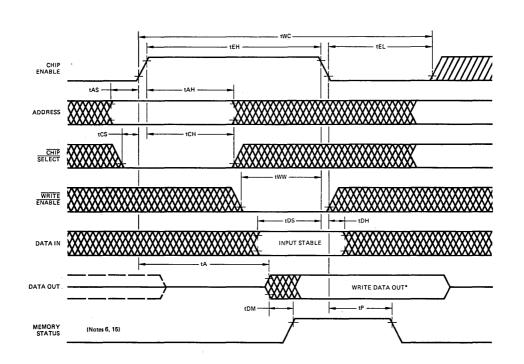

#### SWITCHING CHARACTERISTICS over operating range READ CYCLE (Notes 7, 8, 9)

| Parameter | Description                                        |     | Am9140A<br>Am91L40A<br>Min. Max. |     | Am9140B<br>Am91L40B<br>Min. Max. |     | Am9140C<br>Am91L40C<br>Min. Max. |     | Am9140D<br>Am91L40D<br>Min. Max. |     | Am9140E<br>Min. Max. |    |

|-----------|----------------------------------------------------|-----|----------------------------------|-----|----------------------------------|-----|----------------------------------|-----|----------------------------------|-----|----------------------|----|

| tRC       | Read Cycle Time (Note 5)                           | 770 |                                  | 620 |                                  | 470 |                                  | 395 |                                  | 320 |                      | ns |

| tA        | Access Time (Note 3)<br>(CE to Output Valid Delay) |     | 500                              |     | 400                              | _   | 300                              |     | 250                              |     | 200                  | ns |

| tEH       | Chip Enable HIGH Time (Note 14)                    | 500 |                                  | 400 |                                  | 300 |                                  | 250 |                                  | 200 |                      | ns |

| tEL       | Chip Enable LOW Time (Note 14)                     | 250 |                                  | 200 |                                  | 150 |                                  | 125 |                                  | 100 |                      | ns |

| tCH       | Chip Enable to Chip Select Hold Time               | 200 |                                  | 170 |                                  | 150 |                                  | 130 |                                  | 120 |                      | ns |

| tAH       | Chip Enable to Address Hold Time                   | 200 |                                  | 170 |                                  | 150 |                                  | 130 |                                  | 120 |                      | ns |

| tCS       | Chip Select to CE Set-Up Time (Note 4)             | -5  |                                  | -5  |                                  | -5  |                                  | 5   |                                  | -5  |                      | ns |

| tAS       | Address to Chip Enable Set-Up Time                 | 0   |                                  | 0   |                                  | 0   |                                  | 0   |                                  | 0   |                      | ns |

| tRS       | Read to Chip Enable Set-Up Time                    | 0   |                                  | 0   |                                  | 0   |                                  | 0   |                                  | 0   |                      | ns |

| tRH       | Chip Enable to Read Hold Time                      | 0   |                                  | 0   |                                  | 0   |                                  | 0   |                                  | 0   |                      | ns |

| tOH       | Chip Enable to Output OFF Delay (Note 3)           | 0   |                                  | 0   |                                  | 0   |                                  | 0   |                                  | 0   |                      | ns |

| tCF       | OE or OD to Output OFF Delay (Note 11)             |     | 200                              |     | 165                              |     | 135                              |     | 115                              |     | 100                  | ns |

| tCO       | OE or OD to Output ON Delay (Note 11)              |     | 220                              |     | 185                              |     | 150                              |     | 125                              |     | 110                  | ns |

| tES       | Output Enable to CE LOW Set-Up Time (Note 12)      | 90  |                                  | 75  |                                  | 60  |                                  | 55  |                                  | 50  |                      | ns |

| tDM       | Data Out to Memory Status Delay                    | 0   |                                  | 0   |                                  | 0   |                                  | 0   |                                  | 0   |                      | ns |

| tP        | Internal Preset Interval (Note 14)                 |     | tEL                              |     | tEL                              | 1   | tEL                              |     | tEL                              |     | tEL                  | ns |

2

# Am9140 • Am91L40

# SWITCHING CHARACTERISTICS over operating range

WRITE CYCLE (Notes 7, 8, 9)

|           |                                        | Am9140A<br>Am91L40A |      | Am9140B<br>Am91L40B |      | Am9140C<br>Am91L40C |      | Am9140D<br>Am91L40D |      |         |      |      |

|-----------|----------------------------------------|---------------------|------|---------------------|------|---------------------|------|---------------------|------|---------|------|------|

|           |                                        |                     |      |                     |      |                     |      |                     |      | Am9140E |      |      |

| Parameter | Description                            | Min.                | Max. | Min.                | Max. | Min.                | Max. | Min.                | Max. | Min.    | Max. | Unit |

| tWC       | Write Cycle Time (Note 5)              | 770                 |      | 620                 |      | 470                 |      | 395                 |      | 320     |      | ns   |

| ťA        | Access Time (CE to Output ON Delay)    |                     | 500  |                     | 400  |                     | 300  |                     | 250  |         | 200  | ns   |

| tEH       | Chip Enable HIGH Time (Notes 14, 15)   | 500                 |      | 400                 |      | 300                 |      | 250                 |      | 200     |      | ns   |

| tEL       | Chip Enable LOW Time (Notes 14, 15)    | 250                 |      | 200                 |      | 150                 |      | 125                 |      | 100     |      | ns   |

| tAS       | Address to Chip Enable Set-Up Time     | 0                   |      | 0                   |      | 0                   |      | 0                   |      | 0       |      | ns   |

| tAH       | Chip Enable to Address Hold Time       | 200                 |      | 170                 |      | 150                 |      | 130                 |      | 120     |      | ns   |

| tCS       | Chip Select to CE Set-Up Time (Note 4) | -5                  |      | -5                  |      | 5                   |      | -5                  |      | - 5     |      | ns   |

| tCH*      | Chip Enable to Chip Select Hold Time   | 200                 |      | 170                 |      | 150                 |      | 130                 |      | 120     |      | ns   |

| tWW       | Write Pulse Width (Note 10)            | 200                 |      | 165                 |      | 135                 |      | 115                 |      | 100     |      | ns   |

| tDS       | Data Input Set-Up Time (Note 10)       | 200                 |      | 165                 |      | 135                 |      | 115                 |      | 100     |      | ns   |

| tDH       | Data Input Hold Time (Note 10)         | 0                   |      | 0                   |      | 0                   |      | 0                   |      | 0       |      | ns   |

| tDM       | Data Out to Memory Status Delay        | 0                   |      | 0                   |      | 0                   |      | 0                   |      | 0       |      | ns   |

| tP        | Internal Preset Interval               |                     | tEL  |                     | tEL  |                     | tEL  |                     | tEL  |         | tEL  | ns   |

# SWITCHING WAVEFORMS WRITE CYCLE

\*Assumes output is enabled.

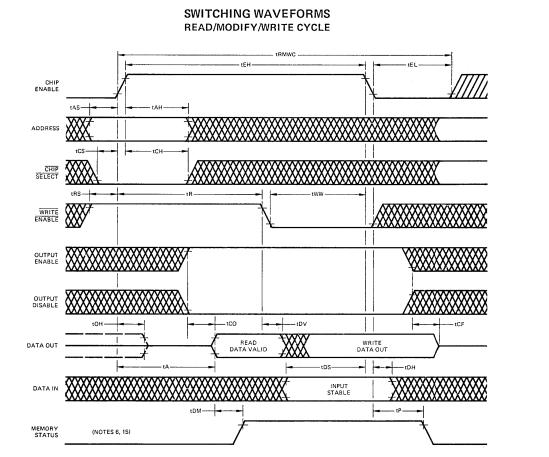

## SWITCHING CHARACTERISTICS over operating range READ/MODIFY/WRITE CYCLE (Notes 7, 8, 9)

|           |                                        |      | \m9140A Am9140B Am9140C Am9140<br>m91L40A Am91L40B Am91L40C Am91L4 |      |      |      |      |      |      |                |      |      |

|-----------|----------------------------------------|------|--------------------------------------------------------------------|------|------|------|------|------|------|----------------|------|------|

| Parameter | Description                            | Min. | Max.                                                               | Min. | Max. | Min. | Max. | Min. | Max. | Min.           | Max. | Unit |

| tRMWC     | R/M/W Cycle Time (Notes 5, 16)         | 970  |                                                                    | 785  |      | 605  |      | 510  |      | 420            |      | ns   |

| tA        | Access Time (CE to Output Valid Delay) |      | 500                                                                |      | 400  |      | 300  |      | 250  |                | 200  | ns   |

| tEH       | Chip Enable HIGH Time (Notes 14, 15)   | 700  |                                                                    | 565  |      | 435  |      | 365  |      | 300            |      | ns   |

| tEL       | Chip Enable LOW Time (Notes 14, 15)    | 250  |                                                                    | 200  |      | 150  |      | 125  |      | 100            |      | ns   |

| tCH       | Chip Enable to Chip Select Hold Time   | 200  |                                                                    | 170  |      | 150  |      | 130  |      | 120            |      | ns   |

| tAH       | Chip Enable to Address Hold Time       | 200  |                                                                    | 170  |      | 150  |      | 130  |      | 120            |      | ns   |

| tCS       | Chip Select to CE Set-Up Time (Note 4) | -5   |                                                                    | 5    |      | -5   |      | 5 \  |      | <sup>-</sup> 5 |      | ns   |

| tAS       | Address to Chip Enable Set-Up Time     | 0    |                                                                    | 0    |      | 0    |      | 0    |      | 0              |      | ns   |

| tRS       | Read to Chip Enable Set-Up Time        | 0    |                                                                    | 0    |      | 0    |      | 0    |      | 0              |      | ns   |

| tOH       | Chip Enable to Output OFF Delay        | 0    |                                                                    | 0    |      | 0    |      | 0    |      | 0              |      | ns.  |

| tDH       | Data Input Hold Time (Note 10)         | 0    |                                                                    | 0    |      | .0   |      | 0    |      | 0              |      | ns   |

| tDS       | Data Input Set-Up Time (Note 10)       | 200  |                                                                    | 165  |      | 135  |      | 115  |      | 100            |      | ns   |

| tWW       | Write Pulse Width (Note 10)            | 200  |                                                                    | 165  |      | 135  |      | 115  |      | 100            |      | ns   |

| tCF       | OE or OD to Output OFF Delay (Note 11) |      | 200                                                                |      | 165  |      | 135  |      | 115  |                | 100  | ns   |

| tCO       | OE or OD to Output ON Delay (Note 11)  |      | 220                                                                |      | 185  |      | 150  |      | 125  |                | 110  | ns   |

| tDV       | Data Valid after Write Delay           | 10   |                                                                    | 10   |      | 10   |      | 10   |      | 10             |      | ns   |

| tR        | Read Mode Hold Time                    | tA   |                                                                    | tA   |      | tA   |      | tA   |      | tA             |      | ns   |

| tDM       | Data Out to Memory Status Delay        | 0    |                                                                    | 0    |      | 0    |      | 0    |      | 0              |      | ns   |

| tP        | Internal Preset Interval               |      | tEL                                                                |      | tEL  |      | tEL  |      | tEL. |                | tEL  | ns   |

2

MPR-394

## NOTES:

- 1. Typical operating supply current values are specified for nominal processing parameters, nominal supply voltage and the specific ambient temperature shown.

- 2. Typical power-down supply current values are specified for nominal processing parameters, the specific supply voltage shown and the specific ambient temperature shown.

- At any operating temperature the minimum access time, tA(min.), will be greater than the maximum CE to output OFF delay, tOH(max.).

- 4. The negative value shown indicates that the Chip Select input may become valid as late as 5.0ns following the start of the Chip Enable rising edge.

- 5. The worst-case cycle times are the sum of CE rise time, tEH, CE fall time and tEL. The cycle time values shown include the worst-case tEH and tEL requirements and assume CE transition times of 10ns.

- 6. The Memory Status signal is a two-state output and is not affected by the Output Disable or Output Enable signals. If the output data buffers are turned off, Memory Status will continue to reflect the internal status of the memory.

- 7. Output loading is assumed to be one standard TTL gate plus 50pF of capacitance.

- 8. Timing reference levels for both input and output signals are 0.8V and 2.0V.

- 9. CE and  $\overline{WE}$  transition times are assumed to be  $\leq 10$  ns.

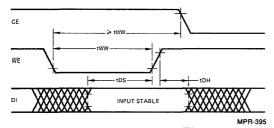

- 10. The internal write time of the memory is defined by the overlap of CE high and WE low. Both signals must be present on a selected chip to initiate a write. Either signal can terminate a write. The tWW, tDS and tDH specifications should all be referenced to the end of the write time. The Write Cycle timing diagram shows termination by the falling edge of CE. If termination is defined by bringing WE high while CE is high, the following timing applies:

## FUNCTIONAL DESCRIPTION

#### **Block Diagram**

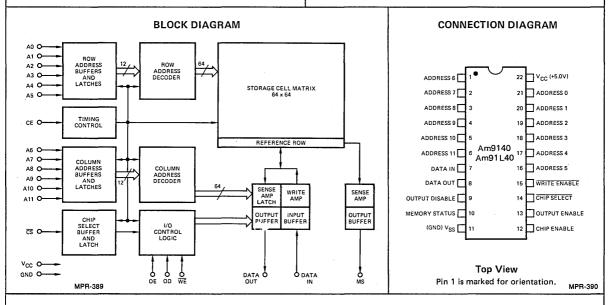

The block diagram for the Am9140 shows the interface connections along with the general signal flow. There are twelve address lines (A0 through A11) that are used to specify one of 4096 locations, with each location containing one bit. The Chip Select signal acts as a high order address. The Chip Enable clock latches the addresses into the address registers and controls the sequence of internal activities.

The row address signals (A0 through A5) and their inversions are distributed to the 64 row address decoders where one of

- 11. The output data buffer can be ON and output data valid only when Output Enable is high and Output Disable is low. OE and OD perform the same function with opposite control polarity.

- 12. The output data buffer should be enabled before the falling edge of CE in order to read output information. When the output is disabled and CE is low, the output data register is cleared.

- 13. Input and output data are the same polarity.

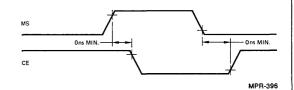

- 14. The Chip Enable waveform requirements may be defined by the Memory Status output waveform. For a read cycle, the basic CE requirement is that tEH ≥ tA and tEL ≥ tP:

- 15. The Memory Status output functions as if all operations are read cycles. If a write cycle begins with WE low and Data In stable at the time CE goes high, the rising edge of MS may be used as an indication that the write is complete and CE may be brought low. In a cycle where WE goes low at some point within the CE high time, the rising edge of MS should be ignored as an indication of write status. The falling edge of MS is always valid independent of the type of operation being performed.

- 16. For the R/M/W cycle, tEH (min.) is defined as tR (min.) + tWW. Note 5 defines tRMWC but it may also be viewed as tRC + tWW, Modify times are assumed to be zero. For systems with Data In and Data Out tied together R/M/W timing should make allowance for tCF time so that no bus conflict occurs (see Am9130 data sheet for timing approach).

the rows is selected. The 64 cells on the selected row are then connected to their respective bit line columns. Meanwhile, the column address signals (A6 through A11) are decoded and used to select one of 64 columns for the sense amplifier. Thus a single cell is connected into the output path.

During read operations, the sensed data is latched into the output register and is available for the balance of the operating cycle. During write operations, the write amplifier is turned on and drives the input data onto the sense lines, up the column bit lines and into the selected cell. Read and write data are the same polarity.

The data buffer is three-state and unselected chips have their outputs turned off so that several may be wire-ored together. The Output Enable and Output Disable signals provide asynchronous controls for turning off the output buffers.

Within the storage matrix there is an extra row of simulated cells. This reference row is selected on every operating cycle in addition to the addressed row and provides internal timing signals that control the data flow through the memory. The Memory Status output signal is derived from the reference row and uses the same designs for its sense and buffer circuits as used by the data bits.

#### Chip Enable

The Chip Enable input is a control clock that coordinates all internal activities. The rising edge of CE begins each cycle and strobes the Address and Chip Select signals into the on-chip register. Internal timing signals are derived from CE and from transitions of the address latches and the reference cells.

When the actual access time of the part has been reached (or a write operation is complete), CE may be switched low if desired. The worst-case time as specified in the data sheet may be used to determine the access. Alternatively, the access or write-complete time indicated by the rising edge of the Memory Status output signal may be used.

When CE goes low, the internal preset operation begins. The memory is ready for a new cycle only after the preset is complete. The worst-case CE low time specified in the data sheet may be used to determine the preset interval. Alternatively, the actual preset time is indicated as complete when Memory Status goes low.

There are no restrictions on the maximum times that CE may remain in either state so the clock may be extended or stopped whenever convenient. After power-on and before beginning a valid operation, the clock should be brought low to initially preset the memory.

#### Address and Chip Select

The Address inputs are latched into the on-chip address register by the rising edge of CE. Addresses must be held stable for the specified minimum time following the rising edge of CE in order to be properly loaded into the register. Following the address hold time, the address inputs are ignored by the memory until the next cycle is initiated.

The Chip Select input acts as a high order address for use when the system word capacity is larger than that of an individual chip. It allows the Address lines to be wired in parallel to all chips with the CS lines then used to select one active row of chips at a time. Unselected chips have their output buffers off so that selected chips wired to the same data lines can dominate the output bus. Only selected chips can perform write operations.

CS is latched in the same way that Addresses are. Once a memory is selected or deselected, it will remain that way until a new cycle with new select information begins.

#### Write Enable

The Write Enable line controls the read or write condition of the devices. When the CE clock is low, the WE signal may be in any state without affecting the memory. WE does not affect the status of the output buffer. To execute a read cycle, WE is held high while CE is high. To perform a write operation, the WE line is switched low while CE is high. Only a narrow write pulse width is required to successfully write into a cell. In many cases, however, it will be convenient to leave the WE line low during the whole cycle.

A write cycle can take place only when three conditions are met: The chip is selected, CE is high, and WE is low. This means that if either CE goes low or WE goes high, the writing is terminated.

#### Data In and Data Out

The requirements for incoming data during a write operation show a minimum set-up time with respect to the termination of the write. Termination occurs when either WE goes high or CE goes low. If incoming data changes during a write operation, the information finally written in the cell will be that stable data preceeding the termination by the set-up time. Since the data being written during a write cycle is impressed on the sense amplifier inputs, the output data will be the same as the input once the write is established.

During a read cycle, once all of the addressing is complete and the cell information has propagated through the sense amplifier, it enters the output data register. The read information can also flow through to the output if the buffer is enabled. As long as CE is high, the addressing remains valid and the output data will be stable. When CE goes low to begin the internal preset operation, the output information is latched into the data register. It will remain latched and stable as long as CE is low. If the output is disabled when CE is low, the output data register is cleared. At the start of every cycle when CE goes high, the output data latch is cleared in preparation for new information to come from the sense amplifier, and the output buffer is turned off.

OE and OD are designed to provide asynchronous control of the output buffer independent of the synchronous Chip Select control. The OE and OD control lines perform the same internal function except that one is inverted from the other. If either OE is low or OD is high, the output buffer will turn off. If the CS input is latched low and OE is high and OD is low, then the output buffer can turn on when data is available.

#### **Memory Status**

The Memory Status output is derived from the actual performance of the reference row of cells. Since the reference row is always doing a read operation, the MS output will appear in every operating cycle, whether a read or write is being performed. MS uses the same output circuitry as used in the data path. The result is that Memory Status tracks very closely the true operating performance of the memory.

The rising edge of MS indicates when output data is valid and tracks changes in access time with changing operating conditions. The rising edge also specifies the end of the time that CE must be held high for a read. CE may be high as long as desired, but may safely go low any time after MS goes high. The falling edge of MS occurs after CE goes low and the internal preset period is complete. It indicates that CE may go high to begin a new cycle. See the Am9130/40 Application Note for details.