MOS-425

# Am2825 · Am2826 · Am2827

2048-Bit Dynamic Shift Registers

#### **Distinctive Characteristics**

- 6 MHz data rate guaranteed

- Single 2048 and dual 1024-bit configurations

- Low power dissipation

- TTL compatible data inputs and outputs

- On chip recirculate and input select controls

- Plug-in replacement for National 5025/26/27

- Full military temperature range devices available

- 100% reliability assurance testing in compliance with MIL-STD-883

#### **FUNCTIONAL DESCRIPTION**

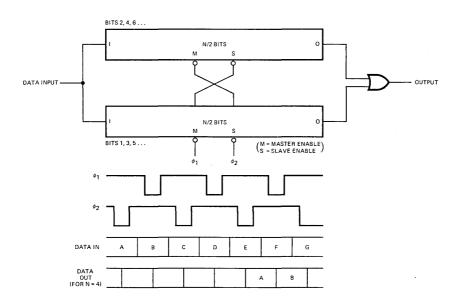

The Am2825/26/27 are military and commercial grade 2048-bit dynamic shift registers. The Am2825 is a dual 1024-bit device with on-chip recirculate and a load control (LC) common to both registers. When LC is HIGH, the two registers recirculate data; when LC is LOW new data is entered through the data inputs. The Am2826 is similar, but each register has two data inputs, selected by separate input select (IS) signals. The Am2827 is a single 2048-bit register with on-chip recirculate and a load control. All the devices can drive one standard TTL load or three Am93L series low-power TTL loads. The select, load command, and data inputs may be driven by TTL signals. Two high-voltage clock signals,  $\phi 1$  and  $\phi 2$ , are required. Internally, each shift register consists of two multiplexed registers, so that a data shift occurs on each  $\phi 1$  or  $\phi 2$  clock pulse. The data rate, therefore, is double the frequency of either clock signal.

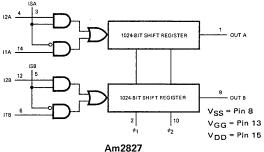

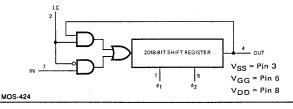

# LOGIC DIAGRAMS Am2825 1(1) 1024-BIT SHIFT REGISTER 1024-BIT SHIFT REGISTER V<sub>SS</sub> = Pin 5 (8) 7(10) 2(2) V<sub>GG</sub> = Pin 8 (13) V<sub>DD</sub> = Pin 10 (15) Am2826

OUT B

#### ORDERING INFORMATION

| Package<br>Type | Temperature<br>Range             | Order<br>Number |

|-----------------|----------------------------------|-----------------|

|                 | ····                             | Number          |

| 10-Pin Molded   | 0°C to +70°C                     | AM2825PC        |

| 16-Pin Hermetic | 0°C to +70°C                     | AM2825DC        |

| 16-Pin Hermetic | –55°C to +125°C                  | AM2825DM        |

| 16-Pin Molded   | 0°C to +70°C                     | AM2826PC        |

| 16-Pin Hermetic | 0°C to +70°C                     | AM2826DC        |

| 16-Pin Hermetic | –55°C to +125°C                  | AM2826DM        |

| 8-Pin Molded    | 0°C to +70°C                     | AM2827PC        |

| 8-Pin Hermetic  | –55°C to +125°C                  | AM2827DM        |

| 8-Pin Hermetic  | $0^{\circ}$ C to $+70^{\circ}$ C | AM2827DC        |

|                 |                                  |                 |

9 D OUT B

### CONNECTION DIAGRAMS

Top View Am2825 Am2825 Am2826 Am2827 OUT A 16 NC OUT A 10 VDD OUT A 16 NC B VDD 9 🗖 IN A aav 🖵 ¢1 [ 15 VDD φ<sub>1</sub> [ \$1 F 15 7 🗀 IN rc [ LC [ 14 🔲 IN A ∃ V<sub>GG</sub> ISA [ 14 🗖 11A 6 D VGG LC [ v<sub>ss</sub> 13 VGG 13 VGG \_\_\_ φ<sub>2</sub> NC. 12A [ IN B OUT [ 12 NC ISB [ 12 | 12B 11 NC 11 NC IN B ITB [ 10 🗖 🕫 NC [ 10 🗖 🕫

# Am2825 • Am2826 • Am2827

#### MAXIMUM RATINGS (Above which the useful life may be impaired)

| Storage Temperature                              | -65°C to +150°C |

|--------------------------------------------------|-----------------|

| Temperature (Ambient) Under Bias                 | −55°C to +125°C |

| DC Input Voltage with Respect to V <sub>SS</sub> | -20V to +0.3V   |

# **OPERATING RANGE**

| Part Number     | V <sub>SS</sub> | V <sub>DD</sub> | V <sub>GG</sub>  | TA              |

|-----------------|-----------------|-----------------|------------------|-----------------|

| AM2825/6/7DM    | +5.0V ±5%       | 0 V             | -10,0V to -11.0V | –55°C to +125°C |

| AM2825/6/7PC,DC | +5.0∨ ±5%       | 0 V             | -10.0V to -11.0V | 0°C to +70°C    |

# ELECTRICAL CHARACTERISTICS OVER OPERATING RANGE (Unless Otherwise Noted)

| Parameters                              | Description                 | Test Con                                                           | ditions                              | Min.                 | Typ.<br>(Note 1) | Max.                 | Units |

|-----------------------------------------|-----------------------------|--------------------------------------------------------------------|--------------------------------------|----------------------|------------------|----------------------|-------|

| v <sub>OH</sub>                         | Output High Voltage         | I <sub>OH</sub> = -0.5mA                                           |                                      | 2.4                  |                  | V <sub>SS</sub>      | Volts |

| V <sub>OL</sub>                         | Output LOW Voltage          | I <sub>OL</sub> = 1.6mA                                            |                                      | 0.0                  |                  | 0.4                  | Volts |

| VIH                                     | Input HIGH Level            | Guaranteed input logical HIGH voltage for all inputs except clocks |                                      | V <sub>SS</sub> -1.0 |                  | V <sub>SS</sub> +0.3 | Volts |

| VIL                                     | Input LOW Level             | Guaranteed input logical LOW voltage for all inputs except clocks  |                                      | V <sub>SS</sub> 10   |                  | V <sub>SS</sub> -4.2 | Volts |

| l <sub>1</sub>                          | Input Leakage Current       | V <sub>IN</sub> = -10V, T <sub>A</sub> = 25°C                      |                                      |                      | 10               | 500                  | nA    |

| Iφ                                      | Clock Input Leakage Current | $V_{\phi} = -15V$ , $T_{A} = 25^{\circ}C$                          |                                      |                      | 50               | 1000                 | nA    |

| $v_{\phi H}$                            | Clock HIGH Level            |                                                                    |                                      | V <sub>SS</sub> -1.0 |                  | V <sub>SS</sub> +0.3 | Volts |

| $V_{\phi L}$                            | Clock LOW Level             |                                                                    |                                      | V <sub>GG</sub> −0.3 |                  | V <sub>GG</sub> +0.8 | Volts |

|                                         |                             | T <sub>A</sub> = 25° C                                             | .01MHz <f<sub>\phi&lt;0.1MHz</f<sub> |                      | 2.5              | 5                    |       |

| IGG                                     | VGG Current                 | V <sub>SS</sub> = 5.25V                                            | $f_{\phi} = 1.0MHz$                  |                      | 2.5              | 5                    | mΑ    |

|                                         |                             | V <sub>GG</sub> = -11.0V                                           | $f_{\phi} = 3.0 MHz$                 |                      | 2.5              | 5                    |       |

| I <sub>DD</sub> V <sub>DD</sub> Current |                             | V <sub>ØL</sub> = −11.0V                                           | $.01MHz <_{\phi} < 0.1MHz$           |                      | 4                | 6                    |       |

|                                         | V <sub>DD</sub> Current     | t <sub>φpw</sub> = 125ns                                           | $f_{\phi} = 1.0 MHz$                 |                      | 20               | 30                   | mA    |

|                                         |                             | Data = 11110000                                                    | $f_{\phi} = 3.0 MHz$                 |                      | 45               | 65                   |       |

Note: 1. Typical Limits are at  $V_{SS}$  = 5.0V,  $V_{GG}$  = -10.5V and  $25^{\circ}$ C ambient.

# SWITCHING CHARACTERISTICS AND OPERATING REQUIREMENTS OVER OPERATING RANGE

| arameters         | Definition                          | Test                                                           | Conditions      | Min.  | <b>Typ.</b> (Note 1) | Max.   | Units |

|-------------------|-------------------------------------|----------------------------------------------------------------|-----------------|-------|----------------------|--------|-------|

|                   | C (N 0)                             | $T_A = 0^{\circ} C \text{ to } +70^{\circ} C$                  |                 | 0.02  |                      | 6.0    |       |

| fD                | Data Rate (Note 2)                  | T <sub>A</sub> = -55° C                                        | to +125° C      | 0.12  |                      | 4.0    |       |

|                   | 0. 1.5 (0. 0)                       | $T_A = 0^{\circ} C \text{ to } +70^{\circ} C$                  |                 | 0.01  |                      | 3.0    | MHz   |

| $f_{\phi}$        | Clock Frequency (Note 3)            | T <sub>A</sub> = -55°C                                         | to +125°C       | 0.06  |                      | 2.0    |       |

| t <sub>Ø</sub> d  | Delay Between Clocks (Note 3)       |                                                                |                 | 10    |                      | Note 3 | ns    |

|                   | 0. 1.0                              |                                                                | 0°C to +70°C    | 0.125 |                      | 10     | μς    |

| t <sub>ø</sub> pw | Clock LOW Time                      | $t_{\phi t} = 20$ ns                                           | -55°C to +125°C | 0.180 |                      | 10     |       |

| t <sub>øt</sub>   | Clock Rise and Fall Times           | 10% to 90%                                                     |                 |       |                      | 0.5    | μs    |

|                   | Set-Up Time, Data and Select Inputs |                                                                | 0°C to 70°C     | 40    |                      |        | ns    |

| t <sub>S</sub>    | (See Definitions)                   | -55° C to +125° C                                              |                 | 60    |                      |        | 1 113 |

|                   | Hold Time, Data and Select Inputs   |                                                                | 0°C to 70°C     | 30    |                      |        | ns    |

| th                | (See Definitions)                   |                                                                | -55°C to +125°C | 50    |                      |        | 113   |

| t <sub>pd</sub>   | Delay, Clock to Data Out            | C <sub>L</sub> = 15pF                                          | 0°C to +70°C    |       |                      | 80     | ns    |

|                   |                                     |                                                                | -55°C to +125°C |       |                      | 120    |       |

| C(D)              | Capacitance, Data Input             | Note 4  f = 1 MHz, V <sub>IN</sub> = 0V  All other pins at GND |                 |       |                      | 5      | pF    |

| C(S)              | Capacitance, Select Input or LC     |                                                                |                 |       |                      | 7      | pF    |

| C(\phi)           | Capacitance, Clock Input            |                                                                |                 |       | 175                  | 220    | 7 "   |

Notes: 2. The Data Rate is twice the frequency of either clock phase.

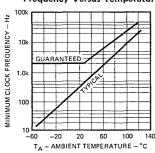

3. The maximum delay between clocks ( $\phi_1$  and  $\phi_2$  both HIGH) is a function of junction temperature. The junction temperature is a function of ambient temperature and clock duty cycle. See curves for minimum frequency on page 3.

4. This parameter is periodically sampled but not 100% tested. It is guaranteed by design.

#### **TRUTH TABLES**

Am2825 and Am2827

| LC | IN | OUT | DATA ENTERED |

|----|----|-----|--------------|

| L  | L  | Х   | L            |

| L  | Н  | X   | Н            |

| Н  | Х  | L   | L            |

| н  | Х  | Н   | Н            |

Am2826

| IS | INPUT 1 | INPUT 2 | DATA ENTERED |

|----|---------|---------|--------------|

| L  | L       | Х       | L            |

| L  | Н       | X       | Н            |

| Н  | Χ       | L       | L            |

| Н  | ×       | Н       | Н            |

#### **FUNCTIONAL EQUIVALENT OF EACH REGISTER**

Since the two registers shift on opposite clock pulses, a new data bit is entered on both  $\phi_1$  and  $\phi_2$ . Data entering the register on  $\phi_1$  will appear at the output on  $\phi_1$  (from the negative edge of  $\phi_1$  to the negative edge of  $\phi_2$ ).

MOS-426

#### **EFINITION OF TERMS**

namic Shift Register A shift register in which data storage curs on small capacitive nodes rather than in bistable logic cuits. Dynamic shift registers must be clocked continuously to intain the charge stored on the nodes.

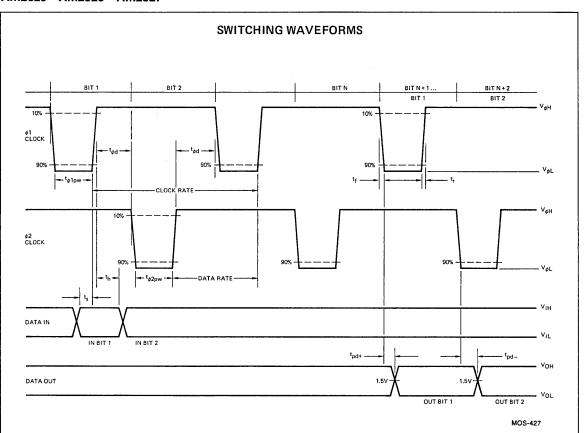

, \$\phi\_2\$ The two clock pulses applied to the register. The clock is I when it is at its negative voltage level and OFF when it is at 3. Data is accepted into the master of each bit during one ase and is transferred to the slave of each bit during the other ase.

Clock delay time. The time elapsing between the LOW-to-3H transition of one clock input and the HIGH-to-LOW trannon of the other clock input. During  $t_{\phi d}$  both clocks are HIGH all data is stored on capacitive nodes.

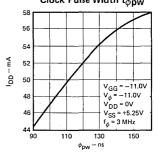

$t_{\phi pw}$  Clock pulse width. The LOW time of each clock signal. During  $t_{\phi pw}$  one of the clocks is ON, and data transfer between master and slave or slave and master occurs.

$t_{\phi t}$  Clock rise and fall times. The time required for the clock signals to change from 10% to 90% of the total level change occuring.

$t_s(D)$  Data set-up time. The time prior to the LOW-to-HIGH transition of  $\phi$  during which the data on the data input must be steady to be correctly written into the memory.

$t_h(D)$  Data hold time. The time following the LOW-to-HIGH transition of  $\phi$  during which the data must be steady. To correctly write data into the register, the data must be applied by  $t_s(D)$  before this transition and must not be changed until  $t_h(D)$  after this transition.

$t_{\mbox{\scriptsize pd}}$  The delay from a HIGH-to-LOW clock transition to correct data present at the register output.

Clock Rise Time 20ns Clock Fall Time 20ns Output Load 1 TTL Load

# 5

# **OPERATING CHARACTERISTICS**

# Guaranteed Minimum Clock Frequency Versus Temperature

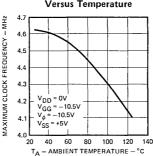

#### Maximum Clock Frequency Versus Temperature

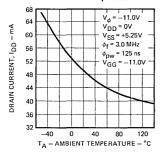

#### Typical Power Supply Current Versus Data Rate

#### Typical Power Supply Current Versus Temperature

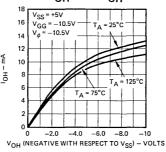

#### VOH Versus IOH

Typical Power Supply Current Versus Clock Pulse Width topw

MOS-428

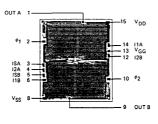

#### Metallization and Pad Layouts

#### Am2825

DIE SIZE 0.145" X 0.162"

### Am2826

DIE SIZE 0.145" X 0.162"

#### Am2827

DIE SIZE 0.145" X 0.162"