# **SoC Ultra-Low Power** RF-Microcontroller for RF **Carrier Frequencies in the** Range 27 - 1050 MHz

### ON Semiconductor®

www.onsemi.com

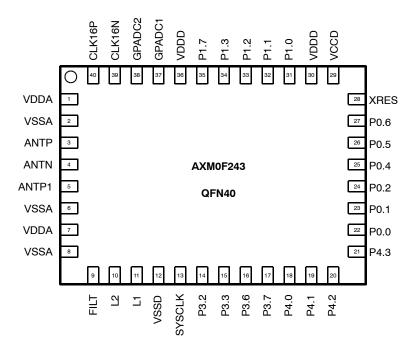

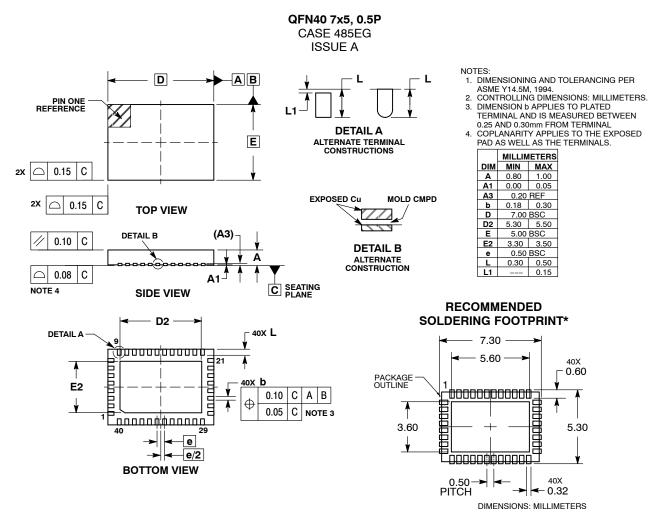

QFN40 7x5, 0.5P CASE 485EG

#### ORDERING INFORMATION

See detailed ordering and shipping information in Table 58 of this data sheet.

#### **OVERVIEW**

#### **Features**

System-on-Chip (SoC) Ultra-low Power Advanced Narrow-band RF-microcontroller Wireless **Communication Applications**

- QFN40 Package

- Supply Range 1.8 V 3.6 V

- $-40^{\circ}$ C to  $85^{\circ}$ C

- Deep Sleep Mode with Operational Analog and 2.5 μA Digital System Current

- Radio RX-mode 6.5 mA @ 169 MHz 9.5 mA @ 868 MHz and 433 MHz

- Radio TX-mode at 868 MHz 7.6 mA @ 0 dBm 21 mA @ 10 dBm 55 mA @ 15 dBm

- This is a Pb-Free Device

### 32-bit MCU Subsystem

- 48-MHz ARM Cortex-M0+ CPU

- Up to 64 KB of Flash with Read Accelerator

- Up to 8 KB of SRAM

### Programmable Analog

- Two opamps with reconfigurable high-drive external and high-bandwidth internal drive and Comparator modes and ADC input buffering capability. Opamps can operate in Deep Sleep low-power mode.

- 12-bit 1-Msps SAR ADC with differential and single-ended modes

- Single-slope 10-bit ADC function

- Two current DACs (IDACs) for general-purpose applications on any pin

- Two low-power comparators that operate in Deep Sleep low-power mode

### Programmable Digital

• Programmable logic blocks allowing Boolean operations to be performed on port inputs and outputs

### Low-Power 1.8 V to 3.6 V Operation

• Deep Sleep mode with operational analog and 2.5 μA digital system current

#### Serial Communication

• Two independent run-time reconfigurable Serial Communication Blocks (SCBs) with re-configurable I<sup>2</sup>C, SPI, or UART functionality

### Timing and Pulse-Width Modulation

- Five 16-bit timer/counter/pulse-width modulator (TCPWM) blocks

- Center-aligned, Edge, and Pseudo-random modes

- Comparator-based triggering of Kill signals for motor drive and other high-reliability digital logic applications

### Up to 19 Programmable GPIO Pins

1

- Any GPIO pin can be analog, or digital

- Drive modes, strengths, and slew rates are programmable

High Performance Narrow-band RF Transceiver compatible to AX5043 (FSK/MSK/4-FSK/GFSK/GMSK/ASK/AFSK/FM/PSK)

- Receiver

- Carrier Frequencies from 27 to 1050 MHz

- Data Rates from 0.1 kbps to 125 kbps

- Optional Forward Error Correction (FEC)

- Sensitivity without FEC

- -135 dBm @ 0.1 kbps, 868 MHz, FSK

- -126 dBm @ 1 kbps, 868 MHz, FSK

- -117 dBm @ 10 kbps, 868 MHz, FSK

- -107 dBm @ 100 kbps, 868 MHz, FSK

- -105 dBm @ 125 kbps, 868 MHz, FSK

- -138 dBm @ 0.1 kbps, 868 MHz, PSK

- -130 dBm @ 1 kbps, 868 MHz, PSK

- -120 dBm @ 10 kbps, 868 MHz, PSK

- -109 dBm @ 100 kbps, 868 MHz, PSK

- -108 dBm @ 125 kbps, 868 MHz, PSK

- Sensitivity with FEC

- –137 dBm @ 0.1 kbps, 868 MHz, FSK

- -122 dBm @ 5 kbps, 868 MHz, FSK

- -111 dBm @ 50 kbps, 868 MHz, FSK

- High Selectivity Receiver with up to 47 dB Adjacent Channel Rejection

- 0 dBm Maximum Input Power

- ♦ ±10% Data-rate Error Tolerance

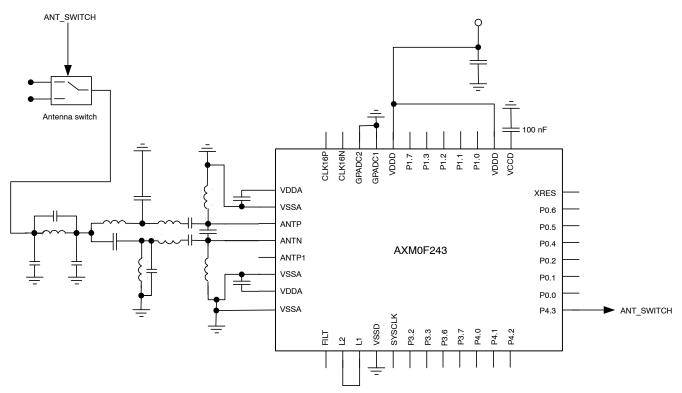

- Support for Antenna Diversity with External Antenna Switch

- Short Preamble Modes allow the Receiver to work with as little as 16 Preamble Bits

- Fast State Switching Times

200 μs TX → RX Switching Time

62 μs RX → TX Switching Time

- Transmitter

- Carrier Frequencies from 27 to 1050 MHz

- Data-rates from 0.1 kbps to 125 kbps

- High Efficiency, High Linearity Integrated Power Amplifier

- Maximum Output Power

- 16 dBm @ 868 MHz

- 16 dBm @ 433 MHz

- 16 dBm @ 169 MHz

- Power Level programmable in 0.5 dB Steps

- GFSK Shaping with BT=0.3 or BT=0.5

- Unrestricted Power Ramp Shaping

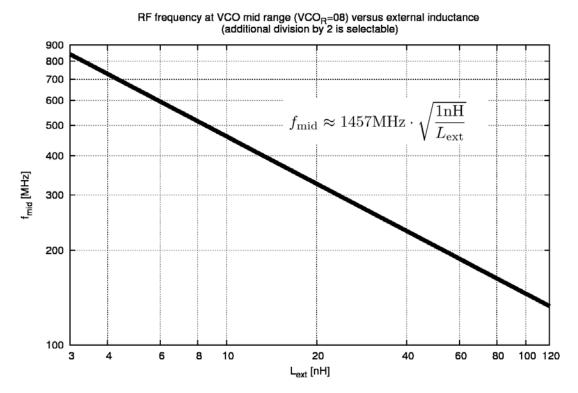

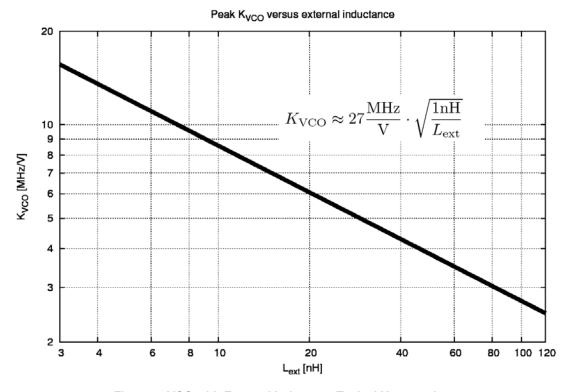

- RF Frequency Generation

- Configurable for Usage in 27 MHz –1050 MHz Bands

- RF Carrier Frequency and FSK Deviation Programmable in 1 Hz Steps

- Ultra Fast Settling RF Frequency Synthesizer for Low-power Consumption

- Fully Integrated RF Frequency Synthesizer with VCO Auto-ranging and Band-width Boost Modes for Fast Locking

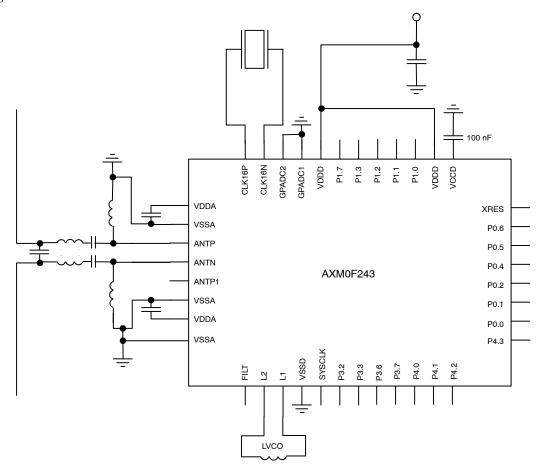

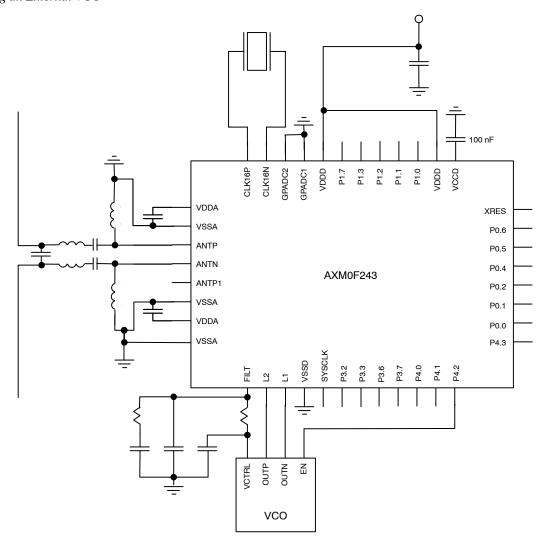

- Configurable for either Fully Integrated VCO, Internal VCO with External Inductor or Fully External VCO

- Configurable for either Fully Integrated or External Synthesizer Loop Filter for a Large Range of Bandwidths

- Channel Hopping up to 2000 hops/s

- ◆ Automatic Frequency Control (AFC)

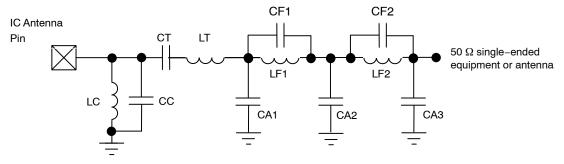

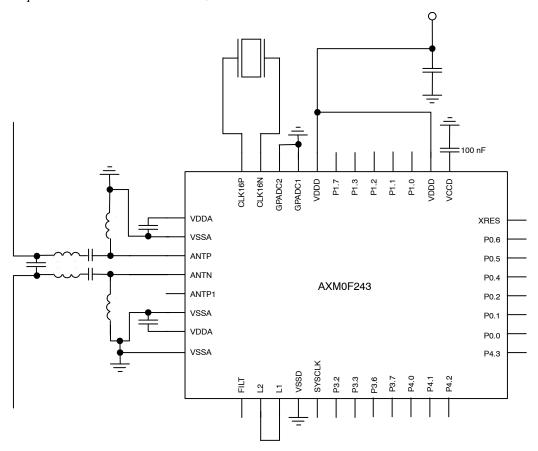

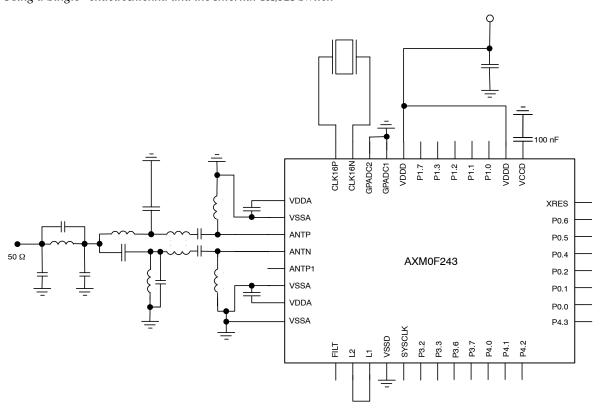

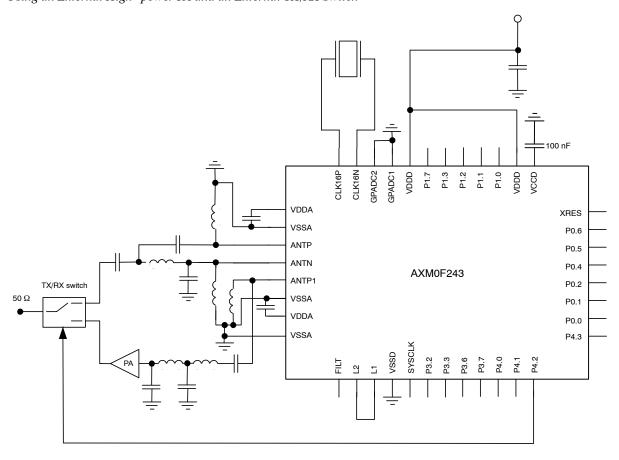

- Flexible Antenna Interface

- ◆ Integrated RX/TX Switching with Differential Antenna Pins

- Mode with Differential RX Pins and Single-ended TX Pin for Usage with External PAs and for Maximum PA Efficiency at Low Output Power

- Wakeup-on-Radio

- 640 Hz or 10 kHz Lowest Power Wake-up Timer

- Wake-up Time Interval programmable between 98 μs and 102 s

- Sophisticated Radio Controller

- Antenna Diversity and RX/TX Switch Control

- ◆ Fully Automatic Packet Reception and Transmission without Micro-controller Intervention

- ◆ Supports HDLC, Raw, Wireless M-Bus Frames and Arbitrary Defined Frames

- Automatic Channel Noise Level Tracking

- µs Resolution Timestamps for Exact Timing (eg. for Frequency Hopping Systems)

- ◆ 256 Byte Micro-programmable FIFO, optionally supports Packet Sizes > 256 Bytes

- Three Matching Units for Preamble Byte, Sync-word and Address

- ◆ Ability to store RSSI, Frequency Offset and Data—rate Offset with the Packet Data

- Multiple Receiver Parameter Sets allow the use of more aggressive Receiver Parameters during Preamble, dramatically shortening the Required Preamble Length at no Sensitivity Degradation

- Advanced Crystal Oscillator (RF Reference Oscillator)

- Fast Start-up and Lowest Power Steady-state XTAL Oscillator for a Wide Range of Crystals

- ♦ Integrated Tuning Capacitors

- Possibility of Applying an External Clock Reference (TCXO)

### **Applications**

27 - 1050 MHz Licensed and Unlicensed Radio Systems

- Internet of Things

- Automatic meter reading (AMR)

- Security applications

- Building automation

- Wireless networks

- Messaging Paging

- Compatible with: Wireless M-Bus, POCSAG, FLEX, KNX, Sigfox, Z-Wave, enocean

- Regulatory Regimes: EN 300 220 V2.3.1 including the Narrow-band 12.5 kHz, 20 kHz and 25 kHz

Definitions; EN 300 422; FCC Part 15.247; FCC Part 15.249; FCC Part 90 6.25 kHz, 12.5 kHz and 25 kHz

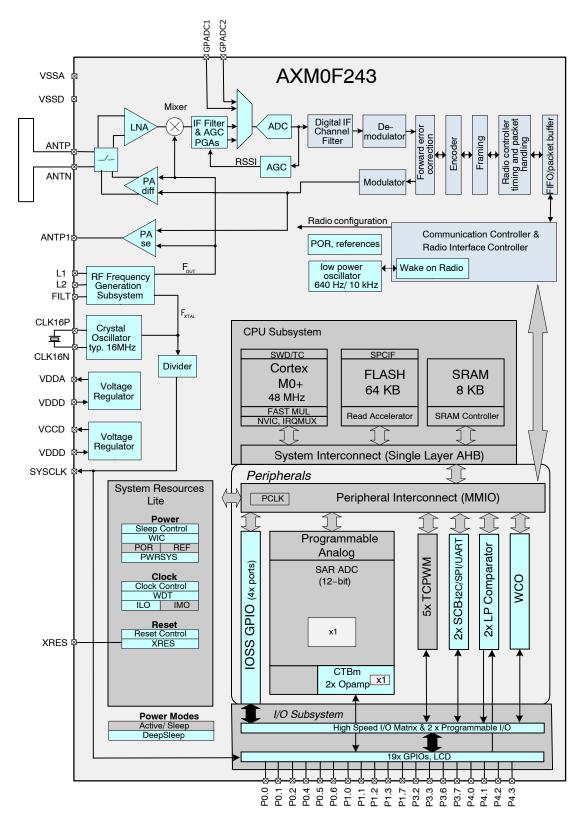

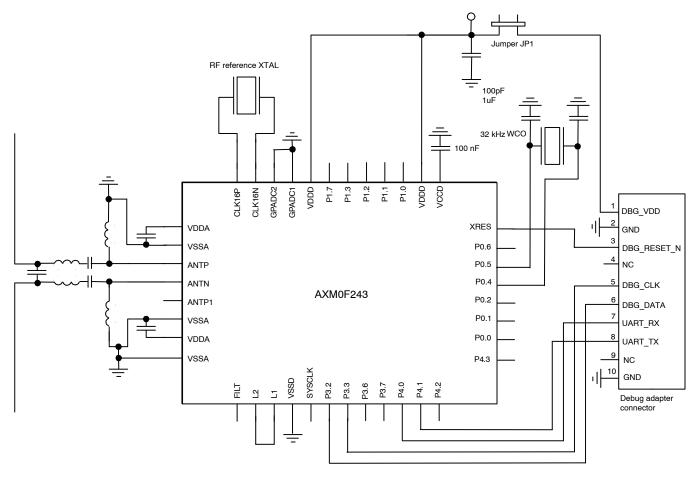

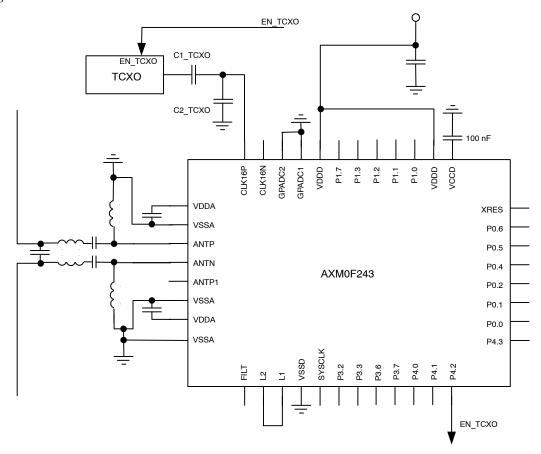

#### **BLOCK DIAGRAM**

Figure 1. Functional Block Diagram of the AXM0F243

**Table 1. PIN FUNCTION DESCRIPTION**

| Symbol | Pin(s)     | Туре        | Description                                               |

|--------|------------|-------------|-----------------------------------------------------------|

| VDDA   | 1          | Р           | Analog power output, decouple to neighboring VSSA         |

| VSSA   | 2          | Р           | Ground, decouple to neighboring VDDA                      |

| ANTP   | 3          | Α           | Differential antenna input/output                         |

| ANTN   | 4          | Α           | Differential antenna input/output                         |

| ANTP1  | 5          | А           | Single-ended antenna output                               |

| VSSA   | 6          | Р           | Ground, decouple to neighboring VDDA                      |

| VDDA   | 7          | Р           | Analog power output, decouple to neighboring VSSA         |

| VSSA   | 8          | Р           | Ground                                                    |

| FILT   | 9          | Α           | Optional synthesizer filter                               |

| L2     | 10         | Α           | Optional synthesizer inductor                             |

| L1     | 11         | Α           | Optional synthesizer inductor                             |

| VSSD   | 12         | Р           | Ground                                                    |

| SYSCLK | 13         | I/O/PU      | Default functionality: system clock output                |

| P3.2   | 14         | I/O/PU/PD/A | General purpose IO                                        |

| P3.3   | 15         | I/O/PU/PD/A | General purpose IO                                        |

| P3.6   | 16         | I/O/PU/PD/A | General purpose IO                                        |

| P3.7   | 17         | I/O/PU/PD/A | General purpose IO                                        |

| P4.0   | 18         | I/O/PU/PD/A | General purpose IO                                        |

| P4.1   | 19         | I/O/PU/PD/A | General purpose IO                                        |

| P4.2   | 20         | I/O/PU/PD/A | General purpose IO                                        |

| P4.3   | 21         | I/O/PU/PD/A | General purpose IO                                        |

| P0.0   | 22         | I/O/PU/PD/A | General purpose IO                                        |

| P0.1   | 23         | I/O/PU/PD/A | General purpose IO                                        |

| P0.2   | 24         | I/O/PU/PD/A | General purpose IO                                        |

| P0.4   | 25         | I/O/PU/PD/A | General purpose IO                                        |

| P0.5   | 26         | I/O/PU/PD/A | General purpose IO                                        |

| P0.6   | 27         | I/O/PU/PD/A | General purpose IO                                        |

| XRES   | 28         | I/PU        | Reset pin                                                 |

| VCCD   | 29         | Р           | Regulated digital supply, decouple to ground              |

| VDDD   | 30         | Р           | Unregulated power supply                                  |

| P1.0   | 31         | I/O/PU/PD/A | General purpose IO                                        |

| P1.1   | 32         | I/O/PU/PD/A | General purpose IO                                        |

| P1.2   | 33         | I/O/PU/PD/A | General purpose IO                                        |

| P1.3   | 34         | I/O/PU/PD/A | General purpose IO                                        |

| P1.7   | 35         | I/O/PU/PD/A | General purpose IO                                        |

| VDDD   | 36         | Р           | Unregulated power supply                                  |

| GPADC1 | 37         | Α           | GPADC input, must be connected to GND if not used         |

| GPADC2 | 38         | Α           | GPADC input, must be connected to GND if not used         |

| CLK16N | 39         | Α           | Crystal oscillator input/output (RF reference oscillator) |

| CLK16P | 40         | Α           | Crystal oscillator input/output (RF reference oscillator) |

| GND    | Center pad | Р           | Ground on center pad of QFN, must be connected            |

A = analog input I = digital input signal O = digital output signal PU = pull-up

N = not to be connected P = power or ground PD = pull-down

### **Alternate Pin Functions**

Each Port pin has can be assigned to one of multiple functions; it can, for instance, be an analog I/O or a digital

peripheral function. The pin assignments are shown in the following table.

### **Table 2. ALTERNATE PIN FUNCTIONS**

|      |                           |                   | HSIOM_PORT_S                  | SEL[x].SELy (*5) |                  |                      |

|------|---------------------------|-------------------|-------------------------------|------------------|------------------|----------------------|

|      |                           | Act               | tive                          |                  | Dee              | pSleep               |

| Pin  | ACTIVE #0                 | ACTIVE #1         | ACTIVE #2                     | ACTIVE #3        | Deep Sleep #2    | Deep Sleep #3        |

| P0.0 |                           | scb[2].uart_cts:0 | pass.dsi_sar_data<br>_valid:0 | tcpwm.tr_in[0]   | scb[2].i2c_scl:0 | scb[0].spi_select1:0 |

| P0.1 |                           | scb[2].uart_rts:0 | pass.tr_sar_out               | tcpwm.tr_in[1]   | scb[2].i2c_sda:0 | scb[0].spi_select2:0 |

| P0.2 |                           |                   | pass.dsi_sar_sam<br>ple_done  |                  |                  | scb[0].spi_select3:0 |

| P0.4 |                           |                   | pass.dsi_sar_data<br>[0]:0    | scb[2].uart_rx:0 |                  |                      |

| P0.5 |                           |                   | pass.dsi_sar_data<br>[1]:0    | scb[2].uart_tx:0 |                  |                      |

| P0.6 | srss.ext_clk              |                   |                               | scb[2].uart_tx:1 |                  |                      |

| P1.0 | tcpwm.line[2]:1           | scb[0].uart_rx:1  |                               |                  | scb[0].i2c_scl:0 | scb[0].spi_mosi:1    |

| P1.1 | tcpwm.line_compl<br>[2]:1 | scb[0].uart_tx:1  |                               |                  | scb[0].i2c_sda:0 | scb[0].spi_miso:1    |

| P1.2 | tcpwm.line[3]:1           | scb[0].uart_cts:1 | pass.dsi_sar_data<br>[3]:0    | tcpwm.tr_in[2]   | scb[2].i2c_scl:1 | scb[0].spi_clk:1     |

| P1.3 | tcpwm.line_compl<br>[3]:1 | scb[0].uart_rts:1 | pass.dsi_sar_data<br>[4]:0    | tcpwm.tr_in[3]   | scb[2].i2c_sda:1 | scb[0].spi_select0:1 |

| P1.7 |                           |                   |                               |                  |                  | scb[2].spi_clk       |

| P3.2 | tcpwm.line[1]:0           |                   |                               |                  | cpuss.swd_data   |                      |

| P3.3 | tcpwm.line_compl<br>[1]:0 |                   |                               |                  | cpuss.swd_clk    |                      |

| P3.6 | tcpwm.line[3]:0           |                   | pass.dsi_ctb_cmp<br>0         |                  |                  |                      |

| P3.7 | tcpwm.line_compl<br>[3]:0 |                   | pass.dsi_ctb_cmp<br>1         |                  | lpcomp.comp[1]:1 | scb[2].spi_miso      |

| P4.0 |                           | scb[0].uart_rx:0  | pass.dsi_sar_data<br>[9]:0    |                  | scb[0].i2c_scl:1 | scb[0].spi_mosi:0    |

| P4.1 |                           | scb[0].uart_tx:0  |                               |                  | scb[0].i2c_sda:1 | scb[0].spi_miso:0    |

| P4.2 |                           | scb[0].uart_cts:0 | pass.dsi_sar_data<br>[10]:0   |                  | lpcomp.comp[0]:0 | scb[0].spi_clk:0     |

| P4.3 |                           | scb[0].uart_rts:0 | pass.dsi_sar_data<br>[11]:0   |                  | lpcomp.comp[1]:0 | scb[0].spi_select0:0 |

### **PINOUT DRAWING**

Figure 2. Pinout Drawing (Top View)

### **SPECIFICATIONS**

Table 3. ABSOLUTE MAXIMUM RATINGS (Note 1)

| Symbol           | Description                                    | Condition                     | Min   | Max        | Units |

|------------------|------------------------------------------------|-------------------------------|-------|------------|-------|

| VDDD             | Supply voltage                                 |                               | -0.5  | 5.5        | V     |

| IDD              | Supply current                                 |                               |       | 200        | mA    |

| P <sub>tot</sub> | Total power consumption                        |                               |       | 800        | mW    |

| P <sub>i</sub>   | Absolute maximum input power at receiver input | ANTP and ANTN pins in RX mode |       | 10         | dBm   |

| I <sub>I1</sub>  | DC current into pin SYSCLK                     |                               | -10   | 10         | mA    |

| I <sub>I2</sub>  | DC current into GPIO                           |                               | -25   | 25         | mA    |

| I <sub>I3</sub>  | DC current into pins ANTP, ANTN, ANTP1         |                               | -100  | 100        | mA    |

| V <sub>ia</sub>  | Input voltage ANTP, ANTN, ANTP1 pins           |                               | -0.5  | 5.5        | V     |

|                  | Input voltage GPIO pins                        |                               | -0.5  | VDDD + 0.5 | V     |

| V <sub>es</sub>  | Electrostatic handling                         | НВМ                           | -2000 | 2000       | V     |

| Lu               | GPIO pin current for latch-up                  |                               | -140  | 140        | mA    |

| T <sub>amb</sub> | Operating temperature                          |                               | -40   | 85         | °C    |

| T <sub>stg</sub> | Storage temperature                            |                               | -65   | 150        | °C    |

| Tj               | Junction Temperature                           |                               |       | 150        | °C    |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

### **DC Characteristics**

**Table 4. SUPPLIES**

| Sym                  | Description                                                                | Condition                                                                                                                                                          | Min | Тур | Max | Units |

|----------------------|----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| T <sub>AMB</sub>     | Operational ambient temperature                                            |                                                                                                                                                                    | -40 | 27  | 85  | °C    |

| VDDD                 | I/O and voltage regulator supply voltage                                   |                                                                                                                                                                    | 1.8 | 3.0 | 3.6 | V     |

| IDDsleep1            | Sleep mode<br>I <sup>2</sup> C wakeup, WDT and Comparators on              | 6 MHz. Max is at 85°C and 3.6 V                                                                                                                                    |     | 1.7 |     | mA    |

| IDDsleep2            | Sleep mode<br>I <sup>2</sup> C wakeup, WDT and Comparators on              | 12 MHz. Max is at 85°C and 3.6 V                                                                                                                                   |     | 2.2 |     | mA    |

| IDDdeep-<br>sleep    | Deep Sleep current I <sup>2</sup> C wakeup and WDT on                      | Max is at 85°C and 3.6 V                                                                                                                                           |     | 2.5 |     | μΑ    |

| IDD6                 | CPU at 6 MHz, execute from flash                                           | Max is at 85°C and 3.6 V                                                                                                                                           |     | 1.8 |     | mA    |

| IDD24                | CPU at 24 MHz, execute from flash                                          | Max is at 85°C and 3.6 V                                                                                                                                           |     | 3.0 |     | mA    |

| IDD48                | CPU at 48 MHz, execute from flash                                          | Max is at 85°C and 3.6 V                                                                                                                                           |     | 5.4 |     | mA    |

| IDDxres              | Supply current while XRES asserted                                         |                                                                                                                                                                    |     | 2   |     | mA    |

| I <sub>RX</sub>      | Current consumption RX                                                     | 868 MHz, datarate 6 kbps                                                                                                                                           |     | 9.5 |     | mA    |

|                      | RF frequency generation subsystem:<br>Internal VCO and internal loop-fiter | 169 MHz, datarate 6 kbps                                                                                                                                           |     | 6.5 |     |       |

|                      | ·                                                                          | 868 MHz, datarate 100 kbps                                                                                                                                         |     | 11  |     |       |

|                      |                                                                            | 169 MHz, datarate 100 kbps                                                                                                                                         |     | 7.5 |     |       |

| I <sub>TX-DIFF</sub> | Current consumption TX differential                                        | 868 MHz, 15 dBm, CW, Note 2 RF frequency generation subsystem: Internal VCO and internal loop-filter Antenna configuration: Differential PA, internal RX/TX switch |     | 55  |     | mA    |

<sup>2.</sup> Measured with optimized matching networks.

<sup>1.</sup> Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

**Table 4. SUPPLIES**

| Sym              | Description                              | Condition                                                                                                                                                             | Min | Тур | Max | Units |

|------------------|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| ltx_se           | Current consumption TX single ended      | 868 MHz, 0 dBm, FSK, Note 2 RF frequency generation subsystem: Internal VCO and internal loop-filter Antenna configuration: Single ended PA, external RX/TX switching |     | 7.6 |     | mA    |

| I <sub>WOR</sub> | Typical wake-on-radio duty cycle current | 1 s, 100 kbps                                                                                                                                                         |     | 6   |     | μА    |

<sup>2.</sup> Measured with optimized matching networks.

For information on current consumption in complex modes of operation tailored to your application, see the software AX-RadioLab.

Both AXM0F243 power amplifiers run from the regulated VDDA supply and not directly from the battery. This has the advantage that the current and output power do not vary much over supply voltage and temperature.

**Table 5. AC SPECIFICATIONS**

| Parameter                  | Description                     | Min | Тур | Max | Units | Details/<br>Conditions |

|----------------------------|---------------------------------|-----|-----|-----|-------|------------------------|

| F <sub>CPU</sub>           | CPU frequency                   | DC  | -   | 48  | MHz   |                        |

| T <sub>SLEEP</sub> [3]     | CPU Wakeup from Sleep mode      | -   | 0   | -   | μs    |                        |

| T <sub>DEEPSLEEP</sub> [3] | CPU Wakeup from Deep Sleep mode | =   | 35  | =   |       |                        |

<sup>3.</sup> Guaranteed by characterization.

### **GPIO**

**Table 6. GPIO DC SPECIFICATIONS**

| Parameter           | Description                               | Min                     | Тур | Max                    | Units | Details/ Conditions                              |

|---------------------|-------------------------------------------|-------------------------|-----|------------------------|-------|--------------------------------------------------|

| V <sub>IH</sub> [4] | Input voltage high threshold              | 0.7 x V <sub>DDD</sub>  | -   | =                      | V     | CMOS Input                                       |

| VIL                 | Input voltage low threshold               | =                       | -   | 0.3 x V <sub>DDD</sub> |       | CMOS Input                                       |

| V <sub>IH</sub> [4] | LVTTL input, V <sub>DDD</sub> < 2.7 V     | 0.7 x V <sub>DDD</sub>  | -   | =                      |       | =                                                |

| V <sub>IL</sub>     | LVTTL input, V <sub>DDD</sub> < 2.7 V     | _                       | -   | 0.3 x V <sub>DDD</sub> |       | _                                                |

| V <sub>IH</sub> [4] | LVTTL input, V <sub>DDD</sub> ≥ 2.7 V     | 2.0                     | -   | =                      |       | -                                                |

| VIL                 | LVTTL input, V <sub>DDD</sub> ≥ 2.7 V     | -                       | -   | 0.8                    |       | =                                                |

| Vон                 | Output voltage high level                 | V <sub>DDD</sub> – 0.6  | -   | =                      |       | I <sub>OH</sub> = 4 mA at 3 V V <sub>DDD</sub>   |

| Vон                 | Output voltage high level                 | V <sub>DDD</sub> - 0.5  | =   | =                      |       | I <sub>OH</sub> = 1 mA at 1.8 V V <sub>DDD</sub> |

| Vol                 | Output voltage low level                  | =                       | -   | 0.6                    |       | $I_{OL} = 4 \text{ mA}$ at 1.8 V $V_{DDD}$       |

| VoL                 | Output voltage low level                  | _                       | -   | 0.6                    |       | I <sub>OL</sub> = 10 mA at 3 V V <sub>DDD</sub>  |

| Vol                 | Output voltage low level                  | =                       | =   | 0.4                    |       | I <sub>OL</sub> = 3 mA at 3 V V <sub>DDD</sub>   |

| RPULLUP             | Pull-up resistor                          | 3.5                     | 5.6 | 8.5                    | kΩ    | _                                                |

| RPULLDOWN           | Pull-down resistor                        | 3.5                     | 5.6 | 8.5                    |       | =                                                |

| lıL                 | Input leakage current (absolute value)    | _                       | -   | 1                      | μΑ    | 25°C, V <sub>DDD</sub> = 3.0 V                   |

| Cin                 | Input capacitance                         | _                       | -   | 7                      | pF    | _                                                |

| VHYSTTL [5]         | Input hysteresis LVTTL                    | 25                      | 40  | -                      | mV    | V <sub>DDD</sub> ≥ 2.7 V                         |

| VHYSCMOS [5]        | Input hysteresis CMOS                     | 0.05 x V <sub>DDD</sub> | -   | -                      |       |                                                  |

| ITOT_GPIO [5]       | Maximum total source or sink chip current | =                       | -   | 200                    | mA    | -                                                |

V<sub>IH</sub> must not exceed V<sub>DDD</sub> + 0.2 V

Guaranteed by characterization.

### Table 7. GPIO AC SPECIFICATIONS \*

| Parameter | Description                                                                   | Min | Тур | Max  | Units | Details/ Conditions                     |

|-----------|-------------------------------------------------------------------------------|-----|-----|------|-------|-----------------------------------------|

| TRISEF    | Rise time in fast strong mode                                                 | 2   | =   | 12   | ns    | 3.3 V V <sub>DDD</sub> , Cload = 25 pF  |

| TFALLF    | Fall time in fast strong mode                                                 | 2   | _   | 12   |       | 3.3 V V <sub>DDD</sub> , Cload = 25 pF  |

| TRISES    | Rise time in slow strong mode                                                 | 10  | _   | 60   | _     | 3.3 V V <sub>DDD</sub> , Cload = 25 pF  |

| TFALLS    | Fall time in slow strong mode                                                 | 10  | -   | 60   | -     | 3.3 V V <sub>DDD</sub> , Cload = 25 pF  |

| FGPIOUT1  | GPIO $F_{OUT}$ , 3.3 $V \le V_{DDD} \le 3.6 V$<br>Fast strong mode            | -   | _   | 33   | MHz   | 90/10%, 25 pF load,<br>60/40 duty cycle |

| FGPIOUT2  | GPIO F <sub>OUT</sub> ; 1.8 V ≤ V <sub>DDD</sub> ≤ 3.3 V<br>Fast strong mode  | -   | -   | 16.7 |       | 90/10%, 25 pF load,<br>60/40 duty cycle |

| FGPIOUT3  | GPIO $F_{OUT}$ ; 3.3 $V \le V_{DDD} \le 3.6 V$ Slow strong mode               | -   | -   | 7    |       | 90/10%, 25 pF load,<br>60/40 duty cycle |

| FGPIOUT4  | GPIO F <sub>OUT</sub> ; 1.8 V ≤ V <sub>DDD</sub> ≤ 3.3 V<br>Slow strong mode  | -   | =   | 3.5  |       | 90/10%, 25 pF load,<br>60/40 duty cycle |

| FGPIOIN   | GPIO input operating frequency;<br>1.8 V $\leq$ V <sub>DDD</sub> $\leq$ 3.6 V | _   | =   | 48   |       | 90/10% V <sub>IO</sub>                  |

<sup>\*</sup>Guaranteed by characterization.

### **XRES**

### **Table 8. XRES DC SPECIFICATIONS**

| Parameter    | Description                  | Min                    | Тур | Max                    | Units | Details/ Conditions |

|--------------|------------------------------|------------------------|-----|------------------------|-------|---------------------|

| VIH          | Input voltage high threshold | 0.7 x V <sub>DDD</sub> | =   | =                      | V     | CMOS Input          |

| VIL          | Input voltage low threshold  | =                      | -   | 0.3 x V <sub>DDD</sub> |       | CMOS Input          |

| RPULLUP      | Pull-up resistor             | _                      | 60  | -                      | kΩ    |                     |

| Cin          | Input capacitance            | =                      | -   | 7                      | pF    |                     |

| VHYSXRES [6] | Input voltage hysteresis     | _                      | 100 | -                      | mV    |                     |

### **Table 9. XRES AC SPECIFICATIONS**

| Parameter       | Description                     | Min | Тур | Max | Units | Details/ Conditions |

|-----------------|---------------------------------|-----|-----|-----|-------|---------------------|

| TRESETWIDTH [6] | Reset pulse width               | 1   | _   | -   | μs    |                     |

| TRESETWAKE [6]  | Wake-up time from reset release | -   | _   | 2.7 | ms    |                     |

<sup>6.</sup> Guaranteed by characterization.

### Table 10. SYSCLK DC SPECIFICATIONS

| Parameter | Description                  | Min | Тур | Max | Units | Details/ Conditions                |

|-----------|------------------------------|-----|-----|-----|-------|------------------------------------|

| VIL       | Input voltage low threshold  | =   | =   | 0.8 | V     | at 3.3 V VDDD                      |

| VIH       | Input voltage high threshold | 2.0 | -   | =   | V     | at 3.3 V VDDD                      |

| RPULLUP   | Pull-up resistor             | -   | 65  | -   | kΩ    |                                    |

| Vol       | Output voltage low level     | =   | -   | 0.4 | V     | I <sub>OL</sub> = 4 mA at 3 V VDDD |

| Vон       | Output voltage high level    | 2.4 | -   | _   | V     | I <sub>OH</sub> = 4 mA at 3 V VDDD |

### **Analog Peripherals**

### **Table 11. CTBm OPAMP SPECIFICATIONS**

| Parameter    | Description                        | Min | Тур  | Max | Units | Details/ Conditions                      |

|--------------|------------------------------------|-----|------|-----|-------|------------------------------------------|

| IDD          | Opamp block current, External load |     |      |     |       |                                          |

| IDD_HI       | power=hi                           | _   | 1100 | -   | μΑ    | _                                        |

| IDD_MED      | power=med                          | _   | 550  | -   |       | -                                        |

| IDD_LOW      | power=lo                           | -   | 150  | -   |       | _                                        |

| Gвw          | Load = 20 pF, 0.1 mA VDDD = 2.7 V  |     |      |     |       |                                          |

| Gвw_нı       | power=hi                           | 6   | -    | _   | MHz   | Input and output are 0.2 V to VDDD-0.2 V |

| GBW_MED      | power=med                          | 3   | -    | _   |       | Input and output are 0.2 V to VDDD-0.2 V |

| GBW_LO       | power=lo                           | =   | 1    | =   |       | Input and output are 0.2 V to VDDD-0.2 V |

| IOUT_MAX     | VDDD = 2.7 V, 500 mV from rail     |     |      |     |       |                                          |

| IOUT_MAX_HI  | power=hi                           | 10  | -    | -   | mA    | Output is 0.5 V<br>VDDD-0.5 V            |

| IOUT_MAX_MID | power=mid                          | 10  | -    | _   |       | Output is 0.5 V<br>VDDD-0.5 V            |

| lout_max_lo  | power=lo                           | -   | 5    | _   |       | Output is 0.5 V<br>VDDD-0.5 V            |

| Іоит         | VDDD = 1.8 V, 500 mV from rail     |     |      |     |       |                                          |

**Table 11. CTBm OPAMP SPECIFICATIONS**

| Parameter    | Description                                              | Min   | Тур  | Max       | Units | Details/ Conditions                                                           |

|--------------|----------------------------------------------------------|-------|------|-----------|-------|-------------------------------------------------------------------------------|

| lout_max_hi  | power=hi                                                 | 4     | -    | -         |       | Output is 0.5 V<br>VDDD-0.5 V                                                 |

| IOUT_MAX_MID | power=mid                                                | 4     | _    | _         | mA    | Output is 0.5 V<br>VDDD-0.5 V                                                 |

| IOUT_MAX_LO  | power=lo                                                 | _     | 2    | -         |       | Output is 0.5 V<br>VDDD-0.5 V                                                 |

| IDD_Int      | Opamp block current Internal Load                        |       |      |           |       |                                                                               |

| IDD_HI_Int   | power=hi                                                 | -     | 1500 | -         | μΑ    | _                                                                             |

| IDD_MED_Int  | power=med                                                | _     | 700  | -         |       | _                                                                             |

| IDD_LOW_Int  | power=lo                                                 | -     | _    | -         |       | _                                                                             |

| Gвw          | VDDD = 2.7 V                                             | -     | -    | _         |       | _                                                                             |

| GBW_HI_Int   | power=hi                                                 | 8     | _    | _         | MHz   | Output is 0.25 V to VDDD-0.25 V                                               |

|              | General opamp specs for both internal and external modes |       |      |           |       |                                                                               |

| Vin          | Charge-pump on, VDDD = 2.7 V                             | -0.05 | -    | VDDD-0.2  | V     | _                                                                             |

| Vсм          | Charge-pump on, VDDD = 2.7 V                             | -0.05 | _    | VDDD-0.2  |       | _                                                                             |

| Vouт         | VDDD = 2.7 V                                             |       |      |           |       |                                                                               |

| Vout_1       | power=hi, Iload=10 mA                                    | 0.5   | _    | VDDD -0.5 | V     | _                                                                             |

| Vout_2       | power=hi, Iload=1 mA                                     | 0.2   | -    | VDDD -0.2 |       | _                                                                             |

| Vоит_з       | power=med, Iload=1 mA                                    | 0.2   | -    | VDDD -0.2 |       | _                                                                             |

| Vout_4       | power=lo, Iload=0.1 mA                                   | 0.2   | -    | VDDD -0.2 |       | -                                                                             |

| Vos_tr       | Offset voltage, trimmed                                  | -1.0  | ±0.5 | 1.0       | mV    | High mode, input 0 V to VDDD-0.2 V                                            |

| Vos_tr       | Offset voltage, trimmed                                  | _     | ±1   | -         |       | Medium mode, input 0 V to VDDD-0.2 V                                          |

| Vos_tr       | Offset voltage, trimmed                                  | =     | ±2   | -         |       | Low mode, input 0 V to VDDD-0.2 V                                             |

| Vos_dr_tr    | Offset voltage drift, trimmed                            | -10   | ±3   | 10        | μV/C  | High mode                                                                     |

| Vos_dr_tr    | Offset voltage drift, trimmed                            | -     | ±10  | _         | μV/C  | Medium mode                                                                   |

| Vos_dr_tr    | Offset voltage drift, trimmed                            | _     | ±10  | -         |       | Low mode                                                                      |

| CMRR         | DC                                                       | 70    | 80   | -         | dB    | Input is 0 V to VDDD-0.2<br>V, Output is 0.2 V to<br>VDDD-0.2 V               |

| PSRR         | At 1 kHz, 10-mV ripple                                   | 70    | 85   | _         |       | V <sub>DDD</sub> = 3.6 V, high–power<br>mode, input is 0.2 V to<br>VDDD–0.2 V |

**Table 11. CTBm OPAMP SPECIFICATIONS**

| Parameter          | Description                                                                  | Min | Тур  | Max | Units   | Details/ Conditions                         |

|--------------------|------------------------------------------------------------------------------|-----|------|-----|---------|---------------------------------------------|

| Noise              |                                                                              |     |      |     |         |                                             |

| VN2                | Input-referred, 1 kHz, power=Hi                                              | _   | 72   | -   | nV/rtHz | 3                                           |

| VN3                | Input-referred, 10 kHz, power=Hi                                             | _   | 28   | -   |         | Input and output are at 0.2 V to VDDD-0.2 V |

| VN4                | Input-referred, 100 kHz, power=Hi                                            | -   | 15   | ı   |         | Input and output are at 0.2 V to VDDD-0.2 V |

| CLOAD              | Stable up to max. load. Performance specs at 50 pF.                          | -   | -    | 125 | pF      | _                                           |

| SLEW_RATE          | Cload = 50 pF, Power = High, VDDD = 2.7 V                                    | 6   | _    | -   | V/μs    | _                                           |

| T_OP_WAKE          | From disable to enable, no external RC dominating                            | =   | -    | 25  | μs      | =                                           |

| OL_GAIN            | Open Loop Gain                                                               | _   | 90   | ı   | dB      |                                             |

| COMP_MODE          | Comparator mode; 50 mV drive, T <sub>rise</sub> =T <sub>fall</sub> (approx.) |     |      |     |         |                                             |

| TPD1               | Response time; power=hi                                                      | _   | 150  | -   | ns      | Input is 0.2 V to<br>VDDD-0.2 V             |

| TPD2               | Response time; power=med                                                     | -   | 500  | -   |         | Input is 0.2 V to<br>VDDD-0.2 V             |

| TPD3               | Response time; power=lo                                                      | -   | 2500 | -   |         | Input is 0.2 V to<br>VDDD-0.2 V             |

| VHYST_OP           | Hysteresis                                                                   | _   | 10   | =   | mV      | _                                           |

| WUP_CTB            | Wake-up time from Enabled to Usable                                          | _   | _    | 25  | μs      | _                                           |

| Deep Sleep<br>Mode | Mode 2 is lowest current range. Mode 1 has higher GBW.                       |     |      |     |         |                                             |

| IDD_HI_M1          | Mode 1, High current                                                         | _   | 1400 | I   | μΑ      | 25°C                                        |

| IDD_MED_M1         | Mode 1, Medium current                                                       | _   | 700  | -   |         | 25°C                                        |

| IDD_LOW_M1         | Mode 1, Low current                                                          | _   | 200  | =   |         | 25°C                                        |

| Idd_hi_m2          | Mode 2, High current                                                         | _   | 120  | -   |         | 25°C                                        |

| IDD_MED_M2         | Mode 2, Medium current                                                       | _   | 60   | _   |         | 25°C                                        |

| IDD_LOW_M2         | Mode 2, Low current                                                          | _   | 15   | -   |         | 25°C                                        |

**Table 11. CTBm OPAMP SPECIFICATIONS**

| Parameter   | Description            | Min | Тур | Max | Units | Details/ Conditions                           |

|-------------|------------------------|-----|-----|-----|-------|-----------------------------------------------|

| Gвw_ні_м1   | Mode 1, High current   | -   | 4   | _   | MHz   | 20-pF load, no DC load<br>0.2 V to VDDD-0.2 V |

| GBW_MED_M1  | Mode 1, Medium current | -   | 2   | -   |       | 20-pF load, no DC load<br>0.2 V to VDDD-0.2 V |

| GBW_LOW_M1  | Mode 1, Low current    | -   | 0.5 | -   |       | 20-pF load, no DC load<br>0.2 V to VDDD-0.2 V |

| Gвw_ні_м2   | Mode 2, High current   | -   | 0.5 | _   |       | 20-pF load, no DC load<br>0.2 V to VDDD-0.2 V |

| GBW_MED_M2  | Mode 2, Medium current | -   | 0.2 | -   |       | 20-pF load, no DC load<br>0.2 V to VDDD-0.2 V |

| GBW_Low_M2  | Mode 2, Low current    | -   | 0.1 | =   |       | 20-pF load, no DC load<br>0.2 V to VDDD-0.2 V |

| Vos_HI_M1   | Mode 1, High current   | -   | 5   | -   | mV    | With trim 25°C, 0.2 V to VDDD-0.2 V           |

| Vos_med_m1  | Mode 1, Medium current | _   | 5   | -   |       | With trim 25°C, 0.2 V to VDDD-0.2 V           |

| Vos_low_m2  | Mode 1, Low current    | _   | 5   | _   |       | With trim 25°C, 0.2 V to VDDD-0.2 V           |

| Vos_HI_M2   | Mode 2, High current   | _   | 5   | _   |       | With trim 25°C, 0.2V to VDDD-0.2 V            |

| Vos_med_m2  | Mode 2, Medium current | _   | 5   | _   |       | With trim 25°C, 0.2 V to VDDD-0.2 V           |

| Vos_Low_M2  | Mode 2, Low current    | -   | 5   | -   |       | With trim 25°C, 0.2 V to VDDD-0.2 V           |

| Іоит_ні_м!  | Mode 1, High current   | -   | 10  | -   | mA    | Output is 0.5 V to<br>VDDD-0.5 V              |

| IOUT_MED_M1 | Mode 1, Medium current | -   | 10  | -   |       | Output is 0.5 V to<br>VDDD-0.5 V              |

| IOUT_LOW_M1 | Mode 1, Low current    | _   | 4   | _   |       | Output is 0.5 V to<br>VDDD-0.5 V              |

| IOUT_HI_M2  | Mode 2, High current   | -   | 1   | -   |       |                                               |

| lou_med_m2  | Mode 2, Medium current | _   | 1   | -   |       |                                               |

| lou_low_m2  | Mode 2, Low current    | =   | 0.5 | _   |       |                                               |

**Table 12. COMPARATOR DC SPECIFICATIONS**

| Parameter | Description                                       | Min | Тур | Max                    | Units | Details/ Conditions                  |

|-----------|---------------------------------------------------|-----|-----|------------------------|-------|--------------------------------------|

| Voffset1  | Input offset voltage, Factory trim                | =   | -   | ±10                    | mV    |                                      |

| VOFFSET2  | Input offset voltage, Custom trim                 | =   | -   | ±4                     |       |                                      |

| VHYST     | Hysteresis when enabled                           | _   | 10  | 35                     |       |                                      |

| VICM1     | Input common mode voltage in normal mode          | 0   | _   | V <sub>DDD</sub> -0.1  | V     | Modes 1 and 2                        |

| VICM2     | Input common mode voltage in low power mode       | 0   | _   | $V_{DDD}$              |       |                                      |

| Vісмз     | Input common mode voltage in ultra low power mode | 0   | _   | V <sub>DDD</sub> -1.15 |       | V <sub>DDD</sub> ≥ 2.2 V at<br>–40°C |

### **Table 12. COMPARATOR DC SPECIFICATIONS**

| CMRR          | Common mode rejection ratio           | 50 | ı | I   | dB        | $V_{DDD} \ge 2.7 \text{ V}$          |

|---------------|---------------------------------------|----|---|-----|-----------|--------------------------------------|

| CMRR          | Common mode rejection ratio           | 42 |   | =   |           | $V_{DDD} \le 2.7 \text{ V}$          |

| ICMP1         | Block current, normal mode            | =  |   | 400 | μΑ        |                                      |

| Ісмр2         | Block current, low power mode         | =  | - | 100 |           |                                      |

| <b>І</b> СМР3 | Block current in ultra low-power mode | _  |   | 6   |           | V <sub>DDD</sub> ≥ 2.2 V at<br>–40°C |

| ZсмР          | DC Input impedance of comparator      | 35 | - | -   | $M\Omega$ |                                      |

### **Table 13. COMPARATOR AC SPECIFICATIONS**

| Parameter | Description                                           | Min | Тур | Max | Units | Details/ Conditions                  |

|-----------|-------------------------------------------------------|-----|-----|-----|-------|--------------------------------------|

| TRESP1    | Response time, normal mode, 50 mV overdrive           | -   | 38  | 110 | ns    |                                      |

| TRESP2    | Response time, low power mode, 50 mV overdrive        | =   | 70  | 200 |       |                                      |

| TRESP3    | Response time, ultra-low power mode, 200 mV overdrive | ı   | 2.3 | 15  | μs    | V <sub>DDD</sub> ≥ 2.2 V at<br>-40°C |

### Table 14. TEMPERATURE SENSOR SPECIFICATIONS

| Parameter | Description                 | Min        | Тур | Max | Units | Details/ Conditions |

|-----------|-----------------------------|------------|-----|-----|-------|---------------------|

| TSENSACC  | Temperature sensor accuracy | <b>-</b> 5 | ±1  | 5   | °C    | −40 to +85°C        |

### **Table 15. SAR SPECIFICATIONS**

| Parameter  | Description                                                          | Min  | Тур | Max      | Units | Details/ Conditions                       |

|------------|----------------------------------------------------------------------|------|-----|----------|-------|-------------------------------------------|

| SAR ADC DC | Specifications                                                       |      |     |          |       | <u>'</u>                                  |

| A_RES      | Resolution                                                           | _    | _   | 12       | bits  |                                           |

| A-MONO     | Monotonicity                                                         | _    | _   | -        |       | Yes.                                      |

| A_GAINERR  | Gain error                                                           | -    | _   | ±0.1     | %     | With external reference.                  |

| A_OFFSET   | Input offset voltage                                                 | -    | -   | 2        | mV    | Measured with 1–V reference               |

| A_ISAR     | Current consumption                                                  | _    | _   | 1        | mA    |                                           |

| A_VINS     | Input voltage range – single ended                                   | Vss  | _   | VDDD     | V     |                                           |

| A_VIND     | Input voltage range – differential[                                  | Vss  | _   | VDDD     | V     |                                           |

| A_INRES    | Input resistance                                                     | _    | _   | 2.2      | ΚΩ    |                                           |

| A_INCAP    | Input capacitance                                                    | _    | _   | 10       | pF    |                                           |

| SAR ADC AC | Specifications                                                       |      | •   |          |       |                                           |

| A_PSRR     | Power supply rejection ratio                                         | 70   | _   | =        | dB    |                                           |

| A_CMRR     | Common mode rejection ratio                                          | 66   | _   |          | dB    | Measured at 1 V                           |

| A_SAMP     | Sample rate                                                          | =    | _   | 1        | Msps  |                                           |

| A_SNR      | Signal-to-noise and distortion ratio (SINAD)                         | 65   | _   | -        | dB    | F <sub>IN</sub> = 10 kHz                  |

| A_BW       | Input bandwidth without aliasing                                     | -    | _   | A_samp/2 | kHz   |                                           |

| A_INL      | Integral non linearity V <sub>DD</sub> = 1.8 V to 3.6 V, 1 Msps      | -1.7 | _   | 2        | LSB   | V <sub>REF</sub> = 1 V to V <sub>DD</sub> |

| A_INL      | Integral non linearity. V <sub>DD</sub> = 1.8 V to 3.6 V, 1 Msps     | -1.5 | _   | 1.7      | LSB   | $V_{REF} = 1.8 \text{ V to } V_{DD}$      |

| A_INL      | Integral non linearity. V <sub>DD</sub> = 1.8 V to 3.6 V, 500 ksps   | -1.5 | _   | 1.7      | LSB   | $V_{REF} = 1 \text{ V to } V_{DD}$        |

| A_DNL      | Differential non linearity. V <sub>DD</sub> = 1.8 V to 3.6 V, 1 Msps | -1   | _   | 2.2      | LSB   | V <sub>REF</sub> = 1 V to V <sub>DD</sub> |

### **Table 15. SAR SPECIFICATIONS**

| A_DNL       | Differential non linearity. V <sub>DD</sub> = 1.8 V to 3.6 V, 1 Msps   | -1 | _ | 2               | LSB  | $V_{REF} = 1.8 \text{ V to } V_{DD}$ |

|-------------|------------------------------------------------------------------------|----|---|-----------------|------|--------------------------------------|

| A_DNL       | Differential non linearity. V <sub>DD</sub> = 1.8 V to 3.6 V, 500 ksps | -1 | _ | 2.2             | LSB  | $V_{REF} = 1 \text{ V to } V_{DD}$   |

| A_THD       | Total harmonic distortion                                              | -  | - | <del>-</del> 65 | dB   | Fin = 10 kHz                         |

| FSARINTRE F | SAR operating speed without external ref. bypass                       | _  | _ | 100             | ksps | 12-bit resolution                    |

### Table 16. CSD AND IDAC SPECIFICATIONS

| Parameter      | Description                                                        | Min | Тур | Max        | Units | Details / Conditions                                                                                                                                                                      |

|----------------|--------------------------------------------------------------------|-----|-----|------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDD_RIPPLE     | Max allowed ripple on power supply, DC to 10 MHz                   | _   | _   | ±50        | mV    | V <sub>DD</sub> > 2 V (with ripple),<br>25°C T <sub>A</sub> , Sensitivity =<br>0.1 pF                                                                                                     |

| VDD_RIPPLE_1.8 | Max allowed ripple on power supply, DC to 10 MHz                   | -   | _   | ±25        | mV    | $\begin{split} &V_{DD} > 1.75 \text{ V (with ripple)}, \\ &25^{\circ}\text{C T}_{A}, \text{ Parasitic Capacitance } (C_{P}) < 20 \text{ pF, Sensitivity} \geq 0.4 \text{ pF} \end{split}$ |

| ICSD           | Maximum block current                                              | -   | _   | 4000       | μΑ    | Maximum block current for both IDACs in dynamic (switching) mode including comparators, buffer, and reference generator.                                                                  |

| VREF           | Voltage reference for CSD and Comparator                           | 0.6 | 1.2 | VDDD - 0.6 | V     | VDDD – 0.06 or 4.4,<br>whichever is lower                                                                                                                                                 |

| VREF_EXT       | External Voltage reference for CSD and Comparator                  | 0.6 |     | VDDD - 0.6 | V     | VDDD – 0.06 or 4.4,<br>whichever is lower                                                                                                                                                 |

| IDAC1IDD       | IDAC1 (7-bits) block current                                       | -   | _   | 1750       | μΑ    |                                                                                                                                                                                           |

| IDAC2IDD       | IDAC2 (7-bits) block current                                       | -   | -   | 1750       | μΑ    |                                                                                                                                                                                           |

| VCSD           | Voltage range of operation                                         | 1.8 | _   | 3.6        | V     |                                                                                                                                                                                           |

| VCOMPIDAC      | Voltage compliance range of IDAC                                   | 0.6 | _   | VDDD-0.6   | V     | VDDD – 0.06 or 4.4,<br>whichever is lower                                                                                                                                                 |

| IDAC1DNL       | DNL                                                                | -1  | -   | 1          | LSB   |                                                                                                                                                                                           |

| IDAC1INL       | INL                                                                | -2  | _   | 2          | LSB   | INL is ±5.5 LSB for VDDD < 2 V                                                                                                                                                            |

| IDAC2DNL       | DNL                                                                | -1  | -   | 1          | LSB   |                                                                                                                                                                                           |

| IDAC2INL       | INL                                                                | -2  | _   | 2          | LSB   | INL is ±5.5 LSB for VDDD < 2 V                                                                                                                                                            |

| SNR            | Ratio of counts of finger to noise. Guaranteed by characterization | 5   | _   | _          | Ratio | Capacitance range of 5 to 35 pF, 0.1–pF sensitivity. All use cases. VDDD > 2 V.                                                                                                           |

| IDAC1CRT1      | Output current of IDAC1 (7 bits) in low range                      | 4.2 | _   | 5.4        | μΑ    | LSB = 37.5-nA typ.                                                                                                                                                                        |

| IDAC1CRT2      | Output current of IDAC1(7 bits) in medium range                    | 34  | =   | 41         | μΑ    | LSB = 300-nA typ.                                                                                                                                                                         |

| IDAC1CRT3      | Output current of IDAC1(7 bits) in high range                      | 275 | _   | 330        | μΑ    | LSB = 2.4-μA typ.                                                                                                                                                                         |

| IDAC1CRT12     | Output current of IDAC1 (7 bits) in low range, 2X mode             | 8   | -   | 10.5       | μΑ    | LSB = 75-nA typ.                                                                                                                                                                          |

| IDAC1CRT22     | Output current of IDAC1(7 bits) in medium range, 2X mode           | 69  | =   | 82         | μΑ    | LSB = 600-nA typ.                                                                                                                                                                         |

| IDAC1CRT32     | Output current of IDAC1(7 bits) in high range, 2X mode             | 540 | _   | 660        | μΑ    | LSB = 4.8-μA typ.                                                                                                                                                                         |

| IDAC2CRT1      | Output current of IDAC2 (7 bits) in low range                      | 4.2 | =   | 5.4        | μΑ    | LSB = 37.5-nA typ.                                                                                                                                                                        |

Table 16. CSD AND IDAC SPECIFICATIONS

| Parameter     | Description                                              | Min | Тур | Max  | Units | Details / Conditions                                                        |

|---------------|----------------------------------------------------------|-----|-----|------|-------|-----------------------------------------------------------------------------|

| IDAC2CRT2     | Output current of IDAC2 (7 bits) in medium range         | 34  | _   | 41   | μΑ    | LSB = 300-nA typ.                                                           |

| IDAC2CRT3     | Output current of IDAC2 (7 bits) in high range           | 275 | =   | 330  | μΑ    | LSB = 2.4-μA typ.                                                           |

| IDAC2CRT12    | Output current of IDAC2 (7 bits) in low range, 2X mode   | 8   | =   | 10.5 | μΑ    | LSB = 75-nA typ.                                                            |

| IDAC2CRT22    | Output current of IDAC2(7 bits) in medium range, 2X mode | 69  | =   | 82   | μΑ    | LSB = 600-nA typ.                                                           |

| IDAC2CRT32    | Output current of IDAC2(7 bits) in high range, 2X mode   | 540 | -   | 660  | μΑ    | LSB = 4.8-μA typ.                                                           |

| IDAC3CRT13    | Output current of IDAC in 8-bit mode in low range        | 8   | =   | 10.5 | μΑ    | LSB = 37.5-nA typ.                                                          |

| IDAC3CRT23    | Output current of IDAC in 8-bit mode in medium range     | 69  | =   | 82   | μΑ    | LSB = 300-nA typ.                                                           |

| IDAC3CRT33    | Output current of IDAC in 8-bit mode in high range       | 540 | =   | 660  | μΑ    | LSB = 2.4-μA typ.                                                           |

| IDACOFFSET    | All zeroes input                                         | -   | -   | 1    | LSB   | Polarity set by Source or<br>Sink. Offset is 2 LSBs for<br>37.5 nA/LSB mode |

| IDACGAIN      | Full-scale error less offset                             | _   | -   | ±10  | %     |                                                                             |

| IDACMISMATCH1 | Mismatch between IDAC1 and IDAC2 in Low mode             | =   | =   | 9.2  | LSB   | LSB = 37.5-nA typ.                                                          |

| IDACMISMATCH2 | Mismatch between IDAC1 and IDAC2 in Medium mode          | =   | =   | 5.6  | LSB   | LSB = 300-nA typ.                                                           |

| IDACMISMATCH3 | Mismatch between IDAC1 and IDAC2 in High mode            | =   | =   | 6.8  | LSB   | LSB = 2.4-μA typ.                                                           |

| IDACSET8      | Settling time to 0.5 LSB for 8-bit IDAC                  | =   | =   | 10   | μs    | Full-scale transition. No external load.                                    |

| IDACSET7      | Settling time to 0.5 LSB for 7-bit IDAC                  | =   | =   | 10   | μs    | Full-scale transition. No external load.                                    |

| CMOD          | External modulator capacitor.                            | _   | 2.2 | -    | nF    | 5-V rating, X7R or NP0 cap.                                                 |

### Table 17. 10-BIT CSD ADC SPECIFICATIONS

| Parameter | Description                        | Min  | Тур | Max  | Units | Details/ Conditions                                                  |

|-----------|------------------------------------|------|-----|------|-------|----------------------------------------------------------------------|

| A_RES     | Resolution                         | -    | _   | 10   | bits  | Auto-zeroing is required every millisecond                           |

| A_CHNLS_S | Number of channels – single ended  | -    | _   | 16   |       | Defined by AMUX Bus.                                                 |

| A-MONO    | Monotonicity                       | -    | _   | _    | Yes   |                                                                      |

| A_GAINERR | Gain error                         | -    | _   | ±2   | %     | In $V_{REF}$ (2.4 V) mode with VDDD bypass capacitance of 10 $\mu F$ |

| A_OFFSET  | Input offset voltage               | -    | _   | 3    | mV    | In $V_{REF}$ (2.4 V) mode with VDDD bypass capacitance of 10 $\mu F$ |

| A_ISAR    | Current consumption                | =    | _   | 0.25 | mA    |                                                                      |

| A_VINS    | Input voltage range - single ended | Vssa | _   | VDDD | V     |                                                                      |

| A_INRES   | Input resistance                   | _    | 2.2 | _    | ΚΩ    |                                                                      |

| A_INCAP   | Input capacitance                  | _    | 20  | _    | pF    |                                                                      |

Table 17. 10-BIT CSD ADC SPECIFICATIONS

| Parameter | Description                                                                                            | Min | Тур | Max  | Units | Details/ Conditions                                                                         |

|-----------|--------------------------------------------------------------------------------------------------------|-----|-----|------|-------|---------------------------------------------------------------------------------------------|

| A_PSRR    | Power supply rejection ratio                                                                           | -   | 60  | _    | dB    | In V <sub>REF</sub> (2.4 V) mode with VDDD bypass capacitance of 10 μF                      |

| A_TACQ    | Sample acquisition time                                                                                | =   | 1   | =    | μs    |                                                                                             |

| A_CONV8   | Conversion time for 8-bit resolution at conversion rate = Fhclk/(2^(N+2)).  Clock frequency = 48 MHz.  | -   | -   | 21.3 | μs    | Does not include acquisition time. Equivalent to 44.8 ksps including acquisition time.      |

| A_CONV10  | Conversion time for 10-bit resolution at conversion rate = Fhclk/(2^(N+2)).  Clock frequency = 48 MHz. | -   | -   | 85.3 | μs    | Does not include acquisition time. Equivalent to 11.6 ksps including acquisition time.      |

| A_SND     | Signal-to-noise and Distortion ratio (SINAD)                                                           | =   | 61  | _    | dB    | With 10-Hz input sine<br>wave, external 2.4-V refer-<br>ence, V <sub>REF</sub> (2.4 V) mode |

| A_BW      | Input bandwidth without aliasing                                                                       | =   | -   | 22.4 | KHz   | 8-bit resolution                                                                            |

| A_INL     | Integral Non Linearity. 1 ksps                                                                         | II  | -   | 2    | LSB   | V <sub>REF</sub> = 2.4 V or greater                                                         |

| A_DNL     | Differential Non Linearity. 1 ksps                                                                     | =   | _   | 1    | LSB   |                                                                                             |

### **Digital Peripherals**

Timer Counter Pulse-Width Modulator (TCPWM)

**Table 18. TCPWM SPECIFICATIONS**

| Parameter             | Description                         | Min  | Тур | Max | Units | Details/ Conditions                                                                                     |

|-----------------------|-------------------------------------|------|-----|-----|-------|---------------------------------------------------------------------------------------------------------|

| ITCPWM1               | Block current consumption at 3 MHz  | -    | _   | 45  | μΑ    | All modes (TCPWM)                                                                                       |

| ITCPWM2               | Block current consumption at 12 MHz |      | _   | 155 |       | All modes (TCPWM)                                                                                       |

| ITCPWM3               | Block current consumption at 48 MHz | -    | _   | 650 |       | All modes (TCPWM)                                                                                       |

| TCPWM <sub>FREQ</sub> | Operating frequency                 | _    | _   | Fc  | MHz   | Fc max = CLK_SYS Maximum = 48 MHz                                                                       |

| TPWM <sub>ENEXT</sub> | Input trigger pulse width           | 2/Fc | _   | -   | ns    | For all trigger events [7]                                                                              |

| TPWM <sub>EXT</sub>   | Output trigger pulse widths         | 2/Fc | -   | _   |       | Minimum possible width of<br>Overflow, Underflow, and<br>CC (Counter equals Com-<br>pare value) outputs |

| TCRES                 | Resolution of counter               | 1/Fc | _   | =   |       | Minimum time between successive counts                                                                  |

| PWM <sub>RES</sub>    | PWM resolution                      | 1/Fc | =   | =   |       | Minimum pulse width of PWM Output                                                                       |

| Q <sub>RES</sub>      | Quadrature inputs resolution        | 1/Fc | -   | _   |       | Minimum pulse width be-<br>tween Quadrature phase<br>inputs                                             |

<sup>7.</sup> Trigger events can be Stop, Start, Reload, Count, Capture, or Kill depending on which mode of operation is selected.

### Table 19. FIXED I<sup>2</sup>C DC SPECIFICATIONS \*

| Parameter         | Description                                 | Min | Тур | Max | Units | Details/ Conditions |

|-------------------|---------------------------------------------|-----|-----|-----|-------|---------------------|

| I <sub>I2C1</sub> | Block current consumption at 100 kHz        | =   | =   | 50  | μΑ    |                     |

| I <sub>I2C2</sub> | Block current consumption at 400 kHz        | -   | -   | 135 |       |                     |

| I <sub>I2C3</sub> | Block current consumption at 1 Mbps         | =   | =   | 310 |       |                     |

| I <sub>I2C4</sub> | I <sup>2</sup> C enabled in Deep Sleep mode | =   | =   | 1.4 | μΑ    |                     |

<sup>\*</sup>Guaranteed by characterization.

### Table 20. FIXED I<sup>2</sup>C AC SPECIFICATIONS \*

| Parameter         | Description | Min | Тур | Max | Units | Details/ Conditions |

|-------------------|-------------|-----|-----|-----|-------|---------------------|

| F <sub>I2C1</sub> | Bit rate    | -   | -   | 1   | Mbps  |                     |

<sup>\*</sup>Guaranteed by characterization.

### Table 21. SPI DC SPECIFICATIONS \*

| Parameter | Description                         | Min | Тур | Max | Units | Details/ Conditions |

|-----------|-------------------------------------|-----|-----|-----|-------|---------------------|

| ISPI1     | Block current consumption at 1 Mbps | _   | _   | 360 | μΑ    |                     |

| ISPI2     | Block current consumption at 4 Mbps | =   | =   | 560 |       |                     |

| ISPI3     | Block current consumption at 8 Mbps | _   | _   | 600 |       |                     |

<sup>\*</sup>Guaranteed by characterization.

### Table 22. SPI AC SPECIFICATIONS \*

| Parameter                               | Description                                       | Min | Тур | Max                        | Units | Details/ Conditions                   |  |  |  |  |

|-----------------------------------------|---------------------------------------------------|-----|-----|----------------------------|-------|---------------------------------------|--|--|--|--|

| FSPI                                    | SPI Operating frequency (Master; 6X Oversampling) | _   | -   | 8                          | MHz   | -                                     |  |  |  |  |

| Fixed SPI Master Mode AC Specifications |                                                   |     |     |                            |       |                                       |  |  |  |  |

| TDMO                                    | MOSI Valid after SClock driving edge              | _   | _   | 15                         | ns    | _                                     |  |  |  |  |

| TDSI                                    | MISO Valid before SClock capturing edge           | 20  | -   | -                          |       | Full clock, late MISO sampling        |  |  |  |  |

| ТНМО                                    | Previous MOSI data hold time                      | 0   | _   | _                          |       | Referred to Slave capturing edge      |  |  |  |  |

| Fixed SPI Slave                         | Mode AC Specifications                            |     |     |                            |       |                                       |  |  |  |  |

| TDMI                                    | MOSI Valid before Sclock Capturing edge           | 40  | -   | _                          | ns    | _                                     |  |  |  |  |

| TDSO                                    | MISO Valid after Sclock driving edge              | _   | -   | 42 +<br>3*T <sub>CPU</sub> |       | T <sub>CPU</sub> = 1/F <sub>CPU</sub> |  |  |  |  |

48

100

ns

TDSO\_EXT

TSSELSSCK

THSO

### Table 23. UART DC SPECIFICATIONS \*

MISO Valid after Sclock driving edge in Ext. Clk mode

Previous MISO data hold time

SSEL Valid to first SCK Valid edge

| Parameter          | Description                            | Min | Тур | Max | Units | Details/ Conditions |

|--------------------|----------------------------------------|-----|-----|-----|-------|---------------------|

| I <sub>UART1</sub> | Block current consumption at 100 Kbps  | =   | =   | 55  | μΑ    |                     |

| I <sub>UART2</sub> | Block current consumption at 1000 Kbps | =   | =   | 312 | μΑ    |                     |

0

<sup>\*</sup>Guaranteed by characterization.

<sup>\*</sup>Guaranteed by characterization.

### Table 24. UART AC SPECIFICATIONS \*

| Parameter         | Description | Min | Тур | Max | Units | Details/ Conditions |

|-------------------|-------------|-----|-----|-----|-------|---------------------|

| F <sub>UART</sub> | Bit rate    | _   | -   | 1   | Mbps  |                     |

<sup>\*</sup>Guaranteed by characterization.

### Memory

### **Table 25. FLASH SPECIFICATIONS**

| Parameter            | Description                                             | Min   | Тур | Max | Units   | Details/ Conditions      |

|----------------------|---------------------------------------------------------|-------|-----|-----|---------|--------------------------|

| TROWWRITE [8]        | Row (block) write time (erase and program)              | -     | -   | 20  | ms      | Row (block) = 128 bytes  |

| TROWERASE [8]        | Row erase time                                          | -     | =   | 16  |         |                          |

| TROWPROGRAM [8]      | Row program time after erase                            | -     | -   | 4   |         | -                        |

| TBULKERASE [8]       | Bulk erase time (64 KB)                                 | -     | -   | 35  |         | =                        |

| TDEVPROG [8] [9]     | Total device program time                               | -     | -   | 7   | Seconds | _                        |

| FEND [9]             | Flash endurance                                         | 100 K | -   | -   | Cycles  | _                        |

| F <sub>RET</sub> [9] | Flash retention. T <sub>A</sub> ≤55°C, 100 K P/E cycles | 20    | -   | _   | Years   | _                        |

|                      | Flash retention. T <sub>A</sub> ≤ 85°C, 10 K P/E cycles | 10    | -   | -   |         | _                        |

| TWS48                | Number of Wait states at 48 MHz                         | 2     | _   | _   |         | CPU execution from Flash |

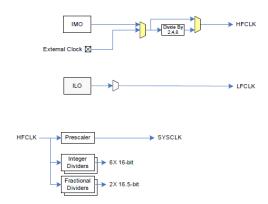

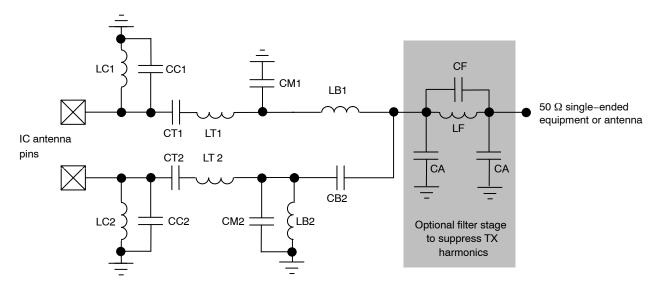

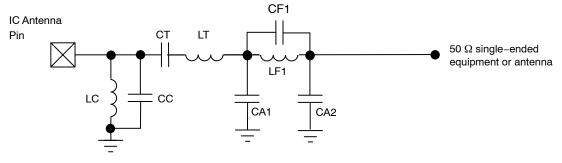

| TWS24                | Number of Wait states at 24 MHz                         | 1     | -   | _   |         | CPU execution from Flash |