# Features

- Protocol

- USB Used as a Physical Layer

- Device Firmware Upgrade Class Compliant

- Auto-Frequency Detection

- In-System Programming

- Read/Write Flash Memory

- Read Device ID

- Full-chip Erase

- Read/Write Configuration Bytes

- Security Setting from ISP Command

- Remote Application Start Command

- In-Application Programming/Self-Programming

- Read/Write Flash Memory

- Read Device ID

- Block Erase

- Read/Write Configuration Bytes

- Bootloader Start

# Description

This document describes the USB bootloader functionalities as well as the USB protocol to efficiently perform operations on the on-chip Flash memory. Additional information on the AT89C51SND1 product can be found in the AT89C51SND1 datasheet and the AT89C51SND1 errata sheet available on the Atmel web site.

The bootloader software (binary file) currently used for production is available from the Atmel web site.

| Bootloader Revision        | Purpose of Modifications | Date      |

|----------------------------|--------------------------|-----------|

| Revisions 1.6.2 and higher | First release            | 3/25/2003 |

USB Microcontrollers

# AT89C51SND1 USB Bootloader

4254C-MP3-03/06

| Functional<br>Description              | The AT89C51SND1 USB Bootloader facilitates In-System Programming (ISP) and In-Applica-<br>tion Programming.                                                                                      |

|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| In-System<br>Programming<br>Capability | In-System Programming allows the user to program or reprogram the microcontroller on-chip Flash memory without removing it from the system and without the need of a pre-programmed application. |

|                                        | The USB bootloader can manage a communication with a host through the USB bus. It can also access and perform requested operations on the on-chip Flash memory.                                  |

| In-Application<br>Programming or       | IAP allows the reprogramming of the microcontroller on-chip Flash memory without removing it from the system and while the embedded application is running.                                      |

| Self-Programming<br>Capability         | The USB bootloader contains some Application Programming Interface routines named API rou-<br>tines allowing IAP by using the user's firmware.                                                   |

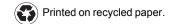

| Block Diagram                          | This section describes the different parts of the USB bootloader. Figure 1 shows the on-chip bootloader and IAP processes.                                                                       |

|                                        |                                                                                                                                                                                                  |

### Figure 1. Bootloader Process Description

| ISP Communication<br>Management | The purpose of this process is to manage the communication and its protocol between the on-<br>chip bootloader and an external device (host). The on-chip bootloader implements a USB proto-<br>col (see Section "Protocol", page 12). This process translates serial communication frames<br>(USB) into Flash memory accesses (read, write, erase). |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| User Call Management            | Several Application Program Interface (API) calls are available to the application program to selectively erase and program Flash pages. All calls are made through a common interface (API calls) included in the bootloader. The purpose of this process is to translate the application request into internal Flash memory operations.            |

| Flash Memory<br>Management      | This process manages low level accesses to the Flash memory (performs read and write accesses).                                                                                                                                                                                                                                                      |

# **Bootloader Configuration**

Configuration and The following table lists Configuration and Manufacturer byte information used by the boot-Manufacturer loader. This information can be accessed through a set of API or ISP commands.

Information

Table 1. Configuration and Manufacturer Information

| Mnemonic              | Description            | Default Value |

|-----------------------|------------------------|---------------|

| BSB                   | Boot Status Byte       | FFh           |

| SBV                   | Software Boot Vector   | FOh           |

| SSB                   | Software Security Byte | FFh           |

| EB                    | Extra Byte             | FFh           |

| Manufacturer          |                        | 58h           |

| Id1: Family Code      |                        | D7h           |

| Id2: Product Name     |                        | F7h           |

| Id3: Product Revision |                        | DFh           |

### Mapping and Default Value of Hardware **Security Byte**

The 4 MSB of the Hardware Byte can be read/written by software (this area is called Fuse bits). The 4 LSB can only be read by software and written by hardware using parallel programmer devices, this area is called Lock bits.

Table 2.

Hardware Byte Information

| Bit Position | Mnemonic | Default Value | Description                                           |  |  |

|--------------|----------|---------------|-------------------------------------------------------|--|--|

| 7            | X2B      | U             | To start in x1 mode                                   |  |  |

| 6            | BLJB     | Р             | To map the boot area in code area between F000h-FFFFh |  |  |

| 5            | _        | U             |                                                       |  |  |

| 4            | _        | U             |                                                       |  |  |

| 3            | reserved | U             |                                                       |  |  |

| 2            | LB2      | Р             |                                                       |  |  |

| 1            | LB1      | U             | To lock the chip (see datasheet)                      |  |  |

| 0            | LB0      | U             |                                                       |  |  |

Note: U: Unprogrammed = 1

P: Programmed = 0

# Security

The bootloader has Software Security Byte (SSB see Table 7) to protect itself from user access or ISP access.

The Software Security Byte (SSB) protects from ISP accesses. The command 'Program Software Security Bit' can only write a higher priority level. There are three levels of security:

- Level 0: NO\_SECURITY (FFh) This is the default level. From level 0, one can write level 1 or level 2.

- Level 1: WRITE\_SECURITY (FEh) In this level it is impossible to write in the Flash memory. The Bootloader returns an err\_WRITE status. From level 1, one can write only level 2.

- Level 2: RD\_WR\_SECURITY (FCh) Level 2 forbids all read and write accesses to/from the Flash memory. The Bootloader returns an err WRITE or an err VENDOR status.

Only a full chip erase command can reset the software security bits.

|                   | Level 0                  | Level 1                  | Level 2                  |  |

|-------------------|--------------------------|--------------------------|--------------------------|--|

| Flash             | Any access allowed       | Read only access allowed | All access not allowed   |  |

| Fuse bit          | Any access allowed       | Read only access allowed | All access not allowed   |  |

| BSB & SBV & EB    | Any access allowed       | Any access allowed       | Any access allowed       |  |

| SSB               | Any access allowed       | Write level2 allowed     | Read only access allowed |  |

| Manufacturer info | Read only access allowed | Read only access allowed | Read only access allowed |  |

| Bootloader info   | Read only access allowed | Read only access allowed | Read only access allowed |  |

| Erase block       | Allowed                  | Not allowed              | Not allowed              |  |

| Full chip erase   | Allowed                  | Allowed                  | Allowed                  |  |

| Blank Check       | Allowed                  | Allowed                  | Allowed                  |  |

Table 3.

Security Levels

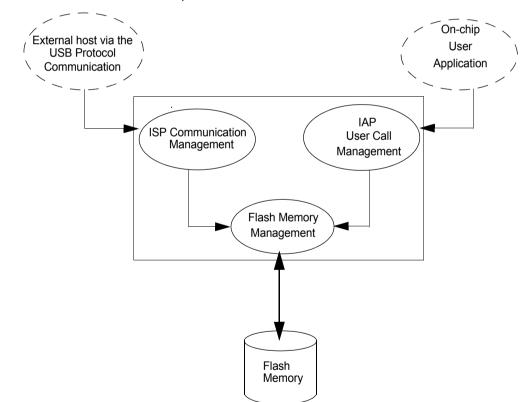

Software Boot Vector The Software Boot Vector (SBV see Table 6) forces the execution of a user bootloader starting at address [SBV]00h in the application area (FM0).

The way to start this user bootloader is described in Section "Bootloader Configuration".

# FLIP SoftwareFLIP is a PC software program running under Windows<sup>®</sup> 9x/Me/2000/XP and LINUX<sup>®</sup> that supports all Atmel Flash microcontrollers and USB protocol communication media.

This free software program is available from the Atmel web site.

| In-System<br>Programming                | The ISP allows the user to program or reprogram the microcontroller's on-chip Flash memory through the serial line without removing it from the system and without the need of a pre-pro-<br>grammed application.                                                                                                  |

|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                         | This section describes how to start the USB bootloader and the higher level protocol.                                                                                                                                                                                                                              |

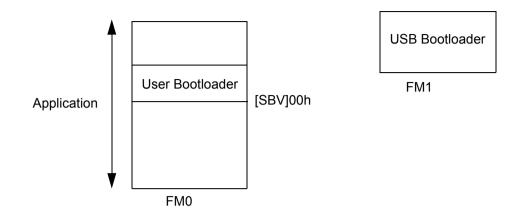

| Bootloader<br>Execution                 | As internal C51 code space is limited to 64K bytes, some mechanisms are implemented to allow boot memory to be mapped in the code space for execution at addresses F000h to FFFFh. The boot memory is enabled by setting the ENBOOT bit in AUXR1 (see Table 4). The three ways to set this bit are detailed below. |

| Software Boot<br>Mapping                | The software way to set ENBOOT consists in writing to AUXR1 from the user's software. This enables bootloader or API routines execution.                                                                                                                                                                           |

| Hardware Condition<br>Boot Mapping      | The hardware condition is based on the ISP# pin. When driving this pin to low level, the chip reset sets ENBOOT and forces the reset vector to F000h instead of 0000h in order to execute the bootloader software.                                                                                                 |

|                                         | As shown in Figure 2, the hardware condition always allows In-System recovery when user's memory has been corrupted.                                                                                                                                                                                               |

| Programmed<br>Condition Boot<br>Mapping | The programmed condition is based on the Bootloader Jump Bit (BLJB) in HSB (see Table 5). As shown in Figure 2, this bit is programmed (by hardware or software programming mode), the chip reset set ENBOOT and forces the reset vector to F000h instead of 0000h, in order to execute the bootloader software.   |

# AT89C51SND1

Figure 2. Boot Process Algorithm

# Registers

Special Function Register

**Table 4.** AUXR1 RegisterAUXR1 (S:A2h) – Auxiliary Register 1

| 7          | 6                     | 5                                                                                                      | 4                                                                                                                                                          | 3               | 2                | 1              | 0   |

|------------|-----------------------|--------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------------------|----------------|-----|

| -          | -                     | ENBOOT                                                                                                 | -                                                                                                                                                          | GF3             | 0                | -              | DPS |

| Bit Number | Bit<br>Mnemonic       | Description                                                                                            |                                                                                                                                                            |                 |                  |                |     |

| 7 - 6      | -                     | Reserved<br>The value read                                                                             | d from these bi                                                                                                                                            | ts are indeterm | inate. Do not se | et these bits. |     |

| 5          | ENBOOT <sup>(1)</sup> | Set this bit to FFFFh.                                                                                 | Enable Boot Flash<br>Set this bit to map the boot Flash in the code space between at addresses F000h to<br>FFFFh.<br>Clear this bit to disable boot Flash. |                 |                  |                |     |

| 4          | -                     | Reserved<br>The value read                                                                             | d from this bit i                                                                                                                                          | s indeterminate | . Do not set thi | s bit.         |     |

| 3          | GF3                   | <b>General Flag</b><br>This bit is a ge                                                                | General Flag<br>This bit is a general-purpose user flag.                                                                                                   |                 |                  |                |     |

| 2          | 0                     | Always Zero<br>This bit is stuck to logic 0 to allow INC AUXR1 instruction without affecting GF3 flag. |                                                                                                                                                            |                 |                  |                |     |

| 1          | -                     | Reserved for Data Pointer Extension.                                                                   |                                                                                                                                                            |                 |                  |                |     |

| 0          | DPS                   |                                                                                                        | <b>Select Bit</b><br>econd data po<br>t first data poin                                                                                                    |                 |                  |                |     |

Reset Value = XXXX 00X0b

Note: 1. ENBOOT bit is only available in AT89C51SND1 product.

**Hardware Bytes**

**Table 5.** HSB Byte – Hardware Security Byte

| 7          | 6                    | 5                                                                                                | 4                                                                                                                                                                                               | 3 | 2   | 1   | 0   |  |

|------------|----------------------|--------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|-----|-----|--|

| X2B        | BLJB                 | -                                                                                                | -                                                                                                                                                                                               | - | LB2 | LB1 | LB0 |  |

| Bit Number | Bit<br>Mnemonic      | Description                                                                                      |                                                                                                                                                                                                 |   |     |     |     |  |

| 7          | X2B <sup>(1)</sup>   | U U                                                                                              | <b>X2 Bit</b><br>Program this bit to start in X2 mode.<br>Unprogram (erase) this bit to start in standard mode.                                                                                 |   |     |     |     |  |

| 6          | BLJB <sup>(2)</sup>  | Program this I                                                                                   | Boot Loader Jump Bit<br>Program this bit to execute the boot loader at address F000h on next reset.<br>Unprogram (erase) this bit to execute user's application at address 0000h on next reset. |   |     |     |     |  |

| 5-4        | -                    | Reserved<br>The value rea                                                                        | Reserved<br>The value read from these bits is always unprogrammed. Do not program these bits.                                                                                                   |   |     |     |     |  |

| 3          | _(3)                 | <b>Reserved</b><br>The value read from this bit is always unprogrammed. Do not program this bit. |                                                                                                                                                                                                 |   |     |     |     |  |

| 2-0        | LB2:0 <sup>(3)</sup> | Hardware Lock Bits<br>Refer to for bits description.                                             |                                                                                                                                                                                                 |   |     |     |     |  |

Reset Value = XXUU UXXX, UUUU UUUU after an hardware full chip erase.

8

#### Note: 1. X2B initializes the X2 bit in CKCON during the reset phase.

- 2. In order to ensure boot loader activation at first power-up, AT89C51SND1 products are delivered with BLJB programmed.

- 3. Bits 0 to 3 (LSN) can only be programmed by hardware mode.

| 7          | 6               | 5                                                                                                                                         | 4     | 3     | 2     | 1    | 0    |

|------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|------|------|

| ADD15      | ADD14           | ADD13                                                                                                                                     | ADD12 | ADD11 | ADD10 | ADD9 | ADD8 |

| Bit Number | Bit<br>Mnemonic | Description                                                                                                                               |       |       |       |      |      |

| 7-0        | ADD15:8         | MSB of the user's boot loader 16-bit address location<br>Refer to the boot loader datasheet for usage information (boot loader dependent) |       |       |       |      |      |

#### Table 6. SBV Byte - Software Boot Vector

Reset Value = XXXX XXXX, UUUU UUUU after an hardware full chip erase.

### Table 7. SSB Byte - Software Security Byte

| 7          | 6               | 5                                                                                                               | 4    | 3    | 2    | 1    | 0    |

|------------|-----------------|-----------------------------------------------------------------------------------------------------------------|------|------|------|------|------|

| SSB7       | SSB6            | SSB5                                                                                                            | SSB4 | SSB3 | SSB2 | SSB1 | SSB0 |

| Bit Number | Bit<br>Mnemonic | Description                                                                                                     |      |      |      |      |      |

| 7-0        | SSB7:0          | Software Security Byte Data<br>Refer to the boot loader datasheet for usage information (boot loader dependent) |      |      |      |      |      |

Reset Value = XXXX XXXX, UUUU UUUU after an hardware full chip erase.

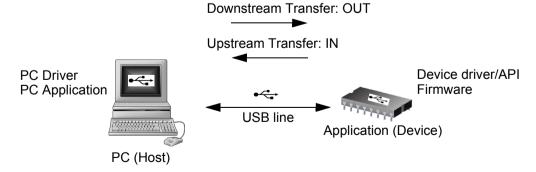

**Physical Layer** The USB norm specifies all the transfers over the USB line. The USB specification also includes several CLASS and SUB-CLASS specifications. These stand-alone documents are used by the manufacturer to implement a USB link between a PC and a device supporting the In-System Programming. Mostly, the USB specification is implemented by hardware (automatic reply, handshakes, timings, ...) and the USB Classes and SubClasses are implemented by software at a data level.

### Figure 3. USB Bus Topography

The USB used to transmit information has the following configuration:

- USB DFU using the Default Control Endpoint only (endpoint 0) with a 32 bytes length.

- 48 MHz for USB controller: frequency auto-detection performed by the bootloader.

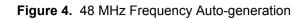

# 48 MHz Frequency Auto-generation

The following table shows the allowed frequencies compatible with the USB bootloader 48 MHz auto-generation.

|         | 12 MHz | 16 MHz | 20 MHz |  |

|---------|--------|--------|--------|--|

| X1 - X2 | ОК     | ОК     | ОК     |  |

# Protocol

**Device Firmware Upgrade Introduction** Device Firmware Upgrade is the mechanism for accomplishing the task of upgrading the device firmware. Any class of USB device can exploit this capability by supporting the requirements specified in this document.

> Because it is impractical for a device to concurrently perform both DFU operations and its normal run-time activities, those normal activities must cease for the duration of the DFU operations. Doing so means that the device must change its operating mode; i.e., a printer is <u>not</u> a printer while it is undergoing a firmware upgrade; it is a PROM programmer. However, a device that supports DFU is not capable of changing its mode of operation on its own. External (human or host operating system) intervention is required.

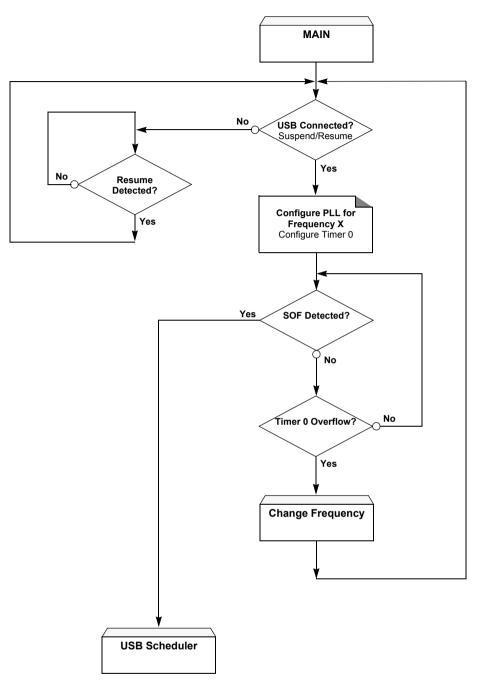

**DFU Specific**In addition of the USB standard requests, 7 DFU class-specific requests are employed to<br/>accomplish the upgrade operations, see Figure 4.

| bmRequestType | bRequest          | wValue   | windex        | wLength | Data     |

|---------------|-------------------|----------|---------------|---------|----------|

| 0010 0001b    | DFU_DETACH (0)    | wTimeout | Interface (4) | Zero    | none     |

| 0010 0001b    | DFU_DNLOAD (1)    | wBlock   | Interface (4) | Length  | Firmware |

| 1010 0001b    | DFU_UPLOAD (2)    | wBlock   | Interface (4) | Length  | Firmware |

| 1010 0001b    | DFU_GETSTATUS (3) | Zero     | Interface (4) | 6       | Status   |

| 0010 0001b    | DFU_CLRSTATUS (4) | Zero     | Interface (4) | Zero    | none     |

| 1010 0001b    | DFU_GETSTATE (5)  | Zero     | Interface (4) | 1       | State    |

| 0010 0001b    | DFU_ABORT (6)     | Zero     | Interface (4) | Zero    | none     |

Table 8. DFU Class-specific Requests

**DFU Descriptors Set** The device exports the DFU descriptor set, which contains:

- A DFU device descriptor

- A single configuration descriptor

- A single interface descriptor (including descriptors for alternate settings, if present)

- A single functional descriptor

*DFU Device Descriptor* This descriptor is only present in the DFU mode descriptor set. The DFU class code is reported in the *bDeviceClass* field of this descriptor.

## Table 9. USB Parameters

| Parameter      | ATMEL - AT89C51SND1 Bootloader |

|----------------|--------------------------------|

| Vendor ID      | 0x03EB                         |

| Product ID     | 0x2FFF                         |

| Release Number | 0x0000                         |

| Offset | Field              | Size | Value  | Description                                                         |

|--------|--------------------|------|--------|---------------------------------------------------------------------|

| 0      | bLength            | 1    | 12h    | Size of this descriptor, in bytes                                   |

| 1      | bDescriptorType    | 1    | 01h    | DFU FUNCTIONAL descriptor type                                      |

| 2      | bcdUSB             | 2    | 0100h  | USB specification release number in binary coded decimal            |

| 4      | bDeviceClass       | 1    | FEh    | Application Specific Class Code                                     |

| 5      | bDeviceSubClass    | 1    | 01h    | Device Firmware Upgrade Code                                        |

| 6      | bDeviceProtocol    | 1    | 00h    | The device does not use a class specific protocol on this interface |

| 7      | bMaxPacketSize0    | 1    | 32     | Maximum packet size for endpoint zero                               |

| 8      | idVendor           | 2    | 03EBh  | Vendor ID                                                           |

| 10     | idProduct          | 2    | 2FFFh  | Product ID                                                          |

| 12     | bcdDevice          | 2    | 0x0000 | Device release number in binary coded decimal                       |

| 14     | iManufacturer      | 1    | 0      | Index of string descriptor                                          |

| 15     | iProduct           | 1    | 0      | Index of string descriptor                                          |

| 16     | iSerialNumber      | 1    | 0      | Index of string descriptor                                          |

| 17     | bNumConfigurations | 1    | 01h    | One configuration only for DFU                                      |

| Table ID. DED MODE DEVICE DESCRIPTOR | Table 10. | DFU Mode Device Descriptor |

|--------------------------------------|-----------|----------------------------|

|--------------------------------------|-----------|----------------------------|

DFU Configuration Descriptor

DFU Interface Descriptor This descriptor is identical to the standard configuration descriptor described in the USB DFU specification version 1.0, with the exception that the *bNumInterfaces* field must contain the value 01h.

This is the descriptor for the only interface available when operating in DFU mode. Therefore, the value of the *bInterfaceNumber* field is always zero.

Table 11. DFU mode Interface Descriptor

| Offset | Field              | Size | Value | Description                                                        |

|--------|--------------------|------|-------|--------------------------------------------------------------------|

| 0      | bLength            | 1    | 09h   | Size of this descriptor, in bytes                                  |

| 1      | bDescriptorType    | 1    | 04h   | INTERFACE descriptor type                                          |

| 2      | bInterfaceNumber   | 1    | 00h   | Number of this interface                                           |

| 3      | bAlternateSetting  | 1    | 00h   | Alternate setting (1)                                              |

| 4      | bNumEndpoints      | 1    | 00h   | Only the control pipe is used                                      |

| 5      | bInterfaceClass    | 1    | FEh   | Application Specific Class Code                                    |

| 6      | bInterfaceSubClass | 1    | 01h   | Device Firmware Upgrade Code                                       |

| 7      | bInterfaceProtocol | 1    | 00h   | The device doesn't use a class specific protocol on this interface |

| 8      | iInterface         | 1    | 00h   | Index of the String descriptor for this interface                  |

Note: 1. Alternate settings can be used by an application to access additional memory segments. In this case, it is suggested that each alternate setting employs a string descriptor to indicate the target memory segment; e.g., "EEPROM". Details concerning other

possible uses of alternate settings are beyond the scope of this document. However, their use is intentionally not restricted because it is anticipated that implementers will devise additional creative uses for alternate settings.

### DFU Functional Descriptor

### Table 12. DFU Functional Descriptor

| Offset | Field           | Size | Value    | Description                                                                                                                                                                                                                                                                                                                                                                                             |

|--------|-----------------|------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0      | bLength         | 1    | 07h      | Size of this descriptor, in bytes                                                                                                                                                                                                                                                                                                                                                                       |

| 1      | bDescriptorType | 1    | 21h      | DFU FUNCTIONAL descriptor type                                                                                                                                                                                                                                                                                                                                                                          |

| 2      | bmAttributes    | 1    | Bit mask | DFU Attributes:<br>bit 7:3: reserved<br>bit 2: device is able to communicate via USB after<br>Manifestation phase<br>1 = yes, 0 = no, must see bus reset<br>bit 1: <i>bitCanUpload</i> : upload capable 1 = yes, 0 = no<br>bit 0: <i>bitCanDnload</i> : download capable 1 = yes, 0 = no                                                                                                                |

| 3      | wDetachTimeOut  | 2    | Number   | Time in milliseconds that the device will wait after receipt<br>of the DFU_DETACH request.<br>If this time elapses without a USB reset, the device will<br>terminate the Reconfiguration phase and revert back to<br>normal operation. This represents the maximum time that<br>the device can wait (depending on its timers,). The<br>Host may specify a shorter timeout in the DFU_DETACH<br>request. |

| 5      | wTransferSize   | 2    | Number   | Maximum number of bytes that the device can accept per control-write transaction                                                                                                                                                                                                                                                                                                                        |

Command Description This protocol allows to:

- Initiate the communication

- Program the Flash Data

- Read the Flash Data

- Program Configuration Information

- Read Configuration and Manufacturer Information

- Erase the Flash

- Start the application

Overview of the protocol is detailed in Appendix-A.

# **Device Status**

Get Status

The Host employs the DFU\_GETSTATUS request to facilitate synchronization with the device. This status gives information on the execution of the previous request: in progress/OK/Fail/...

| bmRequestType | bRequest          | wValue | windex        | wLength | Data   |

|---------------|-------------------|--------|---------------|---------|--------|

| 1010 0001b    | DFU_GETSTATUS (3) | Zero   | Interface (4) | 6       | Status |

| 0010 0001b    | DFU_CLRSTATUS (4) | Zero   | Interface (4) | Zero    | none   |

The device responds to the DFU\_GETSTATUS request with a payload packet containing the following data:

Table 13. DFU\_GETSTATUS Response

| Offset | Field             | Size | Value  | Description                                                                                                                                                                                                                                                                                                                                                                   |

|--------|-------------------|------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0      | bStatus           | 1    | Number | An indication of the status resulting from the execution of the most recent request.                                                                                                                                                                                                                                                                                          |

| 1      | bwPollTime<br>Out | 3    | Number | Minimum time in milliseconds that the host should wait before sending<br>a subsequent DFU_GETSTATUS. The purpose of this field is to allow<br>the device to dynamically adjust the amount of time that the device<br>expects the host to wait between the status phase of the next<br>DFU_DNLOAD and the subsequent solicitation of the device's status<br>via DFU_GETSTATUS. |

| 4      | bState            | 1    | Number | An indication of the state that the device is going to enter immediately following transmission of this response.                                                                                                                                                                                                                                                             |

| 5      | iString           | 1    | Index  | Index of status description in string table.                                                                                                                                                                                                                                                                                                                                  |

## Table 14. bStatus Values

| Status              | Value | Description                                                                                    |

|---------------------|-------|------------------------------------------------------------------------------------------------|

| ОК                  | 0x00  | No error condition is present                                                                  |

| errTARGET           | 0x01  | File is not targeted for use by this device                                                    |

| errFILE             | 0x02  | File is for this device but fails some vendor-specific verification test                       |

| errWRITE            | 0x03  | Device id unable to write memory                                                               |

| errERASE            | 0x04  | Memory erase function failed                                                                   |

| errCHECK_ERASE<br>D | 0x05  | Memory erase check failed                                                                      |

| errPROG             | 0x06  | Program memory function failed                                                                 |

| errVERIFY           | 0x07  | Programmed memory failed verification                                                          |

| errADDRESS          | 0x08  | Cannot program memory due to received address that is out of range                             |

| errNOTDONE          | 0x09  | Received DFU_DNLOAD with <i>wLength</i> = 0, but device does not think it has all the data yet |

| errFIRMWARE         | 0x0A  | Device's firmware is corrupted. It cannot return to run-time operations                        |

### Table 14. bStatus Values (Continued)

| Status       | Value | Description                                                    |

|--------------|-------|----------------------------------------------------------------|

| errVENDOR    | 0x0B  | iString indicates a vendor-specific error                      |

| errUSBR      | 0x0C  | Device detected unexpected USB reset signaling                 |

| errPOR       | 0x0D  | Device detected unexpected power on reset                      |

| errUNKNOWN   | 0x0E  | Something went wrong, but the device does not know what it was |

| errSTALLEDPK | 0x0F  | Device stalled an unexpected request                           |

### Table 15. bState Values

| State                      | Value | Description                                                                                                                                                                                                                             |  |  |  |

|----------------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| appIDLE                    | 0     | Device is running its normal application                                                                                                                                                                                                |  |  |  |

| appDETACH                  | 1     | Device is running its normal application, has received the DFU_DETACH request, and is waiting for a USB reset                                                                                                                           |  |  |  |

| dfuIDLE                    | 2     | Device is operating in the DFU mode and is waiting for requests                                                                                                                                                                         |  |  |  |

| dfuDNLOAD-SYNC             | 3     | Device has received a block and is waiting for the Host to solicit the status via DFU_GETSTATUS                                                                                                                                         |  |  |  |

| dfuDNBUSY                  | 4     | Device is programming a control-write block into its non-volatile memories                                                                                                                                                              |  |  |  |

| dfuDNLOAD-IDLE             | 5     | Device is processing a download operation. Expecting DFU_DNLOAD requests                                                                                                                                                                |  |  |  |

| dfuMANIFEST-SYNC           | 6     | Device has received the final block of firmware from the Host and is waiting for receipt of DFU_GETSTATUS to begin the Manifestation phase or device has completed the Manifestation phase and is waiting for receipt of DFU_GETSTATUS. |  |  |  |

| dfuMANIFEST                | 7     | Device is in the Manifestation phase.                                                                                                                                                                                                   |  |  |  |

| dfuMANIFEST-WAIT-<br>RESET | 8     | Device has programmed its memories and is waiting for a USB reset or a power on reset.                                                                                                                                                  |  |  |  |

| dfuUPLOAD-IDLE             | 9     | The device is processing an upload operation. Expecting DFU_UPLOAD requests.                                                                                                                                                            |  |  |  |

| dfuERROR                   | 10    | An error has occurred. Awaiting the DFU_CLRSTATUS request.                                                                                                                                                                              |  |  |  |

Clear Status

Any time the device detects an error and reports an error indication status to the host in the response to a DFU\_GETSTATUS request, it enters the dfuERROR state. The device cannot transition from the dfuERROR state, after reporting any error status, until after it has received a DFU\_CLRSTATUS request. Upon receipt of DFU\_CLRSTATUS, the device sets a status of OK and transitions to the dfuIDLE state. Only then it is able to transition to other states.

| bmRequestType | bRequest          | wValue | windex        | wLength | Data |

|---------------|-------------------|--------|---------------|---------|------|

| 0010 0001b    | DFU_CLRSTATUS (4) | Zero   | Interface (4) | 0       | None |

### Device State

This request solicits a report about the state of the device. The state reported is the current state of the device with no change in state upon transmission of the response. The values specified in the *bState* field are identical to those reported in DFU\_GETSTATUS.

| bmRequestType | bRequest         | wValue | windex        | wLength | Data  |

|---------------|------------------|--------|---------------|---------|-------|

| 1010 0001b    | DFU_GETSTATE (5) | Zero   | Interface (4) | 1       | State |

### DFU\_ABORT Request

t The DFU\_ABORT request enables the device to exit from certain states and return to the DFU\_IDLE state. The device sets the OK status on receipt of this request. For more information, see the corresponding state transition summary.

| bmRequestType | bRequest      | wValue | windex        | wLength | Data |

|---------------|---------------|--------|---------------|---------|------|

| 1010 0001b    | DFU_ABORT (6) | Zero   | Interface (4) | 0       | None |

#### Programming the Flash

**g the** The firmware image is downloaded via control-write transfers initiated by the DFU\_DNLOAD class-specific request. The host sends between *bMaxPacketSize0* and *wTransferSize* bytes to the device in a control-write transfer. Following each downloaded block, the host solicits the device status with the DFU\_GETSTATUS request.

As described in the USB DFU Specification, Firmware images for specific devices are, by definition, vendor specific. It is therefore required that target addresses, record sizes, and all other information relative to supporting an upgrade are encapsulated within the firmware image file. It is the responsibility of the device manufacturer and the firmware developer to ensure that their devices can consume these encapsulated data. With the exception of the DFU file suffix, the content of the firmware image file is irrelevant to the host.

Firmware image:

- 32 bytes: Command

- X bytes: X is the number of byte (00h) added before the first significative byte of the firmware. The X number is calculated to align the beginning of the firmware with the Flash page. X = start\_address [32]. For example, if the start address is 00AFh (175d), X = 175 [32] = 15.

- The firmware

- The DFU Suffix on 16 Bytes

| Offset | Field          | Size | Value                      | Description                                                                            |

|--------|----------------|------|----------------------------|----------------------------------------------------------------------------------------|

| - 0    | dwCRC          | 4    | Number                     | The CRC of the entire file, excluding <i>dwCRC</i>                                     |

| - 4    | bLength        | 1    | 16                         | The length of this DFU suffix including dwCRC                                          |

| - 5    | ucDfuSignature | 3    | 5: 44h<br>6: 46h<br>7: 55h | The unique DFU signature field                                                         |

| - 8    | bcdDFU         | 2    | BCD<br>0100h               | DFU specification number                                                               |

| - 10   | idVendor       | 2    | ID                         | The vendor ID associated with this file. Either FFFFh or must match device's vendor ID |

## Table 16. DFU File Suffix

### Table 16. DFU File Suffix

| Offset | Field     | Size | Value | Description                                                                                                          |

|--------|-----------|------|-------|----------------------------------------------------------------------------------------------------------------------|

| - 12   | idProduct | 2    | ID    | The product ID associated with this file. Either FFFFf or must match device's product ID                             |

| - 14   | bcdDevice | 2    | BCD   | The release number of the device associated with this file. Either FFFFh or a BCD firmware release or version number |

### Request from Host

| bmRequestType | bRequest       | wValue | windex        | wLength | Data     |

|---------------|----------------|--------|---------------|---------|----------|

| 0010 0001b    | DFU_DNLOAD (1) | wBlock | Interface (4) | Length  | Firmware |

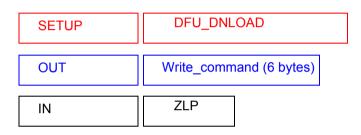

### Write Command

| Command Identifier   | data[0] | data[1]       | data[2] | data[3]     | data[4] | Description            |

|----------------------|---------|---------------|---------|-------------|---------|------------------------|

| ld_prog_start<br>01h | 00h     | start_address |         | end_address |         | Init Flash programming |

The write command is 6 bytes long. In order to reach the USB specification of the Control type transfers, the write command is completed with 26 (=32-6) non-significant bytes. The total length of the command is then 32 bytes, which is the length of the Default Control Endpoint.

- *Firmware* The firmware can now be downloaded to the device. In order to be in accordance with the Flash page size (128 bytes), X non-significant bytes are added before the first byte to program. The X number is calculated to align the beginning of the firmware with the Flash page. X = start\_address [32]. For example, if the start address is 00AFh (175d), X = 175 [32] = 15.

- *DFU Suffix* The DFU suffix of 16 bytes are added just after the last byte to program. This suffix is reserved for future use.

| SETUP | DFU_DNLOAD                               |  |  |  |  |

|-------|------------------------------------------|--|--|--|--|

| OUT   | Prog_Start + (EP0 FIFO length - 6) x 00h |  |  |  |  |

| OUT   | X offset bytes + Firmware Packet 1       |  |  |  |  |

| OUT   | Firmware Packet 2                        |  |  |  |  |

|       |                                          |  |  |  |  |

|       |                                          |  |  |  |  |

| OUT   | Firmware Packet n + DFU suffix           |  |  |  |  |

| IN    | ZLP                                      |  |  |  |  |

Figure 5. Example of Firmware Download Zero Length DFU\_DNLOAD Request

The Host sends a DFU\_DNLOAD request with the wLength field cleared to 0 to the device to indicate that it has completed transferring the firmware image file. This is the final payload packet of a download operation.

This operation should be preceded by a Long Jump address specification using the corresponding Flash command.

Answers from

After each program request, the Host can request the device state and status by sending a DFU\_GETSTATUS message.

Bootloader

If the device status indicates an error, the host can send a DFU\_CLRSTATUS request to the device.

# **Reading the Flash** The flow described below allows the user to read data in the Flash memory. A blank check command on the Flash memory is possible with this flow.

This operation is performed in 2 steps:

- 1. DFU\_DNLOAD request with the read command (6 bytes)

- 2. DFU\_UPLOAD request which correspond to the immediate previous command.

*First Request from Host* The Host sends a DFU Download request with a Display command in the data field.

| SETUP | DFU_DNLOAD             |  |  |  |  |

|-------|------------------------|--|--|--|--|

| OUT   | Display_Data (6 bytes) |  |  |  |  |

| IN    | ZLP                    |  |  |  |  |

| Command Identifier | data[0] | data[1]       | data[2] | data[3]     | data[4] | Description          |

|--------------------|---------|---------------|---------|-------------|---------|----------------------|

| ld_display_data    | 00h     | start_address |         | end_address |         | Display Flash Data   |

| 03h                | 01h     |               |         |             |         | Blank Check in Flash |

# Second Request from Host

The Host sends a DFU Upload request.

Answers from the Device

The device send to the Host the firmware from the specified start address to the end address.

Answers from the Device to a Blank Check Command The Host controller send a GET\_STATUS request to the device. Once internal blank check has been completed, the device sends its status.

- If the device status is "OK": the device memory is then blank and the device waits the next Host request.

- If the device status is "errCHECK\_ERASED": the device memory is not blank. The device waits for an DFU\_UPLOAD request to send the first address where the byte is not 0xFF.

# Programming Configuration Information

The flow described below allows the user to program Configuration Information regarding the bootloader functionality.

- Boot Process Configuration:

- BSB

•

- SBV

- Fuse bits (BLJB, X2B) (see Section "Mapping and Default Value of Hardware Security Byte", page 3).

Ensure that the Program Fuse bit command programs the 4 Fuse bits at the same time.

*Request from Host* To start the programming operation, the Host sends DFU\_DNLOAD request with the Write command in the data field (6 bytes).

| Command Identifier      | data[0] | data[1] | data[2] | data[3] | data[4] | Description               |

|-------------------------|---------|---------|---------|---------|---------|---------------------------|

| ld_write_command<br>04h | 01h     | 00h     | Value   |         |         | Write value in BSB        |

|                         |         | 01h     |         |         |         | Write value in SBV        |

|                         |         | 05h     |         |         |         | Write value in SSB        |

|                         |         | 06h     |         |         |         | Write value in EB         |

|                         | 02h     | 00h     | Value   |         |         | Write value in Fuse (HSB) |

Answers from Bootloader The device has two possible answers to a DFU\_GETSTATUS request:

- If the chip is protected from program access, a "err\_WRITE" status is returned to the Host.

- Otherwise, the device status is "OK".

Reading Configuration The flow described below allows the user to read the configuration or manufacturer information. Information or Manufacturer

Information

Requests from Host

To start the programming operation, the Host sends DFU\_DNLOAD request with the Read command in the data field (2 bytes).

| SETUP | DFU_DNLOAD             |  |  |  |  |

|-------|------------------------|--|--|--|--|

| OUT   | Read_command (2 bytes) |  |  |  |  |

| IN    | ZLP                    |  |  |  |  |

| Command Identifier | data[0] | data[1] | data[2] | data[3] | data[4] | Description             |

|--------------------|---------|---------|---------|---------|---------|-------------------------|

|                    |         | 00h     |         |         |         | Read Bootloader Version |

|                    | 00h     | 01h     |         |         |         | Read Device boot ID1    |

|                    |         | 02h     |         |         |         | Read Device boot ID2    |

|                    |         | 00h     |         |         |         | Read BSB                |

|                    |         | 01h     |         |         |         | Read SBV                |

| ld_read_command    |         | 05h     |         |         |         | Read SSB                |

| 05h                | 01h     | 06h     |         |         |         | Read EB                 |

|                    | UIII    | 30h     |         |         |         | Read Manufacturer Code  |

|                    |         | 31h     |         |         |         | Read Family Code        |

|                    |         | 60h     |         |         |         | Read Product Name       |

|                    |         | 61h     |         |         |         | Read Product Revision   |

|                    | 02h     | 00h     |         |         |         | Read HWB                |

Answers from Bootloader The device has two possible answers to a DFU\_GETSTATUS request:

- If the chip is protected from program access, a "err\_VENDOR" status is returned to the Host.

- Otherwise, the device status is "OK". The Host can send a DFU\_UPLOAD request to the device in order the value of the requested field.

| SETUP | DFU_UPLOAD          |  |  |  |

|-------|---------------------|--|--|--|

| IN    | Byte value (1 byte) |  |  |  |

| OUT   | ZLP                 |  |  |  |

# **Erasing the Flash** The flow described below allows the user to erase the Flash memory.

Two modes of Flash erasing are possible:

- Full chip erase

- Block erase

The Full Chip erase command erases the whole Flash (32 Kbytes) and sets some Configuration Bytes at their default values:

- BSB = FFh

- SBV = FFh

- SSB = FFh (NO\_SECURITY)

The Block erase command erases only a part of the Flash.

Four Blocks are defined in the AT89C51SND1:

- block0 (from 0000h to 1FFFh)

- block1 (from 2000h to 3FFFh)

- block2 (from 4000h to 7FFh)

- block3 (from 8000h to FFFh)

# *Request From Host* To start the erasing operation, the Host sends a DFU\_DNLOAD request with a Write Command in the data field (2 bytes).

| Command Identifier      | data[0] | data[1] | data[2] | data[3] | data[4] | Description                   |

|-------------------------|---------|---------|---------|---------|---------|-------------------------------|

|                         |         | 00h     |         |         |         | Erase block0 (0K to 8K)       |

|                         |         | 20h     |         |         |         | Erase block1 (8K to 16K)      |

| Id_write_command<br>04h | 00h     | 40h     |         |         |         | Erase block2 (16K to 32K)     |

|                         |         | 80h     |         |         |         | Erase block3 (32K to 64K)     |

|                         |         | FFh     |         |         |         | Full Chip Erase (bits at FFh) |

Answers from Bootloader The device has two possible answers to a DFU\_GETSTATUS request:

- If the chip is protected from program access, a "err\_WRITE" status is returned to the Host.

- Otherwise, the device status is "OK".

The full chip erase is always executed whatever the Software Security Byte value is.

# Starting the Application

The flow described below allows to start the application directly from the bootloader upon a specific command reception.

Two options are possible:

- Start the application with a reset pulse generation (using watchdog).

When the device receives this command the watchdog is enabled and the bootloader enters a waiting loop until the watchdog resets the device.

Be aware that if an external reset chip is used, the reset pulse in output may be wrong and in this case the reset sequence is not correctly executed.

- Start the application without reset A jump at the address 0000h is used to start the application without reset.

To start the application, the Host sends a DFU\_DNLOAD request with the specified application start type in the data field (3 or 5 bytes).

This request is immediately followed by a second DFU\_DNLOAD request with no data field to start the application with one of the two options.

Request from Host

| SETUP | DFU_UPLOAD                 |  |  |  |  |

|-------|----------------------------|--|--|--|--|

| IN    | Jump option (3 or 5 bytes) |  |  |  |  |

| OUT   | ZLP                        |  |  |  |  |

|       |                            |  |  |  |  |

| SETUP | DFU_UPLOAD |

|-------|------------|

|-------|------------|

| Command Identifier | data[0] | data[1] | data[2] | data[3] | data[4] | Description    |

|--------------------|---------|---------|---------|---------|---------|----------------|

| Id_write_command   |         | 00h     |         |         |         | Hardware reset |

| 04h                | 03h     | 01h     | add     | lress   |         | LJMP address   |

Answer from Bootloader No answer is returned by the device.

| (B |

|----|

| In-Application<br>Programming/S | The IAP allows to reprogram the microcontroller on-chip Flash memory without removing it from the system and while the embedded application is running. |  |  |  |  |  |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| elf-<br>Programming             | The user application can call Application Programming Interface (API) routines allowing IAP. These API are executed by the bootloader.                  |  |  |  |  |  |

| riogramming                     | To call the corresponding API, the user must use a set of Flash_api routines which can be linked with the application.                                  |  |  |  |  |  |

|                                 | Example of Flash_api routines are available on the Atmel web site:                                                                                      |  |  |  |  |  |

|                                 | C Flash Drivers for the AT89C51SND1                                                                                                                     |  |  |  |  |  |

|                                 | The Flash_api routines on the package work only with the USB bootloader.                                                                                |  |  |  |  |  |

|                                 | The Flash_api routines are listed in APPENDIX-B.                                                                                                        |  |  |  |  |  |

| API Call                        |                                                                                                                                                         |  |  |  |  |  |

| Process                         | The application selects an API by setting the 4 variables available when the Flash_api library is linked to the application.                            |  |  |  |  |  |

|                                 | These four variables are located in RAM at fixed address:                                                                                               |  |  |  |  |  |

|                                 | api_command: 1Ch                                                                                                                                        |  |  |  |  |  |

|                                 | • api_value: 1Dh                                                                                                                                        |  |  |  |  |  |

|                                 | <ul> <li>api_dph: 1Eh</li> <li>api_dpl: 1Fh</li> </ul>                                                                                                  |  |  |  |  |  |

|                                 | All calls are made through a common interface "USER CALL" at the address FFC0h.                                                                         |  |  |  |  |  |

|                                 | The jump at the USER_CALL must be done by LCALL instruction to be able to comeback in the                                                               |  |  |  |  |  |

|                                 | application.                                                                                                                                            |  |  |  |  |  |

|                                 | Before jump at the USER_CALL, the bit ENBOOT in AUXR1 register must be set.                                                                             |  |  |  |  |  |

| Constraints                     | The interrupts are not disabled by the bootloader.                                                                                                      |  |  |  |  |  |

|                                 | Interrupts must be disabled by user prior to jump to the USER_CALL, then re-enabled when returning.                                                     |  |  |  |  |  |

|                                 | The user must take care of hardware watchdog before launching a Flash operation.                                                                        |  |  |  |  |  |

|                                 | For more information regarding the Flash writing time see the AT89C51SND1 datasheet.                                                                    |  |  |  |  |  |

|                                 |                                                                                                                                                         |  |  |  |  |  |

# **API Commands**

Memory

- Several types of APIs are available:

- Read/Program Flash memory

- Read Configuration and Manufacturer Information

- Program Configuration Information

- Erase Flash

- Start bootloader

**Read/Program Flash** To read the Flash memory the bootloader is not involved.

For more details on these routines see the AT89C51SND1 Datasheet section "Program/Code Memory".

Two routines are available to program the Flash:

- \_\_\_api\_wr\_code\_byte

- \_\_api\_wr\_code\_page

- The application program load the column latches of the Flash then call the \_\_api\_wr\_code\_byte or \_\_api\_wr\_code\_page see the datasheet section "Program/Code Memory".

- Parameter settings

| API Name                             | api_command | api_dph | api_dpl | api_value |

|--------------------------------------|-------------|---------|---------|-----------|

| api_wr_code_byte<br>api_wr_code_page | 0Dh         | _       | _       | _         |

• Instruction: LCALL FFC0h.

Note: No special resources are used by the bootloader during this operation

# Read Configuration and Manufacturer Information

# Parameter settings

| API Name                  | api_command | api_dph api_dpl |       | api_value                 |

|---------------------------|-------------|-----------------|-------|---------------------------|

| api_rd_HSB                | 08h         | 08h –           |       | return HSB                |

| api_rd_BSB                | 05h         | -               | 00h   | return BSB                |

| api_rd_SBV                | 05h         | -               | 01h   | return SBV                |

| api_rd_SSB                | 05h         | -               | 05h   | return SSB                |

| api_rd_EB                 | 05h         | -               | – 06h |                           |

| api_rd_manufacturer       | 05h         | -               | 30h   | return manufacturer<br>id |

| api_rd_device_id1         | 05h         | -               | 31h   | return id1                |

| api_rd_device_id2         | 05h         | – 60h           |       | return id2                |

| api_rd_device_id3         | 05h         | -               | 61h   | return id3                |

| api_rd_bootloader_version | 0Eh         | -               | 00h   | return value              |

• Instruction: LCALL FFC0h.

• At the complete API execution by the bootloader, the value to read is in the api\_value variable.

Note: No special resources are used by the bootloader during this operation

# Program Configuration Information

### Parameter settings

| API Name                    | api_command | api_dph | api_dpl | api_value            |

|-----------------------------|-------------|---------|---------|----------------------|

| api_clr_BLJB <sup>(1)</sup> | 07h         | -       | -       | (HSB & BFh)  <br>40h |

| api_set_BLJB <sup>(2)</sup> | 07h         | -       |         |                      |

| api_clr_X2 <sup>(3)</sup>   | 07h         |         |         | (HSB & 7Fh)  <br>80h |

| api_set_X2 <sup>(4)</sup>   | 07h         |         |         | HSB & 7Fh            |

| api_wr_BSB                  | 04h         | – 00h   |         | value to write       |

| api_wr_SBV                  | 04h         | – 01h   |         | value to write       |

| api_wr_SSB                  | 04h         | -       | 05h     | value to write       |

| api_wr_EB                   | 04h         | _       | 06h     | value to write       |

Instruction: LCALL FFC0h.

Notes: 1. Unprogram BLJB so disable bootloader exection at reset.

2. Program BLJB so enable bootloader exection at reset.

3. Unprogram X2B so disable X2 mode at reset.

4. Program X2B so enable X2 mode at reset.

5. Refer to the AT89C51SND1 datasheet for information on Write operation Timing.

6. No special resources are used by the bootloader during these operations.

**Erasing the Flash**

**Flash** The AT89C51SND1 Flash memory is divided into four blocks:

Block 0: from address 0000h to 1FFFh (64 pages)

Block 1: from address 2000h to 3FFFh (64 pages)

Block 2: from address 4000h to 7FFFh (128 pages)

Block 3: from address 8000h to FFFFh (256 pages)

· Parameter settings

| API Name         | api_command | api_dph api_dpl |   | api_value |

|------------------|-------------|-----------------|---|-----------|

| api_erase_block0 | 00h         | 00h             | - | -         |

| api_erase_block1 | 00h         | 20h             | - | -         |

| api_erase_block2 | 00h         | 40h             | - | -         |

| api_erase_block3 | 00h         | 80h             | - | -         |

Instruction: LCALL FFC0h.

Notes: 1. Refer to the AT89C51SND1 datasheet for information on Write operation Timing, then multiply this timing by the number of pages.

2. No special resources are used by the bootloader during these operations.

Starting the Bootloader This routine allows to start at the beginning of the bootloader as after a reset. After calling this routine the regular boot process is performed and the communication must be opened before any action.

- No special parameter setting

- Set bit ENBOOT in AUXR1 register

- instruction: LJUMP or LCALL at address F000h

# Appendix A

# Table 17. Summary of Frames from Host

| Command Identifier   | data[0] | data[1]         | data[2] | data[3]     | data[4] | Description                   |

|----------------------|---------|-----------------|---------|-------------|---------|-------------------------------|

| ld_prog_start<br>01h | 00h     | start_a         | ddress  | end_address |         | Init Flash programming        |

| ld_display_data      | 00h     | - start_address |         | end_address |         | Display Flash Data            |

| 03h                  | 01h     |                 |         | enu_a       | uuress  | Blank Check in Flash          |

|                      |         | 00h             |         |             |         | Erase block0 (0K to 8K)       |

|                      |         | 20h             |         |             |         | Erase block1 (8K to 16K)      |

|                      | 00h     | 40h             |         |             |         | Erase block2 (16K to 32K)     |

|                      |         | 80h             |         |             |         | Erase block3 (32K to 64K)     |

|                      |         | FFh             |         |             |         | Full Chip Erase (bits at FFh) |

| Id_write_command     |         | 00h             |         |             |         | Write value in BSB            |

| 04h                  | 01h     | 01h             | Value   |             |         | Write value in SBV            |

|                      | 0111    | 05h             | value   |             |         | Write value in SSB            |

|                      |         | 06h             |         |             |         | Write value in EB             |

|                      | 02h     | 00h             | Value   |             |         | Write value in Fuse (HSB)     |

|                      | 03h     | 00h             | value   |             |         | Hardware reset                |

|                      |         | 01h add         |         | ress        |         | LJMP address                  |

|                      |         | 00h             |         |             |         | Read Bootloader Version       |

|                      | 00h     | 01h             |         |             |         | Read Device boot ID1          |

|                      |         | 02h             |         |             |         | Read Device boot ID2          |

|                      |         | 00h             |         |             |         | Read BSB                      |

|                      |         | 01h             |         |             |         | Read SBV                      |

| ld_read_command      |         | 05h             |         |             |         | Read SSB                      |

| 05h                  | 01h     | 06h             |         |             |         | Read EB                       |

|                      | UIII    | 30h             |         |             |         | Read Manufacturer Code        |

|                      |         | 31h             |         |             |         | Read Family Code              |

|                      |         | 60h             |         |             |         | Read Product Name             |

|                      |         | 61h             |         |             |         | Read Product Revision         |

|                      | 02h     | 00h             |         |             |         | Read HWB                      |

Table 18. DFU Class-specific Requests

| bmRequestType | bRequest |            | wValue   | wValue wIndex |      | Data |

|---------------|----------|------------|----------|---------------|------|------|

| 0010 0001b    | DFU_E    | DETACH (0) | wTimeout | Interface (4) | Zero | none |

Data

Firmware

Firmware

Status

none

State

none

wLength

| 0010 0001b | DFU_DNLOAD (1)    | wBlock | Interface (4) | Length |

|------------|-------------------|--------|---------------|--------|

| 1010 0001b | DFU_UPLOAD (2)    | wBlock | Interface (4) | Length |

| 1010 0001b | DFU_GETSTATUS (3) | Zero   | Interface (4) | 6      |

| 0010 0001b | DFU_CLRSTATUS (4) | Zero   | Interface (4) | Zero   |

| 1010 0001b | DFU_GETSTATE (5)  | Zero   | Interface (4) | 1      |

| 0010 0001b | DFU_ABORT (6)     | Zero   | Interface (4) | Zero   |

wValue

windex

| Table 18. DFU Class-specific Reques | sts |

|-------------------------------------|-----|

|-------------------------------------|-----|

bRequest

bmRequestType

# Appendix B

# Flash API Routines

# Table 19. API Summary

| Function Name             | Bootloader<br>Execution | api_command | api_dph | api_dpl | api_value         |

|---------------------------|-------------------------|-------------|---------|---------|-------------------|

| api_rd_code_byte          | no                      |             |         |         |                   |

| api_wr_code_byte          | yes                     | 0Dh         |         |         |                   |

| api_wr_code_page          | yes                     | 0Dh         |         |         |                   |

| api_erase block0          | yes                     | 00h         | 00h     |         |                   |

| api_erase block1          | yes                     | 00h         | 20h     |         |                   |

| api_erase block2          | yes                     | 00h         | 40h     |         |                   |

| api_erase block3          | yes                     | 00h         | 80h     |         |                   |

| api_rd_HSB                | yes                     | 08h         |         | 00h     | return value      |

| api_clr_BLJB              | yes                     | 07h         |         |         | (HSB & BFh)   40h |

| api_set_BLJB              | yes                     | 07h         |         |         | HSB & BFh         |

| api_clr_X2                | yes                     | 07h         |         |         | (HSB & 7Fh)   80h |

| api_set_X2                | yes                     | 07h         |         |         | HSB & 7Fh         |

| api_rd_BSB                | yes                     | 05h         |         | 00h     | return value      |

| api_wr_BSB                | yes                     | 04h         |         | 00h     | value             |

| api_rd_SBV                | yes                     | 05h         |         | 01h     | return value      |

| api_wr_SBV                | yes                     | 04h         |         | 01h     | value             |

| api_erase_SBV             | yes                     | 04h         |         | 01h     | FFh               |

| api_rd_SSB                | yes                     | 05h         |         | 05h     | return value      |

| api_wr_SSB                | yes                     | 04h         |         | 05h     | value             |