# rev 0.2

# Low Voltage Zero Delay Buffer

### Features

- Fully Integrated PLL

- Up to 200MHz I/O Frequency

- LVCMOS Outputs

- Outputs Disable in High Impedance

- www.DataSheet4U.com LVCMOS Reference Clock Options

- LQFP and TQFP Packaging

- ±50pS Cycle–Cycle Jitter

- 150pS Output Skews

### **Functional Description**

The ASM5I961C is a 2.5V or 3.3V compatible, 1:18 PLL based zero delay buffer. With output frequencies of up to 200MHz, output skews of 150pS the device meets the needs of the most demanding clock tree applications.

The ASM5I961 is offered with two different input configurations. The ASM5I961C offers an LVCMOS

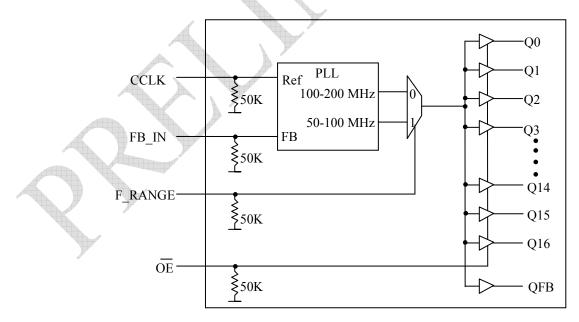

# **Block Diagram**

reference clock while the ASM5I961P offers an LVPECL reference clock.

When pulled high the  $\overline{OE}$  pin will force all of the outputs (except QFB) into a high impedance state. Because the  $\overline{OE}$  pin does not affect the QFB output, down stream clocks can be disabled without the internal PLL losing lock.

The ASM5I961C is fully 2.5V or 3.3V compatible and requires no external loop filter components. All control inputs accept LVCMOS compatible levels and the outputs provide low impedance LVCMOS outputs capable of driving terminated 50 $\Omega$  transmission lines. For series terminated lines the ASM5I961C can drive two lines per output giving the device an effective fanout of 1:36. The device is packaged in a 32 lead LQFP and TQFP Packages.

Figure 1. ASM5I961C Logic Diagram

Alliance Semiconductor www.DataSheet4<mark>U.com</mark> 2575 Augustine Drive • Santa Clara, CA • Tel: 408.855.4900 • Fax: 408.855.4999 • www.alsc.com

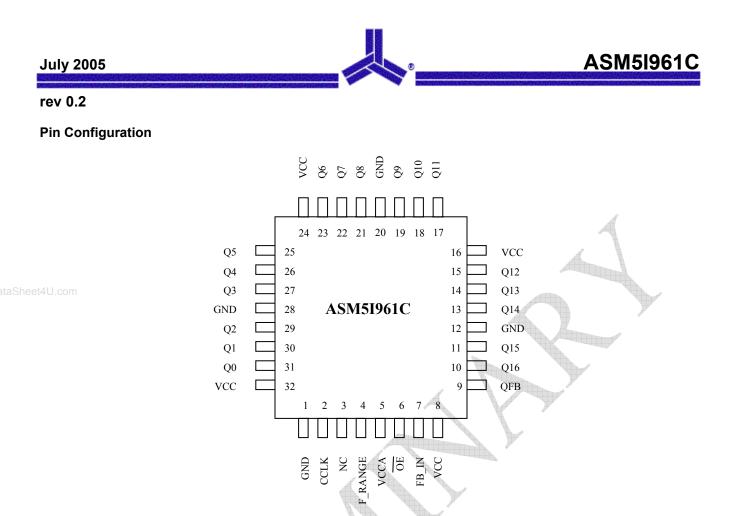

|                                                        |          | A -4   |        |                                                                                                                                                                                        |

|--------------------------------------------------------|----------|--------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin #                                                  | Pin Name | I/O    | Туре   | Function                                                                                                                                                                               |

| 2                                                      | CCLK     | Input  | LVCMOS | PLL reference clock signal                                                                                                                                                             |

| 7                                                      | FB_IN    | Input  | LVCMOS | PLL feedback signal input, connect to a QFB output                                                                                                                                     |

| 4                                                      | F_RANGE  | Input  | LVCMOS | PLL frequency range select                                                                                                                                                             |

| 6                                                      | ŌE       | Input  | LVCMOS | Output enable/disable                                                                                                                                                                  |

| 31,30,29,27,26,25,23,22,21,<br>19,18,17,15,14,13,11,10 | Q0 - Q16 | Output | LVCMOS | Clock outputs                                                                                                                                                                          |

| 9                                                      | QFB      | Output | LVCMOS | PLL feedback signal output, connect to a FB_IN                                                                                                                                         |

| 1,12,20,28                                             | GND      | Supply | Ground | Negative power supply                                                                                                                                                                  |

| 5                                                      | VCCA     | Supply | VCC    | PLL positive power supply (analog power supply). The ASM5I961C requires an external RC filter for the analog power supply pin $V_{CCA}$ . Please see applications section for details. |

| 8,16,24,32                                             | VCC      | Supply | VCC    | Positive power supply for I/O and core                                                                                                                                                 |

| 3                                                      | NC       |        |        | Not connected                                                                                                                                                                          |

# Table 1: Pin Configuration

# **Table 2: FUNCTION TABLE**

| Control | Default | 0                                                                                                    | 1                                                                                                  |

|---------|---------|------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| F_RANGE | 0       | PLL high frequency range. ASM5I961C input reference and output clock frequency range is 100 – 200MHz | PLL low frequency range. ASM5I961C input reference and output clock frequency range is 50 – 100MHz |

| ŌĒ      | 0       | Outputs enabled                                                                                      | Outputs disabled (high-impedance state)                                                            |

# Table 3: ABSOLUTE MAXIMUM RATINGS<sup>1</sup>

| Symbol           | Parameter                 | Min  | Max                   | Unit |

|------------------|---------------------------|------|-----------------------|------|

| V <sub>CC</sub>  | Supply Voltage            | -0.3 | 3.6                   | V    |

| V <sub>IN</sub>  | DC Input Voltage          | -0.3 | V <sub>CC</sub> + 0.3 | V    |

| V <sub>OUT</sub> | DC Output Voltage         | -0.3 | V <sub>cc</sub> + 0.3 | V    |

| I <sub>IN</sub>  | DC Input Current          |      | ±20                   | mA   |

| I <sub>OUT</sub> | DC Output Current         |      | ±50                   | mA   |

| Ts               | Storage Temperature Range | -40  | 125                   | °C   |

Note: 1 These are stress ratings only and are not implied for functional use. Exposure to absolute maximum ratings for prolonged periods of time may affect device reliability.

| Table 4: DC CHARACTERISTICS | $(V_{CC} = 3.3V \pm 5\%, T_A =$ | -40°C to +85°C) |    |

|-----------------------------|---------------------------------|-----------------|----|

|                             |                                 |                 | ð. |

| Symbol           | Characteristic                   | Min  | Тур                | Мах       | Unit | Condition                            |

|------------------|----------------------------------|------|--------------------|-----------|------|--------------------------------------|

| V <sub>IH</sub>  | Input HIGH Voltage               | 2.0  |                    | VCC + 0.3 | V    | LVCMOS                               |

| VIL              | Input LOW Voltage                | -0.3 |                    | 0.8       | V    | LVCMOS                               |

| V <sub>OH</sub>  | Output HIGH Voltage              | 2.4  |                    |           | V    | I <sub>OH</sub> = –20mA <sup>1</sup> |

| V <sub>OL</sub>  | Output LOW Voltage               | Å    |                    | 0.55      | V    | $I_{OL} = 20 \text{mA}^1$            |

| Z <sub>OUT</sub> | Output Impedance                 |      | 14                 | 20        | Ω    |                                      |

| I <sub>IN</sub>  | Input Current                    |      |                    | ±120      | μA   |                                      |

| CIN              | Input Capacitance                |      | 4.0                |           | pF   |                                      |

| C <sub>PD</sub>  | Power Dissipation Capacitance    |      | 8.0                | 10        | pF   | Per Output                           |

| I <sub>CCA</sub> | Maximum PLL Supply Current       |      | 2.0                | 5.0       | mA   | V <sub>CCA</sub> Pin                 |

| Icc              | Maximum Quiescent Supply Current |      |                    | TBD       | mA   | All $V_{CC}$ Pins                    |

| V <sub>TT</sub>  | Output Termination Voltage       |      | V <sub>CC</sub> ÷2 |           | V    |                                      |

Note: 1. The ASM5961C is capable of driving 50Ω transmission lines on the incident edge. Each output drives one 50Ω parallel terminated transmission line to a termination voltage of V<sub>TT</sub>. Alternatively, the device drives up two 50Ω series terminated transmission lines.

rev 0.2

#### **Table 5: AC CHARACTERISTICS** $(V_{CC} = 3.3V + 5\%)$ T<sub>A</sub> = 40°C to +85°C)<sup>1</sup>

| Symbol                           | Characte                                   | eristic                    | Min       | Тур      | Max        | Unit | Condition    |

|----------------------------------|--------------------------------------------|----------------------------|-----------|----------|------------|------|--------------|

| f <sub>ref</sub>                 | Input Frequency                            | F_RANGE = 0<br>F_RANGE = 1 | 100<br>50 |          | 200<br>100 | MHz  |              |

| f <sub>max</sub>                 | Maximum Output<br>Frequency                | F_RANGE = 0<br>F_RANGE = 1 | 100<br>50 |          | 200<br>100 | MHz  |              |

| f <sub>refDC</sub>               | Reference Input Duty Cy                    | cle                        | 25        |          | 75         | %    | 4            |

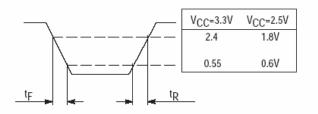

| t <sub>r</sub> , t <sub>f</sub>  | TCLK Input Rise/Fall Tin                   | ne                         |           |          | 3.0        | nS   | 0.8 to 2.0V  |

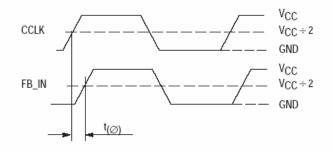

| t <sub>(∅)</sub>                 | Propagation Delay<br>(static phase offset) | CCLK to FB_IN              | -80       |          | 120        | pS   | PLL locked   |

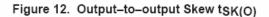

| t <sub>sk(O)</sub> om            | Output-to-Output Skew                      | 2                          |           | 90       | 150        | pS   |              |

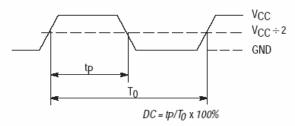

| DCo                              | Output Duty Cycle                          | F_RANGE = 0<br>F_RANGE = 1 | 42<br>45  | 50<br>50 | 55<br>55   | %    |              |

| t <sub>r</sub> , t <sub>f</sub>  | Output Rise/Fall Time                      |                            | 0.1       |          | 1.0        | nS   | 0.55 to 2.4V |

| t <sub>PLZ</sub> , <sub>HZ</sub> | Output Disable Time                        |                            |           |          | 10         | nS   |              |

| t <sub>PZL,LZ</sub>              | Output Enable Time                         |                            |           |          | 10         | nS   |              |

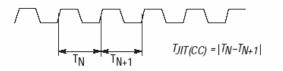

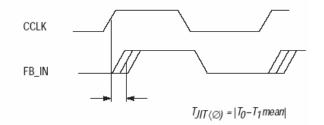

| t <sub>JIT(CC)</sub>             | Cycle-to-Cycle Jitter                      | RMS $(1\sigma)^3$          |           |          | 15         | pS   |              |

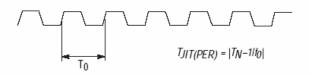

| $t_{\text{JIT}(\text{PER})}$     | Period Jitter                              | RMS (1σ)                   |           | 7.0      | 10         | pS   |              |

| t <sub>JIT(∅)</sub>              | I/O Phase Jitter                           | RMS (1σ)                   |           |          | / 15       | nS   |              |

| t <sub>lock</sub>                | Maximum PLL Lock Time                      | 6                          |           |          | 10         | mS   |              |

Note: 1. AC characteristics apply for parallel output termination of  $50\Omega$  to V<sub>TT</sub>. 2. See applications section for part–to–part skew calculation

3. See applications section for calculation for other confidence factors than  $1\sigma$

# Table 6: DC CHARACTERISTICS ( $V_{CC}$ = 2.5V ± 5%, $T_A$ = -40° to 85°C)

| Symbol           | Characteristic                   | Min  | Тур                | Мах       | Unit | Condition                            |

|------------------|----------------------------------|------|--------------------|-----------|------|--------------------------------------|

| V <sub>IH</sub>  | Input HIGH Voltage               | 1.7  |                    | VCC + 0.3 | V    | LVCMOS                               |

| VIL              | Input LOW Voltage                | -0.3 |                    | 0.7       | V    | LVCMOS                               |

| V <sub>OH</sub>  | Output HIGH Voltage              | 1.8  |                    |           | V    | I <sub>OH</sub> = –15mA <sup>1</sup> |

| V <sub>OL</sub>  | Output LOW Voltage               |      |                    | 0.6       | V    | I <sub>OL</sub> = 15mA <sup>1</sup>  |

| ZOUT             | Output Impedance                 |      | 18                 | 26        | Ω    |                                      |

| I <sub>IN</sub>  | Input Current                    |      |                    | ±120      | mA   |                                      |

| CIN              | Input Capacitance                |      | 4.0                |           | pF   |                                      |

| CPD              | Power Dissipation Capacitance    |      | 8.0                | 10        | pF   | Per Output                           |

| I <sub>CCA</sub> | Maximum PLL Supply Current       |      | 2.0                | 5.0       | mA   | V <sub>CCA</sub> Pin                 |

| I <sub>CC</sub>  | Maximum Quiescent Supply Current |      |                    | TBD       | mA   | All V <sub>CC</sub> Pins             |

| V <sub>TT</sub>  | Output Termination Voltage       |      | V <sub>CC</sub> ÷2 |           | V    |                                      |

Note: 1. The ASM51961C is capable of driving 50 Ω transmission lines on the incident edge. Each output drives one 50 Ω parallel terminated transmission line to a termination voltage of  $V_{TT}$ . Alternatively, the device drives up two 50 $\Omega$  series terminated transmission lines.

| Symbol                          | Characte                                   | eristic                    | Min       | Тур           | Max        | Unit | Condition   |

|---------------------------------|--------------------------------------------|----------------------------|-----------|---------------|------------|------|-------------|

| f <sub>ref</sub>                | Input Frequency                            | F_RANGE = 0<br>F_RANGE = 1 | 100<br>50 |               | 200<br>100 | MHz  |             |

| f <sub>max</sub>                | Maximum Output<br>Frequency                | F_RANGE = 0<br>F_RANGE = 1 | 100<br>50 | $\mathcal{Y}$ | 200<br>100 | MHz  |             |

| f <sub>refDC</sub>              | Reference Input Duty C                     | /cle                       | 25        |               | 75         | %    |             |

| t <sub>r</sub> , t <sub>f</sub> | TCLK Input Rise/Fall Tir                   | ne                         |           |               | 3.0        | nS   | 0.7 to 1.7V |

| t <sub>(Ø)</sub>                | Propagation Delay<br>(static phase offset) | CCLK to FB_IN              | -80       |               | 120        | pS   | PLL locked  |

| t <sub>sk(O)</sub>              | Output-to-Output Skew                      | 2                          | ¢.        | 90            | 150        | pS   |             |

| DCo                             | Output Duty Cycle                          | F_RANGE = 0<br>F_RANGE = 1 | 40<br>45  | 50<br>50      | 60<br>55   | %    |             |

| t <sub>r</sub> , t <sub>f</sub> | Output Rise/Fall Time                      |                            | 0.1       |               | 1.0        | nS   | 0.6 to 1.8V |

| t <sub>PLZ,HZ</sub>             | Output Disable Time                        |                            |           |               | 10         | nS   |             |

| t <sub>PZL,LZ</sub>             | Output Enable Time                         |                            |           |               | 10         | nS   |             |

| t <sub>JIT(CC)</sub>            | Cycle-to-Cycle Jitter                      | RMS $(1\sigma)^3$          |           |               | 15         | pS   |             |

| t <sub>JIT(PER)</sub>           | Period Jitter                              | RMS (1σ)                   |           | 7.0           | 10         | pS   |             |

| t <sub>JIT(Ø)</sub>             | I/O Phase Jitter                           | RMS (1σ)                   |           |               | 15         | nS   |             |

| tlock                           | Maximum PLL Lock Tim                       |                            |           |               | 10         | mS   |             |

# Table 7: AC CHARACTERISTICS $(V_{CC} = 2.5V \pm 5\%, T_A = 40^{\circ}C \text{ to } +85^{\circ}C)^{1}$

Note: 1 AC characteristics apply for parallel output termination of 50 $\Omega$  to V<sub>TT</sub>. 2 See applications section for part–to–part skew calculation

3 See applications section for calculation for other confidence factors than  $1\sigma$

### **APPLICATIONS INFORMATION**

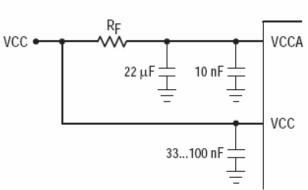

### **Power Supply Filtering**

The ASM5I961C is a mixed analog/digital product and as such it exhibits some sensitivity that would not necessarily be seen on a fully digital product. Analog circuitry is naturally susceptible to random noise, especially if this noise is seen on the power supply pins. The ASM5I961C provides separate power supplies for the output buffers (V $_{\text{CC}}$ ) and the phase–locked loop  $(V_{\mbox{\tiny CCA}})$  of the device. The purpose of this design technique is to isolate the high switching noise digital outputs from the relatively sensitive internal analog phase-locked loop. In a controlled environment such as an evaluation board this level of isolation is sufficient. However, in a digital system environment where it is more difficult to minimize noise on the power supplies a second level of isolation may be required. The simplest form of isolation is a power supply filter on the  $V_{CCA}$  pin for the ASM5I961C.

Figure 3. illustrates a typical power supply filter scheme. The ASM5I961C is most susceptible to noise with spectral content in the 10KHz to 10MHz range. Therefore the filter should be designed to target this range. The key parameter that needs to be met in the final filter design is the DC voltage drop that will be seen between the  $V_{CC}$ supply and the V<sub>CCA</sub> pin of the ASM5I961C. From the data sheet the I<sub>CCA</sub> current (the current sourced through the V<sub>CCA</sub> pin) is typically 2mA (5mA maximum), assuming that a minimum of 2.375V ( $V_{CC}$  = 3.3V or  $V_{CC}$  = 2.5V) must be maintained on the V<sub>CCA</sub> pin. The resistor RF shown in Figure 3. must have a resistance of  $270\Omega$  $(V_{CC} = 3.3V)$  or 5 to  $15\Omega$   $(V_{CC} = 2.5V)$  to meet the voltage drop criteria. The RC filter pictured will provide a broadband filter with approximately 100:1 attenuation for noise whose spectral content is above 20KHz. As the noise frequency crosses the series resonant point of an individual capacitor it's overall impedance begins to look inductive and thus increases with increasing frequency. The parallel capacitor combination shown ensures that a low impedance path to ground exists for frequencies well above the bandwidth of the PLL.

$R_F = 270\Omega$  for  $V_{CC} = 3.3V$

$R_F = 5-15\Omega$  for  $V_{CC} = 2.5V$

Although the ASM5I961C has several design features to minimize the susceptibility to power supply noise (isolated power and grounds and fully differential PLL) there still may be applications in which overall performance is being degraded due to system power supply noise. The power supply filter schemes discussed in this section should be adequate to eliminate power supply noise related problems in most designs.

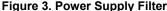

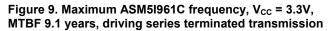

#### Driving Transmission Lines

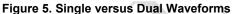

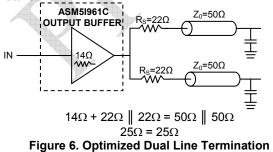

The ASM5I961C clock driver was designed to drive high speed signals in a terminated transmission line environment. To provide the optimum flexibility to the user the output drivers were designed to exhibit the lowest impedance possible. With an output impedance of less than  $15\Omega$  the drivers can drive either parallel or series terminated transmission lines. In most high performance clock networks point-to-point distribution of signals is the method of choice. In a point-to-point scheme either series terminated or parallel terminated transmission lines can be used. The parallel technique terminates the signal at the end of the line with a  $50\Omega$ resistance to V<sub>cc</sub>/2. This technique draws a fairly high level of DC current and thus only a single terminated line can be driven by each output of the ASM5I961C clock driver. For the series terminated case however there is no DC current draw, thus the outputs can drive multiple series terminated lines. Figure 4. illustrates an output driving a single series terminated line vs two series terminated lines in parallel. When taken to its extreme the fanout of the ASM5I961C clock driver is effectively doubled due to its capability to drive multiple lines.

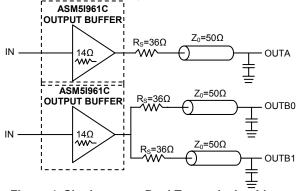

Figure 4. Single versus Dual Transmission Lines

The waveform plots of Figure 5. show the simulation results of an output driving a single line vs two lines. In both cases the drive capability of the ASM5I961C output buffer is more than sufficient to drive  $50\Omega$  transmission lines on the incident edge. Note from the delay measurements in the simulations a delta of only 43pS exists between the two differently loaded outputs. This suggests that the dual line driving need not be used exclusively to maintain the tight output-to-output skew of the ASM5I961C. The output waveform in Figure 5. shows

# ASM51961C

### rev 0.2

a step in the waveform, this step is caused by the impedance mismatch seen looking into the driver. The parallel combination of the  $36\Omega$  series resistor plus the output impedance does not match the parallel combination of the line impedances. The voltage wave launched down the two lines will equal:

$VL = VS (Z_0 / (R_S + R_0 + Z_0))$ Zo = 50\Omega || 50\Omega Rs = 36\Omega || 36\Omega Ro = 14\Omega VL = 3.0 (25 / (18 + 14 + 25) = 3.0 (25 / 57) = 1.31V

At the load end the voltage will double, due to the near unity reflection coefficient, to 2.62V. It will then increment towards the quiescent 3.0V in steps separated by one round trip delay (in this case 4.0nS).

Since this step is well above the threshold region it will not cause any false clock triggering, however designers may be uncomfortable with unwanted reflections on the line. To better match the impedances when driving multiple lines the situation in Figure 6. should be used. In this case the series terminating resistors are reduced such that when the parallel combination is added to the output buffer impedance the line impedance is perfectly matched.

#### Using the ASM5I961C in zero-delay applications

Nested clock trees are typical applications for the ASM5I961C. Designs using the ASM5I961C as LVCMOS PLL fanout buffer with zero insertion delay will show significantly lower clock skew than clock distributions developed from CMOS fanout buffers. The external feedback option of the ASM5I961C clock driver allows for its use as a zero delay buffer. By using the QFB output as a feedback to the PLL the propagation delay through the device is virtually eliminated. The PLL aligns the feedback clock output edge with the clock input reference edge resulting a near zero delay through the device. The maximum insertion delay of the device in zero-delay applications is measured between the reference clock input and any output. This effective delay consists of the static phase offset, I/O jitter (phase or long-term jitter), feedback path delay and the output-to-output skew error relative to the feedback output.

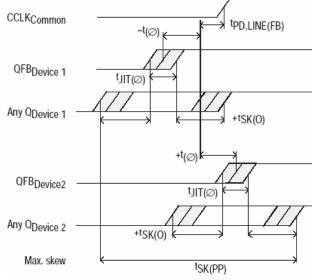

### Calculation of part-to-part skew

The ASM5I961C zero delay buffer supports applications where critical clock signal timing can be maintained across several devices. If the reference clock inputs of two or more ASM5I961C are connected together, the maximum overall timing uncertainty from the common CCLK input to any output is:

$t_{SK(PP)} = t_{(\phi)} + t_{SK(O)} + t_{PD}, L_{INE(FB)} + t_{JIT(\phi)} CF$

This maximum timing uncertainty consist of 4 components: static phase offset, output skew, feedback board trace delay and I/O (phase) jitter:

Figure 7. ASM5I961C max. device-to-device skew

Due to the statistical nature of I/O jitter a rms value  $(1\sigma)$  is specified. I/O jitter numbers for other confidence factors (CF) can be derived from Table 8.

# ASM51961C

### rev 0.2

### Table 8: Confidence Factor C<sub>F</sub>

| CF                 | Probability of clock edge within the<br>distribution |

|--------------------|------------------------------------------------------|

| ± 1σ               | 0.68268948                                           |

| ± 2σ               | 0.95449988                                           |

| ± 3σ               | 0.99730007                                           |

| ± 4σ               | 0.99993663                                           |

| ± 5σ               | 0.99999943                                           |

| ei4U <b>±₀6</b> σ⊨ | 0.99999999                                           |

The feedback trace delay is determined by the board layout and can be used to fine-tune the effective delay through each device. In the following example calculation a I/O jitter confidence factor of 99.7% ( $\pm$  3  $\sigma$ ) is assumed, resulting in a worst case timing uncertainty from input to any output of -275 pS to 315 pS relative to CCLK:

$$\begin{split} t_{SK(PP)} &= [-80pS...120pS] + [-150pS...150pS] + \\ &= [(15pS\_-3)...(15pS\_3)] + t_{PD,\ LINE(FB)} \\ t_{SK(PP)} &= [-275pS...315pS] + t_{PD,\ LINE(FB)} \end{split}$$

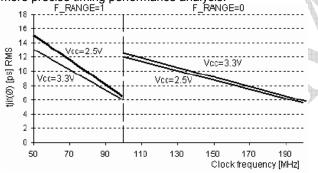

Due to the frequency dependence of the I/O jitter, Figure 8. "Max. I/O Jitter versus frequency" can be used for a more precise timing performance analysis.

Figure 8. Max. I/O Jitter versus frequency

# Power Consumption of the ASM5I961C and Thermal Management

The ASM5I961C AC specification is guaranteed for the entire operating frequency range up to 200MHz. The ASM5I961C power consumption and the associated long-

term reliability may decrease the maximum frequency limit, depending on operating conditions such as clock frequency, supply voltage, output loading, ambient temperature, vertical convection and thermal conductivity of package and board. This section describes the impact of these parameters on the junction temperature and gives a guideline to estimate the ASM5I961C die junction temperature and the associated device reliability.

| Table Or Die | lunation | temperature | and MTDE |

|--------------|----------|-------------|----------|

| Table 9: Die | iuncuon  | temperature |          |

|              |          |             |          |

| Junction temperature (°C) | MTBF (Years) |

|---------------------------|--------------|

| 100                       | 20.4         |

| 110                       | 9.1          |

| 120                       | 4.2          |

| 130                       | 2.0          |

Increased power consumption will increase the die junction temperature and impact the device reliability (MTBF). According to the system-defined tolerable MTBF, the die junction temperature of the ASM5I961C needs to be controlled and the thermal impedance of the board/package should be optimized. The power dissipated in the ASM5I961C is represented in equation 1. Where I<sub>CCQ</sub> is the static current consumption of the ASM5I961C, CPD is the power dissipation capacitance per output,  $(M)\Sigma C_L$  represents the external capacitive output load, N is the number of active outputs (N is always 27 in case of the ASM5I961C). The ASM5I961C supports driving transmission lines to maintain high signal integrity and tight timing parameters. Any transmission line will hide the lumped capacitive load at the end of the board trace, therefore,  $\Sigma C_L$  is zero for controlled transmission line systems and can be eliminated from equation 1. Using parallel termination output termination results in equation 2 for power dissipation. In equation 2, P stands for the number of outputs with a parallel or the venin termination,  $V_{\text{OL}},\,I_{\text{OL}},\,V_{\text{OH}}$  and  $I_{\text{OH}}$  are a function of the output termination technique and  $DC_Q$  is the clock signal duty cycle. If transmission lines are used  $\Sigma C_{L}$  is zero in equation 2 and can be eliminated. In general, the use of controlled transmission line techniques eliminates the impact of the lumped capacitive loads at the end lines and greatly reduces the power dissipation of the device. Equation 3 describes the die junction temperature T<sub>J</sub> as a function of the power consumption.

Equation 1

$$\begin{split} P_{TOT} &= \left[ I_{CCQ} + V_{CC} \cdot f_{CLOCK} \cdot \left( N \cdot C_{PD} + \sum_{M} C_{L} \right) \right] \cdot V_{CC} \end{split} \tag{Equation 1} \\ P_{TOT} &= V_{CC} \cdot \left[ I_{CCQ} + V_{CC} \cdot f_{CLOCK} \cdot \left( N \cdot C_{PD} + \sum_{M} C_{L} \right) \right] + \sum_{P} \left[ DC_{Q} \cdot I_{OH} \cdot \left( V_{CC} - V_{OH} \right) + \left( 1 - DC_{Q} \right) \cdot I_{OL} \cdot V_{OL} \right] \text{Equation 2} \end{split}$$

$T_J = T_A + P_{TOT} \cdot R_{thia}$

Equation 3

$$f_{\text{CLOCK,MAX}} = \frac{1}{C_{\text{PD}} \cdot N \cdot V_{\text{CC}}^2} \cdot \left[ \frac{T_{\text{J,MAX}} - T_{\text{A}}}{R_{\text{thja}}} - \left( I_{\text{CCQ}} \cdot V_{\text{CC}} \right) \right]$$

Equation 4

Where R<sub>thja</sub> is the thermal impedance of the package (junction to ambient) and  $T_A$  is the ambient temperature. According to Table 9, the junction temperature can be used to estimate the long-term device reliability. Further, combining equation 1 and equation 2 results in a maximum operating frequency for the ASM5I961C in a series terminated transmission line system.

### Table 10: Thermal package impedance of the 32 LQFP

| Convection, LFPM | Rthja (1P2S board), °C/W |

|------------------|--------------------------|

| Still air        | 80                       |

| 100 lfpm         | 70                       |

| 200 lfpm         | 61                       |

| 300 lfpm         | 57                       |

| 400 lfpm         | 56                       |

| 500 lfpm         | 55                       |

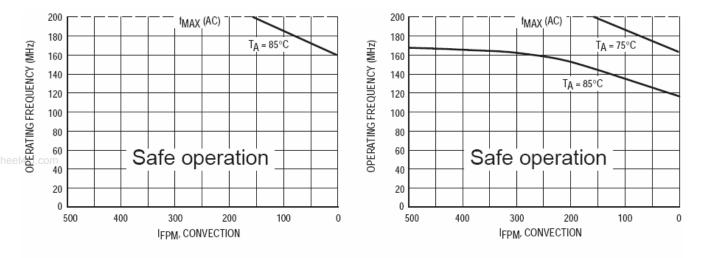

T<sub>J.MAX</sub> should be selected according to the MTBF system requirements and Table 9. Rthia can be derived from Table 10. The R<sub>thia</sub> represent data based on 1S2P boards, using 2S2P boards will result in a lower thermal impedance than indicated below. If the calculated maximum frequency is below 200MHz, it becomes the upper clock speed limit for the given application conditions. The following two derating charts describe the safe frequency operation range for the ASM5I961C. The charts were calculated for a maximum tolerable die junction temperature of 110°C, corresponding to an estimated MTBF of 9.1 years, a supply voltage of 3.3V and series terminated transmission line or capacitive loading. Depending on a given set of these operating conditions and the available device convection a decision on the maximum operating frequency can be made. There are no operating frequency limitations if a 2.5V power supply or the system specifications allow for a MTBF of 4 years (corresponding to a max. junction temperature of 120°C.

# ASM51961C

## rev 0.2

Figure 10. Maximum ASM5I961C frequency, V<sub>CC</sub> = 3.3V, MTBF 9.1 years,4pF load per line

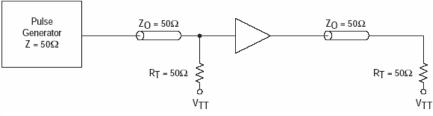

Figure 11. TCLK ASM5I961C AC test reference for  $V_{CC}$  = 3.3V and  $V_{CC}$  =2.5V

# ASM51961C

### rev 0.2

The pin-to-pin skew is defined as the worst case difference in propagation delay between any similar delay path within a single device

The time from the PLL controlled edge to the non controlled edge, divided by the time between PLL controlled edges, expressed as a percentage

### Figure 14. Output Duty Cycle (DC)

The variation in cycle time of a signal between adjacent cycles, over a random sample of adjacent cycle pairs

Figure 18. Output Transition Time Test Reference

# Figure 13. Propagation delay (tpD, static phase offset) test reference

The deviation in  $t_0$  for a controlled edge with respect to a  $t_0$  mean in a random sample of cycles

### Figure 15. I/O Jitter

The deviation in cycle time of a signal with respect to the ideal period over a random sample of cycles

### Figure 17. Period Jitter

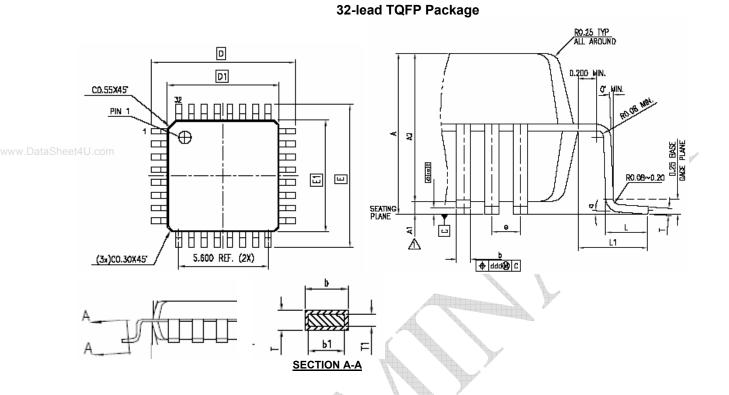

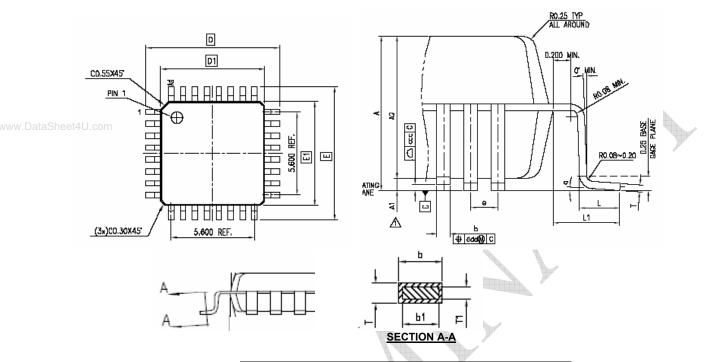

# rev 0.2 Package Diagram

| Dimensions |             |        |             |       |  |

|------------|-------------|--------|-------------|-------|--|

|            | Dimensions  |        |             |       |  |

| Symbol     | Inches      |        | Millimeters |       |  |

|            | Min         | Max    | Min         | Max   |  |

| A          |             | 0.0472 |             | 1.2   |  |

| A1         | 0.0020      | 0.0059 | 0.05        | 0.15  |  |

| A2         | 0.0374      | 0.0413 | 0.95        | 1.05  |  |

| D          | 0.3465      | 0.3622 | 8.8         | 9.2   |  |

| D1         | 0.2717      | 0.2795 | 6.9         | 7.1   |  |

| E          | 0.3465      | 0.3622 | 8.8         | 9.2   |  |

| E1         | 0.2717      | 0.2795 | 6.9         | 7.1   |  |

| L          | 0.0177      | 0.0295 | 0.45        | 0.75  |  |

| L1         | 0.03937 REF |        | 1.00 REF    |       |  |

| Т          | 0.0035      | 0.0079 | 0.09        | 0.2   |  |

| T1         | 0.0038      | 0.0062 | 0.097       | 0.157 |  |

| b          | 0.0118      | 0.0177 | 0.30        | 0.45  |  |

| b1         | 0.0118      | 0.0157 | 0.30        | 0.40  |  |

| R0         | 0.0031      | 0.0079 | 0.08        | 0.2   |  |

| а          | 0°          | 7°     | 0°          | 7°    |  |

| е          | 0.031 BASE  |        | 0.8 BASE    |       |  |

32-lead LQFP Package

|        | Dimensions  |        |             |       |  |

|--------|-------------|--------|-------------|-------|--|

| Symbol | Inches      |        | Millimeters |       |  |

|        | Min         | Max    | Min         | Max   |  |

| Α      |             | 0.0630 |             | 1.6   |  |

| A1     | 0.0020      | 0.0059 | 0.05        | 0.15  |  |

| A2     | 0.0531      | 0.0571 | 1.35        | 1.45  |  |

| D      | 0.3465      | 0.3622 | 8.8         | 9.2   |  |

| D1     | 0.2717      | 0.2795 | 6.9         | 7.1   |  |

| E      | 0.3465      | 0.3622 | 8.8         | 9.2   |  |

| E1     | 0.2717      | 0.2795 | 6.9         | 7.1   |  |

| and L  | 0.0177      | 0.0295 | 0.45        | 0.75  |  |

| L1     | 0.03937 REF |        | 1.00 REF    |       |  |

| Т      | 0.0035      | 0.0079 | 0.09        | 0.2   |  |

| T1     | 0.0038      | 0.0062 | 0.097       | 0.157 |  |

| b      | 0.0118      | 0.0177 | 0.30        | 0.45  |  |

| b1     | 0.0118      | 0.0157 | 0.30        | 0.40  |  |

| R0     | 0.0031      | 0.0079 | 0.08        | 0.20  |  |

| е      | 0.031 BASE  |        | 0.8 BASE    |       |  |

| а      | 0°          | 7°     | 0°          | 7°    |  |

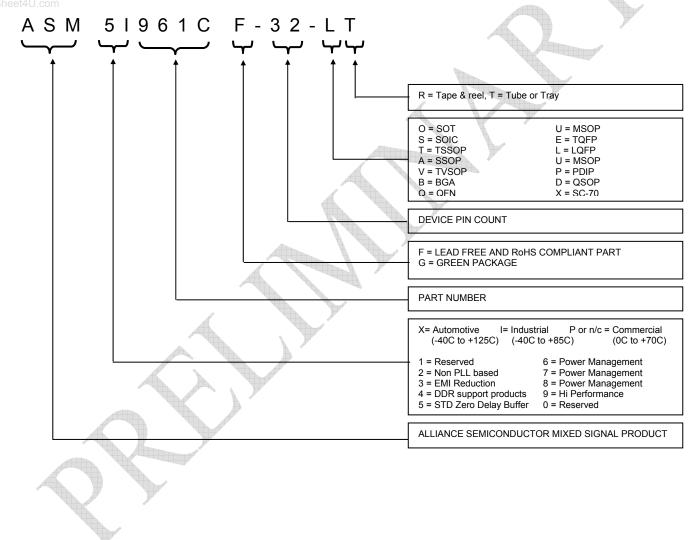

# rev 0.2 Ordering Information

| Part Number      | Marking    | Package Type                       | Temperature |

|------------------|------------|------------------------------------|-------------|

| ASM5I961C-32-ET  | ASM5I961C  | 32 pin TQFP                        | Industrial  |

| ASM5I961C-32-LT  | ASM5I961C  | 32 pin LQFP – Tape and Reel        | Industrial  |

| ASM5I961CG-32-ET | ASM5I961CG | 32 pin TQFP, Green                 | Industrial  |

| ASM5I961CG-32-LT | ASM5I961CG | 32 pin LQFP – Tape and Reel, Green | Industrial  |

# **Device Ordering Information**

Licensed under US patent #5,488,627, #6,646,463 and #5,631,920.

ww.DataSheet4U.com

Alliance Semiconductor Corporation 2575 Augustine Drive, Santa Clara, CA 95054 Tel# 408-855-4900 Fax: 408-855-4999 www.alsc.com Copyright © Alliance Semiconductor All Rights Reserved Part Number: ASM5I961C Document Version: 0.2

Note: This product utilizes US Patent # 6,646,463 Impedance Emulator Patent issued to Alliance Semiconductor, dated 11-11-2003

© Copyright 2003 Alliance Semiconductor Corporation. All rights reserved. Our three-point logo, our name and Intelliwatt are trademarks or registered trademarks of Alliance. All other brand and product names may be the trademarks of their respective companies. Alliance reserves the right to make changes to this document and its products at any time without notice. Alliance assumes no responsibility for any errors that may appear in this document. The data contained herein represents Alliance's best data and/or estimates at the time of issuance. Alliance reserves the right to change or correct this data at any time, without notice. If the product described herein is under development, significant changes to these specifications are possible. The information in this product data sheet is intended to be general descriptive information for potential customers and users, and is not intended to operate as, or provide, any guarantee or warrantee to any user or customer. Alliance does not assume any responsibility or liability arising out of the application or use of any product described herein, and disclaims any express or implied warranties related to the sale and/or use of Alliance products including liability or warranties related to fitness for a particular purpose, merchantability, or infringement of any intellectual property rights, except as express agreed to in Alliance's Terms and Conditions of Sale (which are available from Alliance). All sales of Alliance products are made exclusively according to Alliance's Terms and Conditions of Sale. The purchase of products from Alliance does not convey a license under any patent rights, copyrights; mask works rights, trademarks, or any other intellectual property rights of Alliance or third parties. Alliance does not authorize its products for use as critical components in life-supporting systems where a malfunction or failure may reasonably be expected to result in significant injury to the user, and the inclusion of Alliance products in such life-supporting systems implies that the manufacturer assumes all risk of such use and agrees to indemnify Alliance against all claims arising from such use.