## December 2004

## AS7C332MFT18A

## $3.3V \ 2M \times 18$ Flow-through synchronous SRAM

#### Features

- Organization: 2,097152 words × 18 bits

- Fast clock to data access: 7.5/8.5/10 ns

- Fast OE access time: 3.5/4.0 ns

- Fully synchronous flow-through operation

- Asynchronous output enable control

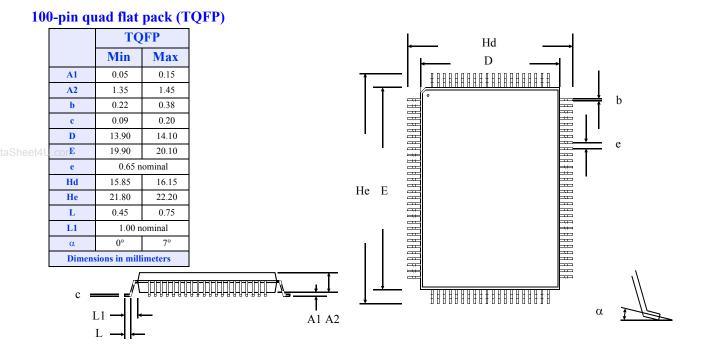

- Available in 100-pin TQFP package

- Individual byte write and global write

#### w.DataSheet4U.com

- Multiple chip enables for easy expansion

- 3.3V core power supply

- + 2.5V or 3.3V I/O operation with separate  $V_{DDO}$

- Linear or interleaved burst control

- Snooze mode for reduced power-standby

- · Common data inputs and data outputs

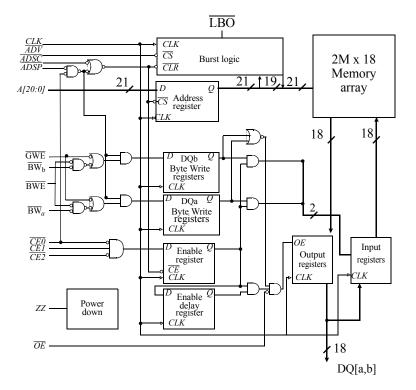

#### Logic block diagram

#### **Selection guide**

|                                   | -75 | -85 | -10 | Units |

|-----------------------------------|-----|-----|-----|-------|

| Minimum cycle time                | 8.5 | 10  | 12  | ns    |

| Maximum clock access time         | 7.5 | 8.5 | 10  | ns    |

| Maximum operating current         | 325 | 300 | 275 | mA    |

| Maximum standby current           | 140 | 130 | 130 | mA    |

| Maximum CMOS standby current (DC) | 90  | 90  | 90  | mA    |

# ®

| Org   | Part Number    | Mode   | Speed           |

|-------|----------------|--------|-----------------|

| 2MX18 | AS7C332MPFS18A | PL-SCD | 200/166/133 MHz |

| 1MX32 | AS7C331MPFS32A | PL-SCD | 200/166/133 MHz |

| 1MX36 | AS7C331MPFS36A | PL-SCD | 200/166/133 MHz |

| 2MX18 | AS7C332MPFD18A | PL-DCD | 200/166/133 MHz |

| 1MX32 | AS7C331MPFD32A | PL-DCD | 200/166/133 MHz |

| 1MX36 | AS7C331MPFD36A | PL-DCD | 200/166/133 MHz |

| 2MX18 | AS7C332MFT18A  | FT     | 7.5/8.5/10 ns   |

| 1MX32 | AS7C331MFT32A  | FT     | 7.5/8.5/10 ns   |

| 1MX36 | AS7C331MFT36A  | FT     | 7.5/8.5/10 ns   |

| 2MX18 | AS7C332MNTD18A | NTD-PL | 200/166/133 MHz |

| 1MX32 | AS7C331MNTD32A | NTD-PL | 200/166/133 MHz |

| 1MX36 | AS7C331MNTD36A | NTD-PL | 200/166/133 MHz |

| 2MX18 | AS7C332MNTF18A | NTD-FT | 7.5/8.5/10 ns   |

| 1MX32 | AS7C331MNTF32A | NTD-FT | 7.5/8.5/10 ns   |

| 1MX36 | AS7C331MNTF36A | NTD-FT | 7.5/8.5/10 ns   |

## 32 Mb Synchronous SRAM products list<sup>1,2</sup>

1 Core Power Supply:  $VDD = 3.3V \pm 0.165V$

2 I/O Supply Voltage: VDDQ =  $3.3V \pm 0.165V$  for 3.3V I/O

$VDDQ = 2.5V \pm 0.125V$  for 2.5V I/O

| PL-SCD | : | Pipelined Burst Synchronous | s SRAM - Single Cycle Deselect |

|--------|---|-----------------------------|--------------------------------|

|--------|---|-----------------------------|--------------------------------|

- PL-DCD : Pipelined Burst Synchronous SRAM Double Cycle Deselect

- FT : Flow-through Burst Synchronous SRAM

- NTD<sup>1</sup>-PL : Pipelined Burst Synchronous SRAM with NTD<sup>TM</sup>

NTD-FT : Flow-through Burst Synchronous SRAM with NTD<sup>TM</sup>

<sup>1</sup>NTD: No Turnaround Delay. NTD<sup>TM</sup> is a trademark of Alliance Semiconductor Corporation. All trademarks mentioned in this document are the property of their respective owners.

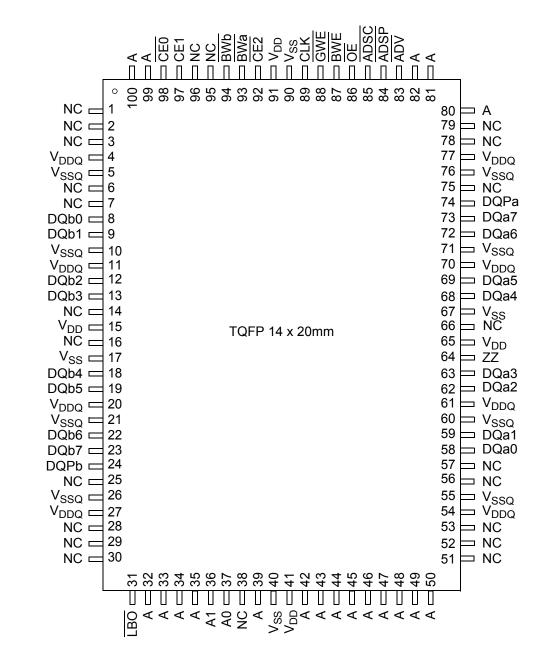

**Pin assignment**

12/23/04, v 1.3

#### **Functional description**

The AS7C332MFT18A is a high-performance CMOS 32-Mbit synchronous Static Random Access Memory (SRAM) device organized as 2,097152 words  $\times$  18 bits.

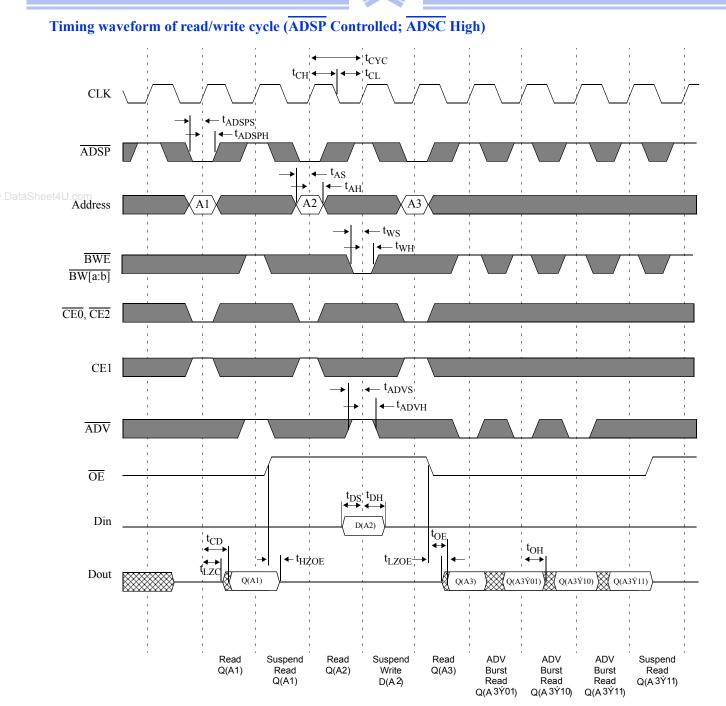

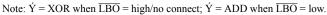

Fast cycle times of 8.5/10/12 ns with clock access times ( $t_{CD}$ ) of 7.5/8.5/10 ns. Three chip enable ( $\overline{CE}$ ) inputs permit easy memory expansion. Burst operation is initiated in one of two ways: the controller address strobe ( $\overline{ADSC}$ ), or the processor address strobe ( $\overline{ADSP}$ ). The burst advance pin ( $\overline{ADV}$ ) allows subsequent internally generated burst addresses.

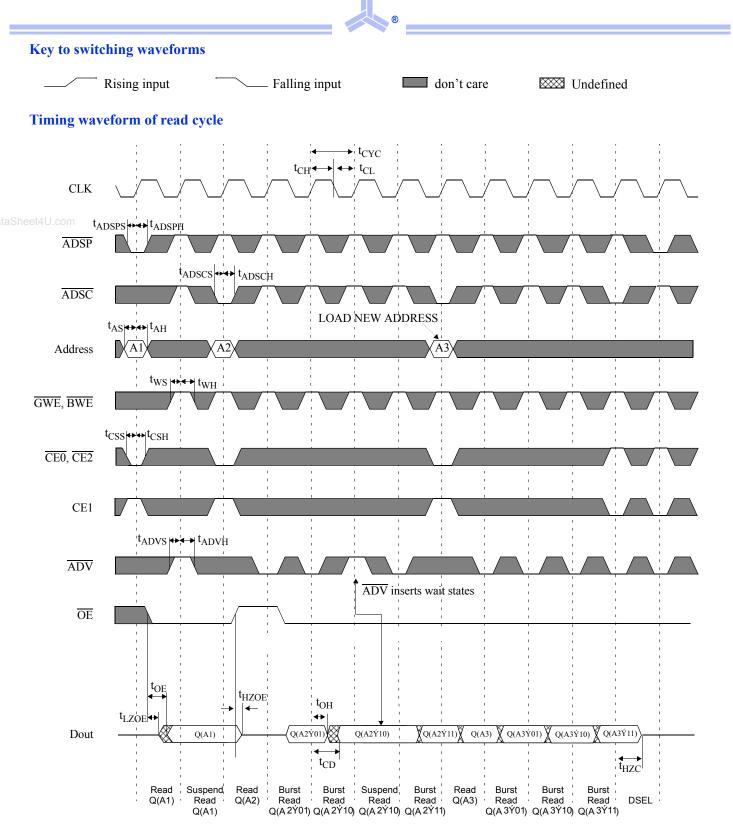

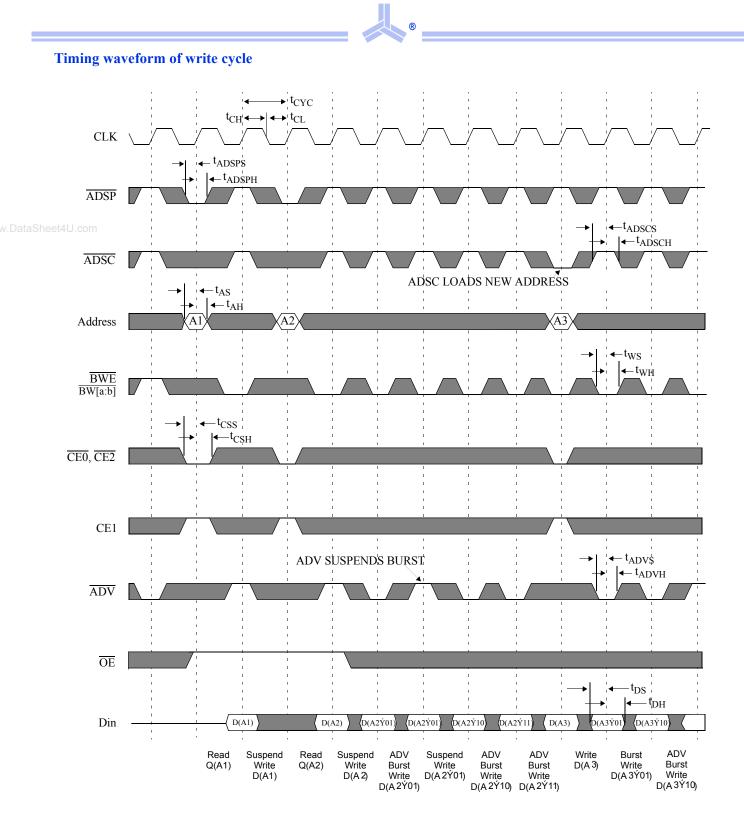

Read cycles are initiated with  $\overline{\text{ADSP}}$  (regardless of  $\overline{\text{WE}}$  and  $\overline{\text{ADSC}}$ ) using the new external address clocked into the on-chip address register when  $\overline{\text{ADSP}}$  is sampled low, the chip enables are sampled active, and the output buffer is enabled with  $\overline{\text{OE}}$ . In a read operation, the data accessed by the current address registered in the address registers by the positive edge of CLK are carried to the data-out buffer.  $\overline{\text{ADV}}$  is ignored on the clock edge that samples  $\overline{\text{ADSP}}$  asserted, but is sampled on all subsequent clock edges. Address is incremented internally for the next access of the burst when  $\overline{\text{ADV}}$  is sampled low and both address strobes are high. Burst mode is selectable with the  $\overline{\text{LBO}}$  input. With  $\overline{\text{LBO}}$  unconnected or driven high, burst operations use an interleaved count sequence. With  $\overline{\text{LBO}}$  driven low, the device uses a linear count sequence.

Write cycles are performed by disabling the output buffers with  $\overline{OE}$  and asserting a write command. A global write enable  $\overline{GWE}$  writes all 18 bits regardless of the state of individual  $\overline{BW[a,b]}$  inputs. Alternately, when  $\overline{GWE}$  is high, one or more bytes may be written by asserting  $\overline{BWE}$  and the appropriate individual byte  $\overline{BWn}$  signals.

$\overline{\text{BWn}}$  is ignored on the clock edge that samples  $\overline{\text{ADSP}}$  low, but it is sampled on all subsequent clock edges. Output buffers are disabled when  $\overline{\text{BWn}}$  is sampled LOW regardless of  $\overline{\text{OE}}$ . Data is clocked into the data input register when  $\overline{\text{BWn}}$  is sampled low. Address is incremented internally to the next burst address if  $\overline{\text{BWn}}$  and  $\overline{\text{ADV}}$  are sampled low.

Read or write cycles may also be initiated with ADSC instead of ADSP. The differences between cycles initiated with ADSC and ADSP follow.

- ADSP must be sampled high when ADSC is sampled low to initiate a cycle with ADSC.

- $\overline{\text{WE}}$  signals are sampled on the clock edge that samples  $\overline{\text{ADSC}}$  low (and  $\overline{\text{ADSP}}$  high).

- Master chip enable  $\overline{CE0}$  blocks  $\overline{ADSP}$ , but not  $\overline{ADSC}$ .

The AS7C332MFT18A family operates from a core 3.3V power supply. I/Os use a separate power supply that can operate at 2.5V or 3.3V. These devices are available in a 100-pin TQFP package.

#### **TQFP** capacitance

| Parameter         | Symbol             | Test conditions | Min | Max | Unit |

|-------------------|--------------------|-----------------|-----|-----|------|

| Input capacitance | ${\rm C_{IN}}^*$   | $V_{IN} = 0V$   | -   | 5   | pF   |

| I/O capacitance   | C <sub>I/O</sub> * | $V_{OUT} = 0V$  | -   | 7   | pF   |

\*Guaranteed not tested

#### **TQFP thermal resistance**

| Description                                                  | Conditions                                                                                   |         | Symbol        | Typical | Units |

|--------------------------------------------------------------|----------------------------------------------------------------------------------------------|---------|---------------|---------|-------|

| Thermal resistance (junction to ambient) <sup>1</sup>        |                                                                                              | 1-layer | $\theta_{JA}$ | 40      | °C/W  |

|                                                              | Test conditions follow standard test methods and procedures for measuring thermal impedance, | 4-layer | $\theta_{JA}$ | 22      | °C/W  |

| Thermal resistance<br>(junction to top of case) <sup>1</sup> | per EIA/JESD51                                                                               |         | $\theta_{JC}$ | 8       | °C/W  |

1 This parameter is sampled

## **Signal descriptions**

| Pin                  | I/O | Properties | Description                                                                                                                                                                                                                                                                                                        |

|----------------------|-----|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK                  | Ι   | CLOCK      | Clock. All inputs except $\overline{OE}$ , ZZ, and $\overline{LBO}$ are synchronous to this clock.                                                                                                                                                                                                                 |

| A,A0,A1              | Ι   | SYNC       | Address. Sampled when all chip enables are active and when $\overline{\text{ADSC}}$ or $\overline{\text{ADSP}}$ are asserted.                                                                                                                                                                                      |

| DQ[a,b]              | I/O | SYNC       | Data. Driven as output when the chip is enabled and when $\overline{OE}$ is active.                                                                                                                                                                                                                                |

| CE0                  | Ι   | SYNC       | Master chip enable. Sampled on clock edges when $\overline{\text{ADSP}}$ or $\overline{\text{ADSC}}$ is active. When $\overline{\text{CE0}}$ is inactive, $\overline{\text{ADSP}}$ is blocked. Refer to the "Synchronous truth table" for more information.                                                        |

| CE1, CE2<br>et4U.com | Ι   | SYNC       | Synchronous chip enables, active high, and active low, respectively. Sampled on clock edges when $\overline{\text{ADSC}}$ is active or when $\overline{\text{CE0}}$ and $\overline{\text{ADSP}}$ are active.                                                                                                       |

| ADSP                 | Ι   | SYNC       | Address strobe processor. Asserted low to load a new address or to enter standby mode.                                                                                                                                                                                                                             |

| ADSC                 | Ι   | SYNC       | Address strobe controller. Asserted low to load a new address or to enter standby mode.                                                                                                                                                                                                                            |

| ADV                  | Ι   | SYNC       | Advance. Asserted low to continue burst read/write.                                                                                                                                                                                                                                                                |

| GWE                  | Ι   | SYNC       | Global write enable. Asserted low to write all 18 bits. When high, $\overline{BWE}$ and $\overline{BW[a,b]}$ control write enable.                                                                                                                                                                                 |

| BWE                  | Ι   | SYNC       | Byte write enable. Asserted low with $\overline{\text{GWE}}$ high to enable effect of $\overline{\text{BW}[a,b]}$ inputs.                                                                                                                                                                                          |

| BW[a,b]              | Ι   | SYNC       | Write enables. Used to control write of individual bytes when $\overline{GWE}$ is high and $\overline{BWE}$ is low. If any of $\overline{BW[a,b]}$ is active with $\overline{GWE}$ high and $\overline{BWE}$ low, the cycle is a write cycle. If all $\overline{BW[a,b]}$ are inactive, the cycle is a read cycle. |

| ŌĒ                   | Ι   | ASYNC      | Asynchronous output enable. I/O pins are driven when $\overline{OE}$ is active and chip is in read mode.                                                                                                                                                                                                           |

| LBO                  | Ι   | STATIC     | Selects Burst mode. When tied to $V_{DD}$ or left floating, device follows interleaved Burst order. When driven Low, device follows linear Burst order. <i>This signal is internally pulled High</i> .                                                                                                             |

| ZZ                   | Ι   | ASYNC      | Snooze. Places device in low power mode; data is retained. Connect to GND if unused.                                                                                                                                                                                                                               |

| NC                   | -   | -          | No connect                                                                                                                                                                                                                                                                                                         |

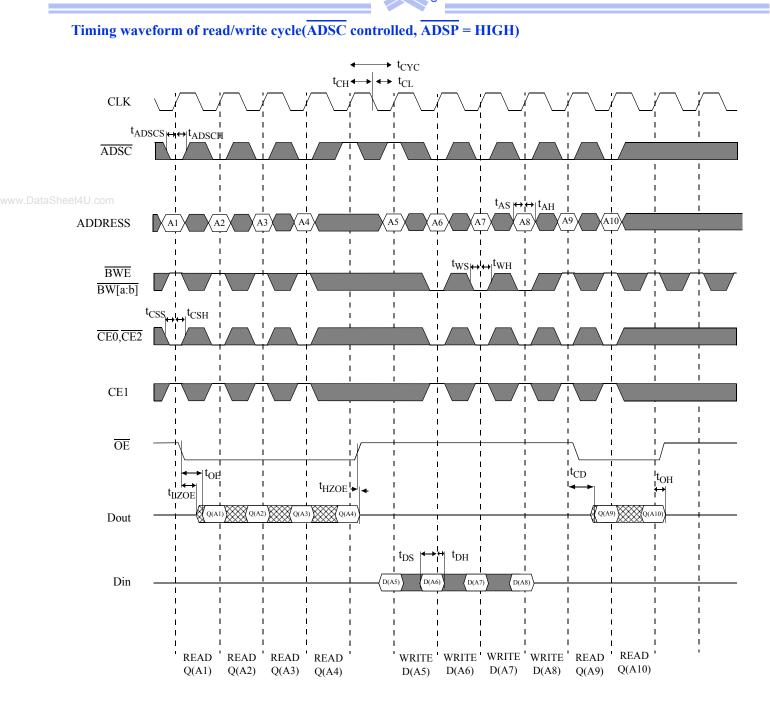

#### **Snooze Mode**

SNOOZE MODE is a low current, power-down mode in which the device is deselected and current is reduced to  $I_{SB2}$ . The duration of SNOOZE MODE is dictated by the length of time the ZZ is in a High state.

The ZZ pin is an asynchronous, active high input that causes the device to enter SNOOZE MODE.

When the ZZ pin becomes a logic High,  $I_{SB2}$  is guaranteed after the time  $t_{ZZI}$  is met. After entering SNOOZE MODE, all inputs except ZZ is disabled and all outputs go to High-Z. Any operation pending when entering SNOOZE MODE is not guaranteed to successfully complete. Therefore, SNOOZE MODE (READ or WRITE) must not be initiated until valid pending operations are completed. Similarly, when exiting SNOOZE MODE during  $t_{PUS}$ , only a DESELECT or READ cycle should be given while the SRAM is transitioning out of SNOOZE MODE.

## Write enable truth table (per byte)

| Function        | GWE | BWE | BWa | BWb |

|-----------------|-----|-----|-----|-----|

| Write All Dates | L   | Х   | Х   | Х   |

| Write All Bytes | Н   | L   | L   | L   |

| Write Byte a    | Н   | L   | L   | Н   |

| Write Byte b    | Н   | L   | Н   | L   |

| D J             | Н   | Н   | Х   | Х   |

| Read            | Н   | L   | Н   | Н   |

Key: X = don't care, L = low, H = high, n = a, b;  $\overline{BWE}$ ,  $\overline{BWn}$  = internal write signal.

## **Asynchronous Truth Table**

| Operation   | ZZ | OE | I/O Status  |

|-------------|----|----|-------------|

| Snooze mode | Н  | Х  | High-Z      |

| Read        | L  | L  | Dout        |

| Keau        | L  | Н  | High-Z      |

| Write       | L  | Х  | Din, High-Z |

| Deselected  | L  | Х  | High-Z      |

Notes:

1. X means "Don't Care"

2. ZZ pin is pulled down internally

3. For write cycles that follows read cycles, the output buffers must be disabled with OE, otherwise data bus contention will occur.

4. Snooze mode means power down state of which stand-by current does not depend on cycle times

5. Deselected means power down state of which stand-by current depends on cycle times

#### **Burst sequence table**

| Interleave              | Linear | burst add | ress (LBC | <del>)</del> = 0) |                         |       |       |       |     |

|-------------------------|--------|-----------|-----------|-------------------|-------------------------|-------|-------|-------|-----|

| A1 A0 A1 A0 A1 A0 A1 A0 |        |           |           |                   | A1 A0                   | A1 A0 | A1 A0 | A1 A0 |     |

| 1 <sup>st</sup> Address | 0 0    | 01        | 10        | 11                | 1 <sup>st</sup> Address | 0 0   | 01    | 10    | 11  |

| 2 <sup>nd</sup> Address | 01     | 0 0       | 11        | 10                | 2 <sup>nd</sup> Address | 01    | 10    | 11    | 0 0 |

| 3 <sup>rd</sup> Address | 10     | 11        | 0 0       | 01                | 3 <sup>rd</sup> Address | 10    | 11    | 0 0   | 01  |

| 4 <sup>th</sup> Address | 11     | 10        | 01        | 0 0               | 4 <sup>th</sup> Address | 11    | 10    | 0 1   | 10  |

# Synchronous truth table<sup>[4]</sup>

|       | CE0 <sup>1</sup> | CE1 | CE2    | ADSP | ADSC | ADV | WRITE <sup>[2]</sup> | <b>OE</b> | Address accessed | CLK    | Operation      | DQ             |

|-------|------------------|-----|--------|------|------|-----|----------------------|-----------|------------------|--------|----------------|----------------|

|       | Н                | Х   | Х      | Х    | L    | Х   | Х                    | Х         | NA               | L to H | Deselect       | Hi–Z           |

|       | L                | L   | Х      | L    | Х    | Х   | Х                    | Х         | NA               | L to H | Deselect       | Hi–Z           |

|       | L                | L   | Х      | Н    | L    | Х   | Х                    | Х         | NA               | L to H | Deselect       | Hi–Z           |

|       | L                | Х   | Н      | L    | Х    | Х   | Х                    | Х         | NA               | L to H | Deselect       | Hi–Z           |

| i t a | L                | X   | Н      | Н    | L    | Х   | Х                    | Х         | NA               | L to H | Deselect       | Hi–Z           |

| i L d | L                | Η   | L      | L    | Х    | Х   | Х                    | L         | External         | L to H | Begin read     | Q              |

|       | L                | Η   | L      | L    | Х    | Х   | Х                    | Н         | External         | L to H | Begin read     | Hi–Z           |

|       | L                | Н   | L      | Н    | L    | Х   | Н                    | L         | External         | L to H | Begin read     | Q              |

|       | L                | Η   | L      | Н    | L    | Х   | Н                    | Н         | External         | L to H | Begin read     | Hi–Z           |

|       | Х                | Х   | Х      | Н    | Н    | L   | Н                    | L         | Next             | L to H | Continue read  | Q              |

|       | Х                | Х   | Х      | Н    | Н    | L   | Н                    | Н         | Next             | L to H | Continue read  | Hi–Z           |

|       | Х                | Х   | Х      | Н    | Н    | Н   | Н                    | L         | Current          | L to H | Suspend read   | Q              |

|       | Х                | Х   | Х      | Н    | Н    | Н   | Н                    | Н         | Current          | L to H | Suspend read   | Hi–Z           |

|       | Н                | Х   | Х      | Х    | Н    | L   | Н                    | L         | Next             | L to H | Continue read  | Q              |

|       | Н                | Х   | Х      | Х    | Н    | L   | Н                    | Н         | Next             | L to H | Continue read  | Hi–Z           |

|       | Н                | Х   | Х      | X    | Н    | Н   | Н                    | L         | Current          | L to H | Suspend read   | Q              |

|       | Н                | Х   | Х      | X    | Н    | Н   | Н                    | Н         | Current          | L to H | Suspend read   | Hi–Z           |

|       | L                | Η   | L      | Н    | L    | Х   | L                    | Х         | External         | L to H | Begin write    | D <sup>3</sup> |

| ]     | Х                | Х   | Х      | Н    | Н    | L   | L                    | Х         | Next             | L to H | Continue write | D              |

| ]     | Н                | Х   | Х      | Х    | Н    | L   | L                    | Х         | Next             | L to H | Continue write | D              |

|       | Х                | Х   | Х      | Н    | Н    | Н   | L                    | Х         | Current          | L to H | Suspend write  | D              |

|       | Н                | Х   | Х      | Х    | Н    | Н   | L                    | Х         | Current          | L to H | Suspend write  | D              |

|       |                  |     | 1 17 1 |      |      |     |                      |           |                  |        |                |                |

ß

1 X = don't care, L = low, H = high

2 For  $\overline{\text{WRITE}}$ , L means any one or more byte write enable signals ( $\overline{\text{BWa or BWb}}$ ) and  $\overline{\text{BWE}}$  are LOW or  $\overline{\text{GWE}}$  is LOW.  $\overline{\text{WRITE}}$  = HIGH for all  $\overline{\text{BWx}}$ ,  $\overline{\text{BWE}}$ ,  $\overline{\text{GWE}}$  HIGH. See "Write enable truth table (per byte)," on page 6 for more information.

3 For write operation following a READ,  $\overline{OE}$  must be high before the input data set up time and held high throughout the input hold time 4 ZZ pin is always Low.

#### Absolute maximum ratings

| Parameter                                  | Symbol                             | Min  | Max             | Unit |

|--------------------------------------------|------------------------------------|------|-----------------|------|

| Power supply voltage relative to GND       | V <sub>DD</sub> , V <sub>DDQ</sub> | -0.5 | +4.6            | V    |

| Input voltage relative to GND (input pins) | V <sub>IN</sub>                    | -0.5 | $V_{DD} + 0.5$  | V    |

| Input voltage relative to GND (I/O pins)   | V <sub>IN</sub>                    | -0.5 | $V_{DDQ} + 0.5$ | V    |

| Power dissipation                          | P <sub>d</sub>                     | _    | 1.8             | W    |

| Short circuit output current               | I <sub>OUT</sub>                   | _    | 20              | mA   |

| Storage temperature                        | T <sub>stg</sub>                   | -65  | +150            | °C   |

| Temperature under bias                     | T <sub>bias</sub>                  | -65  | +135            | °C   |

Stresses greater than those listed under "Absolute maximum ratings" may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at these or any other conditions outside those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions may affect reliability.

#### Recommended operating conditions at 3.3V I/O

| Parameter                 | Symbol           | Min   | Nominal | Max   | Unit |

|---------------------------|------------------|-------|---------|-------|------|

| Supply voltage for inputs | V <sub>DD</sub>  | 3.135 | 3.3     | 3.465 | V    |

| Supply voltage for I/O    | V <sub>DDQ</sub> | 3.135 | 3.3     | 3.465 | V    |

| Ground supply             | Vss              | 0     | 0       | 0     | V    |

#### Recommended operating conditions at 2.5V I/O

| Parameter                 | Symbol           | Min   | Nominal | Max   | Unit |

|---------------------------|------------------|-------|---------|-------|------|

| Supply voltage for inputs | V <sub>DD</sub>  | 3.135 | 3.3     | 3.465 | V    |

| Supply voltage for I/O    | V <sub>DDQ</sub> | 2.375 | 2.5     | 2.625 | V    |

| Ground supply             | Vss              | 0     | 0       | 0     | V    |

#### DC electrical characteristics for 3.3V I/O operation

| Parameter                          | Sym             | Conditions                                                | Min    | Max                   | Unit |

|------------------------------------|-----------------|-----------------------------------------------------------|--------|-----------------------|------|

| Input leakage current <sup>†</sup> | I <sub>LI</sub> | $V_{DD} = Max, 0V \le V_{IN} \le V_{DD}$                  |        | 2                     | μΑ   |

| Output leakage current             | I <sub>LO</sub> | $OE \ge V_{IH}, V_{DD} = Max, 0V \le V_{OUT} \le V_{DDQ}$ | -2     | 2                     | μΑ   |

| Input high (logic 1) voltage       | V <sub>IH</sub> | Address and control pins                                  | 2*     | V <sub>DD</sub> +0.3  | V    |

|                                    |                 | I/O pins                                                  | 2*     | V <sub>DDQ</sub> +0.3 | v    |

| Input low (logic 0) voltage        | V <sub>IL</sub> | Address and control pins                                  | -0.3** | 0.8                   | V    |

| Input low (logic 0) voltage        |                 | I/O pins -0.5** 0.8                                       |        | 0.8                   | v    |

| Output high voltage                | V <sub>OH</sub> | $I_{OH} = -4 \text{ mA}, V_{DDQ} = 3.135 \text{V}$        | 2.4    | -                     | V    |

| Output low voltage                 | V <sub>OL</sub> | $I_{OL} = 8 \text{ mA}, V_{DDQ} = 3.465 \text{ V}$        | -      | 0.4                   | V    |

#### DC electrical characteristics for 2.5V I/O operation

| Parameter                          | Sym             | Conditions                                                | Min    | Max                   | Unit |

|------------------------------------|-----------------|-----------------------------------------------------------|--------|-----------------------|------|

| Input leakage current <sup>†</sup> | $ I_{LI} $      | $V_{DD}$ = Max, $0V \le V_{IN} \le V_{DD}$                | -2     | 2                     | μΑ   |

| Output leakage current             | I <sub>LO</sub> | $OE \ge V_{IH}, V_{DD} = Max, 0V \le V_{OUT} \le V_{DDQ}$ | -2     | 2                     | μΑ   |

| Input high (logic 1) voltage       | V <sub>IH</sub> | Address and control pins                                  |        | V <sub>DD</sub> +0.3  | V    |

| Input high (logic 1) voltage       |                 | I/O pins                                                  | 1.7*   | V <sub>DDQ</sub> +0.3 | V    |

| Lement laws (lawin 0) and taken    | V <sub>IL</sub> | Address and control pins                                  | -0.3** | 0.7                   | V    |

| Input low (logic 0) voltage        |                 | I/O pins                                                  | -0.3** | 0.7                   | V    |

| Output high voltage                | V <sub>OH</sub> | $I_{OH} = -4 \text{ mA}, V_{DDQ} = 2.375 \text{ V}$       |        | _                     | V    |

| Output low voltage                 | V <sub>OL</sub> | $I_{OL} = 8 \text{ mA}, V_{DDQ} = 2.625 \text{V}$         |        | 0.7                   | V    |

$\dagger$   $\overline{LBO}$  and ZZ pins have an internal pull-up or pull-down, and input leakage =  $\pm 10~\mu A.$

$V_{IH}$  max < VDD +1.5V for pulse width less than 0.2 X t<sub>CYC</sub>

\*\* $V_{IL}$  min = -1.5 for pulse width less than 0.2 X t<sub>CYC</sub>

## I<sub>DD</sub> operating conditions and maximum limits

| Parameter                                   | Sym              | Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | -75 | -85 | -10 | Unit |

|---------------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| Operating power supply current <sup>1</sup> | I <sub>CC</sub>  | $eq:central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_central_ce$ | 325 | 300 | 275 | mA   |

|                                             | $I_{SB}$         | All V <sub>IN</sub> $\leq$ 0.2V or $\geq$ V <sub>DD</sub> – 0.2V, Deselected,<br>f = f <sub>Max</sub> , ZZ $\leq$ V <sub>IL</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 140 | 130 | 130 |      |

| Standby power supply current                | I <sub>SB1</sub> | Deselected, f = 0, ZZ $\leq$ 0.2V,<br>all V <sub>IN</sub> $\leq$ 0.2V or $\geq$ V <sub>DD</sub> - 0.2V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 90  | 90  | 90  | mA   |

|                                             | I <sub>SB2</sub> | $ \begin{array}{l} \text{Deselected, } f = f_{Max},  ZZ \geq V_{DD} - 0.2V, \\ \text{all } V_{IN} \leq V_{IL} \text{ or } \geq V_{IH} \end{array} $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 80  | 80  | 80  |      |

1  $I_{CC}$  given with no output loading.  $I_{CC}$  increases with faster cycle times and greater output loading.

\_\_\_\_\_

# ®

## Timing characteristics over operating range

|                                      |                    | -75 |     | -   | 85  | -10 |     |      |                    |

|--------------------------------------|--------------------|-----|-----|-----|-----|-----|-----|------|--------------------|

| Parameter                            | Sym                | Min | Max | Min | Max | Min | Max | Unit | Notes <sup>1</sup> |

| Cycle time                           | t <sub>CYC</sub>   | 8.5 | _   | 10  | _   | 12  | _   | ns   |                    |

| Clock access time                    | t <sub>CD</sub>    | -   | 7.5 | _   | 8.5 | -   | 10  | ns   |                    |

| Output enable low to data valid      | t <sub>OE</sub>    | -   | 3.5 | -   | 4.0 |     | 4.0 | ns   |                    |

| Clock high to output low Z           | t <sub>LZC</sub>   | 2.5 | —   | 2.5 | _   | 2.5 | _   | ns   | 2,3,4              |

| Data output invalid from clock high  | t <sub>OH</sub>    | 2.5 | —   | 2.5 | _   | 2.5 | _   | ns   | 2                  |

| Output enable low to output low Z    | t <sub>LZOE</sub>  | 0   | —   | 0   | _   | 0   | _   | ns   | 2,3,4              |

| Output enable high to output high Z  | t <sub>HZOE</sub>  | -   | 3.5 | _   | 4.0 | _   | 4.0 | ns   | 2,3,4              |

| Clock high to output high Z          | t <sub>HZC</sub>   | -   | 4.0 | -   | 5.0 | -   | 5.0 | ns   | 2,3,4              |

| Output enable high to invalid output | t <sub>OHOE</sub>  | 0   | -   | 0   | _   | 0   | -   | ns   |                    |

| Clock high pulse width               | t <sub>CH</sub>    | 2.5 | _   | 3.0 | _   | 3.0 | _   | ns   | 5                  |

| Clock low pulse width                | t <sub>CL</sub>    | 2.5 | _   | 3.0 | _   | 3.0 | _   | ns   | 5                  |

| Address setup to clock high          | t <sub>AS</sub>    | 2.0 | _   | 2.0 | _   | 2.0 | _   | ns   | 6                  |

| Data setup to clock high             | t <sub>DS</sub>    | 2.0 | _   | 2.0 | _   | 2.0 | _   | ns   | 6                  |

| Write setup to clock high            | t <sub>WS</sub>    | 2.0 | _   | 2.0 | _   | 2.0 | _   | ns   | 6,7                |

| Chip select setup to clock high      | t <sub>CSS</sub>   | 2.0 | _   | 2.0 | _   | 2.0 | _   | ns   | 6,8                |

| Address hold from clock high         | t <sub>AH</sub>    | 0.5 | _   | 0.5 | _   | 0.5 | _   | ns   | 6                  |

| Data hold from clock high            | t <sub>DH</sub>    | 0.5 | _   | 0.5 | _   | 0.5 | _   | ns   | 6                  |

| Write hold from clock high           | t <sub>WH</sub>    | 0.5 | _   | 0.5 | _   | 0.5 | _   | ns   | 6,7                |

| Chip select hold from clock high     | t <sub>CSH</sub>   | 0.5 | _   | 0.5 | _   | 0.5 | _   | ns   | 6,8                |

| ADV setup to clock high              | t <sub>ADVS</sub>  | 2.0 | _   | 2.0 | _   | 2.0 | _   | ns   | 6                  |

| ADSP setup to clock high             | t <sub>ADSPS</sub> | 2.0 | _   | 2.0 | _   | 2.0 | -   | ns   | 6                  |

| ADSC setup to clock high             | t <sub>ADSCS</sub> | 2.0 | _   | 2.0 | _   | 2.0 | -   | ns   | 6                  |

| ADV hold from clock high             | t <sub>ADVH</sub>  | 0.5 | _   | 0.5 | _   | 0.5 | -   | ns   | 6                  |

| ADSP hold from clock high            | t <sub>ADSPH</sub> | 0.5 | _   | 0.5 | _   | 0.5 | -   | ns   | 6                  |

| ADSC hold from clock high            | t <sub>ADSCH</sub> | 0.5 | -   | 0.5 | -   | 0.5 | _   | ns   | 6                  |

1 See "Notes" on page 16.

## **Snooze Mode Electrical Characteristics**

| Description                        | Conditions      | Symbol            | Min | Max | Units |

|------------------------------------|-----------------|-------------------|-----|-----|-------|

| Current during Snooze Mode         | $ZZ \ge V_{IH}$ | I <sub>SB2</sub>  |     | 80  | mA    |

| ZZ active to input ignored         |                 | t <sub>PDS</sub>  | 2   |     | cycle |

| ZZ inactive to input sampled       |                 | t <sub>PUS</sub>  | 2   |     | cycle |

| ZZ active to SNOOZE current        |                 | t <sub>ZZI</sub>  |     | 2   | cycle |

| ZZ inactive to exit SNOOZE current |                 | t <sub>RZZI</sub> | 0   |     |       |

Note:  $\dot{Y} = XOR$  when  $\overline{LBO} = high/no$  connect;  $\dot{Y} = ADD$  when  $\overline{LBO} = low$ .  $\overline{BW[a:b]}$  is don't care.

Note:  $\dot{Y} = XOR$  when  $\overline{LBO} = high/no$  connect;  $\dot{Y} = ADD$  when  $\overline{LBO} = low$ .

Note:  $\overline{\text{ADV}}$  is don't care here.

Timing waveform of power down cycle

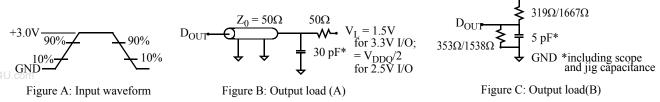

#### **AC test conditions**

- Output load: For  $t_{LZC}$ ,  $t_{LZOE}$ ,  $t_{HZOE}$ ,  $t_{HZC}$ , see Figure C. For all others, see Figure B.

- Input pulse level: GND to 3V. See Figure A.

- Input rise and fall time (measured at 0.3V and 2.7V): 2 ns. See Figure A.

- Input and output timing reference levels: 1.5V.

#### Notes

- 1 For test conditions, see "AC test conditions", Figures A, B, and C.

- 2 This parameter is measured with output load condition in Figure C.

- 3 This parameter is sampled but not 100% tested.

- 4 t<sub>HZOE</sub> is less than t<sub>LZOE</sub>, and t<sub>HZC</sub> is less than t<sub>LZC</sub> at any given temperature and voltage.

- 5  $t_{CH}$  is measured as high if above VIH, and  $t_{CL}$  is measured as low if below VIL.

- 6 This is a synchronous device. All addresses must meet the specified setup and hold times for all rising edges of CLK. All other synchronous inputs must meet the setup and hold times for all rising edges of CLK when chip is enabled.

- 7 Write refers to  $\overline{\text{GWE}}$ ,  $\overline{\text{BWE}}$ , and  $\overline{\text{BW[a,b]}}$ .

- 8 Chip select refers to  $\overline{\text{CE0}}$ , CE1, and  $\overline{\text{CE2}}$ .

#### +3.3V for 3.3V I/O; /+2.5V for 2.5V I/O

Thevenin equivalent:

## Package dimensions

#### **Ordering information**

| Package &<br>Width | -75                 | -85                 | -10                 |

|--------------------|---------------------|---------------------|---------------------|

| TOED 19            | AS7C332MFT18A-75TQC | AS7C332MFT18A-85TQC | AS7C332MFT18A-10TQC |

| TQFP x 18          | AS7C332MFT18A-75TQI | AS7C332MFT18A-85TQI | AS7C332MFT18A-10TQI |

Note: Add suffix 'N' to the above part number for Lead Free Parts (Ex. AS7C332MFT18A-75TQCN)

#### Part numbering guide

| Da | t AS7C | 33 | <b>2M</b> | FT | 18 | Α | -XX | TQ | C/I | X  |

|----|--------|----|-----------|----|----|---|-----|----|-----|----|

|    | 1      | 2  | 3         | 4  | 5  | 6 | 7   | 8  | 9   | 10 |

1. Alliance Semiconductor SRAM prefix

2. Operating voltage: 33 = 3.3V

3.Organization: 2M = 2Meg

4.Flow-through mode

5.Organization:  $18 = x \ 18$

6.Production version: A =first production version

7.Clock access time: [-75 = 7.5 ns; -85 = 8.5 ns; -10 = 10.0 ns]

8.Package type: TQ = TQFP

9.Operating temperature:  $C = commercial (0^{\circ} C to 70^{\circ} C); I = industrial (-40^{\circ} C to 85^{\circ} C)$

10. N = Lead free part

www.DataSheet4U.com

Alliance Semiconductor Corporation 2575, Augustine Drive, Santa Clara, CA 95054 Tel: 408 - 855 - 4900 Fax: 408 - 855 - 4999 www.alsc.com Copyright © Alliance Semiconductor All Rights Reserved Part Number: AS7C332MFT18A Document Version: v 1.3

© Copyright 2003 Alliance Semiconductor Corporation. All rights reserved. Our three-point logo, our name and Intelliwatt are trademarks or registered trademarks of Alliance. All other brand and product names may be the trademarks of their respective companies. Alliance reserves the right to make changes to this document and its products at any time without notice. Alliance assumes no responsibility for any errors that may appear in this document. The data contained herein represents Alliance's best data and/or estimates at the time of issuance. Alliance reserves the right to change or correct this data at any time, without notice. If the product described herein is under development, significant changes to these specifications are possible. The information in this product data sheet is intended to be general descriptive information for potential customers and users, and is not intended to operate as, or provide, any guarantee or warrantee to any user or customer. Alliance does not assume any responsibility or liability arising out of the application or use of any product described herein, and disclaims any express or implied warranties related to the sale and/or use of Alliance products including liability or warranties related to fitness for a particular purpose, merchantability, or infringement of any intellectual property rights, except as express and Conditions of Sale. The purchase of products from Alliance does not convey a license under any patent rights, copyrights; mask works rights, trademarks, or any other intellectual property rights of Alliance or third parties. Alliance does not convey a license under any patent rights, copyrights; mask works rights, trademarks, or any other intellectual property rights of Alliance or third parties. Alliance does not convey a license under any patent rights, copyrights; mask works rights, trademarks, or any other intellectual property rights of Alliance or third parties. Alliance does not convey a license under any patent rights or such is supporting systems where