## **AS3980** UHF RFID Single Chip Reader EPC Class1 Gen2

#### **General Description**

The AS3980 is an UHF RFID reader IC enabling battery-powered, small form-factor handheld and embedded UHF reader systems for a single tag environment of EPC Class1 Gen2 compliant UHF RFID tags. The device directly supports ISO 18000-6C/ EPC Class1 Gen2 transponders in a single-tag environment. The AS3980 operates at very low power, which means that this advanced RFID reader IC is suitable for use in portable and battery-powered equipment such as mobile phones. AS3980 requires only an external simple 8-bit  $\mu$ C to create a complete RFID reader system. AS3980 is highly integrated and implements the RFID functions on chip thus eliminating a need for a complex RFID co-processor. Packaged in a 7 x 7 mm QFN outline, the IC benefits from fabrication process technology unique to **ams** to deliver very high sensitivity and providing high immunity to the effects of antenna reflections and self-jamming. This is critical in mobile and embedded applications, in which antenna design is often compromised by cost or size constraints. High sensitivity enables end-product designs to achieve their required read range while using a simpler and cheaper antenna, thus reducing system bill-of-materials cost.

Ordering Information and Content Guide appear at end of datasheet.

#### **Key Benefits & Features**

The benefits and features of AS3980, UHF RFID Single Chip Reader EPC Class1 Gen2 are listed below:

Figure 1: Added Value of Using AS3980

| Benefit                                   | Feature                                                                                                                                                    |

|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Optimized for battery operation           | <ul> <li>Supply voltage range 3.0V to 3.6V</li> <li>Limited operation possible down to 2.7V</li> <li>Peripheral I/O supply range: 1.65V to 5.5V</li> </ul> |

| ISO 18000-6C implemented in HW.           | Basic protocol support for ISO 18000-6C (EPC Class1 Gen2)                                                                                                  |

| Low coding effort and MCU requirements    | Reception mode M8 on 40kHz link frequency                                                                                                                  |

| High PSRR                                 | Integrated supply regulators                                                                                                                               |

| Flexible modulation method                | ASK or PR-ASK modulation                                                                                                                                   |

| Small package footprint – saving PCB area | • 48-pin QFN (7x7x0.9 mm) package                                                                                                                          |

| Benefit                          | Feature                                           |

|----------------------------------|---------------------------------------------------|

| Avoidance of communication holes | Automatic I/Q selection                           |

| Tag movement detection support   | Phase bit for tag tracking with 8-bit linear RSSI |

| Wide temperature range           | • -40°C to 85°C                                   |

#### Applications

The AS3980 device is well suited for:

- Embedded consumer/industrial applications with cost constraints such as beverage dispensing.

- Hand-Held readers.

- Mobile UHF RFID readers.

- Battery-Powered stationary readers.

- FMCG and brand protection

- Product authentication

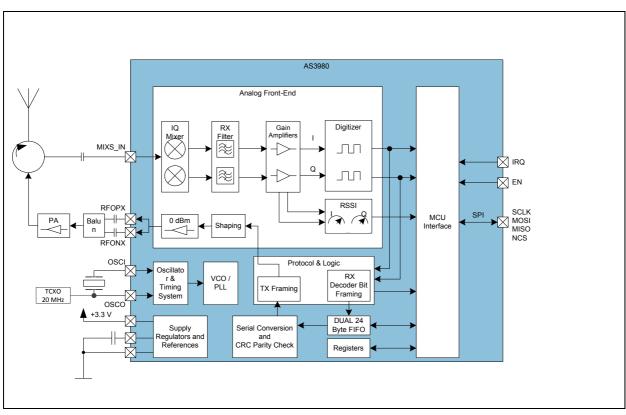

#### **Block Diagram**

The functional blocks of this device for reference are shown below:

Figure 2: AS3980 Block Diagram

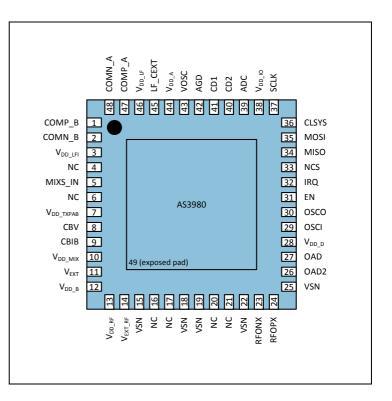

### **Pin Assignment**

#### The AS3980 pin assignments are described below.

Figure 3: Pin Diagram

AS3980 Pin Assignment: This figure shows the pin assignment and location viewed from top.

#### Figure 4: **Pin Description**

| Pin Number | Pin Name              | Pin Type     | Description                                                                 |  |

|------------|-----------------------|--------------|-----------------------------------------------------------------------------|--|

| 48-Pin QFN |                       | гштуре       | Description                                                                 |  |

| 1          | COMP_B                | Analog I/O   | Internal node, connect de-coupling capacitor to $V_{\mbox{DD}\_\mbox{LFI}}$ |  |

| 2          | COMN_B                | Analog I/O   | Internal node, connect de-coupling capacitor to $V_{\mbox{DD\_LFI}}$        |  |

| 3          | V <sub>DD_LFI</sub>   | Supply pad   | Positive supply for LF input stage, connect to $V_{\mbox{DD}\_\mbox{MIX}}$  |  |

| 4          | NC                    |              | Not connected                                                               |  |

| 5          | MIXS_IN               | Analog input | Single ended mixer input                                                    |  |

| 6          | NC                    |              | Not connected                                                               |  |

| 7          | V <sub>DD_TXPAB</sub> | Supply pad   | Bias positive supply. Connect to $V_{DD_MIX}$                               |  |

| 8          | CBV                   | Analog I/O   | Internal node, connect de-coupling capacitor to $V_{\mbox{DD}\_\mbox{MIX}}$ |  |

| 9          | CBIB                  | Analog I/O   | Internal node, connect de-coupling capacitor to ground                      |  |

| 10         | V <sub>DD_MIX</sub>   | Analog I/O   | Mixer positive supply, internally regulated                                 |  |

| Pin Number | Dia Nama            |                               | Description                                                               |

|------------|---------------------|-------------------------------|---------------------------------------------------------------------------|

| 48-Pin QFN | Pin Name            | Pin Type                      | Description                                                               |

| 11         | V <sub>EXT</sub>    | Supply pad                    | Main positive supply input, input to regulators                           |

| 12         | V <sub>DD_B</sub>   | Analog I/O                    | Buffer positive supply, internally regulated                              |

| 13         | V <sub>DD_RF</sub>  | Analog I/O                    | RF positive supply, internally regulated                                  |

| 14         | V <sub>EXT_RF</sub> | Supply pad                    | RF positive supply regulator input                                        |

| 15         | VSN                 | Supply pad                    | Negative supply                                                           |

| 16         | NC                  |                               | Not connected                                                             |

| 17         | NC                  |                               | Not connected                                                             |

| 18         | VSN                 | Supply pad                    | Negative supply                                                           |

| 19         | VSN                 | Supply pad                    | Negative supply                                                           |

| 20         | NC                  |                               | Not connected                                                             |

| 21         | NC                  |                               | Not connected                                                             |

| 22         | VSN                 | Supply pad                    | Negative supply                                                           |

| 23         | RFONX               | Analog output                 | Low power linear negative RF output (~0dBm)                               |

| 24         | RFOPX               | Analog output                 | Low power linear positive RF output (~0dBm)                               |

| 25         | VSN                 | Supply pad                    | Negative supply                                                           |

| 26         | OAD2                | Analog I/O                    | Analog or digital received signal output                                  |

| 27         | OAD                 | Analog I/O                    | Analog or digital received signal output                                  |

| 28         | V <sub>DD_D</sub>   | Analog I/O                    | Positive supply for logic, internally regulated                           |

| 29         | OSCI                | Analog input                  | Crystal oscillator input or short to ground in case external TCXO is used |

| 30         | OSCO                | Analog I/O                    | Crystal oscillator output or external 20MHz clock input                   |

| 31         | EN                  | Digital input                 | Enable input                                                              |

| 32         | IRQ                 | Digital output                | Interrupt request output                                                  |

| 33         | NCS                 | Digital input                 | Serial Peripheral Interface Enable (active low)                           |

| 34         | MISO                | Digital output<br>/ tri-state | Serial Peripheral Interface DATA output                                   |

| 35         | MOSI                | Digital input                 | Serial Peripheral Interface DATA input                                    |

| 36         | CLSYS               | Digital output                | Clock Output for MCU                                                      |

| 37         | SCLK                | Digital input                 | Serial Peripheral Interface Clock                                         |

| Pin Number | Pin Name           | Pin Type      | Description                                                                   |

|------------|--------------------|---------------|-------------------------------------------------------------------------------|

| 48-Pin QFN |                    |               | Decemption                                                                    |

| 38         | V <sub>DD_IO</sub> | Supply pad    | Positive supply for peripheral communication, connect to host positive supply |

| 39         | ADC                | Analog input  | ADC input for external power detector support                                 |

| 40         | CD2                | Analog I/O    | Internal node de-coupling capacitor                                           |

| 41         | CD1                | Analog I/O    | Internal node de-coupling capacitor                                           |

| 42         | AGD                | Analog I/O    | Analog reference voltage                                                      |

| 43         | VOSC               | Analog I/O    | Internal node de-coupling capacitor                                           |

| 44         | $V_{DD_A}$         | Analog I/O    | Analog part positive supply, internally regulated                             |

| 45         | LF_CEXT            | Analog output | PLL Loop filter                                                               |

| 46         | $V_{DD_{LF}}$      | Analog I/O    | Positive supply for LF processing, internally regulated                       |

| 47         | COMP_A             | Analog I/O    | Internal node, connect de-coupling capacitor to $V_{\text{DD}\_\text{LFI}}$   |

| 48         | COMN_A             | Analog I/O    | Internal node, connect de-coupling capacitor to $V_{\text{DD}\_\text{LFI}}$   |

| 49         | Exposed Pad        | Supply pad    | Exposed pad of the package                                                    |

### Absolute Maximum Ratings

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated under Electrical Characteristics is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### Figure 5: Absolute Maximum Ratings

| Symbol              | Parameter                                                                        | Min       | Max                         | Units | Comments                                                                                                                                              |  |  |

|---------------------|----------------------------------------------------------------------------------|-----------|-----------------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                     |                                                                                  | Electrica | al Paramet                  | ers   |                                                                                                                                                       |  |  |

| V <sub>DD_IO</sub>  | Supply voltage V <sub>DD_IO</sub>                                                | -0.3      | 6.0                         | V     |                                                                                                                                                       |  |  |

| V <sub>EXT</sub>    | Supply voltage V <sub>EXT</sub>                                                  | -0.3      | 4                           | V     |                                                                                                                                                       |  |  |

| V <sub>EXT_RF</sub> | Supply voltage V <sub>EXT_RF</sub>                                               | -0.3      | 4.5                         | V     |                                                                                                                                                       |  |  |

| V <sub>INH</sub>    | Input pin voltage host<br>interface                                              | -0.3      | V <sub>DD_IO</sub><br>+ 0.5 | V     | Valid for inputs EN, IRQ, MOSI,<br>SCLK, NCS                                                                                                          |  |  |

| V <sub>INO</sub>    | Input pin voltage, other pins                                                    | -0.3      | V <sub>EXT</sub> +<br>0.5   | V     |                                                                                                                                                       |  |  |

| l_scr               | Input current (latch-up<br>immunity)                                             | -100      | 100                         | mA    | Norm: JEDEC 78, AGD excluded<br>from Latch-up immunity test for EN<br>is high. AGD is a reference voltage<br>pin and must be kept at the<br>reference |  |  |

|                     |                                                                                  | Electrost | atic Disch                  | arge  | ·                                                                                                                                                     |  |  |

| ESD <sub>HBM</sub>  | Electrostatic discharge<br>for the RF pins 5, 23 and ±1 kV<br>ESD <sub>HBM</sub> |           |                             |       | Norm: JESD22-A114E                                                                                                                                    |  |  |

|                     | Electrostatic discharge for other pins                                           | ±2        |                             | kV    |                                                                                                                                                       |  |  |

|                     | Continuous Power Dissipation                                                     |           |                             |       |                                                                                                                                                       |  |  |

| P <sub>T</sub>      | Total power dissipation<br>(all supplies and outputs)                            |           | 1.6                         | W     |                                                                                                                                                       |  |  |

| Symbol            | Parameter                                            | Min | Max | Units | Comments                                                                                                                                                                                                                                         |  |  |  |  |

|-------------------|------------------------------------------------------|-----|-----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                   | Temperature Ranges and Storage Conditions            |     |     |       |                                                                                                                                                                                                                                                  |  |  |  |  |

| Тյ                | Maximum operating<br>virtual junction<br>temperature |     | 120 | °C    |                                                                                                                                                                                                                                                  |  |  |  |  |

| T <sub>strg</sub> | Storage temperature                                  | -55 | 125 | °C    |                                                                                                                                                                                                                                                  |  |  |  |  |

| T <sub>body</sub> | Package Body<br>Temperature                          |     | 260 | °C    | Norm: IPC/JEDEC J-STD-020. The<br>reflow peak soldering temperature<br>(body temperature) is specified<br>according IPC/JEDEC J-STD-020<br>"Moisture/Reflow Sensitivity<br>Classification for Non-hermetic<br>Solid State Surface Mount Devices" |  |  |  |  |

| RH <sub>NC</sub>  | Relative Humidity<br>non-condensing                  | 5   | 85  | %     |                                                                                                                                                                                                                                                  |  |  |  |  |

| MSL               | Moisture Sensitivity<br>Level                        |     | 3   |       | Represents a max. floor life time of 168h                                                                                                                                                                                                        |  |  |  |  |

### **Electrical Characteristics**

All limits are guaranteed. The parameters with min and max values are guaranteed with production tests or SQC (Statistical Quality Control) methods.

$V_{EXT}$  = 3.3 V,  $V_{EXT\_RF}$  = 3.3 V,  $V_{DD\_IO}$  = 3.3 V,  $T_A$  = 25 °C unless otherwise noted.

Figure 6: Electrical Characteristics

| Symbol                 | Parameter                                                        | Conditions                                                    | Min               | Тур  | Max  | Units |

|------------------------|------------------------------------------------------------------|---------------------------------------------------------------|-------------------|------|------|-------|

| I <sub>EXT</sub>       | Supply current without<br>VDD_RF current                         | V <sub>EXT</sub> consumption                                  | 65 <sup>(1)</sup> | 75   |      | mA    |

| I <sub>STBY</sub>      | Supply current in standby mode                                   |                                                               |                   | 3    |      | mA    |

| I <sub>PD</sub>        | Supply current in<br>power-down mode                             | All system disabled<br>including supply<br>voltage regulators |                   | 1    | 10   | μΑ    |

| V <sub>AGD</sub>       | AGD voltage                                                      |                                                               | 1.45              | 1.55 | 1.65 | V     |

| V <sub>POR</sub>       | Power on reset voltage<br>(POR)                                  |                                                               | 1                 | 1.8  | 2.0  | V     |

| V <sub>RD</sub>        | Regulator drop                                                   | see note (2)                                                  |                   | 300  |      | mV    |

| P <sub>PSSR</sub>      | Rejection of external supply<br>noise on the supply<br>regulator | see note (3)                                                  |                   | 26   |      | dB    |

| P <sub>RF</sub>        | RF output power                                                  | $V_{DD_B} = 3V$                                               |                   | 0    |      | dBm   |

| R <sub>RFIN</sub>      | Single ended mixer input<br>impedance                            |                                                               |                   | 50   |      | Ω     |

| V <sub>SENS_NOM</sub>  | Input sensitivity                                                | Nominal mixer<br>setting, PER=0.1%                            |                   | -67  |      | dBm   |

| V <sub>SENS_GAIN</sub> | Input sensitivity                                                | Increased mixer<br>gain, PER=0.1%                             |                   | -77  |      | dBm   |

| V <sub>SENS_LBT</sub>  | LBT sensitivity                                                  | Maximum LBT<br>sensitivity                                    |                   | -90  |      | dBm   |

| IP3                    | Third order intercept point                                      | Nominal mixer<br>setting <sup>(4)</sup><br>VEXT = 3V          |                   | 17   |      | dBm   |

| 1dB <sub>CP</sub>      | Input 1dB compression point                                      | Nominal mixer<br>setting <sup>(4)</sup><br>VEXT = 3V          |                   | 7    |      | dBm   |

| T <sub>REC</sub>       | Recovery time after modulation                                   | Maximum LF<br>selected                                        |                   | 18   |      | μs    |

| Symbol            | Parameter                                                                  | Conditions                                                                       | Min                         | Тур          | Max                         | Units  |

|-------------------|----------------------------------------------------------------------------|----------------------------------------------------------------------------------|-----------------------------|--------------|-----------------------------|--------|

|                   | CMOS In                                                                    | put (valid for all CMOS                                                          | inputs)                     |              |                             |        |

| V <sub>IH</sub>   | High level input voltage                                                   | see note (5)                                                                     | 0.8 *<br>V <sub>DD_IO</sub> |              |                             | V      |

| V <sub>IL</sub>   | Low level input voltage                                                    | see note (6)                                                                     |                             |              | 0.2 *<br>V <sub>DD_IO</sub> | V      |

| I <sub>LEAK</sub> | Input leakage current                                                      |                                                                                  |                             |              | 1                           | μΑ     |

|                   | <b>CMOS Out</b><br>outputs, it is recommended to e<br>ent/spikes problems. | put (valid for all CMOS<br>use loads with the small                              |                             | l drive capa | ability in ord              | der to |

|                   |                                                                            | $hs\_output = 1^{(7)},$<br>$V_{DD\_IO} \ge 3V,$<br>$C_{LOAD} = 50pF$             |                             |              | 5                           | MHz    |

| f <sub>SCLK</sub> | SCLK frequency                                                             | <b>hs_output</b> = 1,<br>V <sub>DD_IO</sub> ≥ 1.65V,<br>C <sub>LOAD</sub> = 50pF |                             |              | 3                           | MHz    |

|                   |                                                                            | <b>hs_output</b> = 0,<br>V <sub>DD_IO</sub> ≥ 3V,<br>C <sub>LOAD</sub> = 50pF    |                             |              | 2                           | MHz    |

| R <sub>NMOS</sub> | Output NMOS resistance on digital pins                                     | hs_output = 1                                                                    |                             | 120          |                             | Ω      |

| R <sub>PMOS</sub> | Output PMOS resistance on                                                  | $hs\_output = 1, V_{DD\_IO} > 3V$                                                |                             | 150          |                             | Ω      |

| "PMOS             | digital pins                                                               | <b>hs_output</b> = 1,<br>V <sub>DD_IO</sub> > 1.65V                              |                             | 300          |                             | Ω      |

#### Note(s) and/or Footnote(s):

1. Using **ic\_bia\_m<1:0>** option bits, the consumption can be decreased up to 9%. The drawback of decreased power consumption can be higher noise, lower output power, and declining sensitivity.

2. After execution of direct command: Automatic Power Supply Level Setting (A2 $_{\rm h}$ ).

3. The difference between the external supply and the regulated voltage is higher than 300mV.

4. Register settings for nominal mixer settings:  $0A:01_h$ ,  $0D:84_h$ ,  $22:13_h$ .

5. At supply voltage  $\leq$  1.8V, the minimum VIH is defined as 0.9\*V<sub>DD IO</sub>.

6. At supply voltage  $\leq$  1.8V, the maximum VIL is defined as 0.1\*V<sub>DD IO</sub>.

7. Option bit 7 of Miscellaneous Register 1.

## Typical Operating Characteristics

All in this specification defined tolerances for external components need to be assured over the whole operation condition range and also over lifetime.

#### Figure 7:

**Typical Operating Characteristics**

| Symbol              | Parameter                                     | Min  | Max | Units | Comments                                                                                                                                                                     |

|---------------------|-----------------------------------------------|------|-----|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>DD_IO</sub>  | Positive supply voltage<br>V <sub>DD_IO</sub> | 1.65 | 5.5 | V     |                                                                                                                                                                              |

| V <sub>EXT</sub>    | Positive supply voltage<br>V <sub>EXT</sub>   | 2.7  | 3.6 | V     | For optimal power supply rejection and performance a supply voltage of at least 3.3                                                                                          |

| V <sub>EXT_RF</sub> | Positive supply voltage<br>V <sub>EXTRF</sub> | 2.7  | 4.3 | V     | V is required. A supply voltage<br>above 3.0V allows operation<br>with reduced power supply<br>rejection. Operation down to<br>2.7V is possible with reduced<br>performance. |

| V <sub>SS</sub>     | Negative supply voltage                       | 0    | 0   | V     | Valid for all VSS and VSN pins                                                                                                                                               |

| T <sub>AMB</sub>    | Ambient temperature                           | -40  | 85  | °C    |                                                                                                                                                                              |

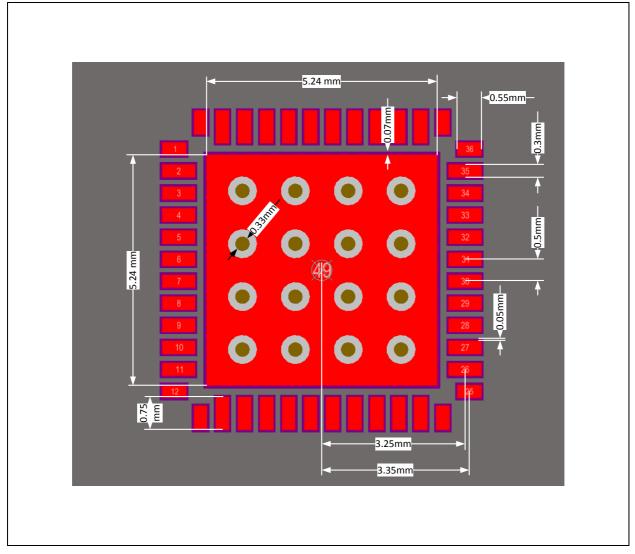

## **PCB Pad Layout**

Figure 8: Recommended PCB Pad Layout

**AS3980 PCB Pad Layout :** This figure shows the recommended PCB land pattern of the AS3980 device.

#### **Soldering Information**

#### **Stencil Design & Solder Paste Application**

- 1. Stainless steel stencils are recommended for solder paste application.

- 2. A stencil thickness of 0.125 0.150 mm (5 6 mils) is recommended for screening.

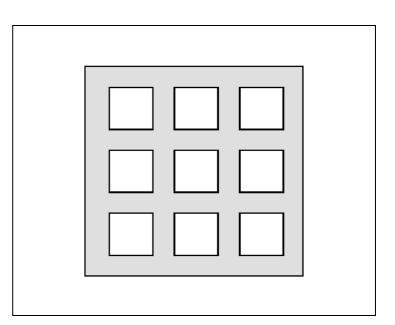

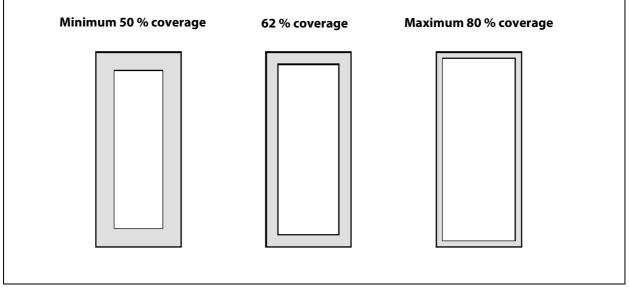

- 3. For the PCB thermal pad, solder paste should be printed on the PCB by designing a stencil with an array of smaller openings that sum to 50% of the QFN thermal pad area as shown in Figure 9.

- 4. The aperture opening for the signal pads should be between 50-80% of the QFN pad area as shown in Figure 10.

- 5. Optionally, for better solder paste release, the aperture walls should be trapezoidal and the corners rounded.

- The fine pitch of the IC leads requires accurate alignment of the stencil and the printed circuit board. The stencil and printed circuit assembly should be aligned to within + 1 mil prior to application of the solder paste.

- 7. No-clean flux is recommended since flux from underneath the thermal pad will be difficult to clean if water-soluble flux is used.

**Solder Paste Paddle Pattern:** Solder paste should be applied through an array of squares (or circles) which totals 50 % of the total area of the paddle.

#### Figure 10: Solder Paste Application on Pads

Solder Paste on Pads: The aperture opening for the signal pads should be between 50-80% of the QFN pad area.

#### **Soldering Options & Package Placement**

- 1. Hand soldering of these devices is not recommended even for prototypes.

- 2. Infrared or Convection mass reflow soldering is the preferred method of QFN attachment.

- 3. Manual placement and/or manual repositioning of QFN packages is not recommended.

#### **Solder Reflow Profile**

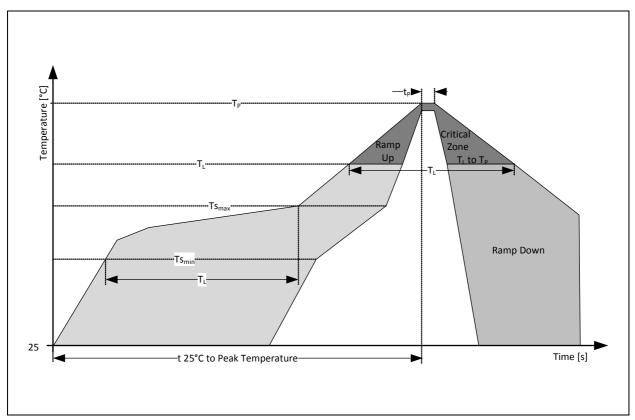

The PCB assembly should be instrumented and the reflow oven's process parameters established to ensure the solder paste manufacturer's reflow profile specification is met during the assembly process. See Figure 12.

The maximum PCB temperature recommended by the supplier must not be exceeded.

Figure 11: Solder Reflow Profile

| Profile Feature                                                                                                                                   | Lead-free Assembly                   |

|---------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| Average ramp-up rate (Ts <sub>max</sub> to T <sub>P</sub> )                                                                                       | 3 °C/second max.                     |

| <ul> <li>Preheat</li> <li>Temperature Min (Ts<sub>min</sub>)</li> <li>Temperature Max (Ts<sub>max</sub>)</li> <li>Time (t<sub>L</sub>)</li> </ul> | 150 °C<br>200 °C<br>60 – 120 seconds |

| Time maintained above:         • Temperature (TL)         • Time (tL)                                                                             | 217 °C<br>60 – 150 seconds           |

| Peak/classification temperature (T <sub>P</sub> )                                                                                                 | 260 °C                               |

| Time within 5 °C of actual peak temperature ( $T_P$ )                                                                                             | 30 seconds                           |

| Ramp-down rate                                                                                                                                    | 6 °C/second max.                     |

| Time 25 °C to peak temperature                                                                                                                    | 8 minutes max.                       |

JEDEC standard Lead-free reflow profile: According to J-STD-020D.

#### Figure 12:

**Recommended Reflow Soldering Profile**

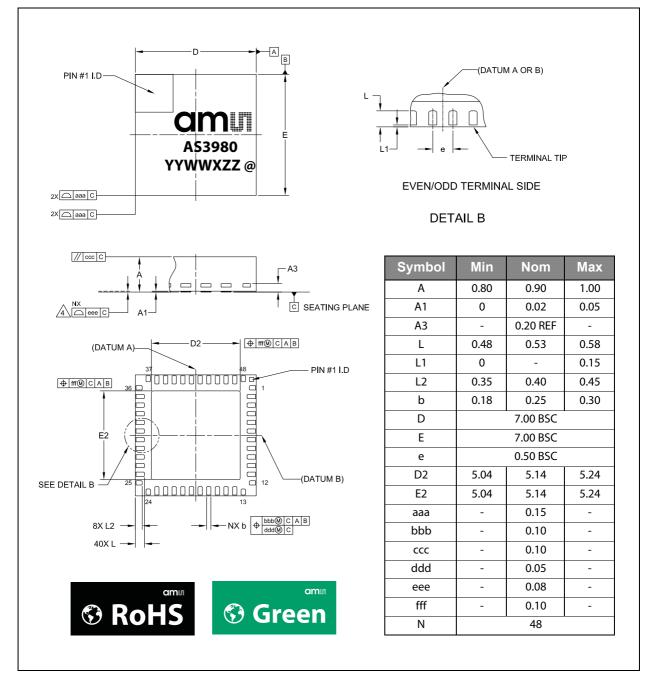

### Package Drawings & Markings

#### Note(s) and/or Footnote(s):

- 1. Dimensioning and tolerances conform to ASME Y14.5M-1994.

- 2. All dimensions are in millimeters. Angles are in degrees.

- 3. Dimension b applies to metallized terminal and is measured between 0.25mm and 0.30mm from terminal tip. Dimension L1 represents terminal full back from package edge up to 0.15mm is acceptable.

- 4. Co-planarity applies to the exposed heat slug as well as the terminal.

- 5. Radius on terminal is optional.

- 6. N is the total number of terminals.

- 7. This drawing is subject to change without notice.

Figure 14: Packaging Code YYWWXZZ@

| YY   | ww                                   | X                | ZZ                                 | @                 |

|------|--------------------------------------|------------------|------------------------------------|-------------------|

| Year | Working week assembly /<br>packaging | Plant identifier | Free choice /<br>traceability code | Sublot Identifier |

Packaging Code YYWWXZZ: This figure explains the laser marked date code on the package.

### Ordering & Contact Information

Figure 15: Ordering Information

| Ordering Code | Package                    | Marking | Delivery Form | Delivery<br>Quantity |

|---------------|----------------------------|---------|---------------|----------------------|

| AS3980-BQFM   | 48-pin QFN<br>(7x7x0.9 mm) | AS3980  | Tape & Reel   | 50                   |

| AS3980-BQFT   |                            |         |               | 500                  |

Ordering Information: This figure shows ordering information for the AS3980 device.

Buy our products or get free samples online at: www.ams.com/ICdirect

Technical Support is available at: www.ams.com/Technical-Support

Provide feedback about this document at: www.ams.com/Document-Feedback

For further information and requests, e-mail us at: ams\_sales@ams.com

For sales offices, distributors and representatives, please visit: www.ams.com/contact

#### Headquarters

ams AG Tobelbaderstrasse 30 8141 Unterpremstaetten Austria, Europe

Tel: +43 (0) 3136 500 0 Website: www.ams.com

### RoHS Compliant & ams Green Statement

**RoHS:** The term RoHS compliant means that ams AG products fully comply with current RoHS directives. Our semiconductor products do not contain any chemicals for all 6 substance categories, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, RoHS compliant products are suitable for use in specified lead-free processes.

**ams Green (RoHS compliant and no Sb/Br):** ams Green defines that in addition to RoHS compliance, our products are free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material).

**Important Information:** The information provided in this statement represents ams AG knowledge and belief as of the date that it is provided. ams AG bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. ams AG has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. ams AG and ams AG suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

### **Copyrights & Disclaimer**

Copyright ams AG, Tobelbader Strasse 30, 8141 Unterpremstaetten, Austria-Europe. Trademarks Registered. All rights reserved. The material herein may not be reproduced, adapted, merged, translated, stored, or used without the prior written consent of the copyright owner.

Devices sold by ams AG are covered by the warranty and patent indemnification provisions appearing in its General Terms of Trade. ams AG makes no warranty, express, statutory, implied, or by description regarding the information set forth herein. ams AG reserves the right to change specifications and prices at any time and without notice. Therefore, prior to designing this product into a system, it is necessary to check with ams AG for current information. This product is intended for use in commercial applications. Applications requiring extended temperature range, unusual environmental requirements, or high reliability applications, such as military, medical life-support or life-sustaining equipment are specifically not recommended without additional processing by ams AG for each application. This product is provided by ams AG "AS IS" and any express or implied warranties, including, but not limited to the implied warranties of merchantability and fitness for a particular purpose are disclaimed.

ams AG shall not be liable to recipient or any third party for any damages, including but not limited to personal injury, property damage, loss of profits, loss of use, interruption of business or indirect, special, incidental or consequential damages, of any kind, in connection with or arising out of the furnishing, performance or use of the technical data herein. No obligation or liability to recipient or any third party shall arise or flow out of ams AG rendering of technical or other services.

#### **Document Status**

| Document Status          | Product Status  | Definition                                                                                                                                                                                                                                                                     |

|--------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Product Preview          | Pre-Development | Information in this datasheet is based on product ideas in<br>the planning phase of development. All specifications are<br>design goals without any warranty and are subject to<br>change without notice                                                                       |

| Preliminary Datasheet    | Pre-Production  | Information in this datasheet is based on products in the<br>design, validation or qualification phase of development.<br>The performance and parameters shown in this document<br>are preliminary without any warranty and are subject to<br>change without notice            |

| Datasheet                | Production      | Information in this datasheet is based on products in<br>ramp-up to full production or full production which<br>conform to specifications in accordance with the terms of<br>ams AG standard warranty as given in the General Terms of<br>Trade                                |

| Datasheet (discontinued) | Discontinued    | Information in this datasheet is based on products which<br>conform to specifications in accordance with the terms of<br>ams AG standard warranty as given in the General Terms of<br>Trade, but these products have been superseded and<br>should not be used for new designs |

## **Revision Information**

The initial version of short datasheet was derived from version 2-01 of full datasheet.

#### **Content Guide**

#### 1 General Description

- 1 Key Benefits & Features

- 2 Applications

- 2 Block Diagram

- 3 Pin Assignment

- 6 Absolute Maximum Ratings

- 8 Electrical Characteristics

- **10** Typical Operating Characteristics

- 11 PCB Pad Layout

- 12 Soldering Information

- 12 Stencil Design & Solder Paste Application

- 13 Soldering Options & Package Placement

- 13 Solder Reflow Profile

- 15 Package Drawings & Markings

- 17 Ordering & Contact Information

- **18 RoHS Compliant & ams Green Statement**

- **19** Copyrights & Disclaimer

- 20 Document Status

- 21 Revision Information