a leap ahead in analog

AS1324 Data Sheet

## 1.5MHz, 600mA, DC/DC Step-Down Regulator

# 1 General Description

The AS1324 is a high-efficiency, constant-frequency synchronous buck converter available in adjustable- and fixed-voltage versions. The wide input voltage range (2.7V to 5.5V), automatic powersave mode and minimal external component requirements make the AS1324 perfect for any single Li-Ion battery-powered application.

Typical supply current with no load is 30µA and decreases to ≤1µA in shutdown mode.

The AS1324 is available as the standard versions listed in Table 1.

Table 1. Standard Versions

| Model     | Output Voltage                    |

|-----------|-----------------------------------|

| AS1324-AD | Adjustable via External Resistors |

| AS1324-12 | Fixed: 1.2V                       |

| AS1324-15 | Fixed: 1.5V                       |

| AS1324-18 | Fixed: 1.8V                       |

An internal synchronous switch increases efficiency and eliminates the need for an external Schottky diode. The internally fixed switching frequency (1.5MHz) allows for the use of small surface mount external components.

Very low output voltages can be delivered with the internal 0.6V feedback reference voltage.

The AS1324 is available in a 5-pin TSOT-23 package.

# 2 Key Features

High Efficiency: Up to 96%

Output Current: 600mA

■ Input Voltage Range: 2.7V to 5.5V

Constant Frequency Operation: 1.5MHz

■ Variable- and Fixed-Output Voltages

No Schottky Diode Required

Automatic Powersave Operation

■ Low Quiescent Current: 30µA

Internal Reference: 0.6V

Shutdown Mode Supply Current: ≤1µA

Thermal Protection

5-pin TSOT-23 Package

# 3 Applications

The device is ideal for mobile communication devices, laptops and PDAs, ultra-low-power systems, threshold detectors/discriminators, telemetry and remote systems, medical instruments, or any other space-limited application with low power-consumption requirements.

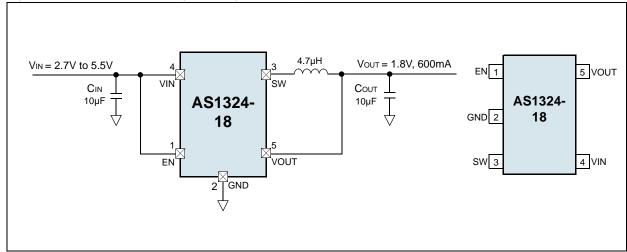

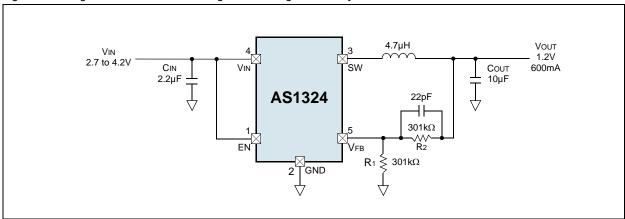

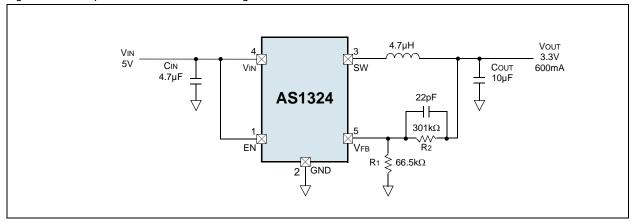

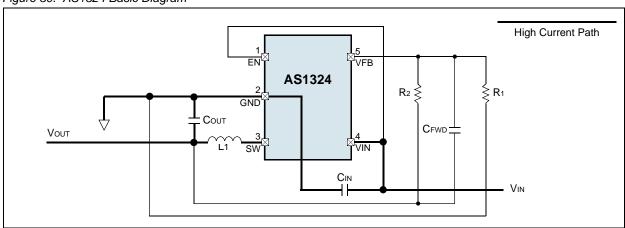

Figure 1. Typical Application Diagram - High Efficiency Step Down Converter

# 4 Pinout and Packaging

## **Pin Assignments**

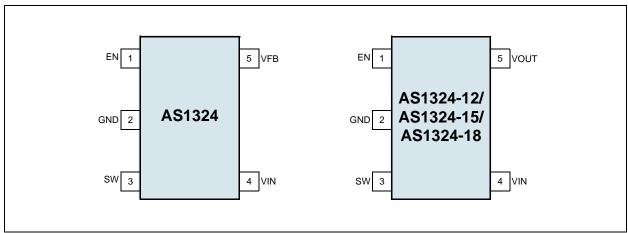

Figure 2. Pin Assignments (Top View)

## **Pin Descriptions**

Table 2. Pin Descriptions

| Pin<br>Number | Pin Name | Description                                                                                                                                                                                                                                                                     |

|---------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1             | EN       | Enable Input. Driving this pin above 1.5V enables the device. Driving this pin below 0.3V puts the device in shutdown mode. In shutdown mode all functions are disabled while SW goes high impedance, drawing <1µA supply current.  Note: This pin should not be left floating. |

| 2             | GND      | Ground.                                                                                                                                                                                                                                                                         |

| 3             | SW       | <b>Switch Node Connection to Inductor.</b> This pin connects to the drains of the internal main and synchronous power MOSFET switches.                                                                                                                                          |

| 4             | VIN      | <b>Input Supply Voltage</b> . This pin must be closely decoupled to GND with a $\geq 4.7 \mu F$ ceramic capacitor. Connect to any supply voltage between 2.7 to 5.5V.                                                                                                           |

| 5             | VFB      | <b>Feedback Pin</b> . This pin receives the feedback voltage from the external resistor divider across the output. (Adjustable voltage variant only.)                                                                                                                           |

| 5             | VOUT     | Output Voltage Feedback Pin. An internal resistor divider steps the output voltage down for comparison to the internal reference voltage. (Fixed voltage variants only.)                                                                                                        |

# **5 Absolute Maximum Ratings**

Stresses beyond those listed in Table 3 may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in Section 6 Electrical Characteristics on page 4 is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Table 3. Absolute Maximum Ratings

| Parameter                   | Min  | Max          | Units | Comments                                                                                                                                                                                                                                                                            |

|-----------------------------|------|--------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VIN to GND                  | -0.3 | 7            | V     |                                                                                                                                                                                                                                                                                     |

| SW, EN, FB to GND           | -0.3 | VIN<br>+ 0.3 | V     |                                                                                                                                                                                                                                                                                     |

| Thermal Resistance ⊕JA      |      | 207.4        | °C/W  | on PCB                                                                                                                                                                                                                                                                              |

| ESD                         | 2    | 2            | kV    | HBM MIL-Std. 883E 3015.7 methods                                                                                                                                                                                                                                                    |

| Latch-Up                    | -100 | +100         | mA    | JEDEC 78                                                                                                                                                                                                                                                                            |

| Operating Temperature Range | -40  | +85          | °C    |                                                                                                                                                                                                                                                                                     |

| Storage Temperature Range   | -65  | +125         | °C    |                                                                                                                                                                                                                                                                                     |

| Package Body Temperature    |      | +260         | °C    | The reflow peak soldering temperature (body temperature) specified is in accordance with IPC/JEDEC J-STD-020C "Moisture/Reflow Sensitivity Classification for Non-Hermetic Solid State Surface Mount Devices".  The lead finish for Pb-free leaded packages is matte tin (100% Sn). |

| Junction Temperature        |      | 125          | °C    | Junction temperature (TJ) is calculated from<br>the ambient temperature (TAMB) and power<br>dissipation (PD) as:<br>$TJ = TAMB + (PD)(207.4^{\circ}C/W) \qquad (EQ 1)$                                                                                                              |

# **6 Electrical Characteristics**

VIN = EN = 3.6V, VOUT < VIN - 0.5V, TAMB = -40 to  $+85^{\circ}C$ , typ. values @  $TAMB = +25^{\circ}C$  (unless otherwise specified).

Table 4. Electrical Characteristics

| Symbol                                                               | Parameter                                  | Conditions                                                                                                                                   | Min   | Тур   | Max   | Units |  |

|----------------------------------------------------------------------|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|--|

| Vin                                                                  | Input Voltage Range                        |                                                                                                                                              | 2.7   |       | 5.5   | V     |  |

| lQ                                                                   | Quiescent Current                          | Powersave Mode; VFB = 0.62V or Vout = 103%, lout = 0mA, TAMB = +25°C                                                                         |       | 30    | 35    | μA    |  |

| ISHDN                                                                | Shutdown Current                           | Shutdown Mode; VEN = 0V, TAMB = +25°C                                                                                                        |       | 0.1   | 1     |       |  |

| Regulation                                                           | 1                                          |                                                                                                                                              |       |       |       |       |  |

| VFB                                                                  | Regulated Feedback<br>Voltage <sup>1</sup> | AS1324, IOUT = 100mA                                                                                                                         | 0.585 | 0.6   | 0.615 | V     |  |

| ΔVFB                                                                 | Reference Voltage<br>Line Regulation       | VIN = 2.7V to 5.5V                                                                                                                           |       | 0.1   | 1     | %/V   |  |

| IVFB                                                                 | Feedback Current                           | <i>TAMB</i> = +25°C                                                                                                                          | -30   |       | 30    | nA    |  |

|                                                                      |                                            | AS1324-AD, IOUT = 100mA <sup>2</sup>                                                                                                         | VFB   |       |       |       |  |

| IQ ISHDN Regulation VFB  ΔVFB IVFB  VOUT  ΔVOUT VLOADREG IPK RPFET F | Regulated Output                           | AS1324-12, IOUT = 100mA                                                                                                                      | 1.164 | 1.20  | 1.236 | V     |  |

|                                                                      | Voltage                                    | AS1324-15, IOUT = 100mA                                                                                                                      | 1.455 | 1.50  | 1.545 | , v   |  |

|                                                                      |                                            | AS1324-18, IOUT = 100mA                                                                                                                      | 1.746 | 1.80  | 1.854 |       |  |

| ΔVουτ                                                                | Output Voltage<br>Line Regulation          | VIN = 2.7 to 5.5V                                                                                                                            |       | 0.1   | 1     | %/V   |  |

| VLOADREG                                                             | Output Voltage<br>Load Regulation          | Iout = 0 to 100mA                                                                                                                            |       | 0.02  |       | %/mA  |  |

| DC-DC Sw                                                             | itches                                     |                                                                                                                                              |       |       |       |       |  |

| lрк                                                                  | Peak Inductor Current                      | $\label{eq:Vin} \begin{aligned} \text{Vin} = 3\text{V, Vfb} = 0.5\text{V or Vout} = 90\%, \\ \text{TAMB} = 25^{\circ}\text{C} \end{aligned}$ | 0.5   | 0.75  | 1     | А     |  |

| RPFET                                                                | P-Channel FET RDS(ON)                      | ILSW = 100mA                                                                                                                                 |       | 0.4   |       | Ω     |  |

| RNFET                                                                | N-Channel FET RDS(ON)                      | ILSW = -100mA                                                                                                                                |       | 0.35  |       | Ω     |  |

| ILSW                                                                 | SW Leakage                                 | VEN = 0V, VSW = 0V or 5V                                                                                                                     |       | ±0.01 | ±1    | μΑ    |  |

| Control In                                                           | puts                                       |                                                                                                                                              |       |       |       |       |  |

| VEN                                                                  | EN Threshold                               |                                                                                                                                              | 0.3   | 1     | 1.5   | V     |  |

| len                                                                  | EN Leakage Current                         |                                                                                                                                              |       | ±0.01 | ±1    | μA    |  |

| Oscillator                                                           |                                            |                                                                                                                                              |       |       |       |       |  |

| fosc                                                                 | Oscillator Frequency                       | VFB = 0.6V or Vout = 100%                                                                                                                    | 1.2   | 1.5   | 1.8   | MHz   |  |

| 1030                                                                 | Oscillator i requerity                     | $V_{FB} = 0V$ or $V_{OUT} = 0V$ , $T_{AMB} = 25^{\circ}C$                                                                                    |       | 115   |       | kHz   |  |

<sup>1.</sup> The device is tested in a proprietary test mode where VFB is connected to the output of the error amplifier.

<sup>2.</sup> Please see Feedback Resistor Selection on page 13 for resistor values.

*a*B austria**micro**systems

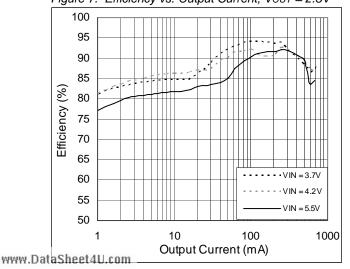

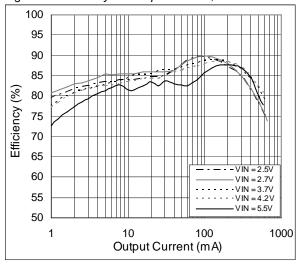

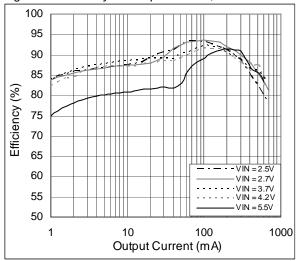

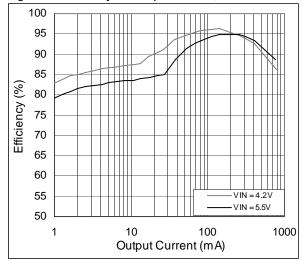

# 7 Typical Operating Characteristics

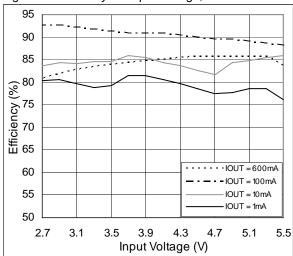

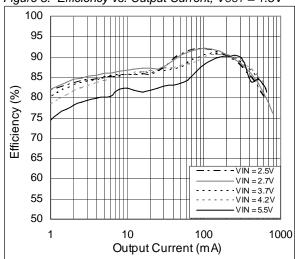

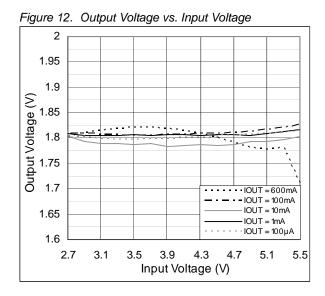

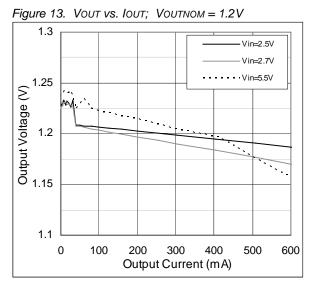

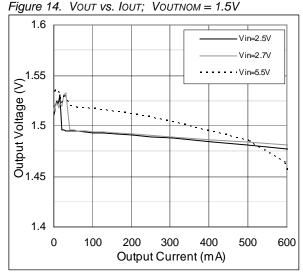

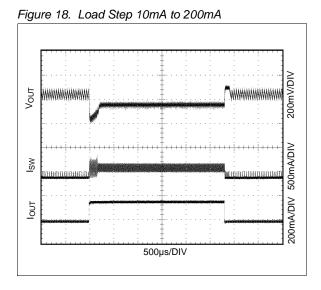

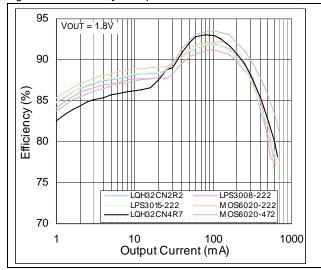

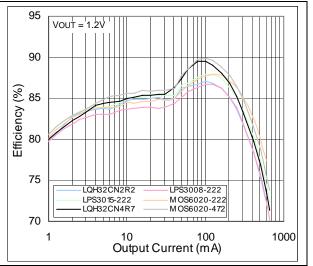

Parts used for measurement: 4.7µH (MOS6020-472) Inductor, 10µF (GRM188R60J106ME47) CIN and COUT.

Figure 3. Efficiency vs. Input Voltage; Vout = 1.8V

Figure 5. Efficiency vs. Output Current; Vout = 1.5V

Figure 7. Efficiency vs. Output Current; Vout = 2.5V

Figure 4. Efficiency vs. Output Current; Vout = 1.2V

Figure 6. Efficiency vs. Output Current; Vout = 1.8V

Figure 8. Efficiency vs. Output Current; Vout = 3.3V

www.DataSheet4U.com

Figure 9. Switching Frequency vs. Supply Voltage

1.6

(RHW) 1.55

(OUTHON 1.55)

(OUTHON 1.45)

(OUTHON

Figure 10. Switching Frequency vs. Temperature

1.6

(NHW)

1.55

1.4

-45 -30 -15 0 15 30 45 60 75 90

Temperature (°C)

Figure 11. Feedback Voltage vs. Temperature

0.61

0.605

0.605

0.595

-45 -30 -15 0 15 30 45 60 75 90

Temperature (C°)

Figure 15. Quiescent Current vs. Input Voltage 50 45 40 5

3.9

Input Voltage (V)

4.3

4.7

5.1

5.5

3.1

2.7

3.5

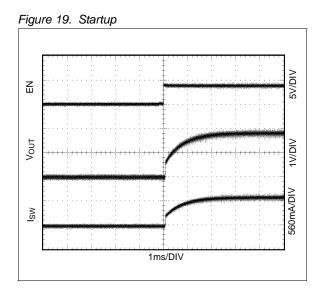

Figure 17. Load Step 0mA to 600mA

Figure 16. Quiescent Current vs. Temperature 50 45 40 Ouiescent Current (µA) 22 20 15 10 5 -45 -30 -15 0 15 30 60 75 45 90 Temperature (°C)

200mV/DIV Vou 500mA/DIV lsw 600mA/DIV lout

500µs/DIV

# 8 Detailed Description

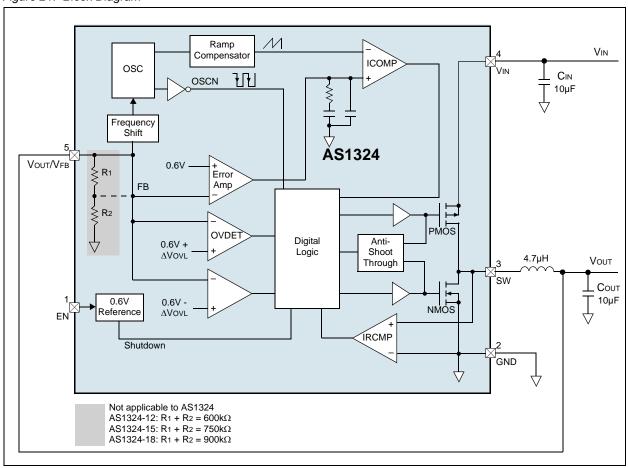

The AS1324 is a high-efficiency buck converter that uses a constant-frequency current-mode architecture. The device contains two internal MOSFET switches and is available in adjustable- and fixed-output voltage versions.

Figure 21. Block Diagram

## **Main Control Loop**

During PWM operation the converters use a 1.5MHz fixed-frequency, current-mode control scheme. Basis of the current-mode PWM controller is an open-loop, multiple input comparator that compares the error-amp voltage feedback signal against the sum of the amplified current-sense signal and the slope-compensation ramp. At the beginning of each clock cycle, the internal high-side PMOS turns on until the PWM comparator trips. During this time the current in the inductor ramps up, sourcing current to the output and storing energy in the inductor's magnetic field. When the PMOS turns off, the internal low-side NMOS turns on. Now the inductor releases the stored energy while the current ramps down, still providing current to the output. The output capacitor stores charge when the inductor current exceeds the load and discharges when the inductor current is lower than the load. Under overload conditions, when the inductor current exceeds the current limit, the high-side PMOS is turned off and the low-side NMOS remains on until the next clock cycle.

When the PMOS is off, the NMOS is turned on until the inductor current starts to reverse (as indicated by the current reversal comparator (IRCMP)), or the next clock cycle begins. The IRCMP detects the zero crossing.

The peak inductor current (IPK) is controlled by the error amplifier. When IOUT increases, VFB decreases slightly relative to the internal 0.6V reference, causing the error amplifier's output voltage to increase until the average inductor current matches the new load current.

The over-voltage detection comparator (OVDET) guards against transient overshoots by turning the main switch off and keeping it off until the transient is removed.

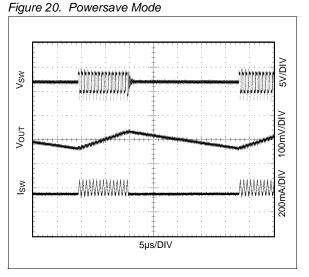

## **Powersave Operation**

The AS1324 uses an automatic powersave mode where the peak inductor current (IPK) is set to approximately 200mA while independent of the output load. In powersave mode, load current is supplied solely from the output capacitor. As the output voltage drops, the error amplifier output rises above the powersave threshold signaling to switch into PWM fixed frequency mode and turn the PMOS on. This process repeats at a rate determined by the load demand.

Each burst event can last from a few cycles at light loads to almost continuous cycling (with short sleep intervals) at moderate loads. In between bursts, the power MOSFETs are turned off, as is any unneeded circuitry, reducing quiescent current to 30µA.

### **Short-Circuit Protection**

In cases where the AS1324 output is shorted to ground, the oscillator frequency (fosc) is reduced to 1/13 the nominal frequency ( $\cong$  115kHz). This frequency reduction ensures that the inductor current has more time to decay, thus preventing runaway conditions. fosc will progressively increase to 1.5MHz when VFB/VOUT > 0V.

#### **Shutdown**

Connecting EN to GND or logic low places the AS1324 in shutdown mode and reduces the supply current to 0.1µA. In shutdown the control circuitry and the internal NMOS and PMOS turn off and SW becomes high impedance disconnecting the input from the output. The output capacitance and load current determine the voltage decay rate. For normal operation connect EN to VIN or logic high.

Note: Pin EN should not be left floating.

# 9 Application Information

The AS1324 is perfect for mobile communications equipment like cell phones and smart phones, digital cameras and camcorders, portabel MP3 and DVD players, PDA's and palmtop computers and any other handheld instruments.

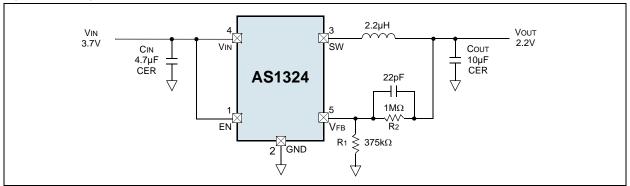

Figure 22. Single Li-Ion 1.2V/600mA Regulator for High-Efficiency

Figure 23. 5V Input to 3.3V/600mA Buck Regulator

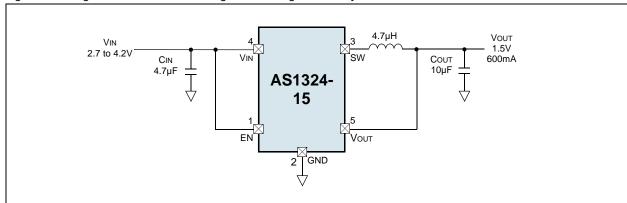

Figure 24. Single Li-Ion 1.5V/600mA Regulator for High-Efficiency

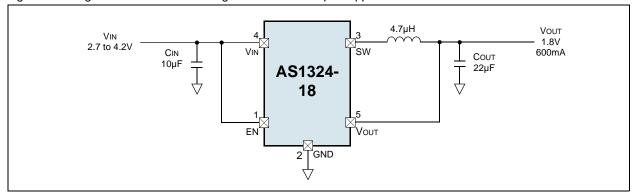

Figure 25. Single Li-Ion 1.8V/600mA Regulator for Low Output Ripple

### **External Component Selection**

#### **Inductor Selection**

For most applications the value of the external inductor should be in the range of 2.2 to 6.8µH as the inductor value has a direct effect on the ripple current. The selected inductor must be rated for its DC resistance and saturation current. The inductor ripple current (ΔIL) decreases with higher inductance and increases with higher Vin or Vout.

In Equation (EQ 2) the maximum inductor current in PWM mode under static load conditions is calculated. The saturation current of the inductor should be rated higher than the maximum inductor current as calculated with Equation (EQ 3). This is recommended because the inductor current will rise above the calculated value during heavy load transients.

$$\Delta I_{L} = V_{OUT} \times \frac{1 - \frac{V_{OUT}}{V_{IN}}}{L \times f}$$

(EQ 2)

$$I_{LMAX} = I_{OUTMAX} + \frac{\Delta I_{L}}{2}$$

(EQ 3)

#### Where:

f = Switching Frequency (1.5 MHz typical)

L = Inductor Value

ILmax = Maximum Inductor current

$\Delta I_L$  = Peak to Peak inductor ripple current

The recommended starting point for setting ripple current is  $\Delta IL = 240 \text{mA}$  (40% of 600mA).

The DC current rating of the inductor should be at least equal to the maximum load current plus half the ripple current to prevent core saturation. Thus, a 720mA rated inductor should be sufficient for most applications (600mA + 120mA). A easy and fast approach is to select the inductor current rating fitting to the maximum switch current limit of the converter.

Note: For highest efficiency, a low DC-resistance inductor is recommended.

Accepting larger values of ripple current allows the use of low inductance values, but results in higher output voltage ripple, greater core losses, and lower output current capability.

The total losses of the coil have a strong impact on the efficiency of the dc/dc conversion and consist of both the losses in the dc resistance and the following frequency-dependent components:

- 1. The losses in the core material (magnetic hysteresis loss, especially at high switching frequencies)

- 2. Additional losses in the conductor from the skin effect (current displacement at high frequencies)

- 3. Magnetic field losses of the neighboring windings (proximity effect)

- 4. Radiation losses

Table 5. Recommended Inductors

| Part Number     | L     | DCR                 | <b>Current Rating</b> | Dimensions (L/W/T) | Manufacturer      |

|-----------------|-------|---------------------|-----------------------|--------------------|-------------------|

| LQH32CN2R2M33   | 2.2µH | 97m $\Omega$        | 790mA                 | 3.2x2.5x2.0mm      | Murata            |

| LQH32CN4R7M33   | 4.7µH | 150m $\Omega$       | 650mA                 | 3.2x2.5x2.0mm      | www.murata.com    |

| LPS3008-222MLC  | 2.2µH | 175m $Ω$            | 1100mA                | 3.1x3.1x0.8mm      | Coilcraft         |

| LPS3015-222MLC  | 2.2µH | 110m $\Omega$       | 2000mA                | 3.1x3.1x1.5mm      | www.coilcraft.com |

| MOS6020-222MLC  | 2.2µH | $35 \text{m}\Omega$ | 3260mA                | 6.0x6.8x2.4mm      |                   |

| MOS6020-472MLC  | 4.7µH | 50m $Ω$             | 1820mA                | 6.0x6.8x2.4mm      |                   |

| CDRH3D16NP-2R2N | 2.2µH | $72 m\Omega$        | 1200mA                | 4.0x4.0x1.8mm      | Sumida            |

| CDRH3D16ND-4R7N | 4.7µH | 105m $Ω$            | 900mA                 | 4.0x4.0x1.8mm      | www.sumida.com    |

Figure 26. Efficiency Comparison of Different Inductors, VIN = 2.7V, VOUT = 1.8V and 1.2V

## **Output Capacitor Selection**

The advanced fast-response voltage mode control scheme of the AS1324 allows the use of tiny ceramic capacitors. Because of their lowest output voltage ripple low ESR ceramic capacitors are recommended. X7R or X5R dielectric output capacitor are recommended.

At high load currents, the device operates in PWM mode and the RMS ripple current is calculated as:

$$I_{RMSC_{OUT}} = V_{OUT} \times \frac{1 - \frac{V_{OUT}}{V_{IN}}}{L \times f} \times \frac{1}{2 \times \sqrt{3}}$$

(EQ 4)

While operating in PWM mode the overall output voltage ripple is the sum of the voltage spike caused by the output capacitor ESR plus the voltage ripple caused by charging and discharging the output capacitor:

$$\Delta V_{OUT} = V_{OUT} \times \frac{1 - \frac{V_{OUT}}{V_{IN}}}{L \times f} \times \left(\frac{1}{8 \times C_{OUT} \times f} + ESR\right)$$

(EQ 5)

Higher value, low cost ceramic capacitors are available in very small case sizes, and their high ripple current, high voltage rating, and low ESR make them ideal for switching regulator applications. Because the AS1324 control loop is not dependant on the output capacitor ESR for stable operation, ceramic capacitors can be used to achieve very low output ripple and accommodate small circuit size.

At light loads, the converter operates in powersave mode and the output voltage ripple is in direct relation to the output capacitor and inductor value used. Larger output capacitor and inductor values minimize the voltage ripple in powersave mode and tighten DC output accuracy in powersave mode.

### Input Capacitor Selection

In continuous mode, the source current of the PMOS is a square wave of the duty cycle Vout/Vin. To prevent large voltage transients while minimizing the interference with other circuits caused by high input voltage spikes, a low ESR input capacitor sized for the maximum RMS current must be used. The maximum RMS capacitor current is given as:

$$I_{RMS} = I_{MAX} \times \frac{\sqrt{V_{OUT} \times (V_{IN} - V_{OUT})}}{V_{IN}}$$

(EQ 6)

where the maximum average output current IMAX equals the peak current minus half the peak-to-peak ripple current, IMAX =  $ILIM - \Delta IL/2$

This formula has a maximum at VIN = 2VOUT where IRMS = IOUT/2. This simple worst-case condition is commonly used for design because even significant deviations only provide negligible affects.

The input capacitor can be increased without any limit for better input voltage filtering. Take care when using small ceramic input capacitors. When a small ceramic capacitor is used at the input, and the power is being supplied through long wires, such as from a wall adapter, a load step at the output, or VIN step on the input, can induce ringing at the VIN pin. This ringing can then couple to the output and be mistaken as loop instability, or could even damage the part by exceeding the maximum ratings.

#### **Ceramic Input and Output Capacitors**

When choosing ceramic capacitors for CIN and COUT, the X5R or X7R dielectric formulations are recommended. These dielectrics have the best temperature and voltage characteristics for a given value and size. Y5V and Z5U dielectric capacitors, aside from their wide variation in capacitance over temperature, become resistive at high frequencies and therefore should not be used.

Table 6. Recommended Input and Output Capacitor

| Part Number       | С     | TC Code | Rated Voltage | Dimensions (L/W/T) | Manufacturer                |

|-------------------|-------|---------|---------------|--------------------|-----------------------------|

| JMK212BJ226MG-T   | 22µF  | X5R     | 6.3V          | 0805               | Taiyo Yuden www.t-yuden.com |

| GRM188R60J106ME47 | 10µF  | X5R     | 6.3V          | 0603               | Murata                      |

| GRM21BR71A475KA73 | 4.7µF | X7R     | 10V           | 0805               | www.murata.com              |

Because ceramic capacitors lose a lot of their initial capacitance at their maximum rated voltage, it is recommended that either a higher input capacity or a capacitance with a higher rated voltage is used.

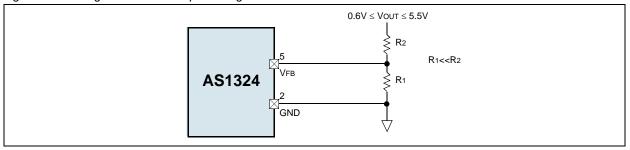

#### **Feedback Resistor Selection**

In the AS1324-AD, the output voltage is set by an external resistor divider connected to VFB (see Figure 27). This circuitry allows for remote voltage sensing and adjustment.

austriamicrosystems

Figure 27. Setting the AS1324 Output Voltage

Resistor values for the circuit shown in Figure 27 can be calculated as:

$$V_{OUT} = 0.6 \times \left[1 + \frac{R_2}{R_1}\right]$$

(EQ 7)

The output voltage can be adjusted by selecting different values for R<sub>1</sub> and R<sub>2</sub>. For R<sub>1</sub> a value between  $10k\Omega$  and  $500k\Omega$  is recommended. A higher resistance of R<sub>1</sub> and R<sub>2</sub> will result in a lower leakage current at the output. It is recommended to keep Vin 500mV higher than VouT.

### **Efficiency**

The efficiency of a switching regulator is equivalent to:

$$Efficiency = (POUT/PIN)100\% (EQ 8)$$

For optimum design, an analysis of the AS1324 is needed to determine efficiency limitations and to determine design changes for improved efficiency. Efficiency can be expressed as:

Efficiency =

$$100\% - (L1 + L2 + L3 + ...)$$

(EQ 9)

#### Where:

L<sub>1</sub>, L<sub>2</sub>, L<sub>3</sub>, etc. are the individual losses as a percentage of input power.

Althought all dissipative elements in the circuit produce losses, those four main sources should be considered for efficiency calculation:

#### **Input Voltage Quiescent Current Losses**

The Vin current is the DC supply current given in the electrical characteristics which excludes MOSFET driver and control currents. Vin current results in a small (<0.1%) loss that increases with Vin, even at no load. The Vin quiescent current loss dominates the efficiency loss at very low load currents.

#### I<sup>2</sup>R Losses

Most of the efficiency loss at medium to high load currents are attributed to I²R loss, and are calculated from the resistances of the internal switches (Rsw) and the external inductor (RL). In continuous mode, the average output current flowing through inductor L is split between the internal switches. Therefore, the series resistance looking into the SW pin is a function of both NMOS & PMOS RDS(ON) as well as the the duty cycle (DC) and can be calculated as follows:

$$Rsw = (RDS(ON)PMOS)(DC) + (RDS(ON)NMOS)(1 - DC)$$

(EQ 10)

The RDS(ON) for both MOSFETs can be obtained from the Electrical Characteristics on page 4. Thus, to obtain I²R losses calculate as follows:

$$I^2R losses = IouT^2(Rsw + RL)$$

(EQ 11)

#### **Switching Losses**

The switching current is the sum of the control currents and the MOSFET driver. The MOSFET driver current results from switching the gate capacitance of the power MOSFETs. If a MOSFET gate is switched from low to high to low again, a packet of charge dQ moves from VIN to ground. The resulting dQ/dt is a current out of VIN that is typically much larger than the DC bias current. In continuous mode:

$$IGC = f(QPMOS + QNMOS)$$

(EQ 12)

Where: QPMOS and QNMOS are the gate charges of the internal MOSFET switches.

The losses of the gate charges are proportional to VIN and thus their effects will be more visible at higher supply voltages.

#### **Other Losses**

Basic losses in the design of a system should also be considered. Internal battery resistances and copper trace can account for additional efficiency degradations in battery operated systems. By making sure that CIN has adequate charge storage and very low ESR at the given switching frequency, the internal battery and fuse resistance losses can be minimized. CIN and COUT ESR dissipative losses and inductor core losses generally account for less than 2% total additional loss.

#### Thermal Shutdown

Due to its high-efficiency design, the AS1324 will not dissipate much heat in most applications. However, in applications where the AS1324 is running at high ambient temperature, uses a low supply voltage, and runs with high duty cycles (such as in dropout) the heat dissipated may exceed the maximum junction temperature of the device.

As soon as the junction temperature reaches approximately 150°C the AS1324 goes in thermal shutdown. In this mode the internal PMOS & NMOS switch are turned off. The device will power up again, as soon as the temperature falls below +145°C again.

### **Checking Transient Response**

The main loop response can be evaluated by examining the load transient response. Switching regulators normally take several cycles to respond to a step in load current. When a load step occurs, VouT immediately shifts by an amount equivalent to:

$$VDROP = \Delta IOUT \times ESR$$

(EQ 13)

#### Where:

ESR is the effective series resistance of Cout.

Alout also begins to charge or discharge Cout, which generates a feedback error signal. The regulator loop then acts to return Vout to its steady-state value. During this recovery time Vout can be monitored for overshoot or ringing that would indicate a stability problem.

## **Design Example**

Figure 28 shows the AS1324 used in a single lithium-ion (3.7V typ) battery-powered mobile phone application. The load current requirement is 600mA (max) but most of the time the device will require only 2mA (standby mode current).

Figure 28. Design Example

For the circuit shown in Figure 28, efficiency at low- and high-load currents is an important consideration when selecting the value for the external inductor, which is calculated as:

$$L = \frac{V_{OUT}}{f\Delta I_L} \times \left(1 - \frac{V_{OUT}}{V_{IN}}\right)$$

(EQ 14)

From (EQ 14), substituting Vout = 2.2V, Vin = 3.7V,  $\Delta I_L$  = 240mA and f = 1.5MHz gives:

$$L = \frac{2.2V}{(1.5 \text{MHz} \times 240 \text{mA})} \times \left(1 - \frac{2.2V}{3.7V}\right) = 2.48 \mu \text{H}$$

(EQ 15)

Therefore, a standard 2.2µH inductor should be used for this design.

For best overall efficiency use an inductor with a rating of 720mA or greater and less than  $0.2\Omega$  series resistance. CIN will require an RMS current rating of at least  $0.3A \cong ILOAD(MAX)/2$ , whereas COUT will require an ESR of less than  $0.25\Omega$ . In most cases, a ceramic capacitor will satisfy this requirement.

For the feedback resistors, select the value for  $R_1 = 375k\Omega$ .  $R_2$  can then be calculated from (EQ 7) to be:

$$R_2 = (Vout/0.6 - 1)375k = 1000k\Omega$$

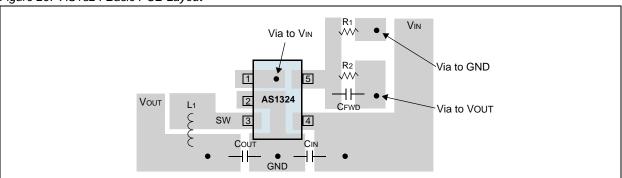

### **Layout Considerations**

The AS1324 requires proper layout and design techniques for optimum performance.

- The power traces (GND, SW, and VIN) should be kept as short, direct, and wide as is practical.

- Pin VFB (AS1324 only) should be connected directly to the feedback resistors (R1 and R2). A potentiometer as replacement for R1 and R2 should be avoided to minimize the output voltage ripple and to maintain the stability of the regulator.

- The resistive divider (R<sub>1</sub>/R<sub>2</sub>) must be connected between the positive plate of Cout and ground.

- The positive plate of CIN should be connected as close to VIN as is practical since CIN provides the AC current to the internal power MOSFETs.

- Switching node SW should be kept far away from the sensitive VFB node.

- The negative plates of CIN and COUT should be kept as close to each other as is practical. A starpoint to Ground is recommended.

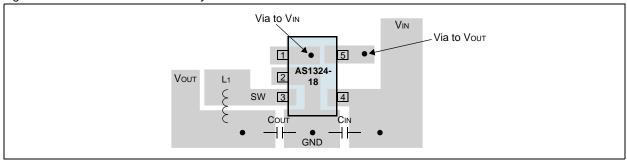

Figure 29. AS1324 Basic PCB Layout

Figure 30. AS1324 Basic Diagram

Figure 31. AS1324-18 Basic PCB Layout

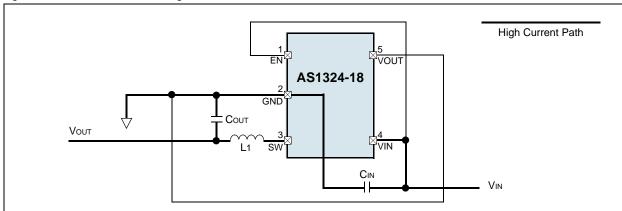

Figure 32. AS1324-18 Basic Diagram

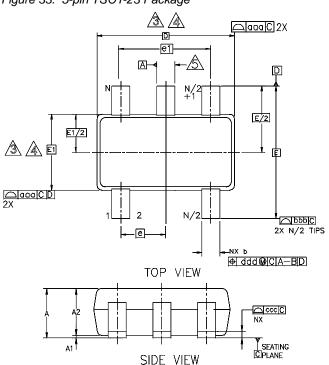

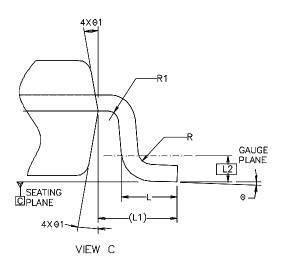

# 10 Package Drawings and Markings

The device is available in an 5-pin TSOT-23 package.

Figure 33. 5-pin TSOT-23 Package

| Symbol | Min  | Тур     | Max  | Notes | Symbol | Min        | Тур       | Max         | Notes |

|--------|------|---------|------|-------|--------|------------|-----------|-------------|-------|

| Α      |      |         | 1.00 |       | L      | 0.30       | 0.40      | 0.50        |       |

| A1     | 0.01 | 0.05    | 0.10 |       | L1     | 0.60REF    |           |             |       |

| A2     | 0.84 | 0.87    | 0.90 |       | L2     |            | 0.25BSC   |             |       |

| b      | 0.30 |         | 0.45 |       | N      |            | 5         |             |       |

| b1     | 0.31 | 0.35    | 0.39 |       | R      | 0.10       |           |             |       |

| С      | 0.12 | 0.15    | 0.20 |       | R1     | 0.10       |           | 0.25        |       |

| c1     | 0.08 | 0.13    | 0.16 |       | θ      | 00         | 40        | 80          |       |

| D      |      | 2.90BSC |      | 3,4   | θ1     | 4º         | 10°       | 12º         |       |

| Е      |      | 2.80BSC |      | 3,4   | •      | Tolerances | of Form a | nd Position | 1     |

| E1     |      | 1.60BSC |      | 3,4   | aaa    |            | 0.15      |             |       |

| е      |      | 0.95BSC |      |       | bbb    |            | 0.25      |             |       |

| e1     |      | 1.90BSC |      |       | ccc    |            | 0.10      |             |       |

|        |      |         |      |       | ddd    |            | 0.20      |             |       |

#### Notes:

- 1. Dimensioning and tolerancing conform to ASME Y14.5M 1994.

- 2. Dimensions are in millimeters.

- 3. Dimension D does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, and gate burrs shall not exceed 0.15mm per end. Dimension E1 does not include interlead flash or protrusion. Interlead flash or protrusion shall not exceed 0.15mm per side. Dimensions D and E1 are determined at datum H.

- 4. The package top can be smaller than the package bottom. Dimensions D and E1 are determined at the outer-most extremes of the plastic body exclusive of mold flash, tie bar burrs, gate burrs, and interlead flash, but include any mistmatches between the top of the package body and the bottom. D and E1 are determined at datum H.

# 11 Ordering Information

The device is available as the following standard versions.

Table 7. Ordering Information

| Model          | Marking | Output     | Description                                  | Delivery Form | Package       |

|----------------|---------|------------|----------------------------------------------|---------------|---------------|

| AS1324-BTTT-AD | ASKR    | adjustable | 1.5MHz, 600mA Synchronous<br>DC/DC Converter | Tape and Reel | 5-pin TSOT-23 |

| AS1324-BTTT-12 | ASKT    | 1.2V       | 1.5MHz, 600mA Synchronous<br>DC/DC Converter | Tape and Reel | 5-pin TSOT-23 |

| AS1324-BTTT-15 | ASKU    | 1.5V       | 1.5MHz, 600mA Synchronous<br>DC/DC Converter | Tape and Reel | 5-pin TSOT-23 |

| AS1324-BTTT-18 | ASKS    | 1.8V       | 1.5MHz, 600mA Synchronous<br>DC/DC Converter | Tape and Reel | 5-pin TSOT-23 |

All devices are RoHS compliant and free of halogene substances.

## Copyrights

Copyright © 1997-2009, austriamicrosystems AG, Schloss Premstaetten, 8141 Unterpremstaetten, Austria-Europe. Trademarks Registered ®. All rights reserved. The material herein may not be reproduced, adapted, merged, translated, stored, or used without the prior written consent of the copyright owner.

All products and companies mentioned are trademarks or registered trademarks of their respective companies.

#### **Disclaimer**

Devices sold by austriamicrosystems AG are covered by the warranty and patent indemnification provisions appearing in its Term of Sale. austriamicrosystems AG makes no warranty, express, statutory, implied, or by description regarding the information set forth herein or regarding the freedom of the described devices from patent infringement. austriamicrosystems AG reserves the right to change specifications and prices at any time and without notice. Therefore, prior to designing this product into a system, it is necessary to check with austriamicrosystems AG for current information. This product is intended for use in normal commercial applications. Applications requiring extended temperature range, unusual environmental requirements, or high reliability applications, such as military, medical life-support or life-sustaining equipment are specifically not recommended without additional processing by austriamicrosystems AG for each application. For shipments of less than 100 parts the manufacturing flow might show deviations from the standard production flow, such as test flow or test location.

The information furnished here by austriamicrosystems AG is believed to be correct and accurate. However, austriamicrosystems AG shall not be liable to recipient or any third party for any damages, including but not limited to personal injury, property damage, loss of profits, loss of use, interruption of business or indirect, special, incidental or consequential damages, of any kind, in connection with or arising out of the furnishing, performance or use of the technical data herein. No obligation or liability to recipient or any third party shall arise or flow out of austriamicrosystems AG rendering of technical or other services.

#### **Contact Information**

#### **Headquarters**

austriamicrosystems AG A-8141 Schloss Premstaetten, Austria

Tel: +43 (0) 3136 500 0 Fax: +43 (0) 3136 525 01

For Sales Offices, Distributors and Representatives, please visit:

http://www.austriamicrosystems.com/contact-us