July 2009

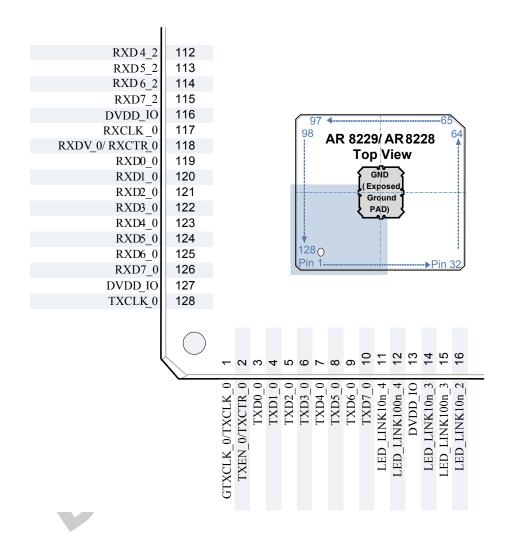

# AR8229/AR8228 Seven-Port Fast Ethernet Switch

# **General Description**

The AR8229/AR8228 is a highly integrated three-Giga MAC plus Five-port Fast Ethernet switch with non-blocking switch fabric, a high-performance lookup unit with 1024 MAC address, 4096 VLAN table, 32 ACL rule table and a four-traffic class Quality of Service (QoS) engine. The AR8229/AR8228 has the flexibility to support various networking applications. The AR8229/AR8228 support many offload function to increase the system performance. The AR8229/AR8228 is designed for cost

sensitive switch applications in wireless AP router, home gateway, and xDSL/PON/cable modem platform. The Fast Ethernet in the AR8229/AR8228 complies fully with IEEE 802.3 standards. The AR8229/AR8228 implements power saving techniques to facilitate low power consumption. The AR8229/AR8228 is designed to work in all environments. True Plug-n-Play is supported with Auto-Crossover, Auto Polarity, and Auto-Negotiation in PHYs.

# AR8229/AR8228 Features

- Single-chip seven-port Fast Ethernet QoS switch

- Single chip 7 port Fast Ethernet QoS switch controller with:

- 5 port 10/100 UTP + 2 port GMII/RGMII MAC

- 4 port 10/100 UTP + 2 port GMII/RGMII MAC + 1 RGMII MAC

- 4 port 10/100 UTP + 2 port GMII/RGMII MAC + 1 port MII PHY

- QoS support with four traffic classes based on arrival port, IEEE802.1p, IPv4 TOS, IPv6 TC and Destination MAC Address

- Supports strict priority, WRR, and mix mode (1 SP + 3 WRR or 2 SP + 2 WRR)

- Full IEEE 802.1Q VLAN ID processing per port and VLAN tagging for 40% VLAN IDs; and port based VLANs supported

- Support VLAN tag insert or remove function on per-port basis

- Support QinQ double tag, and 16 entry of VLAN translation table

- IGMPv1/v2/v3 and MLDv1/v2 Snooping with hardware join and fast leave function

- Support 32 ACL rules and rule based counters

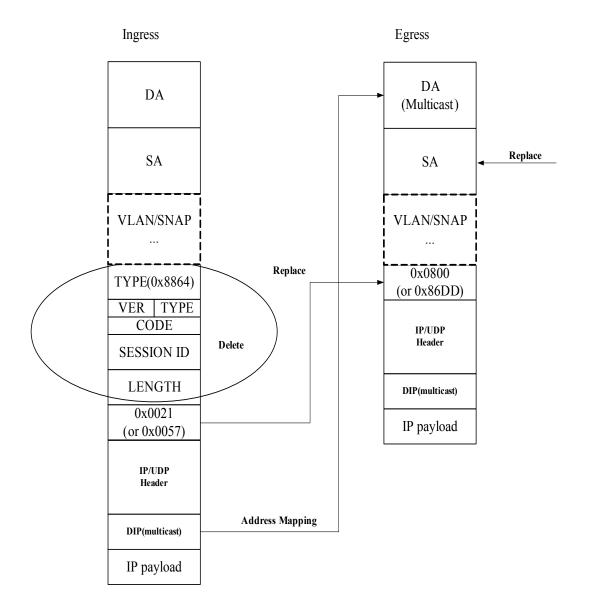

- Support 16 PPPoE sessions header remove

- Port states & BPDU handling support IEEE802.1D Spanning Tree Protocol

- High performance lookup engine with 1024 MAC Address with automatic learning and aging and support for static addresses

- Support 40 MIB counters per port

- Autocast MIB counters to cpu port

- Support ingress & egress rate limit

- Broadcast storm Suppression

- Supports port mirror

- Support MAC and PHY loopback function for diagnosis

- Fully compliant with IEEE 802.3/802.3u auto-negotiation function

- Flow control fully supported IEEE 802.3x flow control for full duplex and back pressure for half duplex

- Supports port lock function

- Supports hardware looping detection

- Power saving on no link and low traffic rate for 10Base-T

© 2009 by Atheros Communications, Inc. All rights reserved. Atheros®, Atheros Driven®, Atheros XR®, Driving the Wireless Future®, ROCm®, Super A/G®, Super G®, Super N®, Total 802.11®, XSPAN®, Wireless Future. Unleashed Now®, and Wake on Wireless® are registered by Atheros Communications, Inc. Atheros SST™, Signal-Sustain Technology™, the Air is Cleaner at 5-GHz™, and 5-UP™ are trademarks of Atheros Communications, Inc. The Atheros logo is a registered trademark of Atheros Communications, Inc. All other trademarks are the property of their respective holders. Subject to change without notice.

COMPANY CONFIDENTIAL • 1

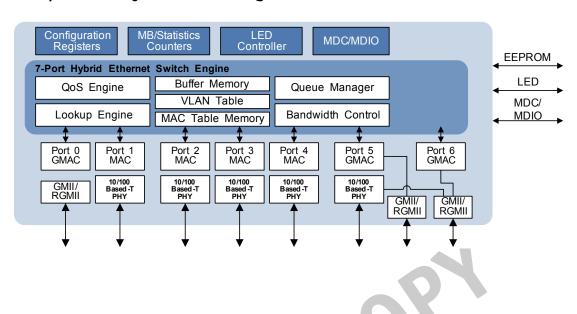

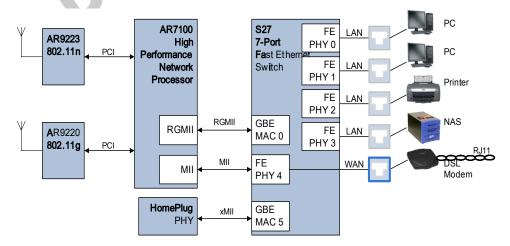

# AR8229/AR8228 System Block Diagram

| General Description1                               | 2.8.10 Egress Mode                                        | 34   |

|----------------------------------------------------|-----------------------------------------------------------|------|

| AR8229/AR8228 Features1                            | 2.8.11 VLAN Table                                         | 34   |

| AR8229/AR8228 System Block Diagram 2               | 2.9 IEEE Port Security                                    | 34   |

|                                                    | 2.9.1 Port Locking                                        | 35   |

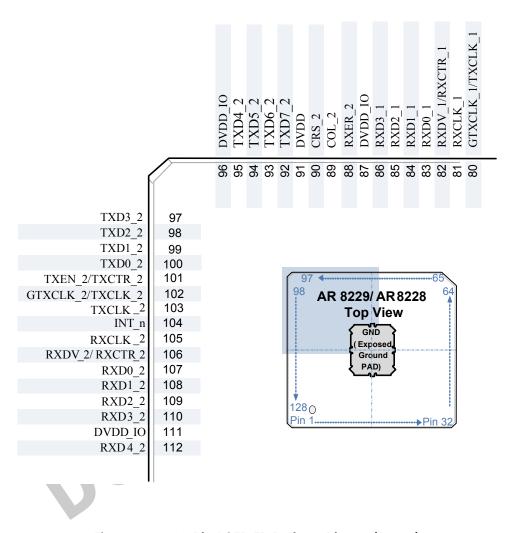

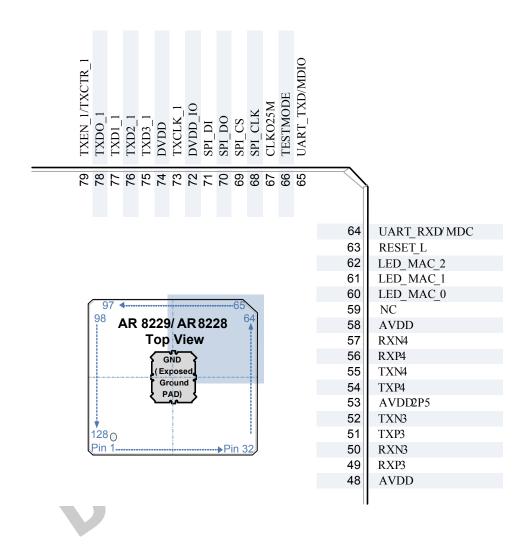

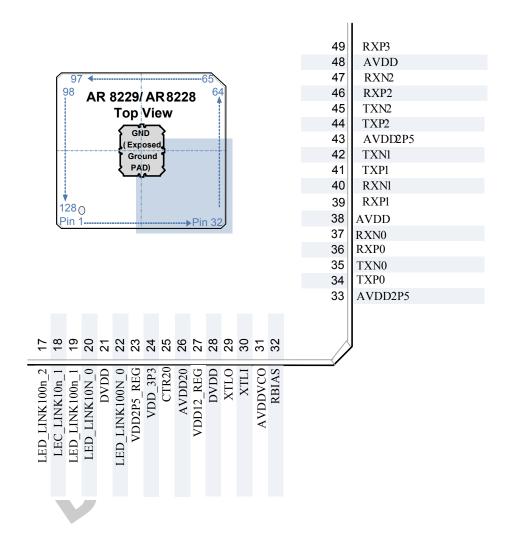

| 1 Pin Descriptions5                                | 2.9.2 802.1X                                              | 35   |

|                                                    | 2.10 Class/Quality of Service                             | 36   |

| 2 Functional Description19                         | 2.10.3 Priority Scheduling                                | 37   |

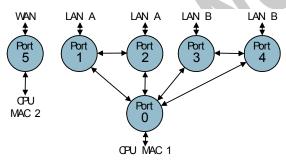

| 2.1 Appl ications                                  | 2.10.4 Rate Limiting                                      | 37   |

| 2.1.1 AP Router Application19                      | 2.11 Mirroring                                            | 37   |

| 2.2 Basic Switch Operation20 2.2.2 Lookup Engine20 | 2.12 Broadcast/Multicast/unknown Unicast St<br>Control 37 | torm |

| 2.2.3 Autom atic Address Learning 20               | 2.13 IGMP/MLD Snooping                                    | 37   |

| 2.2.4 Automatic Address Aging 20                   | 2.14 Spanning Tree                                        |      |

| 2.3 Media Access Controllers (MAC)20               | 2.15 MIB/Statistics Counters                              |      |

| 2.3.5 Port Status Configuration20                  | 2.16 Atheros Header Configuration                         |      |

| 2.3.1 Ful 1-Duplex Flow Control21                  | 2.17 IEEE 802.3 Reserved Group Addresses File             |      |

| 2.3.2 Half-Duplex Flow Control21                   | Control 41                                                | O    |

| 2.3.3 Int er-Packet Gap (IPG)21                    | 2.18 Forwarding Unknown                                   | 41   |

| 2.3.4 Ille gal Frames21                            | 2.19 PPPoE Header Removal                                 | 41   |

| 2.4 AC L22                                         | 2.20 Memory Map                                           | 43   |

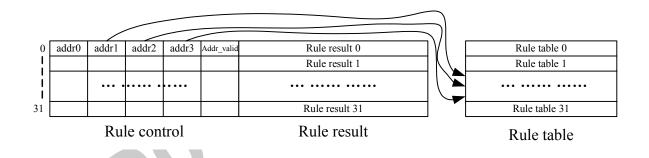

| 2.4.5 Rul e Control22                              |                                                           |      |

| 2.4.6 ACL Rule Match Result23                      | 3 Register Descriptions                                   |      |

| 2.4.7 Rul e Table23                                | 3.1 Global Control Registers 0x0000 —0x00FC               |      |

| 2.4.8 Rul e Select24                               | 3.2 Port Control Registers 0x0100 —0x0124                 |      |

| 2.4.9 MAC Rule24                                   | 3.3 Mask Control Register                                 |      |

| 2.4.10 MAC Mask25                                  | 3.4 Operational Mode Register 0                           |      |

| 2.4.11 IPv425                                      | 3.5 Operational Mode Register 1                           |      |

| 2.4.12 IPv4 Rule25                                 | 3.6 Operational Mode Register 2                           |      |

| 2.4.13 IPv4 Mask25                                 | 3.7 Power-On Strapping Register                           |      |

| 2.4.14 IPv6 Rule26                                 | 3.8 Global Interrupt Register                             |      |

| 2.4.15 IPv6 Mask27                                 | 3.9 Global Interrupt Mask Register                        |      |

| 2.4.16 ACL Access28                                | 3.9.6 Loop Check Result                                   |      |

| 2.5 Regi ster Access28                             | •                                                         |      |

| 2.6 LE D Control                                   | 3.10 Flood Mask Register 3.11 Global Control Register     |      |

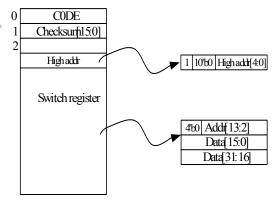

| 2.7 EE PROM Description30                          | 3.12 Flow Control Register 0                              |      |

| 2.8 VL ANs30                                       | 3.13 Flow Control Register 1                              |      |

| 2.8.1 Port-Based VLAN31                            | 3.13.7 QM Control Register                                |      |

| 2.8.2 802. 1Q VLANs31                              | 3.14 VLAN Table Function Register 0                       |      |

| 2.8.3 Leaky VLAN31                                 | 3.15 VLAN Table Function Register 1                       |      |

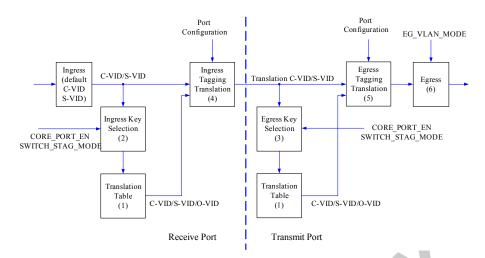

| 2.8.4 VLAN Translation Architecture 31             | 3.16 Address Table Function Register 0                    |      |

| 2.8.5 VLAN Translation Table32                     | 3.17 Address Table Function Register 1                    |      |

| 2.8.6 Ingress Key Selection32                      | 3.18 Address Table Function Register 2                    |      |

| 2.8.7 Egress Key Selection33                       | 3.19 Address Table Control Register                       |      |

| 2.8.8 In gress Tagging Translation 33              | 3.20 IP Priority Mapping Register 2                       |      |

| 2.8.9 Egress Tagging Translation 33                | 3.21 Tag Priority Mapping Register                        |      |

|                                                    | 7 11-00                                                   | -    |

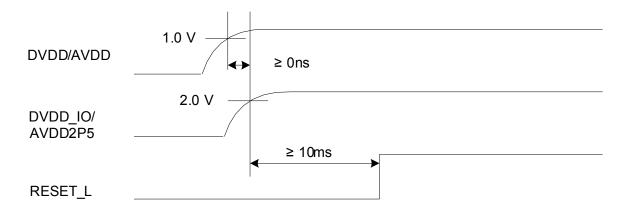

| 3.22 Service Tag Register76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5.4.8 Powe r-on-Reset T                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

| 3.23 CPU Port Register77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5.5 AC Timing                            |

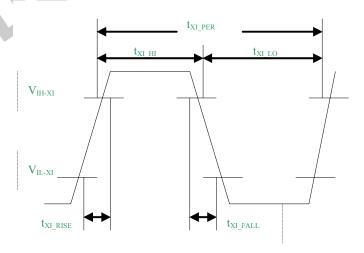

| 3.24 MIB Function Register 077                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5.5.9 XTAL/OSC Timin                     |

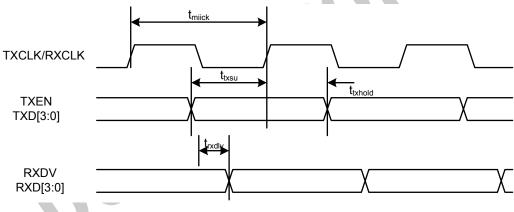

| 3.25 MDIO Control Register78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5.5.10 MII Timing                        |

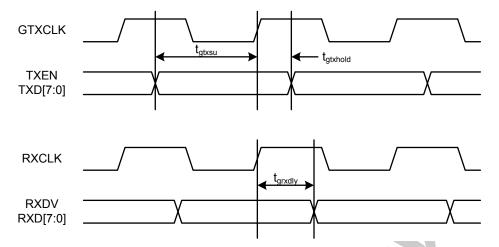

| 3.26 LED Control Register79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5.5.11 GMII Timing                       |

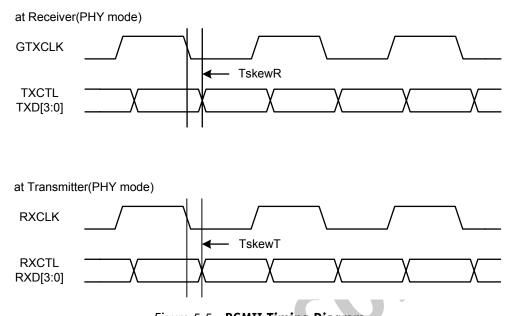

| 3.27 Port Control Registers — Summary for all Ports 80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 5.5.12 RGMII Timing<br>5.5.13 SPI Timing |

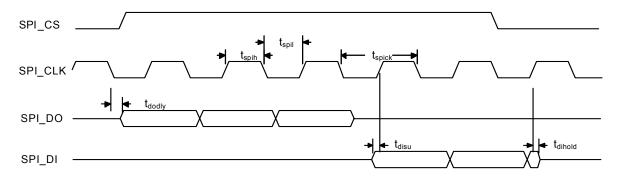

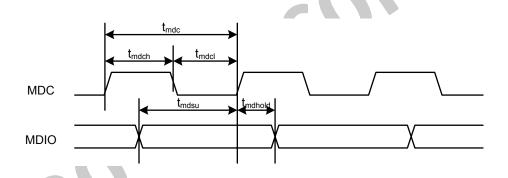

| 3.28 Port Status Register82                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5.5.14 MDIO Timing                       |

| 3.29 Port Control Register83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5.6 Typical Power Consumption            |

| 3.30 Port-based VLAN Register86                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3.0 Typical Fower Consumption            |

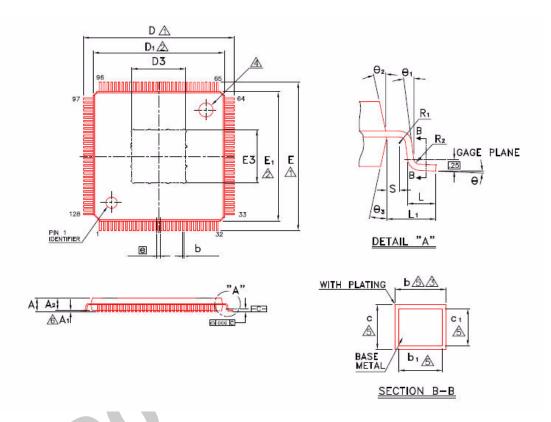

| 3.31 Port-based VLAN Register287                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 6 Package Dimensions                     |

| 3.32 Rate Limit Register89                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | O                                        |

| 3.33 Priority Control Register89                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 7 Ordering Informatio                    |

| 3.34 Storm Control Register90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -                                        |

| 3.35 Queue Control Register91                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                          |

| 3.36 Rate Limit Register 193                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                          |

| 3.37 Rate Limit Register 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                          |

| 3.38 Rate Limit Register 394                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                          |

| 3.39 Robin Register94                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                          |

| -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                          |

| 4 PHY Control Registers96                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                          |

| 4.40 Control Register97                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                          |

| 4.41 Status Register99                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                          |

| 4.42 PHY Identifier101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                          |

| 4.43 PHY Identifier 2102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                          |

| 4.44 Auto-negotiation Advertisement Register .103                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                          |

| 4.45 Link Partner Ability Register107                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                          |

| 4.46 Auto-negotiation Expansion Register 109                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                          |

| 4.47 Function Control Register 110                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                          |

| 4.48 PHY Specific Status Register112                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                          |

| 4.49 Interrupt Enable Register 114                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                          |

| 4.50 Interrupt Status Register 116                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                          |

| 4.51 Receive Error Counter Register118                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                          |