**Data Sheet**

February 2009

### AR6102 ROCm<sup>TM</sup> MAC/BB/Radio for 2.4 GHz Embedded WLAN **Applications**

### **General Description**

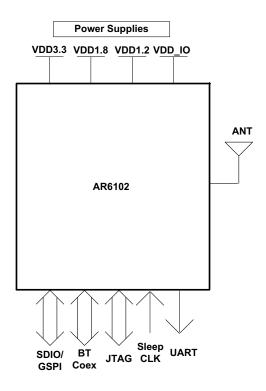

This document describes the AR6102, Rev. 2.1.

The Atheros AR6102 is a member of the WLAN ROCm family of chips. The compact size and low power consumption of this design make it an ideal vehicle for adding WLAN to hand-held and other battery-powered consumer electronic devices. The IEEE 802.11g (2.4 GHz) standard is supported by this chipset.

The AR6102 family includes a highly integrated, RF front-end (Power Amplifier, Low-Noise Amplifier and RF switch) and high-frequency reference clock, enabling low-cost designs with Fidential minimal external components. Advanced architecture and protocol techniques save power during sleep, stand-by and active states.

The AR6102 family supports 2, 3 and 4 wire Bluetooth coexistence protocols with advanced algorithms for predicting channel usage by the co-located Bluetooth transceiver. A 26MHz reference clock output is also available, eliminating the need for a dedicated BT clock.

The AR6102 provides multiple peripheral interfaces including UART.

### AR6102 Features

- IEEE 802.11b/g compliant

- Data rates of 1–54 Mbps for 802.11g

- Advanced power management to minimize standby, sleep and active power

- Security support for WPS, WPA2, WPA, WAPI and protected management frames

- Support for 2.4 GHz operation in all available bands in all regulatory domains

- Full 802.11e QoS support including WMM and U-APSD

- Support for fast Tx and Rx antenna diversity allowing optimal antenna selection on a perpacket basis

- Supports both SDIO 1.1 and GSPI host interfaces.

- Standard 2, 3 and 4 wire Bluetooth coexistence handshake support

- 16550-compliant UART

- Wake-on-Wireless (WoW) maximizes host sleep duration

- 7.4 x 8 mm LGA package

- Pre-certified to meet FCC, ETSI, and TELEC standards

- Integrated PA, LNA, RF switch and High Freq Reference Clock, minimizing external component count

- Integrated RF shielding

- Suports cellular co-existence with an external band-pass filter

ATHEROS CONFIDENTIAL 1

Atheros AR6102 Block Diagram

### **Table of Contents**

| 1   | Dimensions and Footprint 5                                   |

|-----|--------------------------------------------------------------|

|     | Pin Assignment and Description 9 Pin Description11           |

|     | Electrical Characteristics 15                                |

| 3.1 | Absolute Maximum Ratings15                                   |

| 3.2 | Recommended Operating Conditions15                           |

| 3.3 | DC Electrical Characteristics16                              |

| 3.4 | Radio Receiver Characteristics 17                            |

| 3.5 | Radio Transmitter Characteristics 18                         |

| 3.6 | Synthesizer Composite Characteristics for 2.4GHz Operation18 |

| 3.7 | Typical Power Consumption19                                  |

|     | 3.7.1 Measurement Conditions for Low Power State             |

|     | 3.7.2 Measurement Conditions for Continuous Receive20        |

|     | 3.7.3 Measurement Conditions for Continuous Transmit21       |

| 3.8 | Power Sequence Operation22                                   |

| 4   | AC Specifications25                                          |

|     | External 32KHz Input Clock Timing 25                         |

| 4.2 |                                                              |

|     | Application Guidelines27                                     |

| 5.1 | Typical 11b/g Application27                                  |

| 5.2 | Application Schematic27                                      |

| 5.3 | 11b/g Application with Cellular<br>Coexistence Filter28      |

| 5.4 | 11b/g Application with Bluetooth-Coexistence29               |

| 5.5 | 11b/g Application with Antenna<br>Diversity32                |

| 5.6 | Power Supply Management32                                    |

| 5.7 | Grounding35                                                  |

| 5.8 | Host Interfaces and GPIOs35                                  |

|     | 5.8.1 Secure Digital Input/Output (SDIO)35                   |

|     | 5.8.2 Dedicated Function Pins 35                             |

| 59  | RF Port Matching 36                                          |

| . 30 |

|------|

| . 30 |

| . 30 |

| . 37 |

| . 37 |

| . 37 |

| ace  |

| . 37 |

| . 38 |

| . 38 |

| . 39 |

| .41  |

| . 4  |

| . 4  |

| .43  |

| .45  |

|      |

Atheros Confidential

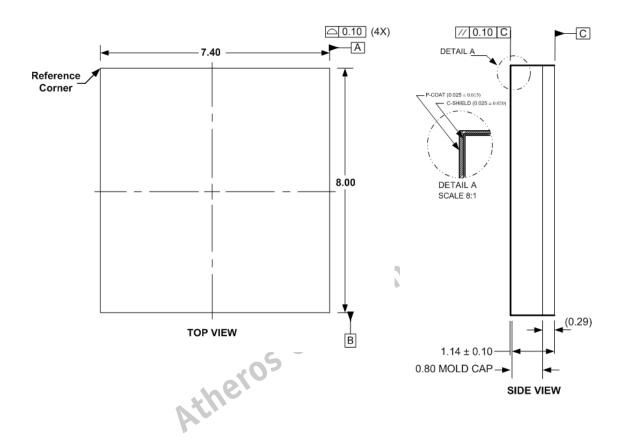

### 1. Dimensions and Footprint

This section provides the dimensions and footprint of the AR6102. Figure 1-1 shows the top and side view of the AR6102.

Figure 1-1. Dimensions and Footprint - Top and Side View

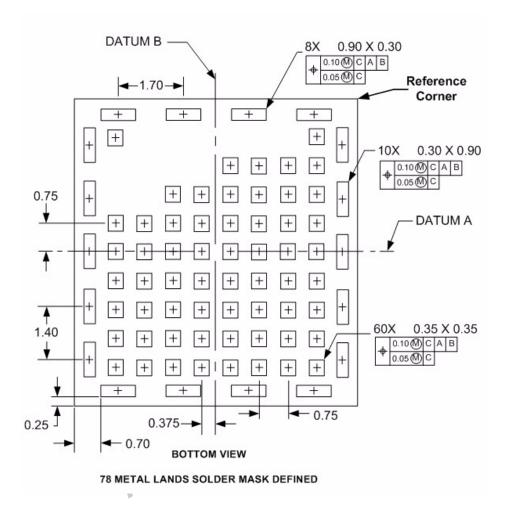

Figure 1-2 shows the bottom view of the AR6102.

Figure 1-2. Dimensions and Footprint - Bottom View

Figure 1-3. Dimensions and Footprint - Bottom View Details

Atheros Confidential

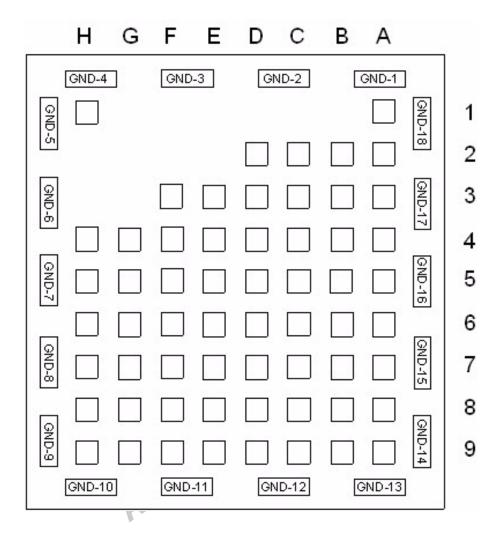

### 2. Pin Assignment and Description

This section provides pin assignments descriptions.

The following nomenclature is used for signal types described in this chapter.

The following nomenclature is used for signal names:

| NIC | N.T.          | 1 11     | 1 1 .      |

|-----|---------------|----------|------------|

| NC  | No connection | ı snoula | be made to |

this pin

\_L At the end of the signal name,

indicates active low signals

$A_I/O$ Analog input signal

Ι Digital input signal

PU Weak internal pull-up, to prevent Confidential

signals from floating when left

open

PD Weak internal pull-down, to

prevent signals from floating

when left open

I/O A digital bidirectional signal

O A digital output signal

P A power or ground signal

See Table 2-1 for the AR6102 package pin assignments.

Table 2-1. Pin Assignment

| Pin No.    | Name         | Pin No.          | Name        |

|------------|--------------|------------------|-------------|

| A1         | GND          | F7               | VDD_BT      |

| A2         | VCC_FEM      | F8               | WLAN_ACTIVE |

| A3         | BT_CLK_OUT   | F9               | VDD18       |

| A4         | VDD_12       | G4               | VDD_GPIO    |

| A5         | JTAG_SEL     | G5               | XTALO       |

| A6         | CLK_REQ      | G6               | ANTD        |

| A7         | SYS_RST_L    | G7               | ANTE        |

| A8         | SD_D0        | G8               | GND         |

| A9         | SD_CLK       | G9               | VDD18       |

| B2         | VCC_FEM      | H1               | RF_OUT      |

| В3         | BT_CLK_EN    | H4               | GND         |

| B4         | RSVD_BBPI    | H5               | ANTA        |

| B5         | TXD0         | H6               | BT_FREQ     |

| B6         | CHIP_PWD_L   | H7               | BT_ACTIVE   |

| B7         | SD_D1        | H8               | GND         |

| B8         | SD_D2        | H9               | GND         |

| B9         | TDI          | GND-1            | GND         |

| C2         | GND          | GND-2            | GND         |

| C3         | VDD_1.2VA    | GND-3            | GND         |

| <u>C4</u>  | GND          | GND-4            | GND         |

| C5         | GND          | GND-5            | GND         |

| C6         | WAKE_ON_WLAN | GND-6            | GND         |

| C7         | SD_D3        | GND-7            | GND         |

| C8         | TDO          | GND-8            | GND         |

| <u> </u>   | TMS          | GND-9            | GND         |

| D2         | GND          | GND-10           | GND         |

| D3         | GND          | GND-11           | GND         |

| D4         | GND          | GND-12           | GND         |

| D5         | GND          | GND-13           | GND         |

| D6         | GND          | GND-13<br>GND-14 | GND         |

| D7         | SD_CMD       | GND-14<br>GND-15 | GND         |

| D8         | TCK          | GND-15<br>GND-16 | GND         |

| D9         | CLK32K       | GND-10<br>GND-17 | GND         |

| E3         | GND          | GND-17           | GND         |

| E4         | GND          | G11D 10          | GIAD        |

| E5         | GND          |                  |             |

| E6         | GND          |                  |             |

| E <b>7</b> | DVDD_SDIO    |                  |             |

| E8         | HMODE_1      |                  |             |

| E9         | BT_PRIORITY  |                  |             |

| F3         | GND          |                  |             |

| F4         | GND          |                  |             |

| F5         | GND          |                  |             |

| F6         | VCC_FEM      |                  |             |

| ΓU         | VCC_FEIVI    |                  |             |

### 2.1 Pin Description

Table 2-2 describes the pins.

Table 2-2. Pin Description

| Pin No.        | Name      | Туре | Description                                               | Reset State | Pad Power<br>Supply Domain |

|----------------|-----------|------|-----------------------------------------------------------|-------------|----------------------------|

|                | 1101110   | -31  | Power Supply                                              |             |                            |

| B2<br>A2<br>F6 | VCC_FEM   | P    | Supply for front-end components and switch control lines. | N/A         | N/A                        |

| C3             | VDD_1.2VA | P    | Analog 1.2V supply                                        | N/A         | N/A                        |

| A4             | VDD_12    | P    | Digital 1.2V supply                                       | N/A         | N/A                        |

| F7             | VDD_BT    | P    | BT-coexistence I/O Supply                                 | N/A         | N/A                        |

| G4             | VDD_GPIO  | P    | GPIO supply voltage                                       | N/A         | N/A                        |

| E7             | DVDD_SDIO | Р    | Host interface supply voltage                             | N/A         | N/A                        |

| F9             | VDD18     | P    | Analog 1.8V supply                                        | N/A         | N/A                        |

| G9             | VDD18     | P    | Analog 1.8V supply                                        | N/A         | N/A                        |

| A1             | GND       | P    | Ground connections                                        | N/A         | N/A                        |

| C2             | GND       | P    | Ground connections                                        | N/A         | N/A                        |

| C4             | GND       | P    | Ground connections                                        | N/A         | N/A                        |

| C5             | GND       | P    | Ground connections                                        | N/A         | N/A                        |

| D2             | GND       | P    | Ground connections                                        | N/A         | N/A                        |

| D3             | GND       | P    | Ground connections                                        | N/A         | N/A                        |

| D4             | GND       | P    | Ground connections                                        | N/A         | N/A                        |

| D5             | GND       | P    | Ground connections                                        | N/A         | N/A                        |

| D6             | GND       | P    | Ground connections                                        | N/A         | N/A                        |

| E3             | GND       | P    | Ground connections                                        | N/A         | N/A                        |

| E4             | GND       | P    | Ground connections                                        | N/A         | N/A                        |

| E5             | GND       | P    | Ground connections                                        | N/A         | N/A                        |

| E6             | GND       | P    | Ground connections                                        | N/A         | N/A                        |

| F3             | GND       | P    | Ground connections                                        | N/A         | N/A                        |

| F4             | GND       | P    | Ground connections                                        | N/A         | N/A                        |

| F5             | GND       | P    | Ground connections                                        | N/A         | N/A                        |

| G8             | GND       | P    | Ground connections                                        | N/A         | N/A                        |

| H4             | GND       | P    | Ground connections                                        | N/A         | N/A                        |

| H8             | GND       | P    | Ground connections                                        | N/A         | N/A                        |

| H9             | GND       | P    | Ground connections                                        | N/A         | N/A                        |

| GND-1          | GND       | P    | Ground connections                                        | N/A         | N/A                        |

| GND-2          | GND       | P    | Ground connections                                        | N/A         | N/A                        |

Table 2-2. Pin Description (continued)

| Pin No. | Name        | Туре   | Description                                                   | Reset State | Pad Power<br>Supply Domain |

|---------|-------------|--------|---------------------------------------------------------------|-------------|----------------------------|

| GND-2   | GND         | P      | Ground connections                                            | N/A         | N/A                        |

| GND-3   | GND         | P      | Ground connections                                            | N/A         | N/A                        |

| GND-4   | GND         | P      | Ground connections                                            | N/A         | N/A                        |

| GND-5   | GND         | P      | Ground connections                                            | N/A         | N/A                        |

| GND-6   | GND         | P      | Ground connections                                            | N/A         | N/A                        |

| GND-7   | GND         | P      | Ground connections                                            | N/A         | N/A                        |

| GND-8   | GND         | P      | Ground connections                                            | N/A         | N/A                        |

| GND-9   | GND         | P      | Ground connections                                            | N/A         | N/A                        |

| GND-10  | GND         | P      | Ground connections                                            | N/A         | N/A                        |

| GND-11  | GND         | P      | Ground connections                                            | N/A         | N/A                        |

| GND-12  | GND         | P      | Ground connections                                            | N/A         | N/A                        |

| GND-13  | GND         | P      | Ground connections                                            | N/A         | N/A                        |

| GND-14  | GND         | P      | Ground connections                                            | N/A         | N/A                        |

| GND-15  | GND         | P      | Ground connections                                            | N/A         | N/A                        |

| GND-16  | GND         | P      | Ground connections                                            | N/A         | N/A                        |

| GND-17  | GND         | P      | Ground connections                                            | N/A         | N/A                        |

| GND-18  | GND         | P      | Ground connections                                            | N/A         | N/A                        |

|         |             | ے      | Host Interface                                                |             |                            |

| A8      | SD_D0       | I/O    | SDIO data signal                                              | PU          | DVDD_SDIO                  |

| B7      | SD_D1       | I/O    | SDIO data signal                                              | PU          | DVDD_SDIO                  |

| B8      | SD_D2       | I/O    | SDIO data signal                                              | PU          | DVDD_SDIO                  |

| C7      | SD_D3       | I/O    | SDIO data signal                                              | PU          | DVDD_SDIO                  |

| D7      | DS_CMD      | I      | SDIO command signal                                           | PU          | DVDD_SDIO                  |

| A9      | SD_CLK      | I      | SDIO clock signal                                             | -           | DVDD_SDIO                  |

|         |             |        | RF Port                                                       |             |                            |

| H1      | RF_OUT      | A_I/O  | RF I/O port                                                   | -           | -                          |

|         |             | Blueto | oth Coexistence Interface                                     |             |                            |

| E9      | BT_PRIORITY | I/0    | Input to WLAN indicating BT Status. Leave as NC when unused.  | -           | VDD_BT                     |

| F8      | WLAN_ACTIVE | I/0    | Output to BT indicating WLAN Status. Leave as NC when unused. | PD          | VDD_BT                     |

| Н6      | BT_FREQ     | I/0    | Input to WLAN indicating BT Status. Leave as NC when unused.  | -           | VDD_BT                     |

Table 2-2. Pin Description (continued)

| Pin No. | Name             | Туре | Description                                                           | Reset State | Pad Power<br>Supply Domain |

|---------|------------------|------|-----------------------------------------------------------------------|-------------|----------------------------|

| H7      | BT_ACTIVE        | I/0  | Input to WLAN indicating<br>BT Status                                 | -           | VDD_BT                     |

|         |                  | R    | adio Control Signals                                                  |             |                            |

| H5      | ANTA             | О    | Control signal for external                                           | PD          | VCC_FEM                    |

| G6      | ANTD             | О    | RF front-end components.<br>Leave as NC when unused.                  | PU          |                            |

| G7      | ANTE             | О    | Leave as ive when unused.                                             | PD          |                            |

|         | <u> </u>         |      | Clocking Interface                                                    |             |                            |

| D9      | CLK32K           | I    | Input for external 32KHz sleep clock.                                 | -           | VDD_GPIO                   |

| G5      | XTALO            | I    | Input for external reference clock oscillator. Leave as NC.           | -           | -                          |

| A3      | BT_CLK_OUT       | О    | Buffered reference clock output. Leave as NC when unused.             | -           | -                          |

|         |                  |      | Digital Control                                                       | I           | 1                          |

| В6      | CHIP_PWD_L       | I    | Chip power down input                                                 | PD          | DVDD_SDIO                  |

| A7      | SYS_RST_L        | I    | Chip reset input                                                      | PU          | DVDD_SDIO                  |

| E8      | HMODE_1          | I    | Host interface selection input                                        | -           | VDD_GPIO                   |

| A6      | CLK_REQ          | 00   | External oscillator enable signal. Leave as NC.                       | PD          | DVDD_SDIO                  |

| В3      | BT_CLK_EN        | I    | Input signal to enable buffered clock output. Tie to GND when unused. | -           | VDD18                      |

| C6      | WAKE_ON_WL<br>AN | О    | Output signal to interrupt host                                       | PD          | VDD_GPIO                   |

|         |                  |      | System Test                                                           |             |                            |

| B4      | RSVD_BBPI        | NC   | Reserved for internal use.                                            | -           | -                          |

| B5      | TXD0             | NC   | Leave as NC.                                                          | -           | -                          |

| A5      | JTAG_SEL         | NC   |                                                                       | -           | VDD_GPIO                   |

| B9      | TDI              | NC   |                                                                       |             | DVDD_SDIO                  |

| C8      | TDO              | NC   |                                                                       |             |                            |

| D8      | TCK              | NC   |                                                                       |             |                            |

| C9      | TMS              | NC   |                                                                       |             |                            |

Atheros Confidential

### 3. Electrical Characteristics

This section describes electrical characteristics of the AR6102.

### 3.1 Absolute Maximum Ratings

See Table 3-1

Table 3-1. Absolute Maximum Ratings

| Parameter        | Min.      | Max.    | Unit |

|------------------|-----------|---------|------|

| VDD_1.2VA        | -0.3      | 1.35    | V    |

| VDD_12           | -0.3      | 1.35    | V    |

| VDD_BT           | -0.3      | 4.0     | V    |

| VDD_GPIO         | -0.3      | 4.0     | V    |

| DVDD_SDIO        | -0.3      | 4.0     | V    |

| VDD18            | -0.3      | 2.5     | V    |

| led Operating Co | onditions | nfident |      |

### 3.2 Recommended Operating Conditions

See Table 3-2.

Table 3-2. Recommneded Operating Conditions

| Parameter         | Min. | Тур. | Max. | Unit |

|-------------------|------|------|------|------|

| VCC_FEM           | 3.0  | 3.3  | 3.6  | V    |

| VDD_1.2VA         | 1.14 | 1.2  | 1.26 | V    |

| VDD_12            | 1.14 | 1.2  | 1.26 | V    |

| VDD_BT            | 1.71 | 1.8  | 3.46 | V    |

| VDD_GPIO          | 1.71 | 1.8  | 3.46 | V    |

| DVDD_SDIO         | 1.71 | 1.8  | 3.46 | V    |

| VDD18             | 1.71 | 1.8  | 1.89 | V    |

| T <sub>case</sub> | -20  | 25   | 85   | °C   |

### 3.3 DC Electrical Characteristics

General DC Electrical Characteristics (For 3.3V I/O Operation)

Table 3-3. General DC Electrical Characteristics (For 3.3 V I/O Operation)

| Symbol            | Parameter                |                                 | Conditions                                                          | Min                   | Тур | Max                   | Unit |

|-------------------|--------------------------|---------------------------------|---------------------------------------------------------------------|-----------------------|-----|-----------------------|------|

| $V_{\mathrm{IH}}$ | High Level Input         | t Voltage                       |                                                                     | 0.8 x V <sub>dd</sub> | -   | $V_{dd} + 0.3$        | V    |

| $V_{IL}$          | Low Level Input          | Voltage                         |                                                                     | -0.3                  | -   | 0.2 x V <sub>dd</sub> | V    |

| $I_{IL}$          | Input Leakage<br>Current | Without Pull-up<br>or Pull-down | $0 \text{ V} < V_{in} < V_{dd}$<br>$0 \text{ V} < V_{out} < V_{dd}$ | -10                   |     | 10                    | μΑ   |

|                   |                          | With Pull-up or<br>Pull-down    | $0 \text{ V} < V_{in} < V_{dd}$<br>$0 \text{ V} < V_{out} < V_{dd}$ | -65                   |     | 65                    | μΑ   |

| V <sub>OH</sub>   | High Level Outp          | ut Voltage                      | $I_{OH} = -4 \text{ mA}$                                            | $V_{dd} - 0.35$       | -   | -                     | V    |

|                   |                          |                                 | $I_{OH} = -12 \text{ mA}^{[1]}$                                     | $V_{dd} - 0.35$       | -   | -                     | V    |

| V <sub>OL</sub>   | Low Level Outpu          | ıt Voltage                      | $I_{OL} = 4 \text{ mA}$                                             | -                     | -   | 0.40                  | V    |

|                   |                          |                                 | $I_{OL} = 12 \text{ mA}[1]$                                         | -                     | -   | 0.40                  | V    |

| C <sub>IN</sub>   | Input Capacitano         | ce <sup>[2]</sup>               | -                                                                   | -                     | 6   | -                     | pF   |

<sup>[1]</sup> For these pins only: SDIO\_DATA\_0, SDIO\_DATA\_1, SDIO\_DATA\_2, SDIO\_DATA\_3

Table 3-4. General DC Electrical Characteristics (For 1.8 V I/O Operation)

| Symbol            | Parameter                                  | Conditions                                                          | Min                   | Тур | Max                   | Unit |

|-------------------|--------------------------------------------|---------------------------------------------------------------------|-----------------------|-----|-----------------------|------|

| $V_{\mathrm{IH}}$ | High Level Input Voltage                   |                                                                     | 0.8 x V <sub>dd</sub> | -   | $V_{dd} + 0.2$        | V    |

| $V_{\rm IL}$      | Low Level Input Voltage                    |                                                                     | -0.3                  | -   | 0.2 x V <sub>dd</sub> | V    |

| $I_{IL}$          | Input Leakage Without Pull-up or Pull-down | $0 \text{ V} < V_{in} < V_{dd}$<br>$0 \text{ V} < V_{out} < V_{dd}$ | -10                   | -   | 10                    | μА   |

|                   | With Pull-up or<br>Pull-down               | $0 \text{ V} < V_{in} < V_{dd}$<br>$0 \text{ V} < V_{out} < V_{dd}$ | -35                   | -   | 35                    | μА   |

| V <sub>OH</sub>   | High Level Output Voltage                  | $I_{OH} = -2 \text{ mA}$                                            | $V_{dd} - 0.35$       | -   | -                     | V    |

|                   |                                            | $I_{OH} = -6 \text{ mA}^{[1]}$                                      | $V_{dd} - 0.35$       | -   | -                     | V    |

| V <sub>OL</sub>   | Low Level Output Voltage                   | $I_{OL} = 2 \text{ mA}$                                             | -                     | -   | 0.3                   | V    |

|                   | '                                          | $I_{OL} = 6 \text{ mA}[1]$                                          | -                     | -   | 0.3                   | V    |

| $C_{IN}$          | Input Capacitance <sup>[2]</sup>           | -                                                                   | -                     | 6   | -                     | pF   |

<sup>[1]</sup>For these pins only: SDIO\_DATA\_0, SDIO\_DATA\_1, SDIO\_DATA\_2, SDIO\_DATA\_3

<sup>[2]</sup> Parameter not tested; value determined by design simulation

<sup>[2]</sup>Parameter not tested; value determined by design simulation

### 3.4 Radio Receiver Characteristics

Table 3-5 summarize the AR6102 receiver characteristics.

Table 3-5. Receiver Characteristics for 2.4 GHz Operation

| Symbol              | Parameter                               | Conditions               | Min   | Тур | Max   | Unit   |

|---------------------|-----------------------------------------|--------------------------|-------|-----|-------|--------|

| F <sub>rx</sub>     | Receive input frequency range           | 5 MHz<br>channel spacing | 2.412 | -   | 2.484 | GHz    |

| S <sub>rf</sub>     | Sensitivity                             | -                        |       |     |       | dBm    |

|                     | 1 Mbps                                  |                          | -96   | -98 | -100  |        |

|                     | 2 Mbps                                  |                          | -92   | -93 | -96   |        |

|                     | 5.5 Mbps                                |                          | -89   | -92 | -94   |        |

|                     | 11 Mbps                                 |                          | -85   | -88 | -91   |        |

|                     | 6 Mbps                                  |                          | -91   | -93 | -96   |        |

|                     | 9 Mbps                                  |                          | -89   | -92 | -95   |        |

|                     | 12 Mbps                                 |                          | -89   | -91 | -93   |        |

|                     | 18 Mbps                                 |                          | -87   | -88 | -92   |        |

|                     | 24 Mbps                                 |                          | -83   | -85 | -88   |        |

|                     | 36 Mbps                                 |                          | -80   | -82 | -85   |        |

|                     | 48 Mbps                                 | 10,1                     | -75   | -77 | -81   |        |

|                     | 54 Mbps                                 | -nfideni                 | -73   | -75 | -77   |        |

| IP1dB               | Input 1 dB compression (min. gain)      | - 1011                   | -8    | -2  | -     | dBm    |

| IIP3                | Input third intercept point (min. gain) | O.                       | -2    | +3  | -     | dBm    |

| ER <sub>phase</sub> | I,Q phase error                         |                          | -4    | 0.5 | 4     | degree |

| ERamp               | I,Q amplitude error                     |                          | -1    | 0   | 1     | dB     |

| R <sub>adj</sub>    | Adjacent channel rejection              | 10 to 20 MHz             |       |     |       | dB     |

| •                   | 1 Mbps                                  |                          | 34    | 36  | _     |        |

|                     | 11 Mbps                                 |                          | 31    | 34  | _     |        |

|                     | 6 Mbps                                  |                          | 35    | 37  | _     |        |

|                     | 54 Mbps                                 |                          | 22    | 24  | -     |        |

| TRpowup             | Time for power up (from RxOn)           | -                        | -     | 1.5 | -     | μs     |

#### 3.5 Radio Transmitter Characteristics

Table 3-6 a summarize the transmitter characteristics for AR6102.

Table 3-6. Transmitter Characteristics for 2.4 GHz operation

| Symbol           | Parameter                                  | Conditions             | Min                | Тур | Max   | Unit |

|------------------|--------------------------------------------|------------------------|--------------------|-----|-------|------|

| F <sub>tx</sub>  | Transmit output frequency range            | 5 MHz center frequency | 2.412              | -   | 2.484 | GHz  |

| P <sub>out</sub> | Mask Compliant CCK output power            |                        | +15 <sup>[1]</sup> | -   | 17.5  | dBm  |

|                  | EVM Compliant OFDM output power for 64 QAM |                        | +15 <sup>[1]</sup> | -   | 17    | dBm  |

| $SP_{gain}$      | PA gain step                               | See Note [2]           | -1.5               | 0.5 | 1.5dB | dB   |

| A <sub>pl</sub>  | Accuracy of power leveling loop            | -                      | -1.5               | -   | 1.5   | dB   |

| TTpowup          | Time for power up (from TxOn)              | -                      | -                  | 1.5 | 2     | μs   |

<sup>[1]</sup>Over all temperature -20 to 85 °C

### 3.6 Synthesizer Composite Characteristics for 2.4GHz Operation

fidential Table 3-7. Synthesizer Composite Characteristics for 2.4 GHz Operation

| Symbol              | Parameter                                                                          | Conditions                            | Min         | Тур                        | Max                        | Unit    |

|---------------------|------------------------------------------------------------------------------------|---------------------------------------|-------------|----------------------------|----------------------------|---------|

| Pn                  | Phase noise (at Tx_Out)                                                            |                                       |             |                            |                            | dBc/Hz  |

|                     | At 30 KHz offset<br>At 100 KHz offset<br>At 500 KHz offset<br>At 1 MHz offset      |                                       | -<br>-<br>- | -99<br>-99<br>-108<br>-115 | -95<br>-95<br>-100<br>-105 |         |

| F <sub>c</sub>      | Center channel frequency                                                           | Center frequency at 5 MHz spacing [1] | 2.312       | -                          | 2.484                      | GHz     |

| BT_CLK_OUT          | Reference oscillator frequency                                                     | ± 20 ppm                              | -           | 26                         | -                          | MHz     |

| BT_CLK_OUT_Pn       | Phase noise at BT_CLK_OUT<br>At 10KHz offset<br>At 100KHz offset<br>At 1MHz offset |                                       |             |                            | -149.3<br>-160.1<br>-164.1 | dBc/Hz  |

| BT_CLK_OUT_A<br>MP  | BT_CLK_OUT amplitude                                                               |                                       |             | 1.2                        |                            | V pk-pk |

| TS <sub>powup</sub> | Time for power up (from sleep)                                                     | -                                     | -           | 0.2                        | -                          | ms      |

<sup>[1]</sup>Frequency is measured at the Tx output.

<sup>[2]</sup> Guaranteed by design.

### 3.7 Typical Power Consumption

Table 3-8 illustrate TYPICAL, room temperature power consumption data.

Table 3-8. AR6102 Typical Power Consumption - Low Power States

|         |          | Current Consumption [mA] |        |        | Power               |

|---------|----------|--------------------------|--------|--------|---------------------|

| Mode    |          | @1.2 V                   | @1.8 V | @3.3 V | Consumption<br>[mW] |

| Standby | CHIP_PWD | 0.008                    | 0.000  | 0.000  | 0.010               |

|         | HOST_OFF | 0.050                    | 0.007  | 0.001  | 0.076               |

|         | SLEEP    | 0.500                    | 0.007  | 0.002  | 0.619               |

| IEEE PS | DTIM=1   | 1.750                    | 0.707  | 0.042  | 3.51                |

|         | DTIM=3   | 0.917                    | 0.240  | 0.015  | 1.58                |

|         | DTIM=10  | 0.625                    | 0.077  | 0.006  | 0.91                |

# eros confidential 3.7.1 Measurement Conditions for Low Power State

$T_amb = 25$  °C

All I/O pins except CHIP\_PWD\_L are maintained at their default polarities.

$VDD_{1.2V} = VDD_{12} = 1.2 V$

$VDD_BT = VDD_GPIO =$  $VDD18_DVDD_SDIO = 1.8 V$

$VCC_FEM = 3.3 V$

CHIP\_PWD - all blocks power gated except for "Power, Clock Management"

HOST\_OFF - all blocks power gated except for "Power, Clock Management", "SDIO", and "GSPI."

SLEEP - "LF CLK" running; all blocks voltage scaled or power gated except for "Power, Clock Management", "SDIO", "GSPI", and "GPIO"; internal state is maintained.

Table 3-9. AR6102 Typical Power Consumption - Rx

|        | Rx     |               |        |                        |  |

|--------|--------|---------------|--------|------------------------|--|

| Rate   | Curre  | nt Consumptio | n [mA] | Power Consumption      |  |

| [Mbps] | @1.2 V | @1.8 V        | @3.3 V | Power Consumption [mW] |  |

| 1      | 64     | 28            | 2      | 134                    |  |

| 2      | 64     | 28            | 2      | 134                    |  |

| 5.5    | 69     | 28            | 2      | 140                    |  |

| 11     | 69     | 28            | 2      | 140                    |  |

| 6      | 67     | 28            | 2      | 138                    |  |

| 9      | 68     | 28            | 2      | 139                    |  |

| 12     | 68     | 28            | 2      | 139                    |  |

| 18     | 69     | 28            | 2      | 140                    |  |

| 24     | 70     | 28            | 2      | 141                    |  |

| 36     | 71     | 28            | 2      | 143                    |  |

| 48     | 73     | 28            | 2      | 145                    |  |

| 54     | 73     | 28            | 2      | 145                    |  |

### 3.7.2 Measurement Conditions for Continuous Receive

$T_amb = 25 \,^{\circ}C$

$VDD\_12 = VDD\_1.2VA = 1.2~V$

$VDD18 = 1.8 \ V = DVDD\_SDIO = VDD\_GPIO =$

VDD\_BT

$VCC_FEM = 3.3V$

Table 3-10. AR6102 Typical Power Consumption - Tx

|                | T10-11                       | Current | Consumption | Total Power |                  |

|----------------|------------------------------|---------|-------------|-------------|------------------|

| Rate<br>[Mbps] | Target Output<br>Power [dBm] | @1.2 V  | @1.8 V      | @3.3 V      | Consumption [mW] |

| 1              | 15                           | 37      | 51          | 135         | 582              |

| 2              | 15                           | 37      | 51          | 135         | 582              |

| 5.5            | 15                           | 37      | 51          | 135         | 582              |

| 11             | 15                           | 37      | 51          | 135         | 582              |

| 6              | 15                           | 44      | 65          | 130         | 600              |

| 9              | 15                           | 44      | 65          | 130         | 600              |

| 12             | 15                           | 44      | 65          | 130         | 600              |

| 18             | 15                           | 44      | 65          | 130         | 600              |

| 24             | 15                           | 45      | 65          | 130         | 600              |

| 36             | 14                           | 45      | 58          | 122         | 561              |

| 48             | 13                           | 45      | 55          | 115         | 532              |

| 54             | 12                           | 45      | 65          | 115         | 551              |

### 3.7.3 Measurement Conditions for Continuous Transmit

$T_amb = 25$  °C

VDD\_12 = VDD\_1.2VA = 1.2 V

VDD18 = 1.8 V = DVDD\_SDIO = VDD\_GPIO =

VDD\_BT

$VCC_FEM = 3.3V$

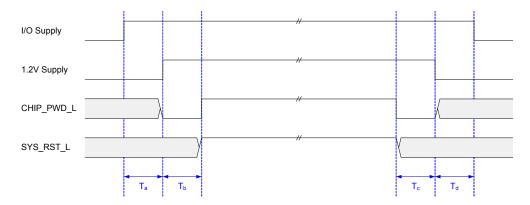

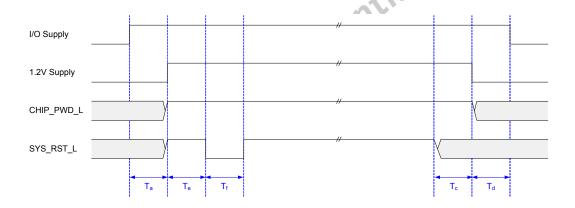

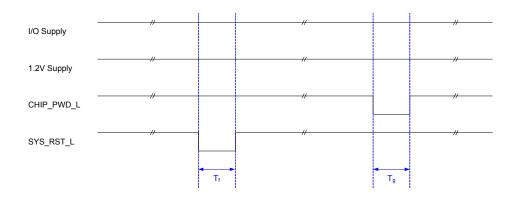

# 3.8 Power Sequence Operation I/O Supply = VDD18, DVDD\_SDIO, VDD\_GPIO, VDD\_BT, VCC\_FEM

1.2V Supply = VDD\_1.2VA, VDD\_12

**NOTE:** CHIP\_PWD\_L or SYS\_RST\_L need to be toggled after all supplies are stable in order to ensure proper reset.

Figure 3-1. Power Up/Power Down Timing While Asserting CHIP\_PWD\_L

Figure 3-2. Power Up/Down Timing While Asserting SYS\_RST\_L

Figure 3-3. Reset and Power Cycle Timing

Table 3-11. Timing Diagram Definitions

|                  | Description                                                            | Min (μsec)       |

|------------------|------------------------------------------------------------------------|------------------|

| T <sub>a</sub>   | Time between I/O supply valid** and 1.2V supply valid                  | 0 <sup>[1]</sup> |

| T <sub>b</sub>   | Time between 1.2V supply valid and CHIP_PWD_L deassertion              | 5                |

| T <sub>c</sub>   | Time between CHIP_PWD_L or SYS_RST_L assertion and 1.2V supply invalid | 0                |

| T <sub>d</sub>   | Time between 1.2V supply invalid and I/O supply invalid                | N/A***           |

| T <sub>e</sub>   | Time between 1.2V supply valid and SYS_RST_L assertion                 | 0                |

| $T_{\mathrm{f}}$ | Length of SYS_RST_L pulse                                              | 1                |

| Tg               | Length of CHIP_PWD_L pulse                                             | 5                |

<sup>[1]</sup>If Ta were negative, there would be additional leakage power which would not exceed 15mW on the 1.2V supply and 150uW on the I/O supply under recommended operating conditions. There would be no functional impact as long as the remainder of the power Atheros Confide up timing is followed.

<sup>\*\*</sup> Supply valid represents the voltage level has reached 90% level.

<sup>\*\*\*</sup> No strict requirement for this parameter. This parameter can also be negative.

Atheros Confidential

### 4. AC Specifications

### 4.1 External 32KHz Input Clock Timing

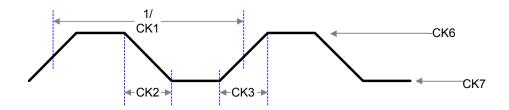

Figure 4-1 and Table 4-1 show the external 32 KHz input clock timing requirements.

Figure 4-1. External 32 KHz Input Clock Timing Requirements

Table 4-1. External 32 KHz Input Clock Timing

| Symbol | Description                    | Min        | Тур    | Max        | Unit |

|--------|--------------------------------|------------|--------|------------|------|

| CK1    | Frequency                      | - , 16     | 32.768 | -          | KHz  |

| CK2    | Fall time                      | 1          | -      | 100        | ns   |

| СК3    | Rise time                      | 1          | -      | 100        | ns   |

| CK4    | Duty cycle (high-to-low ratio) | 15         | -      | 85         | %    |

| CK5    | Frequency stability            | -50        | -      | 50         | ppm  |

| CK6    | Input high voltage             | 0.8*VDD_BT | -      | VDD_BT+0.2 | V    |

| CK7    | Input low voltage              | -0.3       | -      | 0.2*VDD_BT | V    |

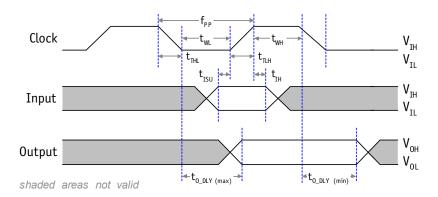

### 4.2 SDIO/GSPI Interface Timing

Figure 4-2 shows the write timing for a SDIO style transaction.

Figure 4-2. SDIO Timing

**Table 4-2. SDIO Timing Constraints**

|                          | rigule 4-2. SDIC                                             | , , , , , , , , , , , , , , , , , , , , | ıy   |      |                                             |

|--------------------------|--------------------------------------------------------------|-----------------------------------------|------|------|---------------------------------------------|

| constraints f            | ows the values for timing for SDIO.  SDIO Timing Constraints | 46,                                     | ntia |      |                                             |

| Parameter                | Description                                                  | Min                                     | Max  | Unit | Note                                        |

| $f_{PP}$                 | Clock frequency data transfer mode                           | 0                                       | 25   | MHz  | $100 \text{ pF} \ge C_L (7 \text{ cards})$  |

| $t_{\mathrm{WL}}$        | Clock low time                                               | 10                                      | -    | ns   | $100 \text{ pF} \ge C_L (7 \text{ cards})$  |

| $t_{WH}$                 | Clock high time                                              | 10                                      | -    | ns   | $100 \text{ pF} \ge C_L (7 \text{ cards})$  |

| $t_{TLH}$                | Clock rise time                                              | -                                       | 10   | ns   | $100 \text{ pF} \ge C_L (10 \text{ cards})$ |

| t <sub>THL</sub>         | Clock fall time                                              | -                                       | 10   | ns   | 100 pF ≥ $C_L$ (7 cards)                    |

| t <sub>ISU</sub>         | Input setup time                                             | 5                                       | -    | ns   | $25 \text{ pF} \ge C_L (1 \text{ card})$    |

| $t_{IH}$                 | Input hold time                                              | 5                                       | -    | ns   | $25 \text{ pF} \ge C_L (1 \text{ card})$    |

| t <sub>O_DLY (min)</sub> | Output delay time during data transfer mode                  | 0                                       | 14   | ns   | $25 \text{ pF} \ge C_L (1 \text{ card})$    |

| t <sub>O_DLY (max)</sub> | Output delay time during identification mode                 | 0                                       | 50   | ns   | 25 pF ≥ $C_L$ (1 card)                      |

### 5. Application Guidelines

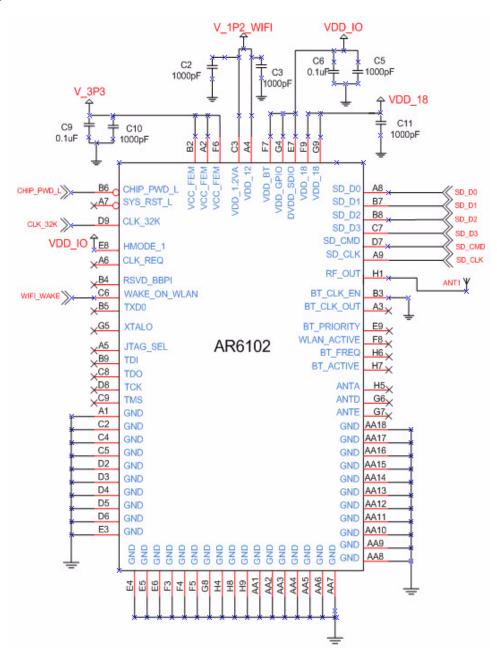

### 5.1 Typical 11b/g Application

For applications that require only 802.11b/g single-antenna operation without the need for cellular and/or Bluetooth coexistence, the AR6102 can be used with a minimal number of external passive components. This is especially advantageous for low-cost, small form-factor

consumer electronics devices such as PMPs, PNDs, gaming devices, and cameras. See Figure 5-1 for details. This design is the basis of the implementations in subsequent sections.

Table 5-1 shows the minimum RBOM for typical 11b/g application.

### 5.2 Application Schematic

Figure 5-1. Application Schematic

Table 5-1. Minimum RBOM for Typical 11b/g Application

| Item | Qty. | Description | Designator           | Size | Value  |

|------|------|-------------|----------------------|------|--------|

| 1    | 5    | Capacitor   | C2, C3, C5, C10, C11 | 0201 | 1000pF |

| 2    | 2    | Capacitor   | C6, C9               | 0201 | 0.1uF  |

| 3    | 1    | Antenna     | ANT1                 | N/A  | N/A    |

### 5.3 11b/g Application with Cellular Coexistence Filter

For those applications that are used in an environment with interference from cellular radios, an external band-pass filter may be used with the AR6102. This filter is installed between the AR6102 RF output port and the antenna. Atheros recommends several filters below, each with different characteristics. Table 5-2. Recommended Co-existence Bandpass Filters Depending on design constraints related to

size, insertion loss, or attenuation at certain critical frequency bands, an appropriate filter can be chosen. See Table 5-2 for details.

Table 5-3 shows the AR6102 output spur levels for 15dBm 1Mbps transmit.

|                         | Filter Attenuation (dB)    |                           |                               |                     |                     |                   |  |

|-------------------------|----------------------------|---------------------------|-------------------------------|---------------------|---------------------|-------------------|--|

| Cellular<br>Frequencies | Murata<br>LFB212G45CE2D006 | TDK<br>DEA202450BT-3201B2 | TDK DEA162450BT-<br>2092AT1-H | Soshin<br>HMD847H   | Soshin<br>HMD844H   | Soshin<br>HMD848H |  |

| 2.17 GHz                | 30                         | 26                        | 30                            | 20                  | 12                  | 35                |  |

| 1.99 GHz                | 35                         | 40                        | 40                            | 40                  | 20                  | 40                |  |

| 1.91 GHz                | 40                         | 40                        | 40                            | 40                  | 20                  | 40                |  |

| 1.79 GHz                | 40                         | 40                        | 40                            | 40                  | 28                  | 40                |  |

| 824 MHz                 | 40                         | 40                        | 40                            | 40                  | 30                  | 40                |  |

| Insertion<br>Loss (dB)  | 2.7                        | 2.5                       | 3.0                           | 2.5                 | 1.5                 | 3.2               |  |

| Size (L x W<br>x H mm)  | 2.0 x 1.25 x 0.6           | 2.0 x 1.25 x 0.8          | 1.60 x 0.8 x 0.6              | 2.0 x 1.25 x<br>1.0 | 2.0 x 1.25 x<br>0.8 | 2.0 x 1.25 x 0.8  |  |

Table 5-3. Output Spur Levels for 15dBm 1Mbps Transmit

| Modulated<br>Data Rate | Frequency<br>(GHz) | Spur Level |

|------------------------|--------------------|------------|

| 1Mbps                  | 1.8196             | -88.75     |

|                        | 1.8461             | -83.61     |

|                        | 1.8981             | -86.8      |

|                        | 1.9501             | -89.56     |

|                        | 2.0021             | -94.4      |

|                        | 2.0541             | -92.54     |

|                        | 2.1061             | -92.56     |

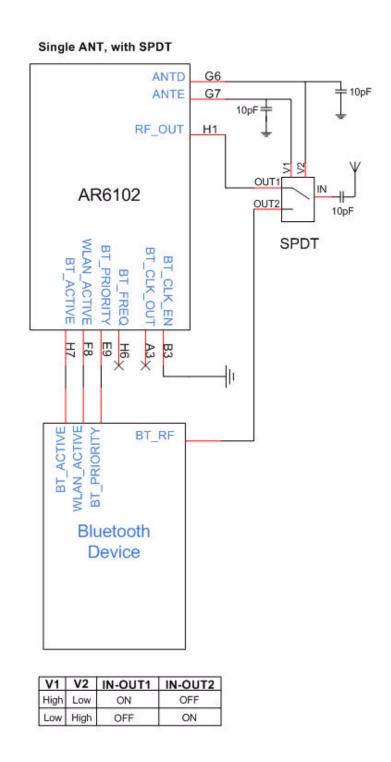

### 5.4 11b/g Application with Bluetooth-Coexistence

orts of the Confidential The AR6102 supports the standard 2, 3, and 4wire Bluetooth coexistence handshake protocol. As such, it can easily interface with any 3rd party Bluetooth device which supports this interface. The pins used for each coexistence interface are described in the Figure 5-2.

Table 5-4. Bluetooth Coexistence Interface Pins

|             | 2-Wire                                                                                                                                                                                                        | 3-Wire                                                                               | 4-Wire                                                                                                                                                                                                                                                                                                              |  |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| BT_ACTIVE   | Signals when the BT device is expecting or is currently performing Tx or Rx activity. It remains asserted until the BT device is finished using the medium.                                                   |                                                                                      |                                                                                                                                                                                                                                                                                                                     |  |

| BT_PRIORITY | Not used. Leave as is.                                                                                                                                                                                        | Asserts when<br>current BY activity<br>is high priority<br>(e.e., SCO LMP<br>traffic | <ul> <li>Time-shared pin:</li> <li>■ At the start of BT_ACTIVE, it asserts to indicate BT activity priority.</li> <li>■ Then indicates BT activity, whether it is Tx or Rx</li> </ul>                                                                                                                               |  |

| BT_FREQ     | Not used. Leave as is.                                                                                                                                                                                        | Not used. Leave as is.                                                               | Indicates whether the BT device is using a restricted channel occupied by WLAN; signal is only applicable for non-AFH BT devices and provides no benefits if using AFH with WLAN, and/or if BT has low RF isolation from WLAN. The functionality of this pin is made obsolete by the Atheros coexistence scheduler. |  |

| WLAN_ACTIVE | Indicates whether WLAN grants or blocks BT's Tx/Rx request. The pin polarity is configurable. By default, when asserted, it signals to BT that it has WLAN activity and is blocking BT from using the medium. |                                                                                      |                                                                                                                                                                                                                                                                                                                     |  |

Because the 3-wire interface offers robust coexistence performance and is the most widely adopted, the focus for the implementation will be on this interface. In addition, since most embedded applications utilize a single antenna for WLAN and BT to share, the hardware implementation will focus on the components and control signals that are required for single antenna coexistence.

Given the single-antenna requirement and the fact that WLAN transmit and receive will occur at one port, the following front-end options are available. These options, along with some high level advantages/disadvantages are summarized in the table below

Table 5-5. Front End Options - Advantages and Disadvantages

|               | Single ANT, with SPDT                                                                                                                                                             |  |  |  |  |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Advantages    | <ul> <li>Lowest path loss for both WLAN and BT, which allows for highest output power and receive sensitivy.</li> <li>Targeted for higher performance at longer range.</li> </ul> |  |  |  |  |

| Disadvantages | ■ No simultaneous WLAN and BT activity, since only one device has access to the antenna at any given time.                                                                        |  |  |  |  |

Figure 5-2. Bluetooth Coexistence Application

It is important to connect the switch control lines such that BT\_RF has the antenna when ANTD is HIGH. The reason for this is that when WLAN is asleep or in power-down/reset mode, ANTD defaults to a HIGH and hence allows BT to take control of the medium while WLAN is not being used. Power to the VCC\_FEM pins must be continually supplied in each of the operating modes in order to maintain the switch state. While in powerdown or power-save mode, the voltage on ANTD ranges from 1.9 - 2.4V across the full range of VCC\_FEM (3.0 - 4.2V). Therefore, it is important to select a switch that operates with a switch control voltage between 1.9 - 2.4V in order to allocate the RF path to BT while the

WLAN device is in power-down or power-save mode.

Figure 5-3 depict the major components and signal connections that are necessary for implementing the options summarized in Table 5-5.

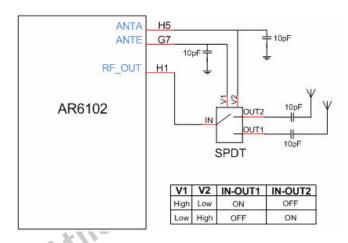

### 5.5 11b/g Application with Antenna Diversity

The AR6102 supports fast antenna diversity with the addition of an external SPDT switch and the use of two antennas. To achieve the maximum benefits of antenna diversity, it is recommended to place the antennas as far apart as possible.

Figure 5-3. AR6102 Fast Antenna Diversity Implementation

### 5.6 Power Supply Management

The AR6102 requires various power supplies and are described in the table below. The recommended operating conditions for each power supply are also given. It is important to note the current consumption on each supply rail (refer to Table 3-8, 3-9, and 3-10) in order to budget the typical amount of power that needs to be delivered to each supply. Maximum current consumption across temperature and voltage is given in Table 5-6

Atheros Confidential

Table 5-6. Power Supplies and Recommended Operating Conditions

| Symbol    | Description / Recommendations                                                                                                                                                                                                                                                                                                                                   | Min. | Тур. | Max  | Unit |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| VCC_FEM   | M ■ Supplies internal PA and RF switch controls.  ■ When using an off-module switch, as in the case for antenna diversity implementations, it is important to make sure that VCC_FEM is at least 100mV higher than the recommended control signal levels of the off-module switch.  ■ Maximum current consumption of 165mA.                                     |      | 3.3  | 3.6  |      |

| VDD_1.2VA | <ul> <li>Supplies critical analog RF and baseband blocks such as the 2.4GHz Tx/Rx chain, synthesizer, and current reference circuitry.</li> <li>Bypass this supply with a 1000pF capacitor placed close to the supply pin. Refer to C2 in Section 5.2 and layout guidelines for details.</li> <li>Combined VDD_1.2VA and VDD_12 current is 97mA MAX.</li> </ul> | 1.14 | 1.2  | 1.26 |      |

| VDD_12    | <ul> <li>Supplies the internal digital logic.</li> <li>This can share the same supply as the VDD_1.2VA pin.</li> <li>Bypass this supply with a 1000pF capacitor placed close to the supply pin. Refer to C3 in the "Application Schematic" and layout guidelines for details.</li> <li>Combined VDD_1.2VA and VDD_12 current is 97mA MAX.</li> </ul>            | 1.14 | 1.2  | 1.26 | V    |

| VDD_BT    | ■ Supplies the BT co-existence I/O interface: BT_Priority / GPIO0 WLAN_ACTIVE / GPIO1 BT_FREQ / GPIO2 BT_ACTIVE / GPIO3 CLK32K - External 32KHz clock input pin ■ The voltage for this supply should be set at the same level as the voltage of the I/O interface. ■ VDD_BT and sleep clock amplitude should match                                              | 1.71 | 1.8  | 3.46 |      |

| VDD_GPIO  | <ul> <li>Supplies the WAKE_ON_WLAN pin and UART interface pin.</li> <li>The voltage for this supply should be set at the same level as the voltage of the I/O interface.</li> </ul>                                                                                                                                                                             | 1.71 | 1.8  | 3.46 |      |

| DVDD_SDIO | <ul> <li>Supplies the SDIO interface, HMODE_1 strap configuration pin, and JTAG interface.</li> <li>Voltage level should be set at the same level as the host SDIO interface.</li> </ul>                                                                                                                                                                        | 1.71 | 1.8  | 3.46 |      |

| VDD18     | <ul> <li>Supplies the RF analog circuitry.</li> <li>Bypass this supply with a 1000pF capacitor placed close to the supply pin. Refer to C11 in the and layout guidelines. Refer to C11 in the "Application Schematic" and layout "Application Guidelines" on page 27 for details.</li> <li>Maximum current consumption of 83mA</li> </ul>                       | 1.71 | 1.8  | 1.89 |      |

### 5.7 Grounding

The AR6102 ground pads are not differentiated between digital and analog grounds. As such, all grounds should be connected together on the end application board.

#### 5.8 Host Interfaces and GPIOs

### 5.8.1 Secure Digital Input/Output (SDIO)

The AR6102 is compliant with SDIO v1.1 specifications. For 4-bit mode, all four SDIO data lines are available. If 1-bit mode is turned on by software, data is sent only over SD\_D0; this mode is good for troubleshooting (ie., driver loading issues). The table below describes the SDIO mode pins.

Table 5-7. SDIO Mode Pins

| Pin Name | SDIO<br>Type | Pad Power Supply | Description                                                                       |

|----------|--------------|------------------|-----------------------------------------------------------------------------------|

| SD_CLK   | I            |                  | SDIO input clock from Host (up to 25MHz).<br>No external pull-up resistor needed. |

| SD_Cmd   | I/O          | DVDD_SDIO        | SDIO Command Line<br>Internal pull-up, no external pull-<br>up resistor needed.   |

| SD_D0    | I/O          | 25               | SDIO Data0 Line<br>Internal pull-up, no external pull-<br>up resistor needed.     |

| SD_D1    | I/O          | Los Con          | SDIO Data1 Line<br>Internal pull-up, no external pull-<br>up resistor needed.     |

| SD_D2    | I/O          |                  | SDIO Data2 Line<br>Internal pull-up, no external pull-<br>up resistor needed.     |

| SD_D3    | I/O          |                  | SDIO Data3 Line<br>Internal pull-up, no external pull-<br>up resistor needed.     |

#### 5.8.2 Dedicated Function Pins

#### BT Coexistence

Dedicated to WLAN-BT coexistence using a four-wire bus:

> BT\_PRIORITY WLAN\_ACTIVE BT\_FREQ BT\_ACTIVE

#### Sleep Clock

- Dedicated to 32KHz clock input (CLK\_32K)

#### UART Output

Dedicated to UART Tx (TXD0)

#### ■ Wake-on-Wireless

- Dedicated for wake-on-wireless feature (WAKE ON WLAN), a hardware toggle point from the WLAN device to the HOST. Generally, once the system (and thus the WLAN device) is placed into a low-power state, the WLAN device continues to remain associated with its current AP to receive and monitor incoming frames.

- If one of a number of specified patters are detected in the frame, the WLAN device wakes up HOST by asserting a hardware pin. Upon wakeup, the driver for the HOST is notified of the change in power state and data connectivity with the AP is re-established. Because this

ridential

defaults low, the wake-on-wireless interrupt is active high.

### 5.9 RF Port Matching

The AR6102 uses a single port, LGA pad H1, as an RF input/output for receive/transmit operation. No external DC-block is necessary.

For optimal performance, all connections to this port, including traces and antennas, should have a 50-ohm impedance.

### 5.10 External 32KHz Sleep Clock

Two hardware solutions exist for the 32KHz sleep clock:

- External sleep clock driven by an XO

- HOST driven sleep clock

The AR6102 has the ability to provide a buffered 26MHz clock on the BT\_CLK\_OUT pin. Please refer to Table 3-7 for information about the characteristics of this clock.

To save layout area and BOM, the HOST 32KHz drive option is recommended for use in the end application. When a HOST 32KHz drive or external oscillator is used, the clock should be DC-coupled into the CLK\_32K pin.

If the sleep clock voltage swing level exceeds that of the DVDD\_SDIO voltage, then a 1K-ohm series resistor at the CLK\_32K input is necessary. Depending on the drive strength of the clock source, this resistance may need to be lowered to meet the rise time requirements.

### 5.11 Clock Sharing

The buffered clock that is driven out on BT\_CLK\_OUT is enabled by driving BT\_CLK\_EN to 1.8V. It is enabled using this signal only and can be enabled regardless of the power state of the AR6102 (power-down mode, sleep and awake modes). As long as the VDD\_1.2VA and VDD18 supplies are given to the device and the BT\_CLK\_EN is driven high, the buffered clock output will be available.

There is a minimal current consumption penalty when enabling this clock. Typically, there will be an additional 490uA of current on the VDD18 supply and an additional 458uA on the VDD\_1.2VA supply (regardless of operating mode) when the buffered clock is enabled.

#### 5.12 Host Configuration Guidelines

The option to use SDIO is selected by tying HMODE\_1 to the same voltage level as VDD\_GPIO.

#### 5.13 Layout Guidelines

#### 5.13.1 General Guidelines

A cost effective design can be realized by utilizing vias formed with a 6 mil drill, 11 mil pad, with 2.5 mil angular ring; these can be used to route the  $0.35 \times 0.35$  pads on other layers. The figure below depicts an example of the via placement and escape routes used for each of the inner pads.

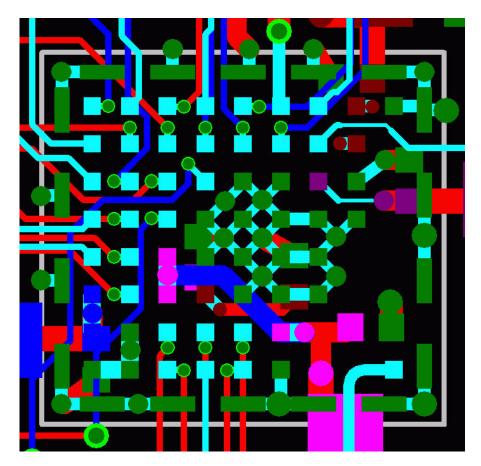

Figure 5-4. Layout Diagram

In general, the AR6102 can be routed on a 4layer board assuming the following layer usage:

**Layer 1**: Signals and RF traces.

**Layer 2**: Mainly ground with some signals. RF traces on layer 1 should traverse over solid ground planes on layer 2.

Layer 3: Power planes

Layer 4: More signals

#### 5.13.2 Component Placement

All bypass capacitors depicted in the reference schematic need to be place as close as possible to the AR6102. Placing these bypass

components on the backside of the board is fine, as long as the physical distance to the supply pin is reduced. Supplies that share a regulator need to have bypass capacitors placed close to the AR6102 and prior to the traces joining.

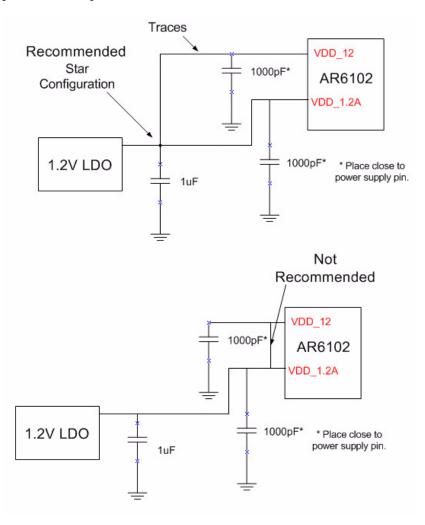

### 5.14 VDD\_12 and VDD\_1.2VA Power Trace Routing

It is critical to route the VDD 12 and VDD\_1.2VA supplies using separate traces. Each trace should have a bypass capacitor placed close to the power supply input pin. The traces should only be connected at a central, noise-free node in a star configuration.

See Figure 5-5 for details. Bypassing these two supplies separately is required for optimal EVM and spectrum mask performance.

Figure 5-5. Recommended Star Configuration

#### 5.14.3 Host Interface Layout

For the layout of the host interface signals SD\_CLK, SD\_CMD, and SD\_D[3:0], the following should be checked:

- Verify that GND with uniform vias between the top and bottom layers is incorporated between the CLK line and the data line(s).

- Avoid connections on data and clock lines due to high speed digital voltage returns and inductive characteristics of vias (which can also incorporate capacitive characteristics due to layer to layer capacitance).

If the AR6102 is to be used on a development platform, it is recommended to incorporate an extra RC filter on the SD\_CLK line or other data lines. This is to allow tenability against different hosts which may require different overshoot handling due to length of the interface traces. Keep capacitor values in the RC filter to a minimal value.

### 5.14.4 32KHz Clock Signal Layout

For an optimal sleep clock signal layout, the designer must keep the clock trace away from digital and power traces.

### 5.14.5 Grounding

The layout designer must avoid ground discontinuity. RF traces should have solid grounding directly under the entire trace for proper impedance control.

Atheros Confidential

Atheros Confidential

### 6. Assembly Guidelines

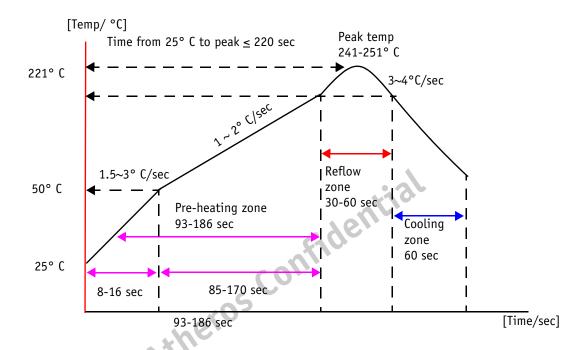

### 6.1 Reflow profile

Figure 6-1 shows the Reflow Profile.

See Table 6-1 for the recommended reflow settings.

Figure 6-1. Reflow Profile

Table 6-1. Recommended Reflow Settings

| Zone       |          |               |             |           |         |            |

|------------|----------|---------------|-------------|-----------|---------|------------|

|            | Dry Zone | Pre-heat Zone | Reflow Zone | Peak Zone | Cooling | Atmosphere |

| Temp ° C   | 25-50    | 50-221        | 221         | 241-251   | 217-50  | N2         |

| Time (sec) | 90       | 65            | 45          | 2         | 60      |            |

#### 6.2 Solder material recommendations

Manufacturer name: Kester

Solder paste part number: EM808-Sn96.5% Ag3.0% Cu0.5% SAC305 alloy with Type 3 power, water soluble solder paste

Atheros Confidential

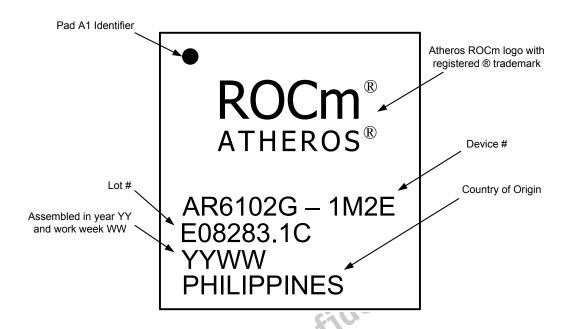

### 7. Package Marking Information

The chapter explains the package marking on the AR6102. See Figure 7-1 for details.

Figure 7-1. AR6102 Package Marking

Atheros Confidential

### 8. Ordering Information

Please contact your local Atheros sales representative at one of the worldwide offices listed below.

#### Atheros Communications, Inc.

5480 Great America Parkway Santa Clara, CA 95054 t +1 408.773.5200 f+1408.773.9940 info@atheros.com

#### **Atheros Communications Irvine**

8 Hughes Irvine, Ca. 92618 t 949.453.2727 f 949.341.0423 info@atheros.com

#### **Atheros Hong Kong Limited**

P.O. Box No. 333, Fo Tan Post Office, N.T., Hong Kong t +852 8206.1131 f +852 8206.1301 sales\_china@atheros.com

#### Atheros (Shanghai) Co., Ltd.

690 Bibo Road,4F,Unit 9 Shanghai, P.R. China 201203 t +86-21.5080.3680 f +86 21.5027.0100 sales\_china@atheros.com

#### Atheros GmbH

Braunschweiger Str. 8 45886 Gelsenkirchen Germany Amy.Chang@atheros.com

#### **Atheros Communications KK-Japan**

KDX Shinbashi Bldg. 2-9, 2-chome Shinbashi, Minato-ku, Tokyo 105-0004, Japan t +81 3.5501.4100 f +81 3.5501.4129 sales\_japan@atheros.com

#### Atheros Korea

1218, 12F, Downtown Bldg., 22-3 SuNae-dong, Bundang-ku, Seongnam City, Gyeonggi-do, Korea 463-825 t +82 31.786.0428 sales\_korea@atheros.com

#### **Atheros Technology Taiwan Corporation**

9F, No.110, Chou Tze St, Nei Hu Dist, Taipei, Taiwan 114 R.O.C. t + 886 2.8751.6385 f + 886 2.8751.6397

sales\_tw@atheros.com

The information in this document has been carefully reviewed and is believed to be accurate. Nonetheless, this document is subject to change without notice. Atheros assumes no responsibility for any inaccuracies that may be contained in this document, and makes no commitment to update or to keep current the contained information, or to notify a person or organization of any updates. Atheros reserves the right to make changes, at any time, to improve reliability, function or design and to attempt to supply the best product possible.

MKG-0942 Rev. 1

Atheros Communications, Incorporated 5480 Great America Parkway Santa Clara, CA 95054 t: 408/773-5200 f: 408/773-9940 www.atheros.com