AP72202

May 2024

### HIGH-EFFICIENCY SYNCHRONOUS DC-DC BUCK-BOOST CONVERTER WITH 4.4A SWITCHES

### **Description**

The AP72202 is a high-current synchronous buck-boost converter providing high efficiency, excellent transient response and high DC output accuracy. The targeted applications are smartphones, tablets, and other handheld devices. The AP72202 utilizes a four-switch Hbridge configuration to support buck and boost operation. The buckboost provides at least 2A output current.

The current control scheme handles wide input/output voltage ratios and provides low external component count with outstanding performance in line/load transient response and seamless transition between buck and boost modes.

The AP72202 features I<sup>2</sup>C compatible, two-wire serial interface consisting of a bidirectional serial-data line, SDA, and a serial-clock line, SCL. It supports SCL clock rates up to 3.4MHz.

The AP72202 also features UVLO, OTP, and OCP to protect the circuit.

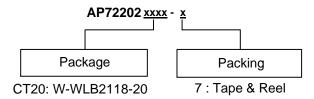

This IC is available in a small 2.125 x 1.750mm, 20 balls WLCSP package.

#### **Features**

- V<sub>IN</sub> 2.3V to 5.5V

- Output Voltage Range: 2.6V to 5.14V

- 2A Continuous Output Current for V<sub>OUT</sub> = 3.4V and V<sub>IN</sub> > 2.9V Efficiency Up to 97%

- 2.5MHz Switching Frequency

- I<sup>2</sup>C Interface

- Selectable MODE PFM/PWM

- Ultrasonic Operation Programmable Through I<sup>2</sup>C

- Power-Good (PG) Indicator with 5MΩ Internal Pullup

- Adjustable Overcurrent Limit

- Fully Protected for Overcurrent, Short-Circuit, Reverse Current Protection, Overtemperature, and UVLO

- Totally Lead-Free & Fully RoHS Compliant (Notes 1 & 2)

- Halogen and Antimony Free. "Green" Device (Note 3)

- For automotive applications requiring specific change control (i.e. parts qualified to AEC-Q100/101/104/200, PPAP capable, and manufactured in IATF 16949 certified facilities), please contact us or your local Diodes representative.

https://www.diodes.com/quality/product-definitions/

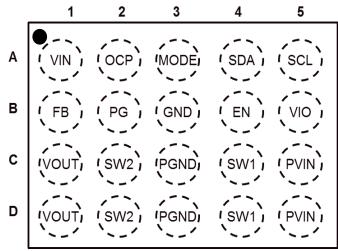

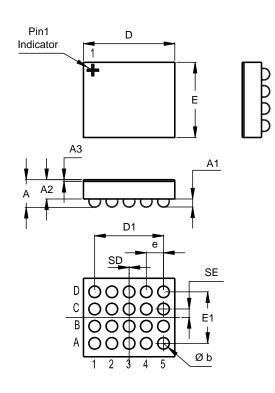

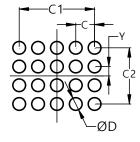

### **Pin Assignments**

TOP VIEW (BALLS SIDE DOWN)

## **Applications**

- **Smartphones**

- **Tablets**

- Portable consumer devices

Notes:

- 1. No purposely added lead. Fully EU Directive 2002/95/EC (RoHS), 2011/65/EU (RoHS 2) & 2015/863/EU (RoHS 3) compliant.

- 2. See https://www.diodes.com/quality/lead-free/ for more information about Diodes Incorporated's definitions of Halogen- and Antimony-free, "Green" and

- 3. Halogen- and Antimony-free "Green" products are defined as those which contain <900ppm bromine, <900ppm chlorine (<1500ppm total Br + CI) and <1000ppm antimony compounds.

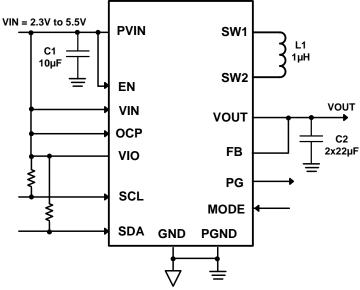

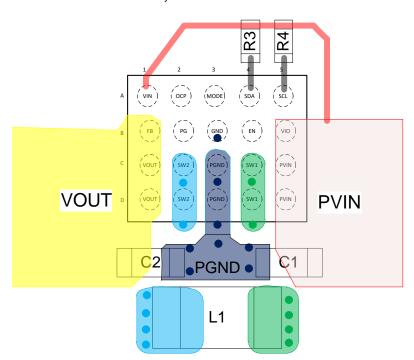

# **Typical Applications Circuit**

Figure 1. Typical Application Circuit

## **Pin Descriptions**

| Pin    | Pin Number | Firmation                                                                                                                                                                                                                                       |

|--------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name   | 20 BALLS   | Function                                                                                                                                                                                                                                        |

| VIN    | A1         | Input supply for the logic control circuitries.                                                                                                                                                                                                 |

| OCP    | A2         | OCP program the current limit. LOW will set the OCP threshold to 2A. HIGH will set the OCP threshold to 4.3A.                                                                                                                                   |

| 001    | AZ         | I <sup>2</sup> C can override the MODE pin. See the register for more detail.                                                                                                                                                                   |

| MODE   | А3         | MODE logic input. LOW for PFM operation. HIGH for forced PWM. There is an internal $5.5M\Omega$ resistor from MODE and GND to set the IC in PFM if left floating. I <sup>2</sup> C can override the MODE pin. See the register for more detail. |

| SDA    | A4         | I <sup>2</sup> C Data I/O.                                                                                                                                                                                                                      |

| SCL    | A5         | I <sup>2</sup> C Clock Input.                                                                                                                                                                                                                   |

| FB     | B1         | Feedback Input. FB senses the output voltage and regulates it. Connect FB to VOUT.                                                                                                                                                              |

| PG     | B2         | Open-drain power-good output that is pulled to GND when the output voltage is out of its regulation limits or during soft-start interval. Active high by default. There is an internal 5MΩ pullup resistor to VIO.                              |

| GND    | B3         | Analog ground that is used for control.                                                                                                                                                                                                         |

| EN     | B4         | Enable Input. EN is a digital input that turns the regulator on or off. Drive EN high to turn on the regulator; low to turn it off.                                                                                                             |

| VIO    | B5         | Input supply for the I <sup>2</sup> C and PG internal pullup resistor.                                                                                                                                                                          |

| VOUT   | C1, D1     | Buck-Boost output.                                                                                                                                                                                                                              |

| SW2    | C2, D2     | Switch Node 2.                                                                                                                                                                                                                                  |

| PGND   | C3, D3     | Power Ground.                                                                                                                                                                                                                                   |

| SW1    | C4, D4     | Switch Node 1.                                                                                                                                                                                                                                  |

| PVIN   | C5, D5     | Power Input. Bypass PVIN to GND with a 10µF capacitor to eliminate noise on the input to the IC.                                                                                                                                                |

| . 7111 | CC, DO     | See Input Capacitor.                                                                                                                                                                                                                            |

### Absolute Maximum Ratings (Note 4) (@TA = +25°C, unless otherwise specified.)

| Symbol                              | Parameter                | Rating             | Unit |

|-------------------------------------|--------------------------|--------------------|------|

| V <sub>IN</sub> , PV <sub>IN</sub>  | Supply Voltage           | -0.3 to 7.0        | V    |

| Vout                                | Output Voltage           | -0.3 to 6.0        | V    |

| Vsw1, Vsw2                          | Switch Node Voltage      | -1.0 to 7.0 (DC)   | V    |

| V <sub>SW1</sub> , V <sub>SW2</sub> | Switch Node Voltage      | -2.5 to 8.0 (20ns) | V    |

| Vio                                 | I <sup>2</sup> C Voltage | -1.0 to 7.0        | V    |

| All Other Pins                      |                          | -0.3 to 7.0        | V    |

| TJ                                  | Junction Temperature     | +150               | °C   |

| TL                                  | Lead Temperature         | +260               | °C   |

| ESD Susceptibility (Note 5)         |                          | _                  | _    |

| НВМ                                 | Human Body Model         | 3000               | V    |

| CDM                                 | Charged Device Model     | 1000               | V    |

Notes:

### Thermal Resistance (Note 6)

| Symbol | Parameter           | Rat             | Unit |      |

|--------|---------------------|-----------------|------|------|

| θЈА    | Junction to Ambient | 2.125 × 1.750mm | 50   | °C/W |

| θυς    | Junction to Case    | 2.125 × 1.750mm | 2    | °C/W |

Note:

6. Test condition for WLCSP: Device mounted on FR-4 substrate, four-layer PC board, 2oz copper, with minimum recommended pad layout

## Recommended Operating Conditions (Note 7) (@TA = +25°C, unless otherwise specified.)

| Symbol | Parameter                           | Min | Max | Unit |

|--------|-------------------------------------|-----|-----|------|

| PVIN   | Supply Voltage                      | 2.3 | 5.5 | V    |

| TA     | Operating Ambient Temperature Range | -30 | +85 | °C   |

Note:

7. The device function is not guaranteed outside of the recommended operating conditions.

<sup>4.</sup> Stresses greater than the *Absolute Maximum Ratings* specified above can cause permanent damage to the device. These are stress ratings only; functional operation of the device at these or any other conditions exceeding those indicated in this specification is not implied. Device reliability can be affected by exposure to absolute maximum rating conditions for extended periods of time.

<sup>5.</sup> Semiconductor devices are ESD sensitive and can be damaged by exposure to ESD events. Suitable ESD precautions should be taken when handling and transporting these devices.

$\begin{tabular}{ll} \textbf{Electrical Characteristics} & (@T_A = +25^{\circ}C, V_{IN} = PV_{IN} = EN = 3.6V, unless otherwise specified.) \\ \textbf{Min/Max limits apply across the recommended ambient temperature range, -30^{\circ}C to +85^{\circ}C and input voltage range 2.3V to 5.5V.} \\ \end{tabular}$

|                                | naracteristics                                                   | Toot Conditions                                                                                                               | M:-   | T     | Max   | 11-2 |

|--------------------------------|------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|------|

| Symbol                         | Parameter                                                        | Test Conditions                                                                                                               | Min   | Тур   | Max   | Unit |

| lin                            | Shutdown Supply Current                                          | V <sub>EN</sub> = 0                                                                                                           | _     | 0.3   | 1     | μA   |

| THN                            |                                                                  | VEN = VIN, Non-Switching,<br>EN_PD BIT = 0                                                                                    | _     | 20    | 30    | μΑ   |

|                                |                                                                  | PFM, $V_{EN} = V_{IN}$ , $V_{IO} = 0$ , $MODE = 0$                                                                            | _     | 29    | 45    | μΑ   |

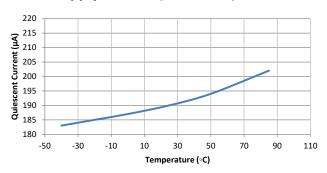

| lin                            | Supply Current (Quiescent)                                       | Ultrasonic Mode, V <sub>EN</sub> = V <sub>IN</sub> ,<br>V <sub>IO</sub> = 0, MODE = 0,<br>BB_UMODE=1, BB_FPWM=0               | 1     | 180   | 250   | μA   |

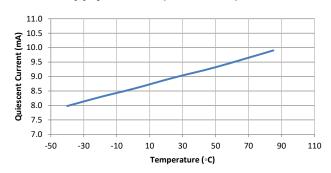

|                                |                                                                  | PWM, VEN = VIN, VIO = 0,<br>MODE = 1                                                                                          | _     | 9     | 15    | mA   |

|                                | V <sub>IN</sub> Power-On-Reset Voltage<br>Threshold, Rising Edge | _                                                                                                                             | 2.150 | 2.225 | 2.295 | V    |

| POR/UVLO                       | V <sub>IN</sub> , Undervoltage Lockout Threshold, Falling Edge   | _                                                                                                                             | 2.055 | 2.125 | 2.230 | V    |

|                                | Hysteresis                                                       | _                                                                                                                             | 50    | 100   | 150   | mV   |

| RDS(ON)1                       | High-Side Switch On-Resistance from PVIN to SW1                  | _                                                                                                                             |       | 25    | 40    | mΩ   |

| RDS(ON)2                       | Low-Side Switch On-Resistance from SW1 to PGND                   | _                                                                                                                             | 1     | 25    | 40    | mΩ   |

| R <sub>DS(ON)3</sub>           | High-Side Switch On-Resistance from SW2 to VOUT                  | _                                                                                                                             |       | 25    | 40    | mΩ   |

| RDS(ON)4                       | Low-Side Switch On-Resistance from SW2 to PGND                   | _                                                                                                                             | 1     | 25    | 40    | mΩ   |

| RDISCHARGE                     | VOUT Soft Discharge On-Resistance                                | _                                                                                                                             | 70    | 100   | 130   | Ω    |

| Leakage<br>Current<br>SW1/SW2  | HS Q1 or HS Q3 Leakage Current                                   | SW1 = 0 or SW2 = 0,<br>V <sub>IN</sub> = 5.5V, EN = 0                                                                         | _     | _     | 1     | μΑ   |

|                                | B :: 110.0                                                       | OCP = 0                                                                                                                       | 2.25  | 2.50  | 2.75  | Α    |

| I <sub>LIMIT</sub>             | Positive HS Current Limit, Q1                                    | OCP = V <sub>IN</sub>                                                                                                         | 4.0   | 4.4   | 4.8   | Α    |

| Ірғмрк                         | PFM Peak Current Limit                                           | _                                                                                                                             | 1.0   | 1.3   | 1.6   | Α    |

| Izc                            | Zero Cross Current Threshold                                     | _                                                                                                                             |       | 200   | _     | mA   |

| INLIMIT                        | Negative LS Current Limit, Q2                                    | _                                                                                                                             | 1.4   | 2.0   | 2.6   | Α    |

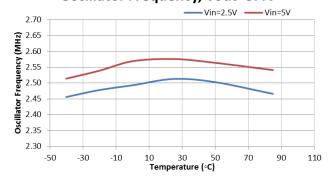

| fsw                            | Oscillator Frequency                                             | Continuous Switching<br>Frequency at Both Buck and<br>Boost Mode                                                              | 2.1   | 2.5   | 2.9   | MHz  |

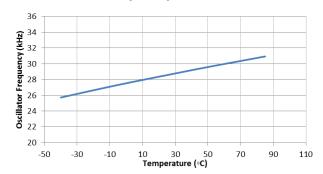

|                                |                                                                  | Ultrasonic Mode,<br>BB_UMODE=1, BB_FPWM=0                                                                                     | 20    | 27    | _     | kHz  |

|                                | Output Voltage Range                                             | I <sup>2</sup> C Programmable (20mV step)                                                                                     | 2.60  | _     | 5.14  | V    |

| Vout                           | Default Output Voltage                                           | IOUT = 0, Address 0x04,<br>VOUT [6:0] = 0x28, MODE = 1                                                                        | 3.366 | 3.400 | 3.434 | V    |

|                                | Output Accuracy                                                  | IOUT = 0, Address 0x04,<br>Vout [6:0] = 0x28, MODE = 0                                                                        | 3.349 | _     | 3.46  | V    |

|                                |                                                                  | PFM, V <sub>IN</sub> = 2.3V-5.5V,<br>I <sub>OUT</sub> = 0, Address 0x04,<br>V <sub>OUT</sub> [6:0] = 0x28, MODE = 0           | _     | 1.3   | _     | mV/\ |

| $\Delta V_{OUT}/\Delta V_{IN}$ | Line Regulation                                                  | Ultrasonic Mode, $V_{IN} = 2.3V$ - $5.5V$ , $I_{OUT} = 0$ , Address $0x04$ , $V_{OUT}$ [6:0] = $0x28$ , BB_UMODE=1, BB_FPWM=0 | _     | 1.7   | _     | mV/\ |

|                                |                                                                  | PWM, V <sub>IN</sub> = 2.3V-5.5V,<br>I <sub>OUT</sub> = 2A, Address 0x04,<br>V <sub>OUT</sub> [6:0] = 0x28, MODE = 1          | _     | 1     | _     | mV/\ |

## **Electrical Characteristics** (continued)

| Symbol                        | Parameter                                | Test Conditions                                                                                   | Min                   | Тур                       | Max                   | Unit |

|-------------------------------|------------------------------------------|---------------------------------------------------------------------------------------------------|-----------------------|---------------------------|-----------------------|------|

|                               |                                          | PFM, Iout = 0-2A, Address<br>0x04,<br>Vout [6:0] = 0x28, MODE = 0                                 | _                     | 16.5                      | _                     | mV/A |

| ΔVουτ/ΔΙουτ                   | Load Regulation                          | Ultrasonic Mode, IouT = 0-2A,<br>Address 0x04, VouT [6:0] =<br>0x28, BB_UMODE = 1,<br>BB_FPWM = 0 | _                     | 16.5                      | _                     | mV/A |

|                               |                                          | PWM, I <sub>OUT</sub> = 0-2A, Address<br>0x04, V <sub>OUT</sub> [6:0] = 0x28,<br>MODE = 1         | _                     | 3.5                       | _                     | mV/A |

| PG Detection                  | Threshold                                | Percentage of Output<br>Regulation                                                                | 75                    | 80                        | 85                    | %    |

|                               | Thresholds Hysteresis                    | —                                                                                                 | _                     | 5                         | _                     | %    |

| PG Low<br>Voltage             | PG LOW                                   | I <sub>PG</sub> Sink = 3mA                                                                        | _                     | _                         | 0.4                   | V    |

| PG Delay                      | Rising Edge                              | _                                                                                                 | _                     | 1.5                       | _                     | ms   |

| PG Delay                      | Falling Edge                             | _                                                                                                 | _                     | 3                         | _                     | μs   |

| Ven_h,<br>Vmode_h,<br>Vocp_h  | EN/MODE/OCP Logic-High                   | _                                                                                                 | 1.4                   | _                         | _                     | V    |

| VEN_L,<br>VMODE_L,<br>VOCP_L  | EN/MODE/OCP Logic-Low                    | _                                                                                                 | _                     | _                         | 0.4                   | V    |

|                               | ENUI                                     | V <sub>EN</sub> = 5.5V, EN_PD BIT = 0                                                             | _                     | 0.1                       | _                     | μΑ   |

| I <sub>EN</sub>               | EN Input Current                         | Ven = 0                                                                                           | _                     | 0.1                       | _                     | μA   |

| ,                             | OCD lanut Current                        | Vocp = 5.5V                                                                                       | _                     | 0.1                       | _                     | μA   |

| I <sub>OCP</sub>              | OCP Input Current                        | Vocp= 0                                                                                           | _                     | 0.1                       | _                     | μA   |

|                               |                                          | VMODE = 5.5V                                                                                      | _                     | 1                         | _                     | μA   |

| IMODE                         | MODE Input Current                       | V <sub>MODE</sub> = 0                                                                             | _                     | 0.1                       | _                     | μA   |

|                               |                                          | OCP = 0                                                                                           | _                     | 0.8                       | _                     |      |

| tss                           | Soft-Start Period                        | OCP = VIN                                                                                         | _                     | 0.12                      | _                     | ms   |

| _                             | Thermal Shutdown (Note 8)                | _                                                                                                 | _                     | 150                       | _                     | °C   |

| T <sub>SD</sub>               | Thermal Hysteresis (Note 8)              | <u> </u>                                                                                          | _                     | 15                        | _                     | °C   |

| I <sup>2</sup> C Electrical C | haracteristics                           | ·                                                                                                 |                       |                           |                       |      |

| Vio                           | VI Voltage Range                         | _                                                                                                 | 1.7                   | _                         | 5.5                   | V    |

|                               | SCL, SDA Input High Voltage<br>Threshold | _                                                                                                 | 0.7 x V <sub>IO</sub> | _                         | _                     | V    |

|                               | SCL, SDA Input Low Voltage<br>Threshold  | _                                                                                                 | _                     | _                         | 0.3 x V <sub>IO</sub> | V    |

| SCL, SDA                      | Hysteresis                               | _                                                                                                 | _                     | 0.05 x<br>V <sub>IO</sub> |                       | V    |

|                               | Input Current                            | _                                                                                                 | -10                   | _                         | 10                    | μΑ   |

|                               | Input Capacitance                        |                                                                                                   | _                     | 10                        | _                     | pF   |

| SDA                           | Output Low Voltage                       | I <sub>SINK</sub> = 20mA                                                                          | _                     | _                         | 0.4                   | V    |

| tor                           | Output Fall Time from VIO to 0.3 x VIO   | _                                                                                                 | _                     | _                         | 120                   | ns   |

Note: 8. All min/max parameters compliance to the datasheet limits are assured by one or more methods: production test, characterization, and/or design.

## **Electrical Characteristics** (continued)

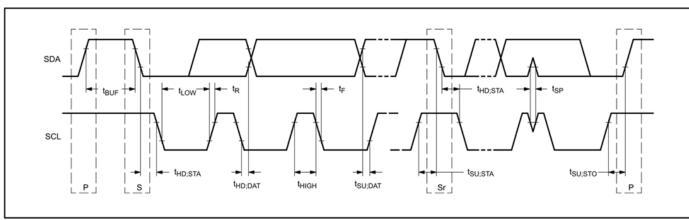

| I <sup>2</sup> C – Compatible Interface Timing (Standard, Fast, and Fast Mode Plus) (Note 8) |                                                                                |                                                                                                                                     |      |     |     |      |  |  |

|----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|------|-----|-----|------|--|--|

| Symbol                                                                                       | Parameter                                                                      | Test Conditions                                                                                                                     | Min  | Тур | Max | Unit |  |  |

| f <sub>SCL</sub>                                                                             | Clock Frequency                                                                | _                                                                                                                                   | _    | _   | _   | MHz  |  |  |

| tsu;sta                                                                                      | Setup Time (Repeated) Start<br>Condition                                       | SCL rising edge to SDA falling edge; Both crossing High threshold                                                                   | 0.26 | _   | _   | μs   |  |  |

| t <sub>HD;STA</sub>                                                                          | Hold Time (Repeated) Start<br>Condition                                        | From SDA falling edge<br>crossing Low threshold to<br>SCL falling edge crossing<br>High threshold                                   | 0.26 | _   | I   | μs   |  |  |

| t <sub>LOW</sub>                                                                             | SCL Low Period                                                                 | Time measured during the<br>Low voltage threshold                                                                                   | 0.5  | _   | _   | μs   |  |  |

| thigh                                                                                        | SCL High Period                                                                | Time measured during the High voltage threshold                                                                                     | 0.26 | _   |     | μs   |  |  |

| thd;dat                                                                                      | Input Data Hold Time                                                           | From SCL falling edge<br>crossing Low threshold to<br>SDA entering the Low-High<br>window                                           | 0    | _   | 1   | μs   |  |  |

| tsu;dat                                                                                      | Input Data Setup Time                                                          | From SDA exiting the Low-<br>High window to SCL rising<br>edge crossing Low threshold                                               | 50   | _   | _   | ns   |  |  |

| tsu;sто                                                                                      | Setup Time for Stop Condition                                                  | From SCL rising edge<br>crossing High threshold to<br>SDA rising edge crossing Low<br>threshold                                     | 0.26 | _   | _   | μs   |  |  |

| tBUF                                                                                         | Bus-Free Time Between Stop and Start                                           | From SDA crossing High<br>threshold during STOP<br>condition to SDA crossing<br>High threshold for the<br>following START condition | 0.5  | _   | _   | μs   |  |  |

| t <sub>SP</sub>                                                                              | Maximum Pulse Width of Spike That<br>Must be Suppressed by the Input<br>Filter | Any pulse width narrower than the maximum specification is suppressed                                                               | _    | 50  | _   | ns   |  |  |

| Св                                                                                           | Capacitive Load for Each Bus Line                                              | Total on-chip and off-chip capacitance                                                                                              | _    | _   | 550 | pF   |  |  |

Note: 8. All min/max parameters compliance to the datasheet limits are assured by one or more methods: production test, characterization, and/or design.

## **Electrical Characteristics** (continued)

| I <sup>2</sup> C – Compatik | ole Interface Timing (High-Speed Mode,                                                 | C <sub>B</sub> = 100pF) (Note 8)                                                                                                    |     |     |     |      |

|-----------------------------|----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| Symbol                      | Parameter                                                                              | Test Conditions                                                                                                                     | Min | Тур | Max | Unit |

| f <sub>SCL</sub>            | Clock Frequency                                                                        | _                                                                                                                                   |     | _   | 3.4 | MHz  |

| tsu;sta                     | Setup Time (Repeated) Start<br>Condition                                               | SCL rising edge to SDA<br>falling edge; Both crossing<br>High threshold                                                             | 160 | _   | _   | ns   |

| thd;sta                     | Hold Time (Repeated) Start<br>Condition                                                | From SDA falling edge<br>crossing Low threshold to<br>SCL falling edge crossing<br>High threshold                                   | 160 | _   | _   | ns   |

| t <sub>LOW</sub>            | SCL Low Period                                                                         | Time measured during the Low voltage threshold                                                                                      | 160 | _   | _   | ns   |

| thigh                       | SCL High Period                                                                        | Time measured during the High voltage threshold                                                                                     | 60  | _   | _   | ns   |

| thd;dat                     | Input Data Hold Time                                                                   | From SCL falling edge<br>crossing Low threshold to<br>SDA entering the Low-High<br>window                                           |     | 35  | _   | ns   |

| tsu;dat                     | Input Data Setup Time                                                                  | From SDA exiting the Low-<br>High window to SCL rising<br>edge crossing Low threshold                                               | 10  | _   | _   | ns   |

| tsu;sto                     | Setup Time for Stop Condition                                                          | From SCL rising edge<br>crossing High threshold to<br>SDA rising edge crossing Low<br>threshold                                     | 160 | _   | _   | ns   |

| trcl                        | SCL Rise time                                                                          | _                                                                                                                                   | 10  | _   | 40  | ns   |

| trcL1                       | Rise Time of SCL Signal after<br>REPEATED START Condition and<br>after Acknowledge Bit | _                                                                                                                                   | 10  | _   | 80  | ns   |

| tFCL                        | SCL Fall Time                                                                          | _                                                                                                                                   | 10  | _   | 40  | ns   |

| trda                        | SDA Rise Time                                                                          | _                                                                                                                                   | 1   | _   | 80  | ns   |

| tfdA                        | SDA Fall Time                                                                          |                                                                                                                                     |     | _   | 80  | ns   |

| tbur                        | Bus-Free Time Between Stop and Start                                                   | From SDA crossing High<br>threshold during STOP<br>condition to SDA crossing<br>High threshold for the<br>following START condition | _   | 10  | _   | ns   |

| t <sub>SP</sub>             | Maximum Pulse Width of Spike That<br>Must be Suppressed by the Input<br>Filter         | Any pulse width narrower than the maximum specification is suppressed                                                               | _   | 10  | _   | ns   |

| Св                          | Capacitive Load for Each Bus Line                                                      | Total on-chip and off-chip                                                                                                          | _   | _   | 100 | pF   |

Note: 8. All min/max parameters compliance to the datasheet limits are assured by one or more methods: production test, characterization, and/or design.

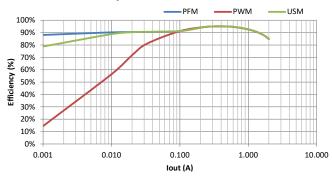

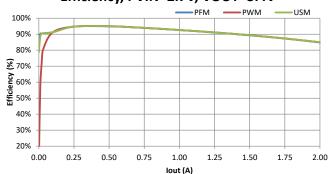

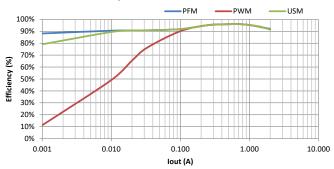

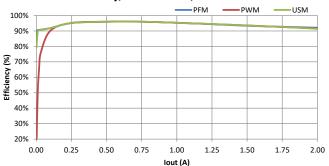

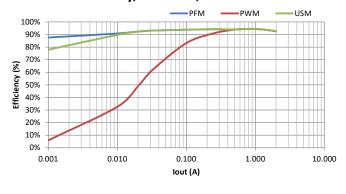

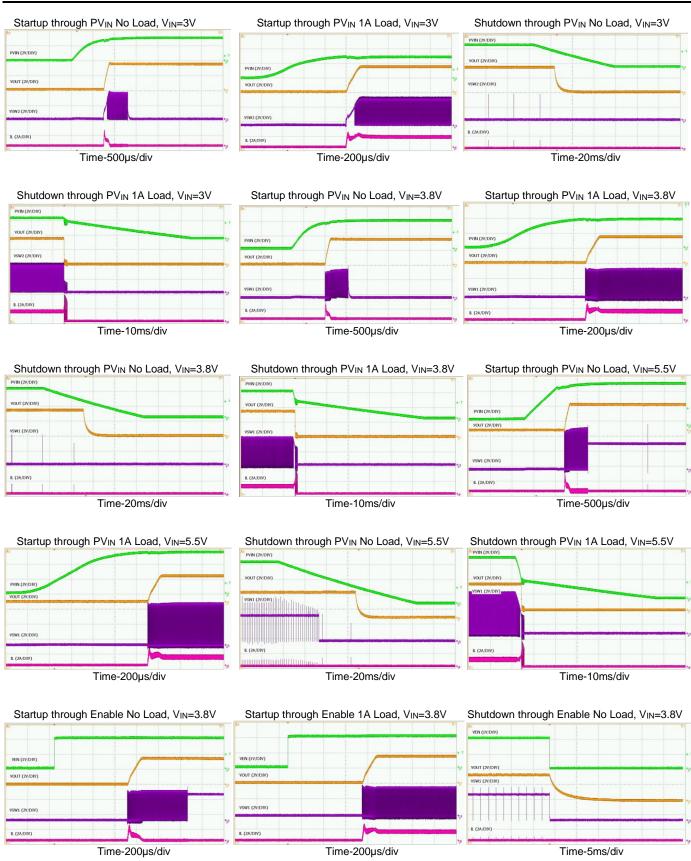

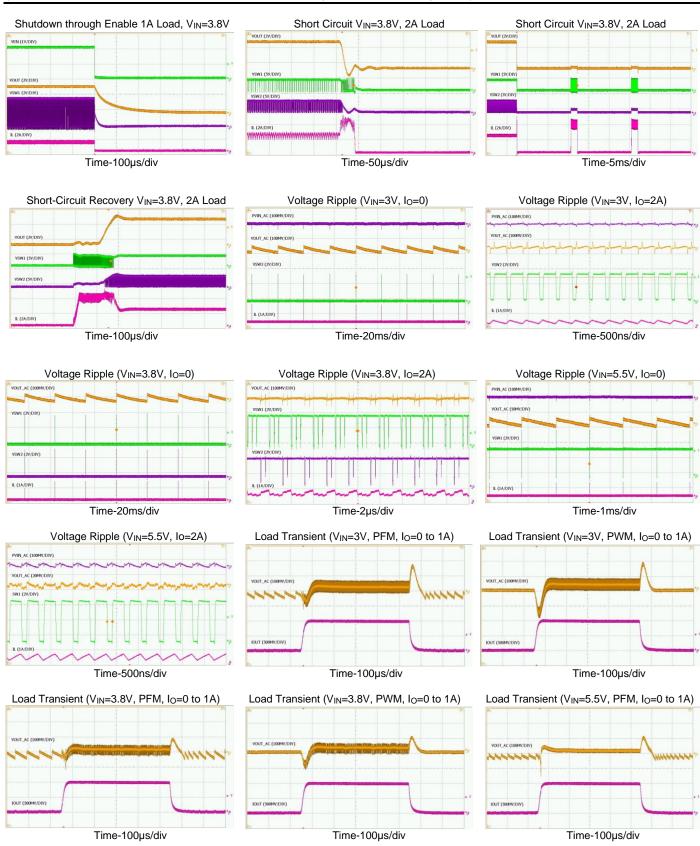

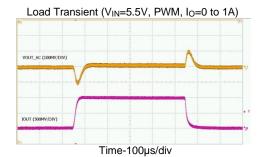

### **Typical Performance Characteristics**

(@T<sub>A</sub> = +25°C, PV<sub>IN</sub> = V<sub>IN</sub> = V<sub>IO</sub> = 2.3V to 5.5V, V<sub>OUT</sub> = 3.4V, L = 1 $\mu$ H, unless otherwise specified.)

### Efficiency, PVIN=2.7V, VOUT=3.4V

### Efficiency, PVIN=2.7V, VOUT=3.4V

### Efficiency, PVIN=3.3V, VOUT=3.4V

### Efficiency, PVIN=3.3V, VOUT=3.4V

### Efficiency, PVIN=5V, VOUT=3.4V

## Efficiency, PVIN=5V, VOUT=3.4V

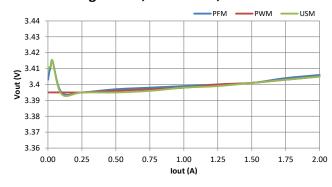

### Load Regulation, PVIN=2.7V, VOUT=3.4V

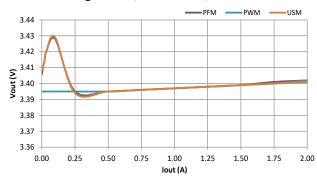

### Load Regulation, PVIN=3.3V, VOUT=3.4V

(@T<sub>A</sub> = +25°C, PV<sub>IN</sub> = V<sub>IN</sub> = V<sub>IO</sub> = 2.3V to 5.5V, V<sub>OUT</sub> = 3.4V, L = 1 $\mu$ H, unless otherwise specified.)

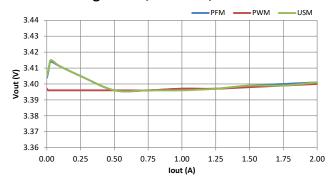

#### Load Regulation, PVIN=5V, VOUT=3.4V

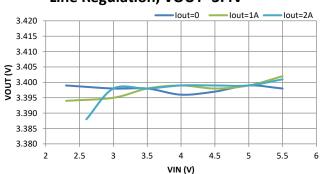

### Line Regulation, VOUT=3.4V

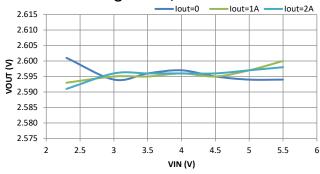

### Line Regulation, VOUT=2.6V

### Line Regulation, VOUT=5.14V

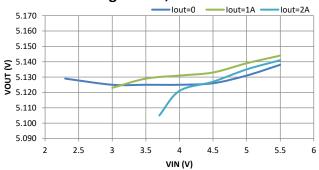

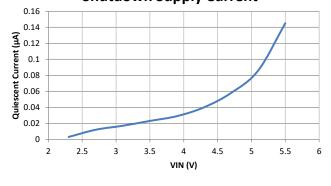

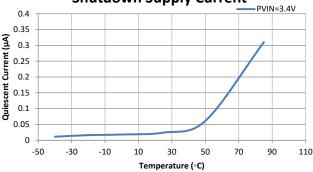

### **Shutdown Supply Current**

**Shutdown Supply Current**

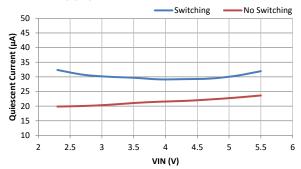

## Supply Current (Quiescent), PFM

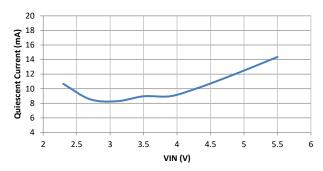

### Supply Current (Quiescent), PWM

(@T<sub>A</sub> = +25°C, PV<sub>IN</sub> = V<sub>IN</sub> = V<sub>IO</sub> = 2.3V to 5.5V, V<sub>OUT</sub> = 3.4V, L = 1 $\mu$ H, unless otherwise specified.)

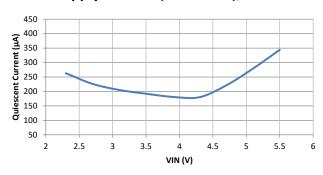

### Supply Current (Quiescent), USM

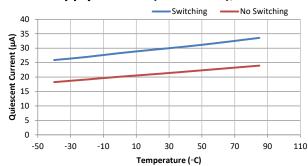

### Supply Current (Quiescent), PFM

## Supply Current (Quiescent), PWM

## Supply Current (Quiescent), USM

## Oscillator Frequency, Vout=3.4V

### Oscillator Frequency, Vout=3.4V, USM

$(@T_A = +25^{\circ}C, PV_{IN} = V_{IN} = V_{IO} = 2.3V \text{ to } 5.5V, V_{OUT} = 3.4V, L = 1 \mu H, unless otherwise specified.)$

(@ $T_A$  = +25°C, PV<sub>IN</sub> = V<sub>IN</sub> = V<sub>IO</sub> = 2.3V to 5.5V, V<sub>OUT</sub> = 3.4V, L = 1 $\mu$ H, unless otherwise specified.)

Typical Performance Characteristics (continued) (@T<sub>A</sub> = +25°C, PV<sub>IN</sub> = V<sub>IN</sub> = V<sub>IO</sub> = 2.3V to 5.5V, V<sub>OUT</sub> = 3.4V, L = 1 $\mu$ H, unless otherwise specified.)

May 2024

### **Application Information**

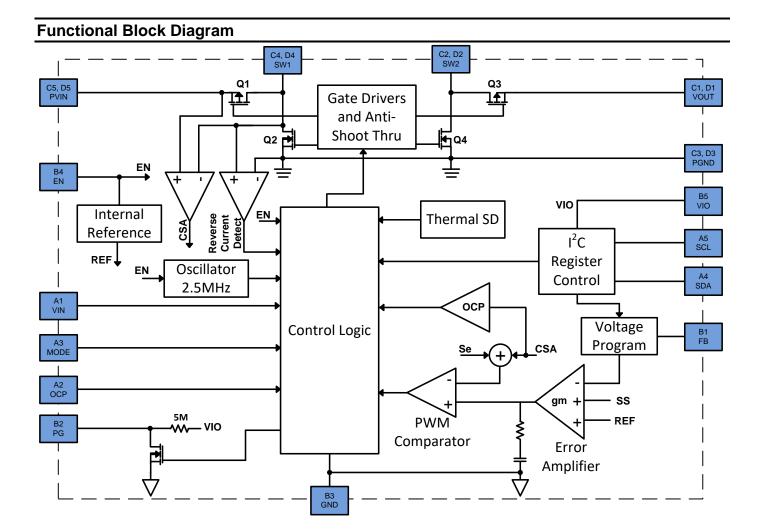

#### **Buck-Boost Power Conversion**

When the EN pin goes high, the AP72202 turns on the internal logic circuitries. Once VIN is supplied, then all user registers are accessible through I<sup>2</sup>C. When EN is pulled low, the AP72202 enters shutdown mode. This event resets all registers to their default values. The AP72202 can operate in either buck or boost mode. Refer to the Functional Block Diagram. When the input voltage PVIN is less than output VOUT, Q1 will be on continuously while Q2 remains off. Q3 and Q4 switch to boost the output up. When the input voltage PVIN is more than output VOUT, Q3 will be on continuously while Q4 remains off. Q1 and Q2 switch to buck the output down. In the event when operating in conditions where PVIN is close to VOUT, the AP72202 alternates between buck and boost mode as necessary to provide a regulated output voltage.

#### **Regulator Enable Control**

Buck-boost has an enable pin EN as well as I<sup>2</sup>C enable bit. As shown in the table 1 below, the AP72202 turns on the internal bias circuitry when EN pin goes high. Once VIO is supplied, all the user registers are accessible through I<sup>2</sup>C. The address register 0x03 bit 6 is the BB\_EN. Change this bit to 0 will disable the output voltage, while the internal logic circuitries are still active. Pulling EN low will turn off the AP72202 and reset all the registers to their POR default values.

| EN   | BB_EN BIT   | Operating Condition |

|------|-------------|---------------------|

| LOW  | Х           | Device OFF          |

| HIGH | 0           | Disable Output      |

| HIGH | 1 (Default) | Enable Output       |

Table 1. Enable Control Logic Truth Table

#### **H-Bridge Controller**

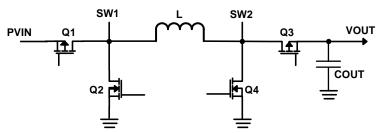

H-bridge architecture operates at 2.5MHz fixed frequency with a pulse-width modulated (PWM), current-mode control scheme. This topology is in a cascade of a boost regulator and a buck regulator using a single inductor and output capacitor. Buck, buck-boost, and boost stages are 100% synchronous for highest efficiency in portable applications. Figure 2 shows a simplified diagram of the internal switches, external inductor, and output capacitor.

Figure 2. Buck-Boost Diagram

In buck PWM, Switch Q3 is continuously closed and Switch Q4 is continuously open. Switches Q1 and Q2 operate as a synchronous buck converter when in this condition. In boost PWM, Switch Q1 remains closed and Switch Q2 remains open. Switches Q3 and Q4 operate as a synchronous boost converter when in this operation. When the input voltage is dropping close to the output voltage such that the duty cycle seen at SW1 is more than 90%, then the regulator will switch from buck to buck-boost (where cycles will alternate between buck and boost). The AP72202 will rapidly and smoothly switch from boost-to-buck mode as needed to maintain the regulated output voltage. As the input voltage continues to drop such that the duty cycle in boost mode is more than 10% seen at SW2, then the regulator switches to all boost operation. This behavior provides excellent efficiency and very low output-voltage ripple.

#### H-Bridge Controller (continued)

The regulator enters PFM as the output load decreases when the valley of the inductor current is less than 0. The zero cross detection will be activated after 40µs delay before switching the mode from PWM to PFM. During PFM operation in buck mode, Switch Q3 is closed and Switch Q4 is open. Switches Q1 and Q2 operate in discontinuous mode during PFM operation until output voltage is approximately 1.2% upper threshold of the PFM hysteretic controller. Then all switches are open to allow VOUT to decay until it reaches nominal regulation before switching again. This operation will reduce switching losses at light load, thus improving efficiency. Likewise, the AP72202 closes Switch Q1 and Switch Q4 to ramp up the current in the inductor during PFM operation in boost mode. When the inductor current reaches 1A, the device turns OFF Switch Q4, then turns ON Switch Q3. With Switch Q3 closed, output voltage increases as the inductor current ramps down. When the loading current gets higher, there will be multiple PFM pulses to charge up the output capacitor. These pulses continue until VOUT has achieved the 1.2% upper threshold of the PFM hysteretic controller. Switching action then stops until VOUT decays until it reaches normal regulation before switching again. The regulator resumes normal PWM operation as the output load increases and VOUT drops 2% below the regulation point.

#### **Regulator MODE Control**

The AP72202 has a MODE pin as well as I<sup>2</sup>C enable bit. Connecting MODE pin low sets the regulator to operate in PFM. Tying the MODE to VIN sets the device in PWM. The MODE pin condition is set during the POR operation of the regulator and can only be overridden by the I<sup>2</sup>C. In the address number 0x02, bit 6 and bit 0 are BB\_UMODE and BB\_FPWM respectively. These two bits can set the mode of operation of PFM, enhanced ultrasonic, or forced PWM.

When the enhanced ultrasonic is set, this activates a unique pulse-skipping mode with a minimum switching frequency of 20kHz. An ultrasonic pulse occurs when the regulator detects that no switching has occurred after 37µs. Once triggered, the ultrasonic pulse turns on the switch Q2 (buck mode) or Q3 (boost mode) for approximately 50ns to induce a negative inductor current. This process continues until FB drops to the regulation point. Then the regulator waits for the next clock edge to initiate the ON time. The table below is the truth table for the MODE operation found in I<sup>2</sup>C address 0x02.

| BIT6 | BIT0 | Operating Mode  |

|------|------|-----------------|

| 0    | 0    | PFM             |

| 1    | 0    | Ultrasonic Mode |

| х    | 1    | PWM             |

Table 2. MODE Control Table

#### Power-Good (PG) Indicator

Buck-boost has an open-drain output that is actively held low during soft-start period until the output voltage reaches 80%. When the output voltage is outside of its regulation by -20%, the PG will pull low until the output returns to set value. The PG low to high transition is delayed by 1.5ms while the falling edge PG is delayed by 3µs to prevent false triggering. The polarity of PG output is programmable thru I<sup>2</sup>C in address 0x03 bit 4. It is active high by default.

#### Overcurrent Protection

The AP72202 has an OCP pin as well as I<sup>2</sup>C enable bit to adjust the threshold 2.5A or 4.4A. The OCP pin control setting is the condition upon POR operation of the regulator and can only be overridden by the I<sup>2</sup>C. The AP72202 detects the current limit on the high side, Q1, to protect the device against overload or short-circuit conditions. The peak current in the switch is monitored cycle by cycle with comparator delay approximately 100ns to guard against noise glitches. If the high side Q1 current limit is reached, the high side Q1 is turned off and the low side Q2 is turned on until the switch current decreases below OC threshold. The frequency is reduced in order to protect the device from damage. The Q1 peak current limit remains active during this state. After 17 consecutive cycles in OCP event, the regulator enters hiccup mode where all power FETs are turned off and wait for 15ms before attempt to restart.

#### **Reverse Current Protection**

During fixed-frequency operation, a reverse current comparator on switch Q2 monitors the current entering VOUT. When this current exceeds 2A (typical), switch Q2 will be turned off for the remainder of the switching cycle. This feature protects the buck-boost converter from excessive reverse current if the buck-boost output is held above the regulation voltage by an external source.

#### **Undervoltage Lockout**

The undervoltage lockout (UVLO) feature prevents abnormal operation in the event that the supply voltage is too low to guarantee proper operation. When the VIN voltage falls below the UVLO threshold, the regulator is disabled.

#### **Thermal Shutdown**

A built-in thermal protection feature protects the AP72202 if the die temperature reaches +150°C (typical). At this die temperature, the regulator is completely shut down. The die temperature continues to be monitored in this thermal-shutdown mode. When the die temperature falls to +135°C (typical), the device will resume normal operation. When exiting thermal shutdown, the AP72202 will execute its soft-start sequence.

#### **Output Voltage Slew-Rate Control**

Buck-boost regulator supports programmable slew-rate control feature when increasing and decreasing the output voltage. The ramp-up slew-rate can be set to 20mV/µs or 40mV/µs through BB\_RU\_SR bit, while the ramp-down slew-rate is programmable to 5mV/µs or 10mV/µs through BB\_RD\_SR bit in I<sup>2</sup>C address 0x02.

#### **Output Active Discharge**

The AP72202 provides an internal 100Ω resistor for output active discharge function. If the active discharge function is enabled (BB\_AD = 1 in I<sup>2</sup>C address 0x02), the internal resistor discharges the energy stored in the output capacitor to PGND whenever the regulator is disabled. Either the regulator remains enabled or the active discharge function is disabled (BB\_AD = 0), the internal resistor is disconnected from the output. If the active discharge function is disabled, the output voltage decays at a rate that is determined by the output capacitance and the load current when the regulator is turned off.

#### **Inductor Selection**

An inductor with high frequency core material (e.g., ferrite core) should be used to minimize core losses and provide good efficiency. The inductor must be able to handle the peak switching currents without saturating. A 1µH inductor with ≥ 4.4A saturation current rating is recommended. Select an inductor with low DCR to provide good efficiency. In applications where radiated noise must be minimized, a toroidal or shielded inductor can be used.

#### **PVIN and VOUT Capacitor Selection**

The input and output capacitors should be ceramic X5R type with low ESL and ESR. The recommended input capacitor value is 22µF, as this would provide adequate RMS current to minimize the input voltage ripple. A minimum of 10µF is required to maintain full functionality of the part. The recommended output capacitor is 2x22µF, 10V, X5R. Note that the effective value of a ceramic capacitor derates with DC voltage bias across it. This derating may be up to 70% of the rated capacitance. Refer to the capacitor datasheet to ensure the combined effective output capacitance is at least 30µF for proper operation over the entire recommended load current range. Low output capacitance may lead to large output-voltage drop during load transient or unstable operation.

17 of 30 May 2024 Document number: DS46304 Rev. 1 - 2 www.diodes.com © 2024 Copyright Diodes Incorporated. All Rights Reserved.

#### **Serial Interface**

The  $I^2C$  compatible 2-wire serial interface is used for regulator on/off control, setting output voltages, and other functions. See the *Register Map* section for details. The  $I^2C$  interface is an open-drain serial bus that consists of a bidirectional serial data line (SDA) and a serial clock line (SCL). Pullup resistors of  $500\Omega$  each or greater must be added from VIO to SDA and VIO to SCL. Optional  $24\Omega$  resistors in series with SDA and SCL help to protect the device inputs from high voltage spikes on the bus lines. Series resistors also minimize crosstalk and undershoot on bus lines.

**System Configuration** SDA SCL MASTER MASTER SI AVE SLAVE SLAVE TRANSMITTER/ TRANSMITTER/ TRANSMITTER/ RECEIVER TRANSMITTER RECEIVER RECEIVER RECEIVER

Figure 3. Functional Logic Diagram for Communications Controller

The I<sup>2</sup>C bus is a multi-master bus. The maximum number of devices that can attach to the bus is limited by bus capacitance. The figure above shows an example of a typical I<sup>2</sup>C system. A device on the I<sup>2</sup>C bus that sends data to the bus is called a transmitter. A device that receives data from the bus is called a receiver. The device that initiates a data transfer and generates the SCL clock signal to control the data transfer is the master. Any device on the bus that can be addressed by the master is considered a slave. When the AP72202 I<sup>2</sup>C compatible interface is operating, it is a slave on I<sup>2</sup>C bus.

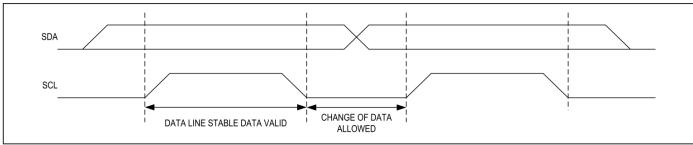

#### **Bit Transfer**

One data bit is transferred for each SCL clock cycle. The data on SDA must remain stable during the high portion of SCL clock pulse. Changes in SDA while SCL is high are control signals (START and STOP conditions).

Figure 4. I<sup>2</sup>C Bit Transfer

#### START and STOP Conditions

When the I<sup>2</sup>C serial interface is inactive, SDA and SCL are pulled high. A master device initiates communication by issuing a START (S) condition. A START condition is a high-to-low transition on SDA while SCL is high. A STOP (P) condition is a low-to-high transition on SDA while SCL is high. A START condition from the master signals the AP72202 that a transmission is about to begin. The master terminates transmission and frees the bus by issuing a STOP condition. To issue a series of commands to the slave, the master may issue REPEATED START (Sr) conditions instead of a STOP condition in order to maintain control of the bus. In general, a REPEATED START condition is functionally equivalent to a regular START condition. The AP72202 will listen for its address after a START condition is detected. If its address is not detected, it will stay idle until the next START condition is detected.

Figure 5. Start and Stop Conditions

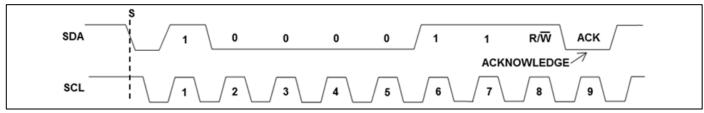

#### Acknowledge

Both I<sup>2</sup>C bus master and AP72202 (slave) generate ACKNOWLEDGE (ACK) bits when receiving data. The ACK bit is the last bit of each nine bit data packet. To generate an ACK bit, the receiving device must pull SDA low before the rising edge of the ACK-related clock pulse (ninth SCL pulse) and keep it low during the high period of the clock pulse. To generate a NOT ACKNOWLEDGE (nACK), the receiving device allows SDA to be pulled high before the rising edge of the ACK-related clock pulse and leaves it high during the high period of the clock pulse. Monitoring the ACK bits allows for detection of unsuccessful data transfers. An unsuccessful data transfer occurs if a receiving device is busy or if a system fault has occurred. In the event of an unsuccessful data transfer, the bus master should reattempt communication at a later time.

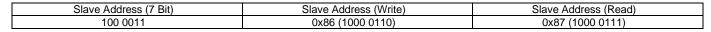

#### Slave Address

The I<sup>2</sup>C slave address of the AP72202 is shown in table below:

Figure 6. Slave Address Byte Example

#### **Clock Stretching**

In general, the clock signal generation for the I<sup>2</sup>C bus is the responsibility of the master device. I<sup>2</sup>C specification allows slow slave devices to alter the clock signal by holding down the clock line. The process in which a slave device holds down the clock line is typically called clock stretching. The AP72202 does not use any form of clock stretching to hold down the clock line.

#### **General Call Address**

The AP72202 does not implement the I<sup>2</sup>C specification called general call address. If the AP72202 sees a general call address (00000000b), it does not issue an ACKNOWLEDGE.

#### **Communication Speed**

The AP72202 provides  $I^2C$  3.0-compatible serial interface.

- I<sup>2</sup>C revision 3-compatible serial communications channel

- 0 to 100kHz (Standard-mode)

- 0 to 400kHz (Fast-mode)

- 0 to 1MHz (Fast-mode Plus)

- 0 to 3.4MHz (High-Speed mode)

- Does not utilize I<sup>2</sup>C clock stretching

Operating in Standard-mode, Fast-mode, or Fast-mode Plus does not require any special protocols. The main consideration when changing the bus speed through this range is the combination of the bus capacitance and pullup resistors. Higher time constants created by the bus capacitance and pullup resistance (C x R) slow the bus operation. Therefore, when increasing bus speeds, the pullup resistance must be decreased to maintain a reasonable time constant. Refer to the Pullup Resistor Sizing section of  $I^2C$  revision 3.0 specification for detailed guidance on the pullup resistor selection. In general, for bus capacitances of 200pF, a 100kHz bus needs pullup resistors of  $5.6k\Omega$ , a 400kHz bus needs about a  $1.5k\Omega$  pullup resistors, and a 1MHz bus needs  $680\Omega$  pullup resistors. Note that the pullup resistor is dissipating power when the open-drain bus is low. Lower values of the pullup resistors result in higher power dissipation ( $V^2/R$ ).

Operating in High-Speed (HS) mode requires some special considerations. For the full list of considerations, refer to the  $I^2C$  3.0 specification. The major considerations with respect to the AP72202 are:

- The I<sup>2</sup>C bus master uses current source pullups to shorten the signal rise times.

- The I<sup>2</sup>C slave must use a different set of input filters on its SDA and SCL lines to accommodate for the higher bus speed.

- The communication protocols need to utilize the High-Speed master code.

At power-up or after each STOP condition, the AP72202 inputs filters are set for Standard-mode, Fast-mode, or Fast-mode Plus (i.e. 0 to 1MHz). Use the High-Speed master code protocols that are described in *Communication Protocols* section to switch the input filters for High-Speed mode.

#### **Communication Protocols**

The AP72202 supports both writing and reading from its registers. The following sections show the I<sup>2</sup>C communication protocols.

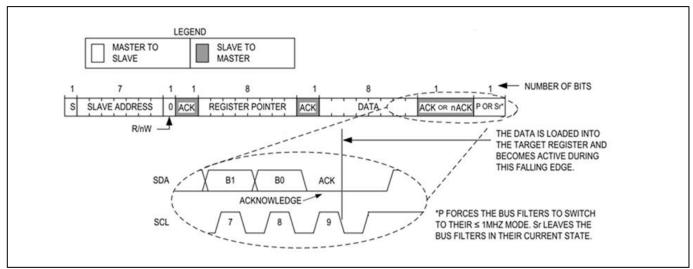

#### Writing to a Single Register

Figure 7 below shows the protocol for I<sup>2</sup>C master device to write one byte of data to the AP72202 the write byte protocol is as follows:

- 1. The master sends a START condition.

- 2. The master sends the 7-bit slave address followed by a write bit (R/nW = 0).

- 3. The addressed slave sends an ACK bit by pulling SDA low.

- 4. The master sends an 8-bit register pointer.

- 5. The slave acknowledges the register pointer.

- 6. The master sends a data byte.

- 7. The slave acknowledges the data byte.

- 8. The next falling edge of SCL loads the data byte into its target register and the data becomes active.

- 9. The master sends a STOP condition or a REPEATED START condition.

Figure 7. Writing to a Single Register with Write Byte Protocol

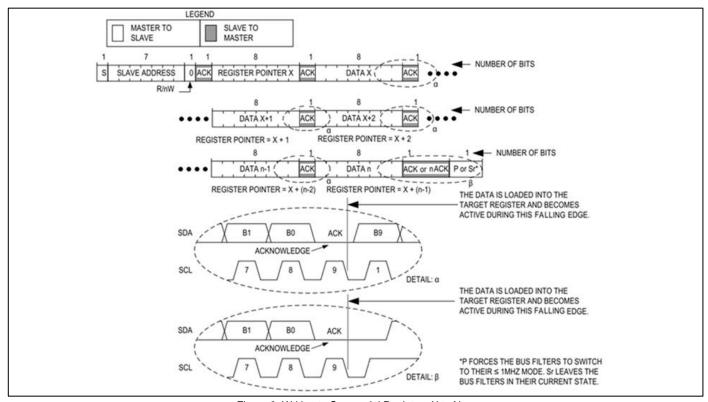

#### Writing to a Sequential Register

Figure 8 below shows the protocol for writing to sequential registers. This protocol is similar to the write byte protocol, except the master continues to write additional data after is receives an ACK from the slave that it successfully received the previous data byte. The slave's register pointer will auto-increment by one after each byte received. When the master is done writing, it issues a STOP or REPEATED START. The writing to sequential registers protocol is as follows:

- 1. The master sends a START condition.

- 2. The master sends the 7-bit slave address followed by a write bit (R/nW = 0).

- 3. The addressed slave sends an ACK bit by pulling SDA low.

- 4. The master sends an 8-bit register pointer.

- 5. The slave acknowledges the register pointer.

- 6. The master sends a data byte.

- 7. The slave acknowledges the data byte.

- 8. The next falling edge on SCL loads the data byte into its target register and the data becomes active.

- 9. Steps 6 to 8 are repeated as many times as the master requires.

- 10. The master sends a STOP condition or a REPEATED START condition.

Figure 8. Writing to Sequential Registers X to N

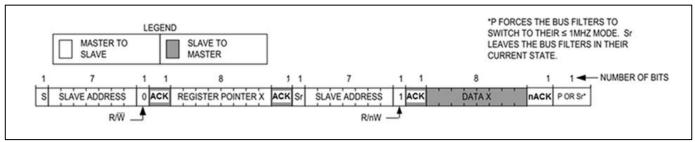

#### Reading from a Single Register

The I<sup>2</sup>C master device reads one byte of data from AP72202. The read byte protocol is as follows:

- 1. The master sends a START condition.

- 2. The master sends the 7-bit slave address followed by a write bit (R/nW = 0).

- 3. The addressed slave sends an ACK bit by pulling SDA low.

- 4. The master sends an 8-bit register pointer.

- 5. The slave acknowledges the register pointer.

- 6. The master sends a REPEATED START condition.

- The master sends the 7-bit slave address followed by a read bit (R/nW = 1).

- 8. The addressed slave sends an ACK bit by pulling SDA low.

- 9. The addressed slave places 8 bits of data on the bus from the register specified by the register pointer.

- 10. The master issues a nACK.

- 11. The master sends a STOP condition or a REPEATED START condition.

Figure 9. Reading from a Single Register X

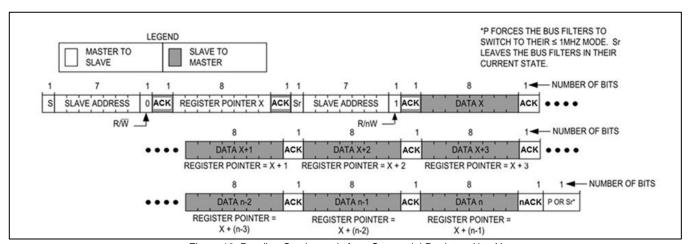

#### Reading from a Sequential Register

Figure 10 below shows the protocol for reading from sequential registers. This protocol is similar to the read byte protocol except the master issues an ACK to signal the slave that it wants more data. The slave's register pointer will auto-increment by one after each byte sent. When the master has all the data it requires, it issues a nACK and a STOP to end the transmission. The continuous read from sequential registers protocol is as follows:

- The master sends a START condition.

- 2. The master sends the 7-bit slave address followed by a write bit (R/nW = 0).

- The addressed slave sends an ACK bit pulling SDA low.

- 4. The master sends an 8-bit register pointer.

- 5. The slave acknowledges the register pointer.

- 6. The master sends a REPEATED START condition.

- 7. The master sends the 7-bit slave address followed by a read bit (R/nW = 1).

- 8. The addressed slave sends an ACK bit by pulling SDA low.

- 9. The addressed slave places 8-bits of data on the bus from the register specified by the register pointer.

- 10. The master issues an ACK signaling the slave that it wishes to receive more data.

- 11. Steps 9 to 10 are repeated as many times as the master requires.

- 12. Following the last byte of data, the master must issue a nACK to signal that it wishes to stop receiving data.

- 13. The master sends a STOP condition or a REPEATED START condition.

Figure 10. Reading Continuously from Sequential Registers  $\boldsymbol{X}$  to  $\boldsymbol{N}$

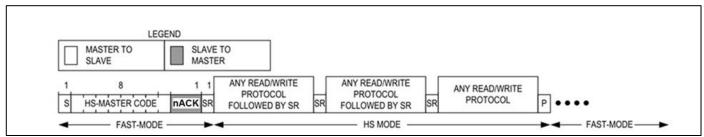

#### Engaging HS Mode for Operation Up to 3.4MHz

Figure 11 below shows the protocol for engaging HS mode operation. HS mode operation allows for a bus operating speed of up to 3.4MHz. The protocol to engage HS mode is as follows:

- 1. Begin the protocol while operating at a bus speed of 1MHz or lower.

- 2. The master sends a START condition.

- 3. The master sends the 8-bit master code of 00001xxxb where xxxb are don't care bits.

- 4. The master code is not acknowledged.

- 4. The master switches to High-Speed communication and can now increase its bus speed up to 3.4MHZ.

- 5. The master sends a REPEATED START condition.

- 6. The master issues any read/write operation in the known manner.

The master may continue to issue High-Speed read/write operations until a STOP is issued. Issuing a STOP ensures that the bus input filters are set for 1MHz or slower operation. Repeat steps 1 to 6 in the above algorithm to re-enter HS mode after a STOP has been issued.

Figure 11. Engaging HS Mode

AP72202 23 of 30

Document number: DS46304 Rev. 1 - 2 **www.diodes.com**

### Registers

Register reset conditions – Registers are reset when VIN = Iow or EN = Iow.

Register Map - I<sup>2</sup>C Slave Address (W/R): 0x86/0x87 (default)

| rtogiotor ivi |                  |               | ( 1 1 , 1 1 , 1 | ONCOF CHOI |                  |          |          |       |          |             |          |                |

|---------------|------------------|---------------|-----------------|------------|------------------|----------|----------|-------|----------|-------------|----------|----------------|

| ADDRESS       | REGISTER<br>NAME | RESET<br>TYPE | R/W             | BIT 7      | BIT6             | BIT5     | BIT4     | BIT3  | BIT2     | BIT1        | віто     | RESET<br>VALUE |

| 0x00          | DEVICE_ID        | TYPE_O        | R               | RESERVED   |                  | VERSIO   | N [3:0]  |       | С        | HIP_REV [2: | 0]       | -              |

| 0x01          | STATUS           | TYPE_O        | R               | RESERVED   | RESERVED         | RESERVED | RESERVED | TSHDN | BB_PGn   | BB_OVP      | BB_OCP   | -              |

| 0x02          | CONFIG1          | TYPE_O        | R/W             | RESERVED   | BB_UMODE         | BB_RU_SR | BB_RD_SR | BB_O\ | /P [1:0] | BB_AD       | BB_FPWM  | 0x0E /<br>0x0F |

| 0x03          | CONFIG2          | TYPE_O        | R/W             | RESERVED   | BB_EN            | EN_PD    | PG_POL   | ОСР   | RESERVED | RESERVED    | RESERVED | 0x70 /<br>0x78 |

| 0x04          | VOUT             | TYPE_O        | R/W             | RESERVED   | ERVED VOUT[ 6:0] |          |          |       |          | 0x28        |          |                |

Device ID Register

| ADDRESS | MOD            | ÞΕ  | TYPE: O                                                                                                                                       | RESET VALUE: N/A |

|---------|----------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 0x00    | R              |     | TIPL. O                                                                                                                                       | RESET VALUE. N/A |

| BIT     | NAME           | POR |                                                                                                                                               | DESCRIPTION      |

| 7       | RESERVE        | 0   |                                                                                                                                               | DESCRIPTION      |

| 6:3     | VERSION [3:0]  | -   | Version<br>0000b: Plain<br>0001b: -1Z<br>0010b: -2Z                                                                                           |                  |

| 2:0     | CHIP_REV [2:0] | -   | Chip Revision History<br>000b: Pass1<br>001b: Pass2<br>010b: Pass3<br>011b: Pass4<br>100b: Pass5<br>101b: Pass6<br>110b: Pass7<br>111b: Pass8 |                  |

Status Register

| MODE            |                                    | TVDE: O                                             | RESET VALUE: N/A                                                                                                                                              |  |

|-----------------|------------------------------------|-----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| R               |                                    | TYPE. U                                             |                                                                                                                                                               |  |

| NAME            | POR                                | DESCRIPTION                                         |                                                                                                                                                               |  |

| RESERVE         | -                                  |                                                     |                                                                                                                                                               |  |

| I 3 I TCHON I - |                                    | 0: Junction Temperature ≤ 150°C                     |                                                                                                                                                               |  |

|                 |                                    | 1: Junction Temperature ≥ 150°C                     |                                                                                                                                                               |  |

| BB_PGn          | -                                  | Buck-boost PG Status                                |                                                                                                                                                               |  |

| BB_OVP          | -                                  | Buck-boost OVP Status                               |                                                                                                                                                               |  |

| BB_OCP          | -                                  | Buck-boost OCP Status                               |                                                                                                                                                               |  |

|                 | R NAME RESERVE TSHDN BB_PGn BB_OVP | R  NAME POR  RESERVE -  TSHDN -  BB_PGn -  BB_OVP - | R  NAME POR  RESERVE -  TSHDN - 0: Junction Temperatu 1: Junction Temperatu 1: Junction Temperatu BB_PGn - Buck-boost PG Status BB_OVP - Buck-boost OVP Statu |  |

The status register BIT are reset automatically upon fault removal.

### Configuration Register 1

| ADDRESS   | MODE                        |                            | TYPE: O                    | RESET VALUE: 0x0E (MODE=0) or 0x0F (MODE=1)     |  |

|-----------|-----------------------------|----------------------------|----------------------------|-------------------------------------------------|--|

| 0x02      | R/W                         |                            | TIPE. U                    | RESET VALUE: 0x0E (IVIODE=0) OF 0x0F (IVIODE=1) |  |

| BIT       | NAME                        | POR                        |                            | DESCRIPTION                                     |  |

| 7         | RESERVE                     | 0                          | - DESCRIPTION              |                                                 |  |

|           |                             |                            | Ultrasonic Mode Enable     | 2                                               |  |

|           |                             |                            | 0: No Ultrasonic Mode      |                                                 |  |

| 6         | BB_UMODE                    | 0                          | 1: Ultrasonic Mode (Fs     | > 20kHz)                                        |  |

|           |                             |                            | Rising Ramp-rate Contr     | rol                                             |  |

| 5         | BB_RU_SR                    | 0                          | 0: 20mV/μs                 |                                                 |  |

|           |                             |                            | 1: 40mV/μs                 |                                                 |  |

|           |                             |                            | Ramp-down Slew Rate        | Control                                         |  |

| 4         | BB_RD_SR                    | 0                          | 0: 5mV/μs                  |                                                 |  |

|           |                             |                            | 1: 10mV/μs                 |                                                 |  |

|           |                             |                            | Output OVP Threshold       |                                                 |  |

|           |                             |                            | 00b: No OVP                |                                                 |  |

| 3:2       | 3:2 BB_OVP_TH [1:0] 11 01b: |                            | 01b: 110% of VOUT          |                                                 |  |

|           |                             |                            | 10b: 115% of VOUT          |                                                 |  |

|           |                             |                            | 11b: 120% of VOUT          |                                                 |  |

|           |                             |                            | Output Active Discharg     | e                                               |  |

| 1 BB_AD 1 |                             | 1                          | 0: Disable Acive Discharge |                                                 |  |

|           |                             | 1: Enable Active Discharge |                            |                                                 |  |

|           |                             | 0                          | PWM Enable                 |                                                 |  |

| 0         | BB_FPWM                     | or                         | 0: PFM<br>1: PWM           |                                                 |  |

|           |                             | 1                          |                            |                                                 |  |

### Configuration Register 2

| ADDRESS | MODE<br>R/W |     | TYPE: O                                                         | DECET VALUE: 0x70 (OCD=0) ox 0x70 (OCD=1) |

|---------|-------------|-----|-----------------------------------------------------------------|-------------------------------------------|

| 0x03    |             |     | TIPE. U                                                         | RESET VALUE: 0x70 (OCP=0) or 0x78 (OCP=1) |

| BIT     | NAME        | POR | DESCRIPTION                                                     |                                           |

| 7       | RESERVE     | 0   |                                                                 |                                           |

| 6       | BB_EN       | 1   | 0: Disable Buck-boost Output 1: Enable Buck-boost Output        |                                           |

| 5       | EN_PD       | 1   | EN Input Pull-down Resistor Enable Setting 0: Disable 1: Enable |                                           |

| 4       | PG_POL      | 1   | 0: Active Low<br>1: Active High                                 |                                           |

| 3       | ОСР         | 1   | Set the Peak Overcurrent Threshold 0: 2.5A 1: 4.4A              |                                           |

| 2:0     | RESERVE     | 000 |                                                                 |                                           |

Output Voltage Setting Register

| ADDRESS | S MODE     |          | TVDF. O                   | TVDE: O DESET VALUE: 0v29 |              |              |

|---------|------------|----------|---------------------------|---------------------------|--------------|--------------|

| 0x04    | R/W        | I        | TYPE: O RESET VALUE: 0x28 |                           | E: UX 28     |              |

| BIT     | NAME       | POR      | DESCRIPTION               |                           |              |              |

| 7       | RESERVE    | 0        |                           |                           | DESCRIPTION  |              |

|         |            |          | 0x00 = 2.60V              | 0x20 = 3.24V              | 0x40 = 3.88V | 0x60 = 4.52V |

|         |            |          | 0x01 = 2.62V              | 0x21 = 3.26V              | 0x41 = 3.90V | 0x61 = 4.54V |

|         |            |          | 0x02 = 2.64V              | 0x22 = 3.28V              | 0x42 = 3.92V | 0x62 = 4.56V |

|         |            |          | 0x03 = 2.66V              | 0x23 = 3.30V              | 0x43 = 3.94V | 0x63 = 4.58V |

|         |            |          | 0x04 = 2.68V              | 0x24 = 3.32V              | 0x44 = 3.96V | 0x64 = 4.60V |

|         |            |          | 0x05 = 2.70V              | 0x25 = 3.34V              | 0x45 = 3.98V | 0x65 = 4.62V |

|         |            |          | 0x06 = 2.72V              | 0x26 = 3.36V              | 0x46 = 4.00V | 0x66 = 4.64V |

|         |            |          | 0x07 = 2.74V              | 0x27 = 3.38V              | 0x47 = 4.02V | 0x67 = 4.66V |

|         |            |          | 0x08 = 2.76V              | 0x28 = 3.40V              | 0x48 = 4.04V | 0x68 = 4.68V |

|         |            |          | 0x09 = 2.78V              | 0x29 = 3.42V              | 0x49 = 4.06V | 0x69 = 4.70V |

|         |            |          | 0x0A = 2.80V              | 0x2A = 3.44V              | 0x4A = 4.08V | 0x6A = 4.72V |

|         |            |          | 0x0B = 2.82V              | 0x2B = 3.46V              | 0x4B = 4.10V | 0x6B = 4.74V |

|         |            |          | 0x0C = 2.84V              | 0x2C = 3.48V              | 0x4C = 4.12V | 0x6C = 4.76V |

|         |            |          | 0x0D = 2.86V              | 0x2D = 3.50V              | 0x4D = 4.14V | 0x6D = 4.78V |

|         |            |          | 0x0E = 2.88V              | 0x2E = 3.52V              | 0x4E = 4.16V | 0x6E = 4.80V |

| 6:0     | VOUT [6:0] | 010 1000 | 0x0F = 2.90V              | 0x2F = 3.54V              | 0x4F = 4.18V | 0x6F = 4.82V |

| 0.0     | VOOT [6:0] | 010 1000 | 0x10 = 2.92V              | 0x30 = 3.56V              | 0x50 = 4.20V | 0x70 = 4.84V |

|         |            |          | 0x11 = 2.94V              | 0x31 = 3.58V              | 0x51 = 4.22V | 0x71 = 4.86V |

|         |            |          | 0x12 = 2.96V              | 0x32 = 3.60V              | 0x52 = 4.24V | 0x72 = 4.88V |

|         |            |          | 0x13 = 2.98V              | 0x33 = 3.62V              | 0x53 = 4.26V | 0x73 = 4.90V |

|         |            |          | 0x14 = 3.00V              | 0x34 = 3.64V              | 0x54 = 4.28V | 0x74 = 4.92V |