### **Features**

- Wide input voltage range: 1.9V 5.5V

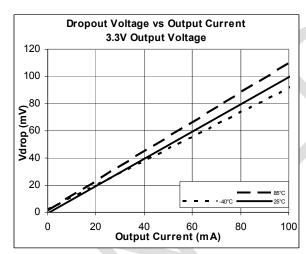

- Low dropout voltage: 100mV at 100mA output current

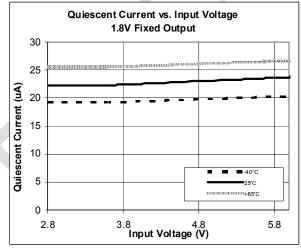

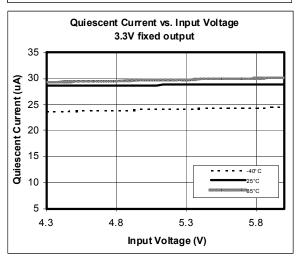

- Very low quiescent current (Iq): 25uA typical

- Fixed output voltage: 1.0V to 3.3V

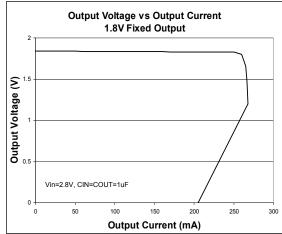

- Up to 150mA per output channel

- Very fast transient response

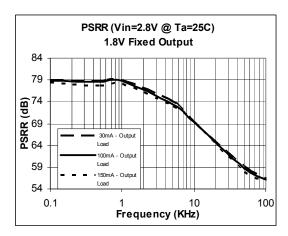

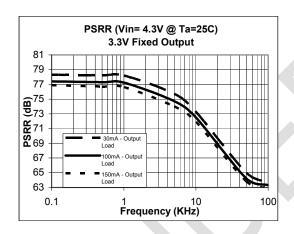

- High PSRR: 78dB at 1kHz

- Accurate voltage regulation

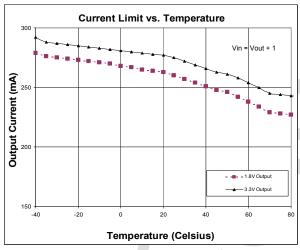

- 300mA current limiting

- Thermal shutdown protection

- Ambient temperature range -40°C to 85°C

- Package available: DFN2018-6 (USP-6B)

- DFN2018-6 (USP-6B): Available in "Green" Molding Compound (No Br. Sb)

- Lead Free Finish / RoHS Compliant (Note 1)

## **General Description**

The AP7201 is a dual low-dropout (LDO) CMOS linear regulator. The device operates from 1.9V to 5.5V input and delivers up to 150mA per output channel.

The AP7201 includes a pass element, voltage reference, error amplifier, current limit and built-in phase compensation. Key features include individual logic-compatible enable/shutdown control inputs, fold-back current limit and thermal shutdown protections.

The AP7201 is fully compatible with low ESR ceramic capacitors, reducing cost and improving output stability. The fixed output voltage for each channel is set independently. Voltages are 100mV per step within a range of 1.0V to 3.3V.

The EN function allows the output of each channel to be turned off independently, resulting in greatly reduced power consumption. The AP7201 is available in the DFN2018-6 (USP-6B) package.

## **Applications**

- Cell Phones

- Smart Phones and PDA

- MP3/MP4

- PMP

- **Bluetooth Headsets**

- Digital Still Cameras

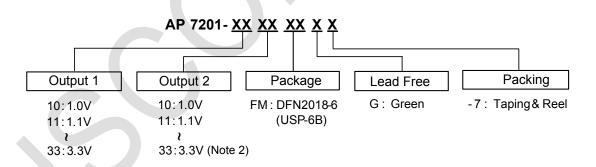

## **Ordering Information**

|                  | Dh Free er          | Dookogo         | Dockoning             | 7" Tape and Reel |                       |  |

|------------------|---------------------|-----------------|-----------------------|------------------|-----------------------|--|

| Device           | Pb-Free or<br>Green | Package<br>Code | Packaging<br>(Note 3) | Quantity         | Part Number<br>Suffix |  |

| AP7201-1818FMG-7 | <u>Pb</u> ,         | FM              | DFN2018-6 (USP-6B)    | 3000/Tape & Reel | -7                    |  |

| AP7201-1828FMG-7 | <b>B</b>            | FM              | DFN2018-6 (USP-6B)    | 3000/Tape & Reel | -7                    |  |

| AP7201-2828FMG-7 | <b>Pb</b> ,         | FM              | DFN2018-6 (USP-6B)    | 3000/Tape & Reel | -7                    |  |

Notes:

- 1. RoHS revision 13.2.2003. Glass and high temperature solder exemptions applied, see EU Directive Annex Notes 5 and 7.

- Diodes, Inc. offers custom laser trimming for additional Fixed output voltage combinations from 1.0V to 3.3V. For output voltage availability, please contact your local Diodes, Inc. sales representative.

Pad layout as shown on Diodes Inc. suggested pad layout document AP02001, which can be found on our website at

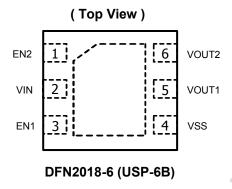

## **Pin Assignments**

## **Pin Descriptions**

| Pin Name  | Pin Number | Function                                                                       |

|-----------|------------|--------------------------------------------------------------------------------|

| EN2       | 1          | Enable input 2 (Active High)                                                   |

| VIN       | 2          | Voltage input pin. Bypass to ground through at least 0.22µF ceramic capacitor. |

| EN1       | 3          | Enable input 1 (Active High)                                                   |

| GND (VSS) | 4          | Ground                                                                         |

| OUT1      | 5          | Voltage output 1. Bypass to ground through at least 0.22µF ceramic capacitor.  |

| OUT2      | 6          | Voltage output 2. Bypass to ground through at least 0.22µF ceramic capacitor.  |

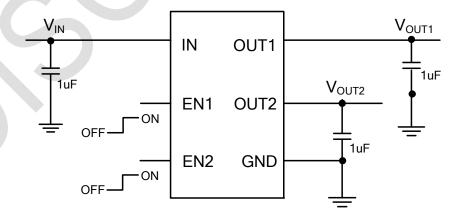

## **Typical Application Circuits**

## **Absolute Maximum Ratings**

| Symbol               | Description                                          | Rating                | Unit |

|----------------------|------------------------------------------------------|-----------------------|------|

| ESD HBM              | Human Body Model ESD Protection                      | 4                     | KV   |

| ESD MM               | Machine Model ESD Protection                         | 250                   | V    |

| Ven1 <sub>MAX</sub>  | Enable 1 Voltage                                     | V <sub>IN</sub> + 0.3 | V    |

| Ven2 <sub>MAX</sub>  | Enable 2 Voltage                                     | V <sub>IN</sub> + 0.3 | V    |

| Vout1 <sub>MAX</sub> | Output 1 Voltage                                     | V <sub>IN</sub> + 0.3 | V    |

| Vout2 <sub>MAX</sub> | Output 2 Voltage                                     | V <sub>IN</sub> + 0.3 | V    |

| Vin <sub>MAX</sub>   | Input Voltage                                        | 6.5                   | V    |

| I OUT MAX            | Continuous Load Current per Channel                  | 150                   | mA   |

| T <sub>LEAD</sub>    | Lead Temperature                                     | 260                   | °C   |

| T <sub>ST</sub>      | Storage Temperature                                  | -65 to 150            | °C   |

| TJ                   | Maximum Junction Temperature                         | 150                   | °C   |

| P <sub>D MAX</sub>   | Power Dissipation (Notes 4, 5, 6) DFN2018-6 (USP-6B) | 1700                  | mW   |

Notes:

## **Recommended Operating Conditions**

| Symbol           | Description                   | Min | Max | Unit |

|------------------|-------------------------------|-----|-----|------|

| V <sub>IN</sub>  | Input Voltage                 | 1.9 | 5.5 | V    |

| I <sub>OUT</sub> | Output Current per Channel    | 0   | 150 | mA   |

| T <sub>A</sub>   | Operating Ambient Temperature | -40 | 85  | °C   |

<sup>4.</sup> T<sub>J</sub>, max =150°C.5. Ratings apply to ambient temperature at 25°C.

## **Electrical Characteristics**

(  $T_A = 25^{\circ}C$ ,  $V_{IN} = V_{EN}$ ,  $C_{IN} = 1$ uF,  $C_{OUT} = 1$ uF unless otherwise stated )

| Symbol                         | Parameter                                          | Test Conditions                                                     | Min | Тур. | Max  | Unit |

|--------------------------------|----------------------------------------------------|---------------------------------------------------------------------|-----|------|------|------|

| $V_{\text{IN}}$                | Operation Input Voltage Range                      |                                                                     | 1.9 |      | 5.5  | V    |

| ΙQ                             | Input Quiescent Current                            | I <sub>OUT</sub> = 0                                                | _   | 25   | 45   | uA   |

| I <sub>Q(OFF)</sub>            | Input Shutdown Current                             | V <sub>EN</sub> = 0V                                                | _   |      | 1    | uA   |

| I <sub>LK(OFF)</sub>           | Input Leakage Current                              | V <sub>EN</sub> = 0V, OUT grounded                                  | _   |      | 1    | uA   |

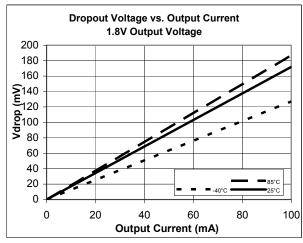

| $V_{Dropout}$                  | Dranaut Valtaga                                    | V <sub>OUT</sub> = 1.8V, I <sub>OUT</sub> = 100mA                   |     | 170  | 220  | mV   |

| $V_{Dropout}$                  | -Dropout Voltage                                   | V <sub>OUT</sub> = 3.3V, I <sub>OUT</sub> = 100mA                   |     | 100  | 150  | mV   |

| V <sub>OUT</sub>               | Output Voltage Accuracy                            |                                                                     | -2  |      | 2    | %    |

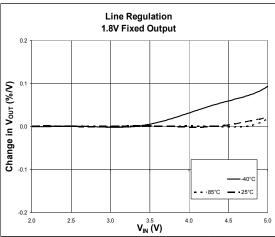

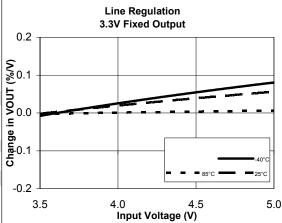

| $\Delta V_OUT/\Delta V_IN/V_O$ | Line Regulation                                    | $V_{IN} = V_{OUT} + 0.2V (V_{IN} > 1.9V)$ to 5.0V, $I_{OUT} = 1$ mA |     | 0.01 | 0.2  | %/V  |

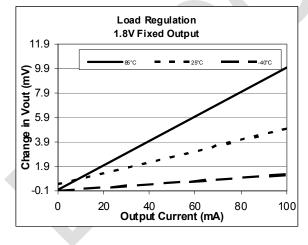

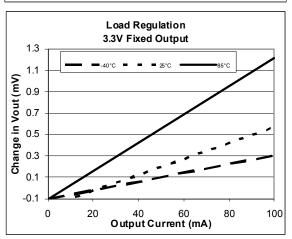

| $\Delta V_{OUT}$               | Load Regulation                                    | I <sub>OUT</sub> from 1mA to 100mA                                  |     | 5    | 30   | mV   |

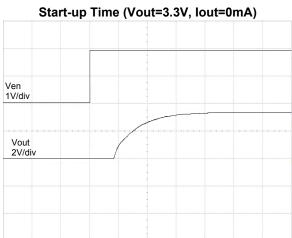

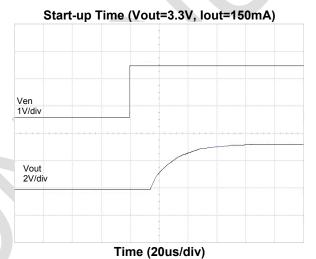

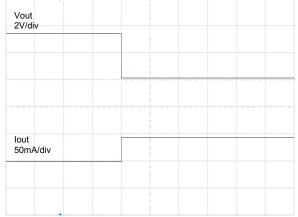

| t <sub>ST</sub>                | Start-up Time                                      | V <sub>EN</sub> = 0V to 2.0V, I <sub>OUT</sub> = 150mA              |     | 50   |      | us   |

| PSRR                           | PSRR                                               | 1kHz, I <sub>OUT</sub> = 30mA                                       |     | 78   |      | dB   |

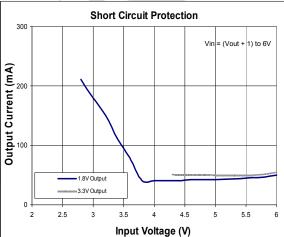

| I <sub>SHORT</sub>             | Short-circuit Current                              | $V_{IN} = 5.0V, V_{OUT} < 0.2V$                                     |     | 40   |      | mA   |

| I <sub>LIMIT</sub>             | Current Limit                                      | $V_{IN} = V_{OUT} + 1.0V$                                           |     | 300  |      | mA   |

| V <sub>IL</sub>                | EN Input Logic Low Voltage                         |                                                                     |     |      | 0.25 | V    |

| V <sub>IH</sub>                | EN Input Logic High Voltage                        |                                                                     | 1.6 |      |      | V    |

| I <sub>EN</sub>                | EN Input Leakage                                   | V <sub>EN</sub> = 0V or Vin                                         | _   |      | 0.1  | uA   |

| T <sub>SHDN</sub>              | Thermal Shutdown Threshold                         |                                                                     |     | 145  |      | °C   |

| T <sub>HYS</sub>               | Thermal Shutdown Hysteresis                        |                                                                     |     | 15   |      | °C   |

| $\theta_{JA}$                  | Thermal Resistance<br>Junction-to-Ambient (Note 6) | DFN2018-6                                                           |     | 70   |      | °C/W |

Notes: 6. Test condition for DFN2018-6: Device mounted on FR-4 2-layer board, 2oz copper, with minimum recommended pad on top layer and 3 vias to bottom layer 1.0"x1.4" ground plane.

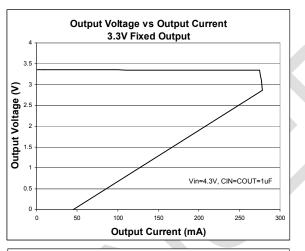

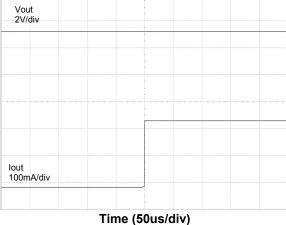

## **Typical Performance Characteristics**

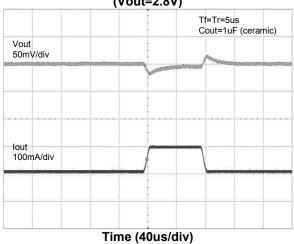

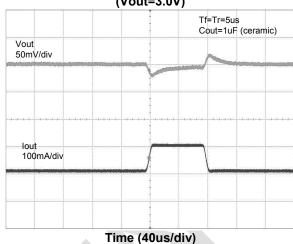

## Typical Performance Characteristics (Continued)

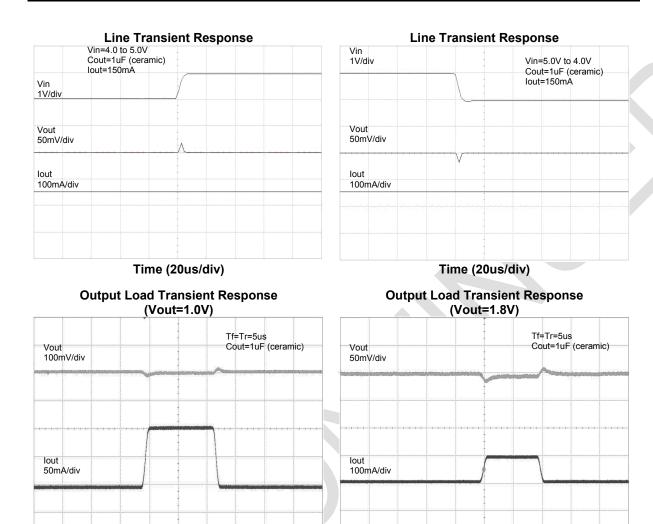

#### **Typical Performance Characteristics** (Continued)

Time (20us/div)

Time (40us/div)

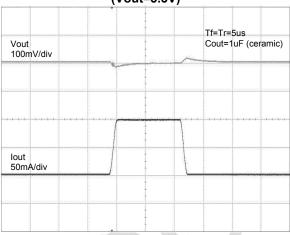

## Typical Performance Characteristics (Continued)

Time (40us/div)

## Typical Performance Characteristics (Continued)

# Output Load Transient Response (Vout=2.8V)

# Output Load Transient Response (Vout=3.0V)

# Output Load Transient Response (Vout=3.3V)

## **Application Note**

#### **Input Capacitor**

AP7201 requires a minimum input capacitance of  $0.22\mu F$  ceramic capacitor between VIN and GND pins to prevent any impedance interactions with the supply. This input capacitor should be located as close as possible to the device to assure input stability and less noise. For PCB layout, a wide copper trace is required for both IN and GND.

#### **Output Capacitor**

AP7201 requires a minimum of  $0.22\mu F$  capacitance on each output to stabilize the transient response of the LDO. The AP7201 is designed to have excellent transient response for most applications with a small amount of output capacitance. A ceramic capacitor is recommended on each channel to connect between OUT and GND pins. The device is also stable with multiple capacitors in parallel, which can be of any type of value. Larger capacitance helps to reduce undershoot and overshoot during transient and provides better stability and noise performance. This output capacitor should be placed as close as possible to OUT and GND pins for optimum performance.

#### **No Load Stability**

Other than external resistor divider, no minimum load is required to keep the device stable. The device will remain stable and regulated in no load condition.

#### **ENABLE/SHUTDOWN Operation**

The AP7201 is turned on by setting the EN pin high by pulling to input voltage (VIN), and is turned off by pulling it low (GND). The EN function allows the output of each regulator to be turned off independently, resulting in greatly reduced power consumption. The EN pin should be tied to VIN pin to keep the regulator output on at all time. To ensure proper operation, the signal source used to drive the EN pin must be able to swing above and below the specified turn-on/off voltage thresholds listed in the Electrical Characteristics section under  $V_{\rm IL}$  and  $V_{\rm IH}$ .

#### **Current Limit Protection**

In the presence of a short or excessive load current condition, the AP7201 uses an internal short circuit fold-back mechanism that triggers the current limit protection and clamps the output current to approximately 300mA.

#### **Short Circuit Protection**

When OUT pin is short-circuited to GND or OUT pin voltage is less than 200mV, short circuit protection will be triggered and clamp the output current to approximately 40mA typical. This feature protects the regulator from over-current and damage due to overheating.

## Application Note (Continued)

#### Wide Fixed Output Range

The AP7201, with a wide fixed output range of 1V to 3.3V, provides a versatile solution for many portable and low power applications.

#### **Low Quiescent Current**

The AP7201, consuming only around 25µA for all input range, provides great power saving in portable and low power applications.

#### **Thermal Shutdown Protection**

Thermal protection disables both outputs when the junction temperature rises to approximately +145°C, allowing the device to cool down. When the junction temperature reduces to approximately +130°C the output circuitry is enabled again. Depending on power dissipation, thermal resistance, and ambient temperature, the thermal protection circuit may cycle on and off. This cycling limits the heat dissipation of the regulator, protecting it from damage due to overheating.

#### **Power Dissipation**

The device power dissipation and proper sizing of the thermal plane that is connected to the thermal pad is critical to avoid thermal shutdown and ensure reliable operation. Power dissipation of the device depends on input voltage and load conditions and can be calculated by:

$$P_{D} = (V_{IN} - V_{OUT})xI_{OUT}$$

The AP7201 is available in the DFN2818-6 package with exposed pad, which is the primary conduction path for heat to the printed circuit board (PCB). The pad can be connected to ground or be left floating; however, to ensure the device will not overheat, it should be attached to an appropriate amount of copper PCB area.

The maximum power dissipation, handled by the device, depends on the maximum junction to ambient thermal resistance, maximum ambient temperature, and maximum device junction temperature, which can be calculated by the equation in the following:

$$P_{D}(\text{max@T}_{A}) = \frac{(+145^{\circ}C - T_{A})}{R_{\theta JA}}$$

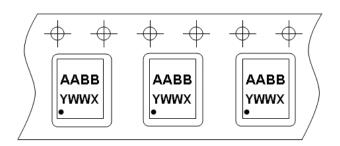

## **Marking Information**

### (1) DFN2018-6 (USP-6B)

(Top View)

AA : Output 1 BB : Output 2

**AA BB** <u>Y WW X</u> Y: Year "7": 2007 "8": 2008 WW: Month 01~52

X: G: Green

### **Marking ID Code Table**

| Device        | ID Code |

|---------------|---------|

| AP7201-1818FM | 1818    |

| AP7201-1828FM | 1828    |

| AP7201-2828FM | 2828    |

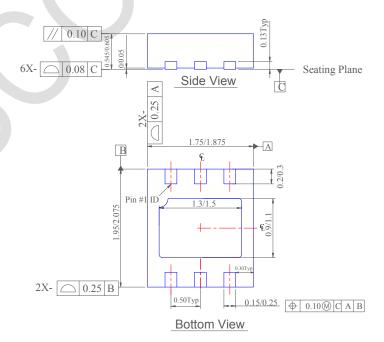

#### **Package Information** ( All Dimensions in mm )

### (1) DFN2018-6 (USP-6B)

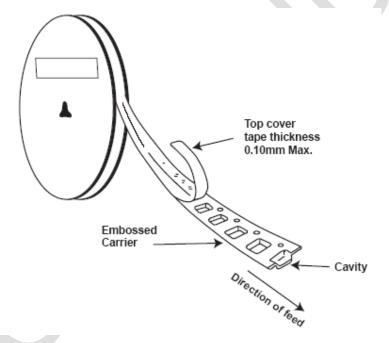

## **Taping Orientation** (Note 7)

Notes: 7. The taping orientation of the other package type can be found on our website at <a href="http://www.diodes.com/datasheets/ap02007.pdf">http://www.diodes.com/datasheets/ap02007.pdf</a>

### IMPORTANT NOTICE

Diodes Incorporated and its subsidiaries reserve the right to make modifications, enhancements, improvements, corrections or other changes without further notice to any product herein. Diodes Incorporated does not assume any liability arising out of the application or use of any product described herein; neither does it convey any license under its patent rights, nor the rights of others. The user of products in such applications shall assume all risks of such use and will agree to hold Diodes Incorporated and all the companies whose products are represented on our website, harmless against all damages.

#### LIFE SUPPORT

Diodes Incorporated products are not authorized for use as critical components in life support devices or systems without the expressed written approval of the President of Diodes Incorporated.