#### COMPACT DUAL-PHASE SYNCHRONOUS-RECTIFIED BUCK CONTROLLER

### **Description**

The AP3598A is a dual-phase synchronous buck PWM controller with integrated drivers which are optimized for high performance graphic card and computer applications. The IC is capable of delivering up to 60A output current capability, supporting 12V MOSFET drivers with internal bootstrap diodes.

The dynamic output voltage could be implemented by analog method with a switching device and a resistor network. The adjustable current balance is achieved by  $R_{DS(ON)}$  current sensing technique.

The AP3598A provides over current protection, input/output under voltage protection, over voltage protection and over temperature protection.

Other features include adjustable soft start, adjustable operation frequency and so on. With aforementioned functions, the IC adopts U-QFN4040-24 package.

#### **Features**

- Operate with Single Supply Voltage

- Reference Voltage Output with 1% Accuracy

- Simple Single Loop Voltage Mode Control

- 12V Bootstrapped Drivers with Internal Boot-strap Diodes

- Adjustable Current Balancing by R<sub>DS(ON)</sub> Current Sensing

- Adjustable Operation Frequency from 200kHz to 500kHz Per Phase

- External Compensation

- Dynamic Output Voltage Adjustment

- Adjustable Soft Start

- Built-in UV and OV Protection Function

- Built-in Over Current Protection

- Built-in Thermal Shutdown Function

- U-QFN4040-24 Package

- Totally Lead-Free & Fully RoHS Compliant (Notes 1 & 2)

- Halogen and Antimony Free. "Green" Device (Note 3)

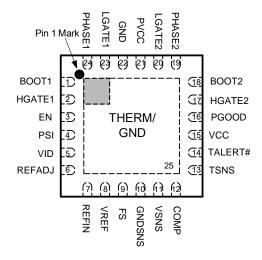

## Pin Assignments

#### (Top View)

U-QFN4040-24

## **Applications**

- Middle-High End Graphic Card

- Generic Desktop and Consumer Electronics

Notes:

- 1. No purposely added lead. Fully EU Directive 2002/95/EC (RoHS) & 2011/65/EU (RoHS 2) compliant.

- 2. See http://www.diodes.com/quality/lead\_free.html for more information about Diodes Incorporated's definitions of Halogen- and Antimony-free, "Green" and Lead-free.

- 3. Halogen- and Antimony-free "Green" products are defined as those which contain <900ppm bromine, <900ppm chlorine (<1500ppm total Br + Cl) and <1000ppm antimony compounds.

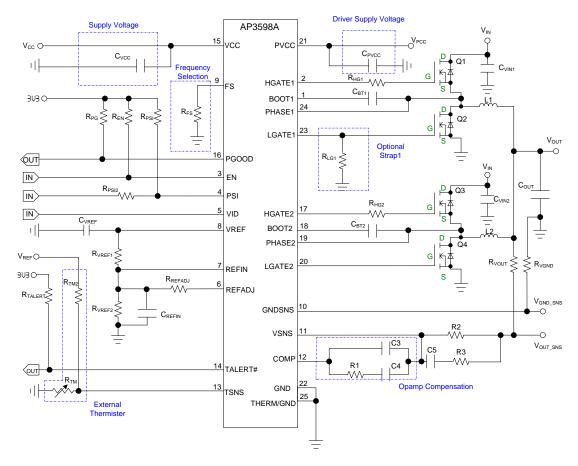

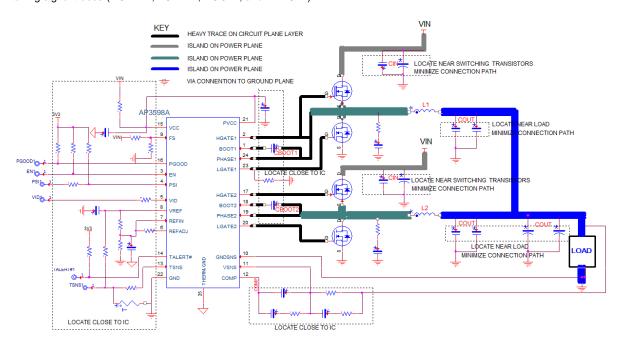

## **Typical Applications Circuit**

| Component           | Value | Unit | Component           | Value  | Unit | Component          | Value | Unit |

|---------------------|-------|------|---------------------|--------|------|--------------------|-------|------|

| C <sub>VCC</sub>    | 10    | μF   | R <sub>TALERT</sub> | 100    | kΩ   | C3                 | 10    | pF   |

| C <sub>P</sub> VCC  | 10    | μF   | R <sub>TM2</sub>    | TBD    | kΩ   | C4                 | 2.2   | nF   |

| C <sub>VIN1</sub>   | 300   | μF   | R <sub>TM</sub>     | TBD    | kΩ   | C5                 | 1.5   | nF   |

| C <sub>VIN2</sub>   | 300   | μF   | R <sub>HG1</sub>    | 0      | Ω    | Соит               | 330*3 | μF   |

| $R_{PG}$            | 100   | kΩ   | C <sub>BT1</sub>    | 100    | nF   | R <sub>VOUT</sub>  | 0     | Ω    |

| R <sub>EN</sub>     | 100   | kΩ   | R <sub>LG1</sub>    | Note 4 | Ω    | R <sub>VGND</sub>  | 0     | Ω    |

| R <sub>FS</sub>     | 33    | kΩ   | R <sub>HG2</sub>    | 0      | Ω    | C <sub>REFIN</sub> | 0.033 | μF   |

| R <sub>PSI</sub>    | 100   | kΩ   | C <sub>BT2</sub>    | 100    | nF   | Q1                 | _     | _    |

| R <sub>PSI2</sub>   | 0     | kΩ   | R1                  | 12     | kΩ   | Q2                 | _     | _    |

| C <sub>VREF</sub>   | 1     | μF   | R2                  | 2.2    | kΩ   | Q3                 | -     | -    |

| R <sub>VREF1</sub>  | 4.75  | kΩ   | R3                  | 560    | Ω    | Q4                 | -     | _    |

| R <sub>VREF2</sub>  | 4.22  | kΩ   | L1                  | 0.36   | μH   | _                  | -     | _    |

| R <sub>REFADJ</sub> | 6.34  | kΩ   | L2                  | 0.36   | μH   | _                  | -     | _    |

Table 1. Component Guide

Note 4:  $R_{LG1}$  are OCP setting resisters: 5k for lower OCP threshold,  $I_{OCP} = 150 \text{mV/R}_{DS(ON)}$  10k for medium OCP threshold,  $I_{OCP} = 250 \text{mV/R}_{DS(ON)}$ >20k for disabling OCP function

# **Pin Descriptions**

| Pin Number | Pin Name  | Function                                                                                             |  |

|------------|-----------|------------------------------------------------------------------------------------------------------|--|

| 1          | BOOT1     | High side gate driver supply of phase 1                                                              |  |

| 2          | HGATE1    | High side gate driver output of phase 1                                                              |  |

| 3          | EN        | Enable input                                                                                         |  |

| 4          | PSI       | Power saving interface                                                                               |  |

| 5          | VID       | Voltage ID input                                                                                     |  |

| 6          | REFADJ    | Reference adjustment output                                                                          |  |

| 7          | REFIN     | External reference input                                                                             |  |

| 8          | VREF      | Output reference voltage. This is high precision voltage reference                                   |  |

| 9          | FS        | Frequency selection. Connect a resistor from this pin to GND to select the switching frequency       |  |

| 10         | GNDSNS    | GND sense. Negative node of the remote voltage sense                                                 |  |

| 11         | VSNS      | V <sub>OUT</sub> sense. Positive node of the remote differential voltage sense                       |  |

| 12         | COMP      | Compensation. Use this pin in combination with VSNS to compensate the feedback loop of the converter |  |

| 13         | TSNS      | Temperature sensing input                                                                            |  |

| 14         | TALERT#   | Thermal alert. Active low open drain output                                                          |  |

| 15         | VCC       | Supply voltage                                                                                       |  |

| 16         | PGOOD     | Open drain power good output                                                                         |  |

| 17         | HGATE2    | High side gate driver output of phase 2                                                              |  |

| 18         | BOOT2     | High side gate driver supply of phase 2                                                              |  |

| 19         | PHASE2    | Switch node of phase 2                                                                               |  |

| 20         | LGATE2    | Low side gate driver output of phase 2                                                               |  |

| 21         | PVCC      | Driver supply voltage                                                                                |  |

| 22         | GND       | Ground. Must be connected to GND on PCB                                                              |  |

| 23         | LGATE1    | Low side gate driver output of phase 1                                                               |  |

| 24         | PHASE1    | Switch node of phase 1                                                                               |  |

| 25         | THERM/GND | Thermal connection to the PCB. Must be connected to GND on PCB                                       |  |

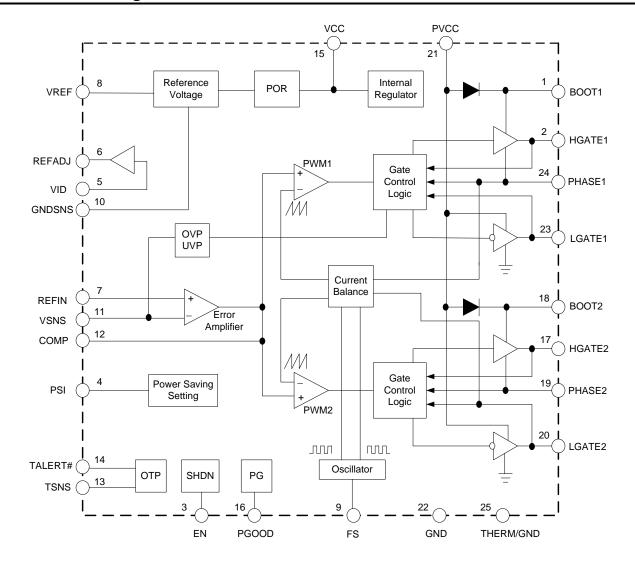

## **Functional Block Diagram**

## **Absolute Maximum Ratings** (Note 5)

| Symbol                                     | Parameter                                  |             | Rating                            | Unit |  |

|--------------------------------------------|--------------------------------------------|-------------|-----------------------------------|------|--|

| V <sub>CC</sub> , V <sub>PCC</sub>         | VCC, PVCC Pin Voltage                      |             | -0.3 to 15                        | V    |  |

| V V                                        | DUACE to CND Voltage                       | <200ns      | -5 to 32                          | V    |  |

| V <sub>PHASE1</sub> , V <sub>PHASE2</sub>  | PHASE to GND Voltage                       | >200ns      | -0.3 to 26                        | _ v  |  |

| VBOOT1_PHASE1, VBOOT2_PHASE2               | BOOT to PHASE Voltage                      |             | -0.3 to 15                        | V    |  |

|                                            | DOOT to OND Veltors                        | <200ns      | -0.3 to 42                        | V    |  |

| V <sub>BOOT1</sub> , V <sub>BOOT2</sub>    | BOOT to GND Voltage                        | >200ns      | -0.3 to 30                        | V    |  |

|                                            |                                            | <200ns      | -5 to V <sub>BOOT_PHASEx</sub> +5 | V    |  |

| V <sub>HGATE1</sub> , V <sub>HGATE2</sub>  | HGATE to PHASE Voltage                     | >200ns      | -0.3 to VBOOT_PHASEx+0.3          |      |  |

| V V                                        | LOATE to OND Veltere                       | <200ns      | -5 to V <sub>IN</sub> +5          | .,   |  |

| V <sub>L</sub> GATE1, V <sub>L</sub> GATE2 | LGATE to GND Voltage                       | >200ns      | -0.3 to V <sub>IN</sub> +0.3      | V    |  |

| -                                          | Other Input, Output or I/O Pin Voltage     |             | 0 to 6                            | V    |  |

| $\theta_{JA}$                              | Thermal Resistance                         |             | 40                                | °C/W |  |

| P <sub>D</sub>                             | Power Dissipation (T <sub>A</sub> = +25°C) |             | 2.5                               | W    |  |

| TJ                                         | Operating Junction Temperature Range       |             | -40 to +150                       |      |  |

| T <sub>STG</sub>                           | Storage Temperature                        | -65 to +150 |                                   | °C   |  |

| T <sub>LEAD</sub>                          | Lead Temperature (Soldering, 10sec)        |             | +260                              |      |  |

| _                                          | ESD(Machine Model)                         | 200         |                                   | V    |  |

| _                                          | ESD(Human Body Model)                      |             | 2000                              | V    |  |

Note 5: Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "Recommended Operating Conditions" is not implied. Exposure to "Absolute Maximum Ratings" for extended periods may affect device reliability.

## **Recommended Operating Conditions**

| Symbol                                       | Parameter            | Min | Max  | Unit |

|----------------------------------------------|----------------------|-----|------|------|

| Vcc, Vpcc                                    | Supply Input Voltage | 4.5 | 13.2 | V    |

| V <sub>OUT</sub>                             | Output Voltage       | 0.3 | 2    | V    |

| T <sub>A</sub> Operating Ambient Temperature |                      | -40 | +85  | °C   |

## **Electrical Characteristics** (V<sub>CC</sub> = 12V, V<sub>PCC</sub> = 12V, T<sub>A</sub> = +25°C, unless otherwise specified.)

| Symbol               | Parameter                                | Conditions                                                             | Min  | Тур  | Max  | Unit |  |

|----------------------|------------------------------------------|------------------------------------------------------------------------|------|------|------|------|--|

| SUPPLY VOLTAGE       |                                          |                                                                        |      |      |      |      |  |

| Icc                  | Supply Current                           | HGATE and LGATE<br>Open, Switching                                     | -    | 5    | _    | mA   |  |

| I <sub>CC_Q</sub>    | Quiescent Supply Current                 | No Switching                                                           | -    | 4    | _    | mA   |  |

| I <sub>SHDN</sub>    | Shutdown Supply Current                  | Shutdown                                                               | -    | 4    | _    | mA   |  |

| POR                  |                                          |                                                                        |      |      |      |      |  |

| V <sub>CCRTH</sub>   | Under Voltage Lockout Threshold for VCC  | -                                                                      | 3.9  | 4.1  | 4.3  | V    |  |

| V <sub>CCHYS</sub>   | Hysteresis for VCC                       | -                                                                      | _    | 0.4  | _    | V    |  |

| V <sub>PCCRTH</sub>  | Under Voltage Lockout Threshold for PVCC | -                                                                      | 3.9  | 4.1  | 4.3  | V    |  |

| V <sub>PCCHYS</sub>  | Hysteresis for PVCC                      | -                                                                      | ı    | 0.4  | _    | V    |  |

| REFERENCE VOLTAG     | GE .                                     |                                                                        |      |      |      |      |  |

|                      | Defended Valley Account                  | $I_{REF} = 100\mu A, T_A = +25^{\circ}C$                               | 1.98 | 2.00 | 2.02 |      |  |

| $V_{REF}$            | Reference Voltage Accuracy               | $I_{REF} = 100 \mu A,$<br>$T_A = 0 \text{ to } +150 ^{\circ} \text{C}$ | 1.97 | _    | 2.03 | V    |  |

| $\Delta V_{REF}$     | Reference Voltage Load Regulation        | I <sub>REF</sub> = 0 to 2mA                                            | -5   | _    | 5    | mV   |  |

| I <sub>REF</sub>     | VREF Maximum Output Current              | -                                                                      | 10   | -    | _    | mA   |  |

| ERROR AMPLIFIER      |                                          |                                                                        |      |      |      |      |  |

| A <sub>O</sub>       | Open Loop DC Gain                        | Guaranteed by design                                                   | 70   | 80   | _    | dB   |  |

| $G_BW$               | Gain-Bandwidth Product                   | C <sub>LOAD</sub> = 5pF,<br>Guaranteed by design                       | ı    | 20   | _    | MHz  |  |

| SR                   | Slew Rate                                | Guaranteed by design                                                   | 15   | 20   | _    | V/µs |  |

| I <sub>COMP</sub>    | Maximum Current (Sink and Source)        | V <sub>COMP</sub> = 1.6V                                               | 1.5  | 2.0  | _    | mA   |  |

| FREQUENCY SETTING    | G                                        |                                                                        |      |      |      |      |  |

| $V_{FS}$             | FS Voltage                               | $R_{FS} = 33k\Omega$                                                   | -    | 1    | _    | V    |  |

| _                    | Switching Frequency Setting Range        | -                                                                      | 200  | -    | 500  | kHz  |  |

| fosc                 | Free Run Switching Frequency             | $R_{FS} = 33k\Omega$                                                   | 270  | 300  | 330  | kHz  |  |

| Δfosc                | Switching Frequency Accuracy             | fosc = 200kHz to 500kHz                                                | -15  | -    | 15   | %    |  |

| OSCILLATOR           |                                          |                                                                        |      |      |      |      |  |

| _                    | Maximum Duty Cycle                       | -                                                                      | 35   | 40   | _    | %    |  |

|                      | Minimum Duty Cycle                       | -                                                                      | -    | 0    | _    | %    |  |

| $\Delta V_{\sf OSC}$ | Ramp Amplitude                           | V <sub>CC</sub> = 12V                                                  | ı    | 3.5  | _    | V    |  |

| ENABLE FUNCTION      |                                          |                                                                        |      |      |      |      |  |

| VENIH                | Enable High Threshold                    | -                                                                      | 1.4  | _    | _    | V    |  |

| V <sub>ENIL</sub>    | Enable Low Threshold                     | -                                                                      | -    | -    | 0.6  | V    |  |

|                      | 1                                        | 1                                                                      | 1    | 1    | 1    | i    |  |

# $\textbf{Electrical Characteristics} \ \, \text{(Cont. V}_{\text{CC}} = 12\text{V}, \, \text{V}_{\text{PCC}} = 12\text{V}, \, \text{T}_{\text{A}} = +25^{\circ}\text{C}, \, \text{unless otherwise specified.)}$

| Symbol                  | Parameter                                        | Conditions                                                                     | Min                      | Тур  | Max                      | Unit     |

|-------------------------|--------------------------------------------------|--------------------------------------------------------------------------------|--------------------------|------|--------------------------|----------|

| POWER SAVING INTERFACE  |                                                  |                                                                                |                          |      |                          |          |

| V <sub>PSIH</sub>       | Power Saving Interface High<br>Threshold         | Dual Phase with FCCM                                                           | 1.5                      | -    | _                        | V        |

| $V_{PSIL}$              | Power Saving Interface Low Threshold             | Single Phase with DCM                                                          | -                        | ı    | 0.4                      | >        |

| $V_{PSIM}$              | Power Saving Interface<br>Intermediate Threshold | Single Phase with FCCM                                                         | 0.8                      | ı    | 1.1                      | ٧        |

| POWER GOOD              |                                                  |                                                                                |                          |      |                          |          |

| t <sub>PG_DLY</sub>     | Delay Time for PGOOD from<br>High to Low         | -                                                                              | -                        | 10   | -                        | μs       |

| R <sub>PG</sub>         | Internal Power Good Pull Low<br>Resistance       | -                                                                              | -                        | -    | 150                      | Ω        |

| GATE DRIVER             |                                                  |                                                                                |                          |      |                          |          |

| I <sub>HG_SRC</sub>     | Upper Gate Sourcing Current                      | V <sub>BOOTx</sub> -V <sub>PHASEx</sub> = 6V                                   | -                        | 1.2  | -                        | Α        |

| R <sub>HG_SNK</sub>     | Upper Gate Sinking<br>Resistance                 | V <sub>UGATEx</sub> -V <sub>PHASEx</sub> = 0.1V<br>I <sub>UGATEx</sub> = 100mA | -                        | 2    | -                        | Ω        |

| I <sub>LG_SRC</sub>     | Lower Gate Sourcing Current                      | V <sub>CC</sub> -V <sub>LGATEx</sub> = 6V                                      | _                        | 1.2  | _                        | Α        |

| R <sub>LG_SNK</sub>     | Lower Gate Sinking<br>Resistance                 | V <sub>LGATEx</sub> = 0.1V<br>I <sub>LGATEx</sub> = 100mA                      | -                        | 1.4  | _                        | Ω        |

| V <sub>BOOT</sub>       | Boot Diode Forward Voltage                       | V <sub>PCC</sub> -V <sub>BOOT</sub> , I <sub>BOOT</sub> = 20mA                 | -                        | 0.8  | -                        | V        |

| PROTECTION              |                                                  |                                                                                |                          |      |                          |          |

| $V_{UVP}$               | Output Under Voltage<br>Protection Threshold     | -                                                                              | -                        | -    | 0.5*<br>V <sub>OUT</sub> | V        |

| tuvp                    | Delay Time for UVP Triggered                     | _                                                                              | _                        | 50   | _                        | μs       |

| V <sub>OVP</sub>        | Output Over Voltage Protection<br>Threshold      | _                                                                              | 1.4*<br>V <sub>OUT</sub> | ı    | -                        | ٧        |

| $t_{OVP}$               | Delay Time for OVP Triggered                     | _                                                                              | _                        | 50   | _                        | μs       |

| IOCSET                  | LGATE OC Setting Current                         | _                                                                              | -                        | 21.5 | _                        | μΑ       |

| -                       | Built-in Maximum OCP Voltage                     | _                                                                              | -                        | 0.35 | ı                        | <b>V</b> |

| THERMAL PROTECTION      |                                                  |                                                                                |                          |      |                          |          |

| T <sub>SD</sub>         | Thermal Shutdown Threshold                       | _                                                                              | +150                     | +160 | +170                     | °C       |

| T <sub>ALERT#</sub>     | Minimum Thermal Alert<br>Threshold               | -                                                                              | +120                     | +130 | +140                     | °C       |

| V <sub>TSNS</sub>       | Temperature Sense Threshold                      | -                                                                              | -                        | 1.00 | _                        | V        |

| PWM-VID DYNAMIC VOLTAGE | CONTROL                                          |                                                                                |                          |      |                          |          |

| V <sub>IH</sub>         | Logic High Level                                 | _                                                                              | 1.5                      | -    | _                        | V        |

| V <sub>IL</sub>         | Logic Low Level                                  | _                                                                              | -                        | -    | 0.4                      | V        |

| V <sub>ID</sub>         | VID Voltage in High-Z Mode                       | _                                                                              | -                        | 1.1  | _                        | V        |

| CURRENT BALANCE         |                                                  |                                                                                |                          |      |                          |          |

| lofs                    | Current Balance Sense Offset                     | _                                                                              | _                        | 0    | _                        | μA       |

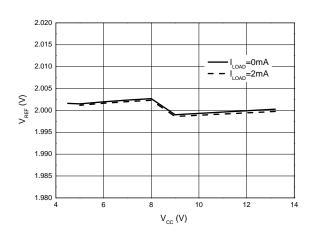

## **Performance Characteristics**

### **V<sub>REF</sub> Line Regulation**

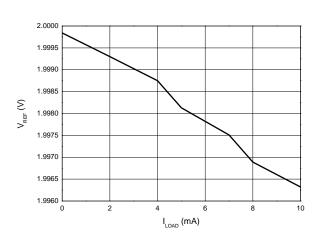

## $\ensuremath{V_{REF}}$ Load Regulation

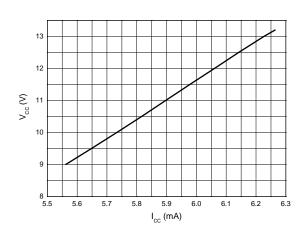

$V_{\text{CC}}$  vs.  $I_{\text{CC}}$

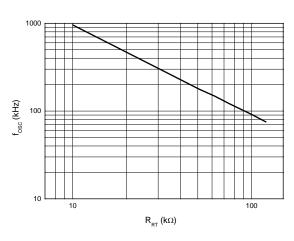

fosc vs. RRT

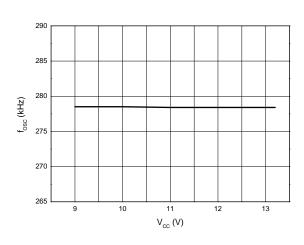

fosc vs. Vcc

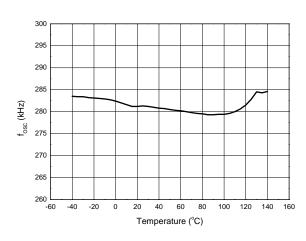

fosc vs. Temperature

## **Performance Characteristics (Cont.)**

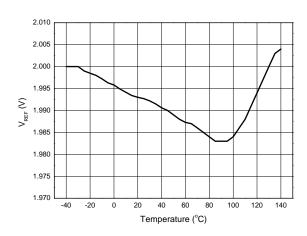

### V<sub>REF</sub> vs. Temperature

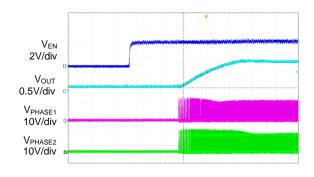

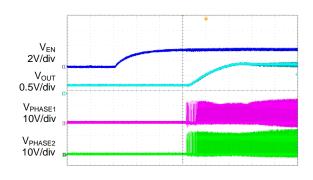

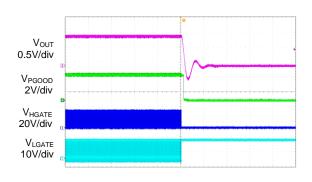

EN On Waveform (V<sub>IN</sub>=12V, V<sub>OUT</sub>=1.0V, I<sub>OUT</sub>=0A)

Time 400µs/div

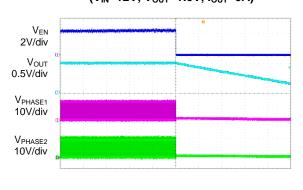

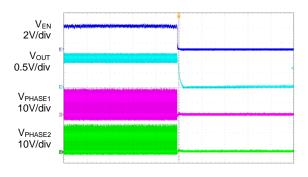

# EN Off Waveform (V<sub>IN</sub>=12V, V<sub>OUT</sub>=1.0V, I<sub>OUT</sub>=0A)

Time 400µs/div

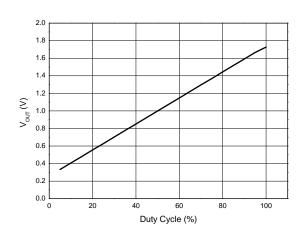

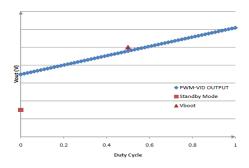

### V<sub>OUT</sub> vs. Duty Cycle

EN On Waveform (V<sub>IN</sub>=12V, V<sub>OUT</sub>=1.0V, I<sub>OUT</sub>=60A)

Time 400µs/div

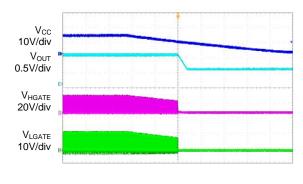

# EN Off Waveform (V<sub>IN</sub>=12V, V<sub>OUT</sub>=1.0V, I<sub>OUT</sub>=60A)

Time 400µs/div

## **Performance Characteristics (Cont.)**

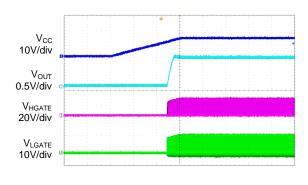

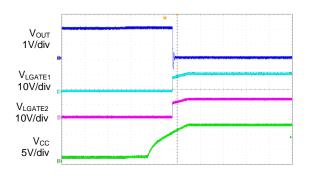

# Power On Waveform (V<sub>IN</sub>=12V, V<sub>OUT</sub>=1.0V, I<sub>OUT</sub>=0A)

Time 4ms/div

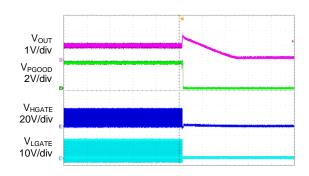

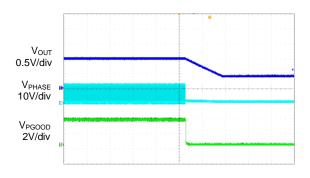

# Power Off Waveform (V<sub>IN</sub>=12V, V<sub>OUT</sub>=1.0V, I<sub>OUT</sub>=0A)

Time 4ms/div

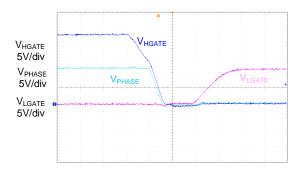

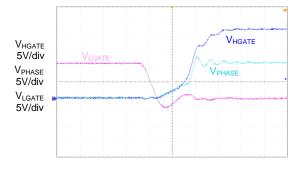

### Dead Time 1

Time 40ns/div

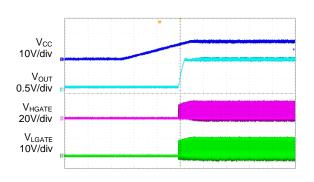

# Power On Waveform (V<sub>IN</sub>=12V, V<sub>OUT</sub>=1.0V, I<sub>OUT</sub>=60A)

Time 4ms/div

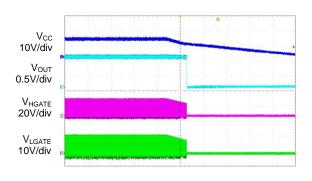

# Power Off Waveform (V<sub>IN</sub>=12V, V<sub>OUT</sub>=1.0V, I<sub>OUT</sub>=60A)

Time 4ms/div

### Dead Time 2

Time 40ns/div

## **Performance Characteristics (Cont.)**

# Under Voltage Protection (V<sub>IN</sub>=12V, V<sub>OUT</sub>=1.0V)

Time 400µs/div

# Over Current Protection (V<sub>IN</sub>=12V, V<sub>OUT</sub>=1.0V)

Time 2ms/div

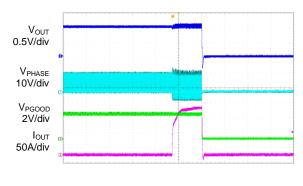

# Pre-bias Start-up (V<sub>IN</sub>=12V, V<sub>OUT</sub>=2V before Power On)

Time 4ms/div

# Over Voltage Protection (V<sub>IN</sub>=12V, V<sub>OUT</sub>=1.0V)

Time 400µs/div

# Over Temperature Protection (V<sub>IN</sub>=12V, V<sub>OUT</sub>=1.0V)

Time 400µs/div

## **Application Information**

#### 1. Overview

The AP3598A is a dual-phase synchronous-rectified buck controller designed to deliver high quality output voltage for high power applications. The IC is capable of delivering up to 60A output current with embedded bootstrapped drivers that support 12V+12V driver capability. The built-in bootstrap diode simplifies the circuit design and reduces external part count and PCB space.

The output voltage is precisely regulated to the reference input that is dynamically adjustable by external voltage divider. The adjustable current balance is achieved by R<sub>DS(ON)</sub> current sensing technique.

The AP3598A features comprehensive protection functions including over current protection, input/output under voltage protection, over voltage protection and over temperature protection.

Other features include adjustable soft start, adjustable operation frequency, and quick response to step load transient. With aforementioned functions, the AP3598A provides customer a compact, high efficiency, well-protected and cost effective solution. It uses U-QFN4040-24 package.

#### 2. Power On Reset

A Power On Reset (POR) circuitry continuously monitors the supply voltage at VCC and PVCC pin. Once the rising POR threshold is exceeded, the AP3598A sets itself to active state and is ready to accept chip enable command. The rising POR threshold is typically 4.1V.

#### 3. Soft Start

The AP3598A initiates its soft start cycle when EN is released from ground once the POR is granted.

Slew rate of voltage transition at REFIN and output voltage VSNS during soft start and V<sub>REFIN</sub> jumping is controlled by the capacitor connected to the REFIN pin. This reduces inrush current to charge/discharge the large output capacitors during soft start and VID changing, and prevents OCP, OVP, UVP false trigger.

#### 4. Pre-Bias Function

The AP3598A features pre-bias start-up capability. If the output voltage is pre-biased voltage, which makes VSNS voltage higher than reference voltage REFIN. The error amplifier keeps COMP voltage lower than the valley of the sawtooth waveform and makes PWM comparators output low until the ramping REFIN voltage catches up the output voltage.

The AP3598A keeps both upper and lower MOSFETS off until the first pulse takes place.

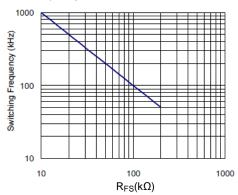

#### 5. Chip Oscillator Frequency Programming

A resistor R<sub>FS</sub> connected to FS pin programs the oscillator frequency as:

$$f_{OSC} = \frac{10000}{R_{FS}(k\Omega)}(kHz)$$

Figure 1 shows the relationship between oscillation frequency and RFS.

Figure 1. Switching Frequency vs. R<sub>FS</sub>

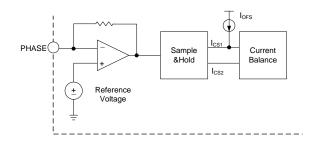

#### 6. Current Balance

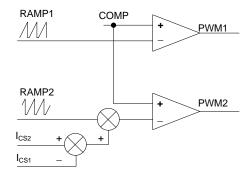

The AP3598A extracts phase currents for current balance by parasitic on-resistance of the lower switches when turned on as shown in Figure 2.

Figure 2. R<sub>DS(ON)</sub> Current Sensing Scheme

The GM amplifier senses the voltage drop across the lower switch and converts it into current signal when it turns on. The sampled and held current is expressed as:

$$I_{CSX} = I_{LX} \times R_{DS(ON)} \times 10^{-3} + 12\mu A$$

Where  $I_{LX}$  is the phase x current in Ampere,  $R_{DS(ON)}$  is the on-resistance of low side MOSFET ( $\Omega$ ), 12 $\mu$ A is a constant current to compensate the offset voltage of the current sensing circuit.

The AP3598A tunes the duty cycle of each channel for current balance according to the sensed inductor current signals as shown in Figure 3. If the current of channel 1 is smaller than the current of channel 2, the AP3598A increases the duty cycle of the corresponding phase to increase its phase current accordingly, vice versa.

Figure 3. Current Balance Scheme of AP3598A

#### 7. Power Saving Interface (PSI)

This is a multilevel input to support Power Saving features. The AP3598A supports dual phase with FCCM and single phase with DCM and FCCM.

| Mode | Descriptions                                                                                                                                                                           |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DCM  | Discontinuous Conduction Mode decreases the switching frequency to improve the efficiency at light load                                                                                |

| FCCM | Forced Continuous Conduction Mode does not change the switching frequency when the inductor current goes to negative at light load. This mode is used to disable Power Saving features |

Table 2. Description of Operating Modes

As shown in Table 2, an input high voltage (>1.5V) will set the controller to dual phase with FCCM mode; an input of intermediate level (between 0.8V and 1.1V) will set the controller to single phase with FCCM mode; an input low voltage will set the controller to single phase with DCM mode.

#### 8. Short Circuit Protection (SCP)

The AP3598A has over current (OCP) and output under voltage protection (UVP) functions.

#### 8.1 OCP function

The AP3598A detects voltage drop across the lower MOSFET (PHASE voltage) of Channel 1 for over current protection when it is turned on. If PHASE voltage is lower than the user programmable voltage  $V_{OCP}$ , the AP3598A asserts OCP and shuts down the converter. The  $V_{OCP}$  level is as shown in Table 3. The over current  $I_{OCP}$  can be calculated according to the on-resistance of the lower MOSFET used.

$$I_{OCP} = -\frac{V_{OCP}}{R_{DS(ON)}}$$

| _                     | >20kΩ  | 10kΩ | 5kΩ |

|-----------------------|--------|------|-----|

| V <sub>OCP</sub> (mV) | No OCP | 250  | 150 |

Table 3. OCP Level Selection

A resistor  $R_{OCSET}$  connected from LGATE1 pin sets the OCP threshold value  $V_{OCSET}$  when Startup. An internal current source  $I_{OCSET}$  (21.5 $\mu$ A typically), flowing through  $R_{OCSET}$  determines to select the  $V_{OCP}$  level, which can be calculated using the following equation:

$$V_{OCSET} = I_{OCSET} \times R_{OCSET}$$

If  $V_{OCSET}$  is lower than 150mV,  $V_{OCP}$  will be set to 150mV; If  $V_{OCSET}$  is between 350mV and 150mV,  $V_{OCP}$  will be set to 250mV; If  $V_{OCSET}$  is higher than 350mV,  $V_{OCP}$  will be disabled.

Because the R<sub>DS(ON)</sub> of MOSFET increases with temperature, it is necessary to take this thermal effect into consideration in calculating OCP point.

#### 8.2 UVP Function

The output voltage  $V_{SNS}$  is also monitored for under voltage protection. The UV threshold is set at 0.3V. The under voltage protection has 50 $\mu$ s triggered delay. When UVP is triggered, both high side and low side are shutdown immediately.

OCP and UVP are latched function, the AP3598A can power off, and then power on or EN reset to restart again.

#### 9. Over Voltage Protection (OVP)

The output voltage  $V_{SNS}$  is continuously monitored for over voltage protection. When it is larger than 1.5 times as setting, the OVP function is triggered. The over voltage protection has 50 $\mu$ s triggered delay. When OVP is triggered, LGATE will go high and UGATE will go low to discharge the output capacitor.

#### 10. Power Good

The PGOOD pin output is an open drain MOSFET. The output is pulled low when the AP3598A shuts down. It is recommended to use a pull-up resistor between the values of  $3k\Omega$  and  $100k\Omega$  to a voltage source that is 5V or less. The PGOOD is in a valid state once the  $V_{CC}$  voltage is greater than 1.2V.

#### 11. Thermal Shutdown

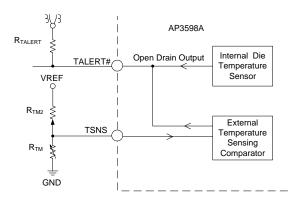

The AP3598A implements an internal thermal shutdown to protect itself if the junction temperature exceeds T<sub>J</sub>.

TSNS is the external thermistor temperature sensing input.

TALERT# is an active low open drain output warning signal to indicate when either the controller has reached 80% percent of T<sub>JMAX</sub> or MOSFET has reached its threshold through the external thermistor.

Figure 4. Thermal Alert and Temperature Sense

#### 12. PWM-VID Dynamic Voltage Control

PWM-VID is a single-wire dynamic voltage control circuit driven by the pulse width modulation method. This circuit reduces the device pin count and enables a wide dynamic voltage range.

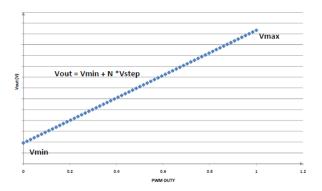

The PWM-VID duty cycle determines the variable output voltage at REFIN, as shown in Figure 5.  $V_{MIN}$  is the zero percent duty cycle voltage value.  $V_{MAX}$  is the one hundred percent duty cycle voltage value. The resolution of each voltage step ( $V_{STEP}$ ) is determined by the number of available steps ( $N_{MAX}$ ) and the selection of the dynamic voltage range ( $V_{MAX}$ - $V_{MIN}$ ). N is the number of steps at a specific  $V_{OUT}$ .  $N/N_{MAX}$  ratio is equal to the duty cycle. The dynamic voltage VID frequency ( $f_{SWVID}$ ) is determined by the unit pulse width ( $t_{U}$ ) and the available step number  $N_{MAX}$  ( $t_{VID} = t_{U}^*N_{MAX}$ ,  $f_{VID} = 1/t_{VID}$ ).  $t_{U}$  is programmable.

Figure 5. Dynamic Output

V<sub>STEP</sub>, N<sub>MAX</sub>, V<sub>MIN</sub>, and V<sub>MAX</sub> are variables that determine V<sub>OUT</sub>. N<sub>MAX</sub> is limited by the unit pulse width and the minimum VID frequency.

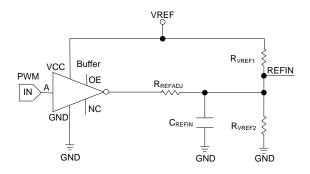

The dynamic voltage output could be implemented by the analog method with a switching device and a resistor network. A buffer is used as the switching device to create dynamic output. Resistor network sets the minimum offset voltage.

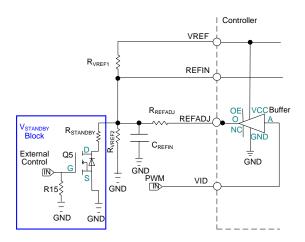

#### 12.1 Circuit Diagram

Figure 6 shows the analog circuit diagram for the PWM-VID dynamic voltage control. The buffer requires a stable, high precision voltage reference ( $V_{REF}$ ) for the linear output. The dynamic range of the circuit is determined by the resistor selection. Resistor  $R_{REFADJ}$  and capacitor  $C_{REFIN}$  function as a filter for the PWM signal, and will affect the ripple voltage and the slew rate at the output (REFIN) during voltage transitions.

Figure 6. PWM-VID Analog Circuit Diagram

| Spec Description                                                                                 | Output Voltage Equation                                                                                            |

|--------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| N <sub>MAX</sub> : Total available voltage step number                                           | -                                                                                                                  |

| N: The step number of the specific $V_{\text{OUT}}$ , $N/N_{\text{MAX}}$ ratio equals duty cycle | -                                                                                                                  |

| V <sub>MAX</sub> : The output voltage of REFIN at one hundred percent duty cycle                 | $V_{\text{REF}} \times \frac{R_{\text{VREF2}}}{R_{\text{VREF2}} + (R_{\text{VREF1}} \parallel R_{\text{REFADJ}})}$ |

| V <sub>MIN</sub> : The output voltage of REFIN at zero percent duty cycle                        | $V_{\text{REF}} \times \frac{R_{VREF2} \parallel R_{REFADJ}}{R_{VREF1} + (R_{VREF2} \parallel R_{REFADJ})}$        |

| V <sub>STEP</sub> : The resolution of the voltage step                                           | $\frac{V_{MAX} - V_{MIN}}{N_{MAX}}$                                                                                |

| V <sub>OUT</sub> : The output voltage at REFIN                                                   | $V_{MIN} + N \times V_{STEP}$                                                                                      |

| f <sub>SWVID</sub> : The dynamic voltage VID frequency                                           | $\frac{1}{t_{\scriptscriptstyle U} \times N_{\scriptscriptstyle \rm MAX}}$                                         |

Table 4. REFIN Dynamic Range

There will be some ripple voltage at REFIN due to the nature of the PWM and filter. The error amplifier at REFIN will be able to tolerate a reasonable amount of Ripple Voltage.

### 12.2 Integrating the Buffer

Figure 7 shows a dynamic voltage control circuit with the integrated buffer. This defines the implementation of the VID and REFADJ functions.

Figure 7. Integrated Buffer Circuit

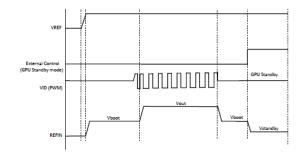

### 12.3 Timing Diagram

Figure 8 contains the details of the timing diagram. After VCC powers up, the controller generates the  $V_{REF}$ . REFIN settles at  $V_{BOOT}$  before the GPU drives the VID pin. After the GPU powers up,  $V_{BOOT}$  control will be pulled low by software. At the same time the VID is driven by a PWM signal, moving REFIN into the normal operating mode. When the GPU is going to standby, software will tri-state VID and  $V_{BOOT}$  control, and an external control will enable  $R_{STANDBY}$ .

Figure 8. Time Diagram

#### 12.4 Standby Mode

Standby mode keeps the GPU in a low voltage state (in the range of 0.3V) for the quick recovery. As the GPU steps into the standby mode, the resistor  $R_{STANDBY}$  and the switch Q6 (parallel to the  $R_{VREF2}$  and  $R_{BOOT}$ ) set the standby voltage. The accuracy of the reference voltage in the standby mode could be reduced from the normal operating mode. Refer to Figure 9 for the illustration of the standby voltage.

Figure 9. Illustration for Standby Mode and Adjustable V<sub>BOOT</sub> Setting

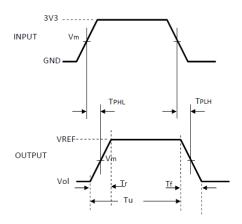

### 12.5 Voltage Waveform and Propagation Delay

Figure 10. The Behavior of the Buffer

## **Application Information (Cont.)**

#### 12.6 Electrical Characteristics

| Parameters                    | Sym                  | Min | Тур              | Max | Unit | Notes                                                |

|-------------------------------|----------------------|-----|------------------|-----|------|------------------------------------------------------|

| Buffer Supply Voltage         | -                    | -   | V <sub>REF</sub> | _   | V    | _                                                    |

| Unit Pulse Width              | tu                   | -   | 27               | -   | ns   | Configurable                                         |

| Buffer Output Rise Time       | t <sub>R</sub>       | -   | 5                | -   | ns   | _                                                    |

| Buffer Output Fall Time       | t <sub>F</sub>       | -   | 5                | -   | ns   | _                                                    |

| Rising and Falling Edge Delay | Δt                   | -   | _                | 0.5 | ns   | $\Delta t =  t_R - t_F $                             |

| Propagation Delay             | t <sub>PD</sub>      | -   | 10               | -   | ns   | t <sub>PD</sub> =t <sub>PHL</sub> =t <sub>PLH</sub>  |

| Propagation Delay Error       | Δt <sub>PD</sub>     | -   | _                | 0.5 | ns   | Δt <sub>PD</sub> =t <sub>PHL</sub> -t <sub>PLH</sub> |

| Upper Resister                | R <sub>VREF1</sub>   | -   | 4.75             | -   | kΩ   | _                                                    |

| Lower Resister                | R <sub>VREF2</sub>   | -   | 4.22             | -   | kΩ   | _                                                    |

| Filter Resister               | R <sub>REFADJ</sub>  | -   | 6.34             | -   | kΩ   | _                                                    |

| Boot Mode Resister            | R <sub>BOOT</sub>    | -   | -                | -   | kΩ   | Project Specific                                     |

| Standby Mode Resister         | R <sub>STANDBY</sub> | -   | 1.07             | -   | kΩ   | _                                                    |

| Filter Capacitor              | C <sub>REFIN</sub>   | -   | 0.033            | -   | μF   | _                                                    |

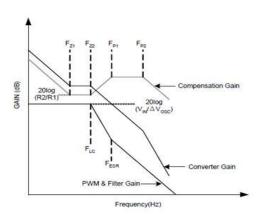

#### 13. PWM Compensation

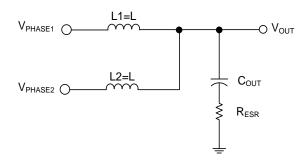

The output LC filter of a step down converter introduces a double pole, which contributes with -40dB/decade gain slope and 180 degrees phase shift in the control loop. A compensation network among COMP, VSNS, and  $V_{OUT}$  should be added. The compensation network is shown in Figure 14. The output LC filters consist of the output inductors and output capacitors. For two-phase convertor, when assuming that  $V_{IN1} = V_{IN2} = V_{IN}$ , L1 = L2 = L, the transfer function of the LC filter is given by:

$$Gain_{LC} = \frac{1 + s \times R_{ESR} \times C_{OUT}}{s^2 \times (1/2)L \times C_{OUT} + s \times R_{ESR} \times C_{OUT} + 1}$$

The poles and zero of the transfer functions are:

$$f_{LC} = \frac{1}{2 \times \pi \times \sqrt{(1/2)L \times C_{OUT}}}$$

$$f_{ESR} = \frac{1}{2 \times \pi \times R_{ESR} \times C_{OUT}}$$

The  $f_{LC}$  is the double-pole frequency of the two-phase LC filters, and  $f_{ESR}$  is the frequency of the zero introduced by the ESR of the output capacitors.

Figure 11. The Output LC Filter

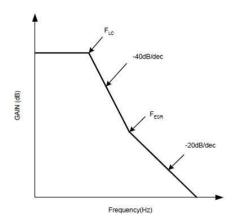

Figure 12. Frequency Response of the LC Filters

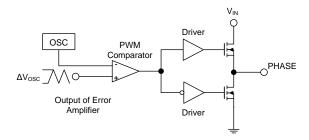

The PWM modulator is shown in Figure 13. The input is the output of the error amplifier and the output is the PHASE node. The transfer function of the PWM modulator is given by:

$$Gain_{\scriptscriptstyle PWM} = \frac{V_{\scriptscriptstyle IN}}{\Delta V_{\scriptscriptstyle OSC}}$$

Figure 13. The PWM Modulator

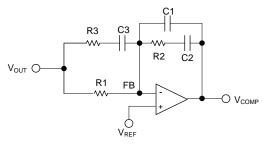

The compensation network is shown in Figure 14. It provides a close loop transfer function with the highest zero crossover frequency and sufficient phase margin. The transfer function of error amplifier is given by:

$$Gain_{AMP} = \frac{V_{COMP}}{V_{OUT}} = \frac{\frac{1}{sC1} / (R2 + \frac{1}{sC2})}{R1 / (R3 + \frac{1}{sC3})} = \frac{R1 + R3}{R1 \times R3 \times C1} \times \frac{(s + \frac{1}{R2 \times C2}) \times \{s + \frac{1}{(R1 + R3) \times C3}\}}{s(s + \frac{C1 + C2}{R2 \times C1 \times C2}) \times (s + \frac{1}{R3 \times C3})}$$

The pole and zero frequencies of the transfer function are:

$$f_{Z1} = \frac{1}{2 \times \pi \times R2 \times C2}$$

$$f_{z2} = \frac{1}{2 \times \pi \times (R1 + R3) \times C3}$$

$$f_{P1} = \frac{1}{2 \times \pi \times R2 \times (\frac{C1 \times C2}{C1 + C2})}$$

$$f_{P2} = \frac{1}{2 \times \pi \times R3 \times C3}$$

Figure 14. Compensation Network

The closed loop gain of the converter can be written as:

$$Gain_{\scriptscriptstyle LC} \times Gain_{\scriptscriptstyle PWM} \times Gain_{\scriptscriptstyle AMP}$$

Figure 15 shows the asymptotic plot of the closed loop converter gain, and the following guidelines will help to design the compensation network. Using the below guidelines will give a compensation similar to the curve plotted. A stable closed loop has a -20dB/decade slope and a phase margin greater than 45 degree.

- 1. Choose a value for R1, usually between  $1k\Omega$  and  $5k\Omega.$

- 2. Select the desired zero crossover frequency.

$$f_O = (1/5 \sim 1/10) \times f_{SW}$$

Use the following equation to calculate R2:

$$R2 = \frac{\Delta V_{OSC}}{V_{IN}} \times \frac{f_O}{f_{LC}} \times R1$$

3. Place the first zero  $f_{Z1}$  before the output LC filter double pole frequency  $f_{LC}$ .

$$f_{Z1} = 0.75 \times f_{LC}$$

Calculate the C2 by the equation:

$$C2 = \frac{1}{2 \times \pi \times R2 \times f_{LC} \times 0.75}$$

4. Set the pole at the ESR zero frequency f<sub>ESR</sub>:

$$f_{P1} = f_{ESR}$$

Calculate the C1 by the following equation:

$$C1 = \frac{C2}{2 \times \pi \times R2 \times C2 \times f_{ESR} - 1}$$

5. Set the second pole  $f_{P2}$  at the half of the switching frequency and also set the second zero  $f_{Z2}$  at the output LC filter double pole  $f_{LC}$ . The compensation gain should not exceed the error amplifier open loop gain. Check the compensation gain at  $f_{P2}$  with the capabilities of the error amplifier.

$$f_{P2} = 0.5 \times f_{SW}$$

$$f_{Z2} = f_{LC}$$

Combine the two equations will get the following component calculations:

$$R3 = \frac{R1}{\frac{f_{SW}}{2 \times f_{LC}} - 1}$$

$$C3 = \frac{1}{\pi \times R3 \times f_{SW}}$$

Figure 15. Converter Gain and Frequency

#### 14. Output Inductor Selection

The duty cycle (D) of a buck converter is the function of the input voltage and output voltage. Once an output voltage is fixed, it can be written as:

$$D = V_{OUT} / V_{IN}$$

For two-phase converter, the inductor value (L) determines the sum of the two inductor ripple current,  $\Delta I_{P-P}$ , and affects the load transient response. Higher inductor value reduces the output capacitors' ripple current and induces lower output ripple voltage. The ripple current can be approximated by:

$$\Delta I_{P-P} = \frac{V_{IN} - 2V_{OUT}}{f_{SW} \times L} \times \frac{V_{OUT}}{V_{IN}}$$

Where f<sub>SW</sub> is the switching frequency of the regulator.

Although the inductor value and frequency are increased and the ripple current and voltage are reduced, a tradeoff exists between the inductor's ripple current and the regulator load transient response time. A smaller inductor will give the regulator a faster load transient response at the expense of higher ripple current. Increasing the switching frequency (f<sub>SW</sub>) also reduces the ripple current and voltage, but it will increase the switching loss of the MOSFETs and the power dissipation of the converter. The maximum ripple current occurs at the maximum input voltage. A good starting point is to choose the ripple current to be approximately 30% of the maximum output current. Once the inductance value has been chosen, select an inductor that is capable of carrying the required peak current without going into saturation. In some types of inductors, especially core that is made of ferrite, the ripple current will increase abruptly when it saturates. This results in a larger output ripple voltage.

#### 15. Output Capacitor Selection

Output voltage ripple and the transient voltage deviation are factors that have to be taken into consideration when selecting output capacitors. Higher capacitor value and lower ESR reduce the output ripple and the load transient drop. Therefore, selecting high performance low ESR capacitors is recommended for switching regulator applications. In addition to high frequency noise related to MOSFET turn-on and turn-off, the output voltage ripple includes the capacitance voltage drop  $\Delta V_{COUT}$  and ESR voltage drop  $\Delta V_{ESR}$  caused by the AC peak-to-peak sum of the inductor's current. The ripple voltage of output capacitors can be represented by:

$$\Delta V_{COUT} = \frac{\Delta I_{P-P}}{8 \times C_{OUT} \times f_{SW}}$$

$$\Delta V_{FSR} = \Delta I_{P-P} \times R_{FSR}$$

These two components constitute a large portion of the total output voltage ripple. In some applications, multiple capacitors have to be paralleled to achieve the desired ESR value. If the output of the converter has to support another load with high pulsating current, more capacitors are needed in order to reduce the equivalent ESR and suppress the voltage ripple to a tolerable level. A small decoupling capacitor in parallel for bypassing the noise is also recommended, and the voltage rating of the output capacitors must be considered too.

To support a load transient that is faster than the switching frequency, more capacitors are needed for reducing the voltage excursion during load step change.

For getting same load transient response, the output capacitance of two-phase converter only needs to be around half of output capacitance of single-phase converter.

Another aspect of the capacitor selection is that the total AC current going through the capacitors has to be less than the rated RMS current specified on the capacitors in order to prevent the capacitor from overheating.

#### 16. Input Capacitor Selection

Use small ceramic capacitors for high frequency decoupling and bulk capacitors to supply the surge current needed each time high-side MOSFET turns on. Place the small ceramic capacitors physically close to the MOSFETs and between the drain of high-side MOSFET and the source of low-side MOSFET.

The important parameters for the bulk input capacitor are the voltage rating and the RMS current rating. For reliable operation, select the bulk capacitor with voltage and current ratings above the maximum input voltage and largest RMS current required by the circuit. The capacitor voltage rating should be at least 1.25 times greater than the maximum input voltage and a voltage rating of 1.5 times is a conservative guideline. For two-phase converter, the RMS current of the bulk input capacitor is roughly calculated as the following equation:

$$I_{RMS} = \frac{I_{OUT}}{2} \times \sqrt{2D \times (1 - 2D)}$$

For a through hole design, several electrolytic capacitors may be needed. For surface mount design, solid tantalum capacitors can be used, but caution must be exercised with regard to the capacitor surge current rating.

#### 17. MOSFET Selection

The AP3598A requires two N-Channel power MOSFETs on each phase. These should be selected based upon R<sub>DS(ON)</sub>, gate supply requirements and thermal management requirements.

In high current applications, the MOSFET power dissipation, package selection, and heatsink are the dominant design factors. The power dissipation includes two loss components: conduction loss and switching loss.

The conduction losses are the largest component of power dissipation for both the high-side and the low-side MOSFETs. These losses are distributed between the two MOSFETs according to duty factor (see the equations below). Only the high-side MOSFET has switching losses since the low-side MOSFETs body diode or an external Schottky rectifier across the lower MOSFET clamps the switching node before the synchronous rectifier turns on. These equations assume linear voltage current transitions and do not adequately model power loss due to the reverse-recovery of the low-side MOSFET body diode. The gate-charge losses are dissipated by AP3598A and don't heat the MOSFETs. However, large gate-charge increases the switching interval tsw, which increases the high-side MOSFET switching losses. Ensure that all MOSFETs are within their maximum junction temperature at high ambient temperature by calculating the temperature rise according to package thermal resistance specifications. A separate heatsink may be necessary depending upon MOSFET power, package type, ambient temperature and air flow.

For the high-side and low-side MOSFETs, the losses are approximately given by the following equations:

Phigh-side=Iout<sup>2</sup>x(1+Tc) xRds(on)xD+ 0.5xIoutxVinxtswxfsw

$P_{LOW-SIDE} = I_{OUT}^2 \times (1 + T_C) \times (R_{DS(ON)}) \times (1 - D)$

Where  $I_{OUT}$  is the load current,  $T_C$  is the temperature dependency of  $R_{DS(ON)}$ ,  $f_{SW}$  is the switching frequency,  $t_{SW}$  is the switching interval, D is the duty cycle.

Note that both MOSFETs have conduction losses while the high-side MOSFET includes an additional transition loss. The switching interval,  $t_{SW}$ , is the function of the reverse transfer capacitance  $C_{RSS}$ . The (1+T<sub>C</sub>) term is a factor in the temperature dependency of the  $R_{DS(ON)}$  and can be extracted from the " $R_{DS(ON)}$  vs. Temperature" curve of the power MOSFET.

#### 18. Layout Consideration

In any high switching frequency converter, a correct layout is important to ensure proper operation of the regulator.

With power devices switching at higher frequency, the resulting current transient will cause voltage spike across the interconnecting impedance and parasitic circuit elements. As an example, consider the turn-off transition of the PWM MOSFET. Before turn-off condition, the MOSFET is carrying the full load current. During turn-off, current stops flowing in the MOSFET and is freewheeling by the low side MOSFET and parasitic diode. Any parasitic inductance of the circuit generates a large voltage spike during the switching interval. In general, using short and wide printed circuit traces should minimize interconnecting impedances and the magnitude of voltage spike.

Besides, signal and power grounds are to be kept separating and finally combined using ground plane construction or single point grounding. The best tie-point between the signal ground and the power ground is at the negative side of the output capacitor on each channel, where there is less noise. Noisy traces beneath the IC are not recommended. Figure 16 illustrates the layout, with bold lines indicating high current paths; these traces must be short and wide. Components along the bold lines should be placed close together. Below is a checklist for your layout:

- 1. Keep the switching nodes (HGATEx, LGATEx, BOOTx, and PHASEx) away from sensitive small signal nodes since these nodes are fast moving signals. Therefore, keep traces to these nodes as short as possible and there should be no other weak signal traces in parallel with theses traces on any layer.

- 2. The signals going through theses traces have both high dv/dt and high dl/dt with high peak charging and discharging current. The traces from the gate drivers to the MOSFETs (HGATEx and LGATEx) should be short and wide.

- 3. Place the source of the high-side MOSFET and the drain of the low-side MOSFET as close as possible. Minimizing the impedance with wide layout plane between the two pads reduces the voltage bounce of the node. In addition, the large layout plane between the drain of the MOSFETs (V<sub>IN</sub> and PHASEx nodes) can get better heat sinking.

- 4. For experiment result of accurate current sensing, the current sensing components are suggested to place close to the inductor part. To avoid the noise interference, the current sensing trace should be away from the noisy switching nodes.

- 5. Decoupling capacitors, the resistor-divider, and the boot capacitor should be close to their pins. (For example, place the decoupling ceramic capacitor as close as possible to the drain of the high-side MOSFET). The input bulk capacitors should be close to the drain of the high-side MOSFET, and the output bulk capacitors should be close to the loads.

- 6. The input capacitor's ground should be close to the grounds of the output capacitors and the low-side MOSFET.

- 7. Locate the resistor-divider close to the VREF and REFIN pins to minimize the high impedance trace. In addition, VSNS pin traces can't be close to the switching signal traces (HGATEx, LGATEx, BOOTx, and PHASEx).

Figure 16. The Layout of AP3598A

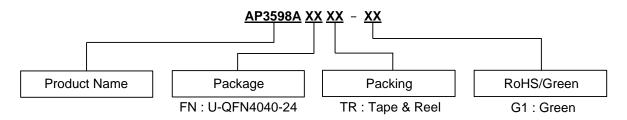

## **Ordering Information**

| Package      | Temperature Range | Part Number    | Marking ID | Packing          |

|--------------|-------------------|----------------|------------|------------------|

| U-QFN4040-24 | -40 to +85°C      | AP3598AFNTR-G1 | B3F        | 5000/Tape & Reel |

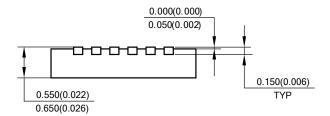

## **Marking Information**

(Top View)

↑B3F YWW • MXX First Line: Logo and Marking ID Second and Third Lines: Date Code

Y: Year

WW: Work Week of Molding M: Assembly House Code XX: 7<sup>th</sup> and 8<sup>th</sup> Digits of Batch No.

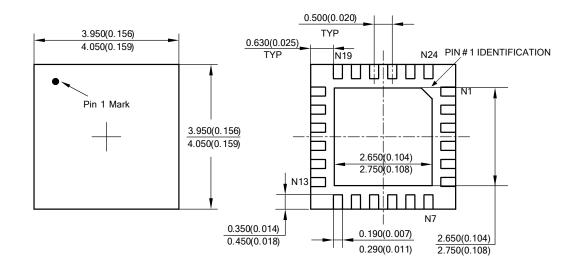

## Package Outline Dimensions (All dimensions in mm(inch).)

#### (1) Package Type: U-QFN4040-24 (Type B)

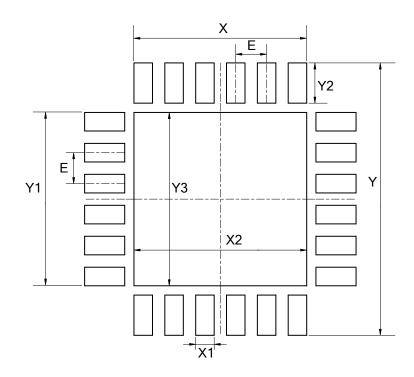

## **Suggested Pad Layout**

(1) Package Type: U-QFN4040-24 (Type B)

| Dimensions | X=Y1<br>(mm)/(inch)  | Y<br>(mm)/(inch) | X1<br>(mm)/(inch) | Y2<br>(mm)/(inch) |

|------------|----------------------|------------------|-------------------|-------------------|

| Value      | 2.840/0.112          | 4.300/0.169      | 0.340/0.013       | 0.600/0.024       |

| Dimensions | X2=Y3<br>(mm)/(inch) | E<br>(mm)/(inch) | -                 | -                 |

| Value      | 2.800/0.110          | 0.500/0.020      | _                 | _                 |

#### **IMPORTANT NOTICE**

DIODES INCORPORATED MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS TO THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).

Diodes Incorporated and its subsidiaries reserve the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. Diodes Incorporated does not assume any liability arising out of the application or use of this document or any product described herein; neither does Diodes Incorporated convey any license under its patent or trademark rights, nor the rights of others. Any Customer or user of this document or products described herein in such applications shall assume all risks of such use and will agree to hold Diodes Incorporated and all the companies whose products are represented on Diodes Incorporated website, harmless against all damages.

Diodes Incorporated does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel. Should Customers purchase or use Diodes Incorporated products for any unintended or unauthorized application, Customers shall indemnify and hold Diodes Incorporated and its representatives harmless against all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized application.

Products described herein may be covered by one or more United States, international or foreign patents pending. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks.

This document is written in English but may be translated into multiple languages for reference. Only the English version of this document is the final and determinative format released by Diodes Incorporated.

#### **LIFE SUPPORT**

Diodes Incorporated products are specifically not authorized for use as critical components in life support devices or systems without the express written approval of the Chief Executive Officer of Diodes Incorporated. As used herein:

- A. Life support devices or systems are devices or systems which:

- 1. are intended to implant into the body, or

- 2. support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in significant injury to the user.

- B. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or to affect its safety or effectiveness.

Customers represent that they have all necessary expertise in the safety and regulatory ramifications of their life support devices or systems, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of Diodes Incorporated products in such safety-critical, life support devices or systems, notwithstanding any devices- or systems-related information or support that may be provided by Diodes Incorporated. Further, Customers must fully indemnify Diodes Incorporated and its representatives against any damages arising out of the use of Diodes Incorporated products in such safety-critical, life support devices or systems.

Copyright © 2014, Diodes Incorporated

www.diodes.com