AKM

# AP3440ABN182

# High-Accurate Step-Down DC-DC Converter with 4.5A MOSFET

#### 1. General Description

The AP3440 is a synchronous rectification PWM control step-down DC-DC converter of the current mode with excellent transient load response characteristics. The recommended operational temperature ranges from -40 to 125°C. It is capable for automotive use that demands high reliability. The AP3440 supports input voltage from 4.1V to 5.5V and its output voltage is 1.822V. It integrates power MOSFET corresponding to a 4.5A output current at the maximum. The AP3440 is equipped with Output Over-Current Protection, Output Over-Voltage Protection, Under Voltage Lock Out, Thermal Protection, and Power-good function. The AP3440 is housed in a 28-pin QFN0505 package.

#### 2. Features

Input Voltage Range Output Voltage

: 1.822V (+1.81%, −1.87%) k : 4.5A

: 4.1V ~ 5.5V

Output Current Peak Oscillation Frequency

y : 2100 kHz

External Synchronization (supporting Master/Slave mode), Frequency Range : 1800kHz ~ 2250kHz Integrated Power MOSFET

Soft Start Function

High-Accurate Power-Good Function

Discharging Function of Output Capacitor

Protection Functions: Over Current, Over Voltage, Under Voltage Lock Out and Thermal Protections Recommended Operational Temperature Range: Ta=-40 ~ 125°C

Package: 28-pin QFN0505 (Exposed Pad and Pins are Plated)

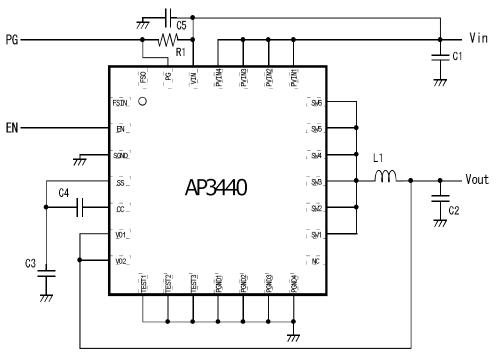

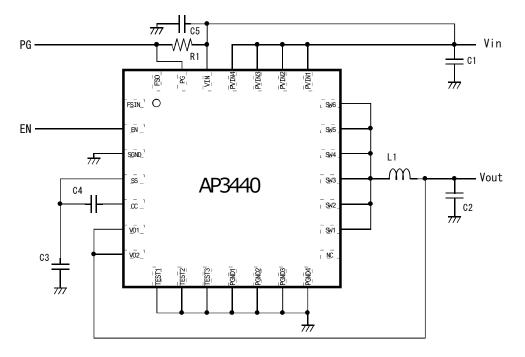

Figure 1. Application

# 3. Table of Contents

| 1.  | General Description                                    | 1  |

|-----|--------------------------------------------------------|----|

| 2.  | Features                                               | 1  |

| 3.  | Table of Contents                                      | 2  |

| 4.  | Block Diagram                                          | 3  |

| 5.  | Ordering Guide                                         | 3  |

| 6.  | Pin Configurations and Functions                       | 4  |

|     | Pin Configurations                                     | 4  |

|     | Functions                                              | 4  |

| 7.  | Absolute Maximum Ratings                               | 5  |

| 8.  | Recommended Operating Conditions                       | 6  |

| 9.  | Electrical Characteristics                             | 7  |

| 10. | Timing Chart                                           | 8  |

| 11. | Functional Descriptions                                | 9  |

|     | 11.1 Normal Operation                                  | 9  |

|     | 11.2 External Synchronous Function                     |    |

|     | 11.3 Extrenal Synchronous Clock Output                 |    |

|     | 11.4 Power Good Function                               |    |

|     | 11.5 Over Voltage Protection (OVP)                     |    |

|     | 11.6 Under Voltage Lockout (UVLO)                      |    |

|     | 11.7 Over Current Protection (OCL: Over Current Limit) |    |

|     | 11.8 Thermal Protection (TSD: Thermal Shut Down)       |    |

|     | 11.9 Output Capacitor Discharge                        |    |

|     | Typical Characteristics                                |    |

|     | Recommended External Circuits                          |    |

| 14. | Layout Examples                                        |    |

|     | VIN Capacitor Wiring                                   |    |

|     | GND Wiring                                             |    |

|     | Switching Node Connection                              |    |

| 45  | Soft Start Capacitor                                   |    |

| 15. |                                                        |    |

|     | Outline Dimensions                                     |    |

|     | Recommended Land                                       |    |

| 16  | Marking Revision History                               |    |

|     | REVISION HISTORY                                       |    |

| 10  |                                                        | 17 |

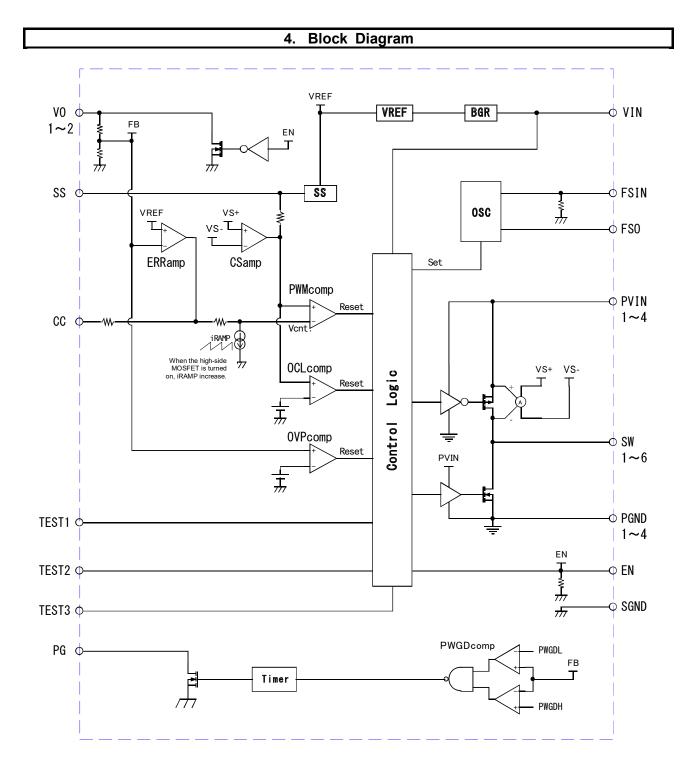

Figure 2. Block Diagram

| 5. Ordering Guide                                           |        |           |                      |  |  |  |  |

|-------------------------------------------------------------|--------|-----------|----------------------|--|--|--|--|

| Part # Output Voltage Operational Temperature Range Package |        |           |                      |  |  |  |  |

| AP3440ABN182                                                | 1.822V | -40 ~ 125 | 28-pin QFN(0505) SFS |  |  |  |  |

#### 6. Pin Configurations and Functions

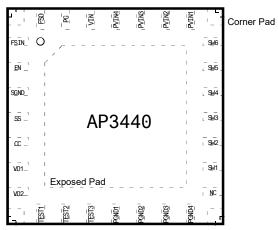

#### ■ Pin Configurations

Figure 3. Pin Configurations

#### Functions

| No | Pin       | I/O | Description                                                                                                                                                                                                                      |  |  |  |  |

|----|-----------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1  | FSIN      | I   | External Synchronous Clock Input<br>Drive frequency is synchronized to the external synchronous clock frequency. This pin<br>should be open or connected to the SGND and PGND pins when not using external<br>synchronous clock. |  |  |  |  |

| 2  | EN        | Ι   | Enable Signal Input<br>The AP3440 starts operation by "H" signal input.                                                                                                                                                          |  |  |  |  |

| 3  | SGND      | I   | Signal Ground                                                                                                                                                                                                                    |  |  |  |  |

| 4  | SS        | I/O | Soft Start Pin<br>Connect a capacitor between this pin and the SGND for soft start time adjustment.                                                                                                                              |  |  |  |  |

| 5  | СС        | 0   | Error Amplifier Output<br>Connect a capacitor and a resistor between this pin and the SS pin for phase<br>compensation of the error amplifier.                                                                                   |  |  |  |  |

| 6  | VO1       |     | Output Voltage Feedback                                                                                                                                                                                                          |  |  |  |  |

| 7  | VO2       | I   | Output voltage is adjusted to meet a setting value.                                                                                                                                                                              |  |  |  |  |

| 8  | TEST1     | I   | - Test Pin                                                                                                                                                                                                                       |  |  |  |  |

| 9  | TEST2     | I   |                                                                                                                                                                                                                                  |  |  |  |  |

| 10 | TEST3     | I   | Connect to the PGND and SGND pins.                                                                                                                                                                                               |  |  |  |  |

| 11 | PGND1     | -   |                                                                                                                                                                                                                                  |  |  |  |  |

| 12 | PGND2     |     | Devuer Crevind                                                                                                                                                                                                                   |  |  |  |  |

| 13 | PGND3     |     | Power Ground                                                                                                                                                                                                                     |  |  |  |  |

| 14 | PGND4     | _   |                                                                                                                                                                                                                                  |  |  |  |  |

| 15 | NC        |     | Open Pin                                                                                                                                                                                                                         |  |  |  |  |

| 16 | SW1       | 0   |                                                                                                                                                                                                                                  |  |  |  |  |

| 17 | SW2       | 0   |                                                                                                                                                                                                                                  |  |  |  |  |

| 18 | SW3       | 0   | Internal MOSEET Switching Output                                                                                                                                                                                                 |  |  |  |  |

| 19 | SW4       | 0   | Internal MOSFET Switching Output                                                                                                                                                                                                 |  |  |  |  |

| 20 | SW5       | 0   | ]                                                                                                                                                                                                                                |  |  |  |  |

| 21 | SW6       | 0   |                                                                                                                                                                                                                                  |  |  |  |  |

| 22 | PVIN1     | I   |                                                                                                                                                                                                                                  |  |  |  |  |

| 23 | PVIN2     | Ι   | Power Supply Input                                                                                                                                                                                                               |  |  |  |  |

| 24 | PVIN3     |     |                                                                                                                                                                                                                                  |  |  |  |  |

| 25 | PVIN4     | Ι   |                                                                                                                                                                                                                                  |  |  |  |  |

| 26 | VIN       | Ι   | Control Power Input                                                                                                                                                                                                              |  |  |  |  |

| 27 | PG        | 0   | Power-Good Signal Output<br>Open drain output of the N-ch MOSFET. This output is off by power-good.                                                                                                                              |  |  |  |  |

| 28 | FSO       | 0   | External Synchronous Clock Output                                                                                                                                                                                                |  |  |  |  |

|    | Exposed P | ad  | Connect to the ground plane of the printed circuit board for heat dissipation.                                                                                                                                                   |  |  |  |  |

|    | Corner Pa | ıd  | Connect to the ground plane of the printed circuit board for the improvement of the solder junction strength.                                                                                                                    |  |  |  |  |

#### 7. Absolute Maximum Ratings

| Parameter                                                                  | Symbol      | Min. | Max.   | Unit |

|----------------------------------------------------------------------------|-------------|------|--------|------|

| Voltage between PGND1~4 and VIN,<br>PVIN1~4 or SW1~6                       | Vterm1      | -0.3 | +6.0   | V    |

| Voltage between SGND and FSIN, EN,<br>SS, CC, TEST1~3, PG, FSO, VO1 or VO2 | Vterm2      | -0.3 | +6.0   | V    |

| Voltage between SGND and PGND1~4                                           | Vterm3      | -0.3 | +0.3   | V    |

| Voltage between VIN and PVIN1~4                                            | Vterm4      | -0.3 | +0.3   | V    |

| Storage Ambient Temperature Range                                          | Tstg        | -40  | 150    | °C   |

| Junction Temperature                                                       | Tj          | -40  | 150    | °C   |

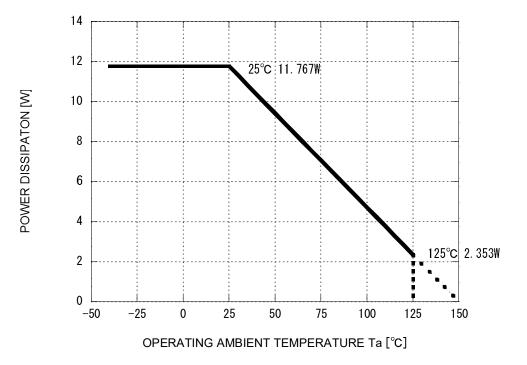

| Power Dissipation (Note 1) Ta=25°C                                         | Pd parallel |      | 11.767 | W    |

Note 1. Junction to Ambient Thermal Resistance Junction to Case Thermal Resistance Parallel Thermal Resistance (θ<sub>JA</sub>: 25%, θ<sub>JC</sub>: 75%)  $\theta_{JA} = 39.7^{\circ}C/W$  $\theta_{JC} = 0.93^{\circ}C/W$

$\theta_{(JA+JC)} = 10.63^{\circ}C /W$

Ambient temperature of 25°C using JEDEC 4L board. (114.3mm × 76.2mm)

Figure 4. Power Dissipation

WARNING: Operation at or beyond these limits may result in permanent damage to the device. Normal operation is not guaranteed at these extremes.

# 8. Recommended Operating Conditions

| Parameter                                                                                         | Symbol             | Min. | Тур. | Max. | Unit |

|---------------------------------------------------------------------------------------------------|--------------------|------|------|------|------|

| Input Voltage Range                                                                               | Vin                | 4.1  | -    | 5.5  | V    |

| Operation Ambient Temperature Range                                                               | Ta                 | -40  | -    | 125  | °C   |

| MOSFET Current Capacity on PG Output                                                              | I <sub>MOSON</sub> | -    | -    | 50   | mA   |

| External Synchronous Clock Frequency                                                              | F <sub>SYN</sub>   | 1800 | 2100 | 2250 | kHz  |

| External Synchronous Clock Frequency ("L" period)                                                 | T <sub>FSYNL</sub> | 100  | -    | 384  | ns   |

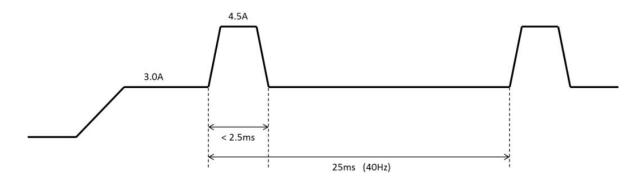

| Continuous Output Current (DC)                                                                    | I <sub>DC</sub>    | -    | -    | 3.0  | Α    |

| Output Current Peak<br>Maximum value of 10% duty in every 25ms.<br>90% Duty: 3A<br>10% Duty: 4.5A | I <sub>PEAK</sub>  | -    | -    | 4.5  | А    |

Figure 5. lout Profile

\* AKM assumes no responsibility for the usage beyond the conditions in this data sheet.

| 9. Electrical Characteristics                           |                     |        |           |              |         |                             |  |

|---------------------------------------------------------|---------------------|--------|-----------|--------------|---------|-----------------------------|--|

|                                                         | (VIN                | =5.05V | , Tj=-40° | C~150°(      | C, unle | ss otherwise specified)     |  |

| Parameter                                               | Symbol              | Min    | Тур       | Max          | Unit    | Condition                   |  |

| Output Voltage Accuracy (Note 5)                        | Vout                | 1.788  | 1.822     | 1.855        | V       |                             |  |

| VIN Pin Current (in operation)                          | Isupply             | -      | -         | 3            | mA      |                             |  |

| VIN Shut-down Current                                   | Ishd1               | -      | -         | 1            | uA      | Tj=25°C                     |  |

| PVIN Shut-down Current                                  | Ishd2               | -      | -         | 1            | uA      | Tj=25°C                     |  |

| Over Current Protection Threshold                       | OCL                 | 5.5    | 7.85      | 10.2         | Α       | Coil Peak Current           |  |

| Over Voltage Protection Threshold                       | OVP                 | 126    | 134       | 142          | %       | Vout ratio                  |  |

| Oscillation Frequency                                   | Freq                | 1950   | 2100      | 2250         | kHz     |                             |  |

| Soft Start Charging Current                             | lss                 | 24     | 30        | 36           | uA      |                             |  |

| Soft Start Finishing Threshold                          | Vss                 | 1.11   | 1.17      | 1.23         | V       |                             |  |

| Soft Start Time                                         | Tss                 | 2.1    | 3.9       | 6.7          | ms      | Css=0.1uF                   |  |

| High-side Minimum On-pulse                              | SWUMINon            | -      | -         | 85           | ns      |                             |  |

| Low-side Minimum On-pulse                               | SWLMINon            | -      | -         | 132          | ns      |                             |  |

| High-side On-resistance<br>of Internal Switching MOSFET | R <sub>DSON</sub> H | -      | 91        | 139          | fo: 0   | Include Cu wire<br>resistor |  |

| Low-side On-resistance<br>of Internal Switching MOSFET  | R <sub>DSON</sub> L | -      | 41        | 69           | rn.C    | Include Cu wire resistor    |  |

| Under Voltage Lock Out<br>Threshold(UVLO)               | VD                  | 3.8    | 3.95      | 4.1          | V       |                             |  |

| Output Voltage Monitoring<br>Threshold (H) (Note 5)     | PWGDH               | 1.873  | 1.905     | 1.936        | V       |                             |  |

| Output Voltage Monitoring<br>Threshold (L) (Note 5)     | PWGDL               | 1.734  | 1.763     | 1.792        | V       |                             |  |

| PG BAD Detection Time                                   | T <sub>RESET1</sub> | 1      | -         | 4.7          | us      |                             |  |

| PG GOOD Detection Time                                  | T <sub>RESET2</sub> | 8      | 10        | 12           | ms      |                             |  |

| PG Output MOSFET On-resistance                          | R <sub>MOSON</sub>  | -      | -         | 50           |         | Drain Current =20mA         |  |

| EN Pin Pull-down Resistance                             | R <sub>EN</sub>     | 60     | 100       | 140          | kΩ      |                             |  |

| EN Pin Input Voltage "H" (Note 2)                       | V <sub>SHDN</sub> H | 2.0    | -         | 5.5          | V       |                             |  |

| EN Pin Input Voltage "L" (Note 2)                       | V <sub>SHDN</sub> L | 0      | -         | 0.4          | V       |                             |  |

| MOSFET On-resistance<br>for EN Off Output Discharge     | R <sub>MOSON</sub>  | -      | -         | 200          |         | Discharging Current = 10mA  |  |

| Line Regulation (Note 3)                                | A.Mino              | -      | -         | 0.685        | %/V     | Vin=4.7~5.4V                |  |

| Load Regulation (Note 3)                                | 6N/Goad             | -      | -         | 0.3          | %       | lo=0.1~3.5A                 |  |

| Load Transient Response (Note 3)                        |                     |        |           | 0.0          |         |                             |  |

| Overshoot                                               | VtranO              | -      | -         | 35.3         | mV      | lo=2↔3.5A                   |  |

| Undershoot                                              |                     | _      | _         | 33.0         | mV      | Slew rate= 0.2A/us          |  |

| Thermal Protection Threshold<br>(Note 2, Note 4)        | Ttsd                | 155    | 175       | 200          | °C      |                             |  |

| Thermal Protection Hysteresis<br>(Note 2, Note 4)       | TSDhys              | 1      | 25        | 50           | °C      |                             |  |

| FSIN Pin Pull-down Resistance                           | R <sub>FSIN</sub>   | 350    | 500       | 650          | kO      |                             |  |

| FSIN Pin Input Voltage "H" (Note 2)                     | V <sub>SHDN</sub> H | 2.0    |           | 5.5          | V       |                             |  |

| FSIN Pin Input Voltage "L" (Note 2)                     | V <sub>SHDN</sub> L | 0      |           | 0.4          | V       |                             |  |

| Note 2 Guaranteed by design                             | - s⊓DN              |        | I         | <b>U</b> . 1 |         | l                           |  |

Note 2. Guaranteed by design.

Note 3. A reference value with the recommended circuit.

Note 4. This function is to protect the IC from an overheat situation. Functional operation of the device including its reliability is not guaranteed under the condition that the overheat status beyond the specifications continues.

Note 5. There is no overlap between Output Voltage and Output Voltage Monitoring since these values are interlocked by tracking.

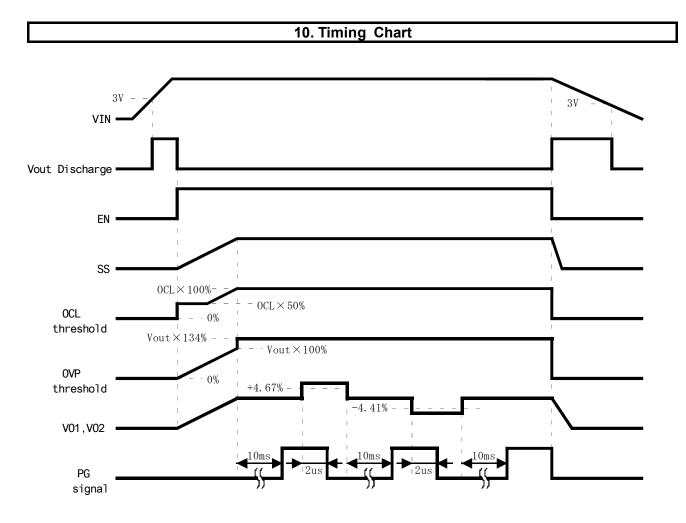

Figure 6. Timing Chart

The AP3440 begin start-up in Soft-Start mode when "H" signal is input to the EN pin while the VIN pin is 4.1V or more. Soft-start operation is controlled by over current and voltage limitations. Each of thresholds change according to the conditions shown below and return to OCL and OVP threshold values at Normal Operation after Soft-Start is completed.

|                 | During Soft-Start                                       | Normal Operation   |

|-----------------|---------------------------------------------------------|--------------------|

| Over Current    | SS Pin Voltage < 0.6V: OCL (7.85Atyp) × 1/2             |                    |

| Limit (OCL)     | SS Pin Voltage ≥ 0.6V: OCL (7.85Atyp) × SS voltage/1.2V | OCL (7.85Atyp)     |

| threshold       |                                                         |                    |

| Over Voltage    | SS Pin Voltage: Vout/1.2V                               |                    |

| Protection(OVP) |                                                         | OVP (Vout×134%typ) |

| threshold       |                                                         |                    |

An open drain Nch-MOSFET of the PG pin(hereinafter called as PG\_MOS) is turned off when 10ms is passed after  $V_{OUT}$  became a level within power-good range following soft-start completion. The PG\_MOS is turned on if  $V_{OUT}$  is out of the power-good range for more than 2us continuously. PG\_MOS is turned off in 10ms after  $V_{OUT}$  is returned into power-good range again.

#### 11. Functional Descriptions

#### 11.1 Normal Operation

The AP3440 operates by PWM control in current mode. It integrates feedback resistances and the output voltage is 1.822V typ. A potential difference of the feedback output voltage of the VO1/2 pin and internal reference voltage is amplified by the error amplifier to set a target value of the coil current. An internal current sense circuit detects the coil current. Synchronous rectification is executed as the internal high-side P-channel MOSFET is turned off and low-side N-channel MOSFET is turned on when the coil current reaches a target value after internal high-side P-channel MOSFET is turned on.

# **11.2 External Synchronous Function**

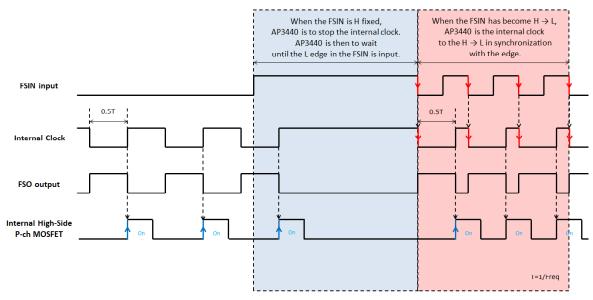

The AP3440 synchronizes the driving frequency to a falling edge ("H"  $\rightarrow$  "L") of input clock to the FSIN pin. Frequency of the input clock must be in a range from 1800kHz to 2250kHz and the "L" period should be in a range from 100ns to 384ns. When using an internal oscillation frequency, the FSIN pin should be open or connected to the SGND and PGND pins. Note that switching operation is stopped if the FSIN pin is fixed to "H" level since a falling edge of the internal clock is not generated.

Figure 7. External Synchronous Timing Chart

# 11.3 Extrenal Synchronous Clock Output

An inverted clock of the driving frequency generated internally is output from the FSO pin. The AP3440 outputs an inverted clock of the external synchronous clock when inputting an external synchronous clock.

# **11.4 Power Good Function**

The AP3440 has a power good function that indicates the output voltage status by the PG pin. The PG pin must be pulled up by a resistor connected to the VIN pin since the PG pin is an open drain output of N-channel MOSFET (hereinafter PG\_MOS). The PG-MOS is turned off when the output voltage is in a range of PWGDH and PWGDL for 10ms. The PG-MOS is turned on when the output voltage is out of the power-good range for more than 2us continuously. The PG-MOS is always ON during power-off status and soft start operation. Refer to the section "9. Electrical Characteristics" about PWGDH and PWGDL.

# 11.5 Over Voltage Protection (OVP)

The output voltage Vout is limited so as not to rise drastically from the setting value.

| Protections               | About on Product Function |                                   |

|---------------------------|---------------------------|-----------------------------------|

| FIDIECIIONS               | Condition                 | Action                            |

| OVP                       | 1/2000 > 1240/(100)       | High-side P-ch Power MOSFET = OFF |

| (Over Voltage Protection) |                           | Low-side N-ch Power MOSFET = ON   |

#### 11.6 Under Voltage Lockout (UVLO)

The AP3440 stops operation when the input voltage drops to a level that is out of operational range.

| Protections                     | About on Product Function |                                                                                                                |

|---------------------------------|---------------------------|----------------------------------------------------------------------------------------------------------------|

| FIDIECIDIIS                     | Condition                 | Action                                                                                                         |

| UVLO<br>(Under Voltage Lockout) | VIN ≤ 4.1V                | DCDC internal circuit is powered off.<br>High-side P-ch Power MOSFET = OFF<br>Low-side N-ch Power MOSFET = OFF |

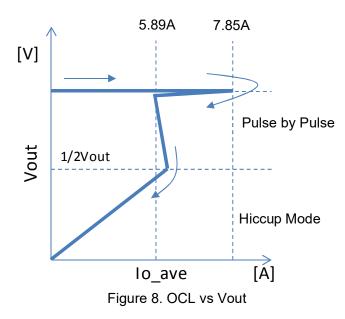

#### 11.7 Over Current Protection (OCL: Over Current Limit)

Current of high-side P-ch power MOSFET is monitored and limited so that the output current does not become too high.

| Protections          | About on Product Function |                                   |

|----------------------|---------------------------|-----------------------------------|

| FIDIECIIDIIS         | Condition                 | Action                            |

| OCL                  | Current of High-side P-ch | High-side P-ch Power MOSFET = OFF |

| (Over Current Limit) | power MOSFET ≥7.85A       | Low-side N-ch Power MOSFET = ON   |

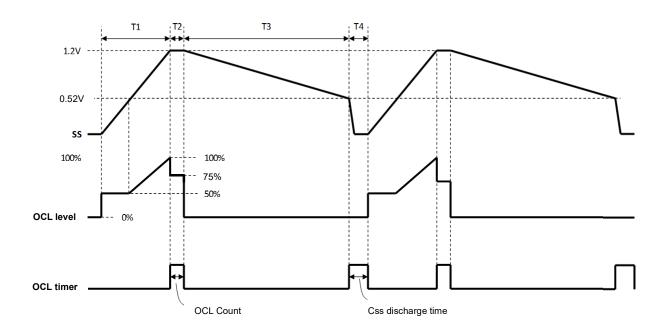

The AP3440 changes OCL level to 75% when OCL is detected 2 cycles continuously. In case that Vout decreases farther, the AP3440 goes into hiccup mode.

The AP3440 starts hiccup operation that repeats ON and OFF if over current statement is kept for 6 cycles while the output voltage is less than half of the setting value. This counter will be reset if one of the 6 cycles does not meet the over current condition. In the OFF period of hiccup operation, the soft-start capacitor is discharged by 1.5uA to reduce the voltage at the SS pin.

The AP3440 starts soft start operation after grounding the SS pin for 32 cycles of the internal clock when the SS pin voltage drops to 0.52V. Hiccup operation is disabled during soft start.

- T1: Soft Start Setting Time. Charging current is 30uA.

- T2: 6 count time of drive frequency. Hiccup mode detection is executed only in this period.

- T3: Discharging Time of Soft Start Capacitor. Discharge current is 1.5uA. This time is equivalent to 12 times as Soft Start Setting Time T1.

- T4: Discharging Time of Soft Start Capacitor. (32 cycles of Internal Clock)

#### 11.8 Thermal Protection (TSD: Thermal Shut Down)

The AP3440 stops operation if the chip temperature overs 175°C (typ) for protection.

| Protections                   | About on Product Function      |                                                                                                      |  |

|-------------------------------|--------------------------------|------------------------------------------------------------------------------------------------------|--|

| FIDIECIIONS                   | Condition                      | Action                                                                                               |  |

| TSD<br>(Thermal Shut<br>down) | Chip Temperature ≥ 175°C (typ) | High-side P-ch Power MOSFET = OFF<br>Low-side N-ch Power MOSFET = OFF<br>DC-DC Circuit Block is OFF. |  |

The AP3440 restarts by soft start when the chip temperature drops.

#### **11.9 Output Capacitor Discharge**

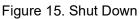

The output capacitor is discharged by the N-ch power MOSFET for discharge that are built into the VO terminal ( $200\Omega$ max) is turned on , if there is no "H" signal input to the EN pin while the VIN voltage is 3V or more. The N-ch power MOSFET for output discharge( $200\Omega$ max) is turned off by "H" signal input to the EN pin or when the VIN voltage becomes less than 3V.

Figure 14. Load Transient

#### 13. Recommended External Circuits

Figure 16. Typical Application

| Parameter                    | Symbol | Effective Value | Nominal Value | Manufacturer           |

|------------------------------|--------|-----------------|---------------|------------------------|

| Input Ceramic Capacitor      | C1     | 10uF ±30%       | -             | -                      |

| Output Ceramic Capacitor     | C2     | 50uF ±30%       | -             | -                      |

| Soft Start Capacitor         | C3     | 0.1uF ±30%      | -             | -                      |

| Phase Compensation Capacitor | C4     | 2.2nF ±30%      | -             | -                      |

| Input Ceramic Capacitor      | C5     | 1uF ±30%        |               |                        |

| PWGD Pull-up Resistance      | R1     | 47kΩ ±10%       | -             | -                      |

| Power Inductor               | L      | -               | 2.2uH         | CLF7045NIT-2R2N-D(TDK) |

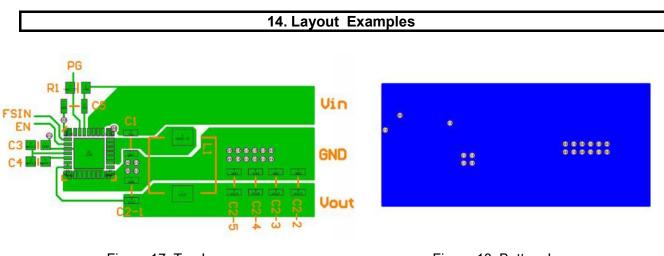

Figure 17. Top Layer

#### ■ VIN Capacitor Wiring

A capacitor connected between a VIN pin and the ground should be as close as possible to a VIN pin or a PGND pin.

#### ■ GND Wiring

GND plane should be large as much as possible. The output capacitor and input capacitor should be connected to the same ground plane. The heat dissipation pad on the back surface of the package should be connected to the GND. Each of the PGND1~4 and SGND pins should be connected to the ground directly under the device.

#### ■ Switching Node Connection

Wirings for switching node that are connected to SW pins should be short and thick.

#### ■ Soft Start Capacitor

A VREF capacitor between the SS pin and the ground should be connected as close as possible to the AP3440.

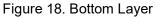

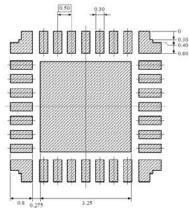

# 15. Package

#### Outline Dimensions

#### 28-pin QFN0505 (Unit: mm)

Figure 19. Outline Dimensions

# Recommended Land

# (Unit: mm)

Figure 20. Recommended Land Pattern

#### Marking

- 1. Marketing Code : AP3440

- 2. Output Voltage Code : 182

: Y

- 3. Date Code

- 82

- : XXX Week

- Administration Code

Figure 20. AP3440 Marking

# 16. Revision History

| Date (Y/M/D) | Revision | Page | Contents      |

|--------------|----------|------|---------------|

| 17/02/08     | 00       | -    | First Edition |

#### IMPORTANT NOTICE

- 0. Asahi Kasei Microdevices Corporation ("AKM") reserves the right to make changes to the information contained in this document without notice. When you consider any use or application of AKM product stipulated in this document ("Product"), please make inquiries the sales office of AKM or authorized distributors as to current status of the Products.

- 1. All information included in this document are provided only to illustrate the operation and application examples of AKM Products. AKM neither makes warranties or representations with respect to the accuracy or completeness of the information contained in this document nor grants any license to any intellectual property rights or any other rights of AKM or any third party with respect to the information in this document. You are fully responsible for use of such information contained in this document in your product design or applications. AKM ASSUMES NO LIABILITY FOR ANY LOSSES INCURRED BY YOU OR THIRD PARTIES ARISING FROM THE USE OF SUCH INFORMATION IN YOUR PRODUCT DESIGN OR APPLICATIONS.

- 2. The Product is neither intended nor warranted for use in equipment or systems that require extraordinarily high levels of quality and/or reliability and/or a malfunction or failure of which may cause loss of human life, bodily injury, serious property damage or serious public impact, including but not limited to, equipment used in nuclear facilities, equipment used in the aerospace industry, medical equipment, equipment used for automobiles, trains, ships and other transportation, traffic signaling equipment, equipment used to control combustions or explosions, safety devices, elevators and escalators, devices related to electric power, and equipment used in finance-related fields. Do not use Product for the above use unless specifically agreed by AKM in writing.

- 3. Though AKM works continually to improve the Product's quality and reliability, you are responsible for complying with safety standards and for providing adequate designs and safeguards for your hardware, software and systems which minimize risk and avoid situations in which a malfunction or failure of the Product could cause loss of human life, bodily injury or damage to property, including data loss or corruption.

- 4. Do not use or otherwise make available the Product or related technology or any information contained in this document for any military purposes, including without limitation, for the design, development, use, stockpiling or manufacturing of nuclear, chemical, or biological weapons or missile technology products (mass destruction weapons). When exporting the Products or related technology or any information contained in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. The Products and related technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 5. Please contact AKM sales representative for details as to environmental matters such as the RoHS compatibility of the Product. Please use the Product in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. AKM assumes no liability for damages or losses occurring as a result of noncompliance with applicable laws and regulations.

- 6. Resale of the Product with provisions different from the statement and/or technical features set forth in this document shall immediately void any warranty granted by AKM for the Product and shall not create or extend in any manner whatsoever, any liability of AKM.

- 7. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of AKM.