# INTEGRATED CIRCUITS

# DATA SHEET

# SAA7182; SAA7183 Digital Video Encoder (EURO-DENC)

Preliminary specification Supersedes data of 1995 Sep 19 File under Integrated Circuits, IC22 1996 Jul 08

**SAA7182; SAA7183**

#### **FEATURES**

- CMOS 5 V device

- Digital PAL/NTSC/SECAM encoder

- · System pixel frequency 13.5 MHz

- Accepts MPEG decoded data on 8-bit wide input port. Input data format Cb, Y, Cr etc. or Y and Cb, Cr on 16 lines ("CCIR 656")

- Three DACs for CVBS, Y and C operating at 27 MHz with 10-bit resolution

- Three DACs for RGB operating at 27 MHz with 9-bit resolution, RGB sync on CVBS and Y

- · CVBS, Y, C and RGB output simultaneously

- Closed captioning and teletext encoding including sequencer and filter

- · On-chip YUV to RGB matrix

- Fast I<sup>2</sup>C-bus control port (400 kHz)

- · Encoder can be master or slave

- Programmable horizontal and vertical input synchronization phase

- · Programmable horizontal sync output phase

- Internal Colour Bar Generator (CBG)

- Overlay with Look-Up Tables (LUTs) 8 × 3 bytes

- Macrovision Pay-per-View protection system as option, also used for RGB output

This applies to SAA7183 only. The device is protected by USA patent numbers 461603, 4577216 and 4819098 and other intellectual property rights.

Use of the Macrovision anti-copy process in the device is licensed for non-commercial home use only. Reverse engineering or disassembly is prohibited. Please contact your nearest Philips Semiconductor sales office for more information

- Controlled rise/fall times of output syncs and blanking

- · Down-mode of DACs

- · PLCC84 package.

#### **GENERAL DESCRIPTION**

The SAA7182; SAA7183 encodes digital YUV video data to an NTSC, PAL, SECAM CVBS or S-Video signal and also RGB.

The circuit accepts CCIR compatible YUV data with 720 active pixels per line in 4 : 2 : 2 multiplexed formats, for example MPEG decoded data. It includes a sync/clock generator and on-chip Digital-to-Analog Converters (DACs).

The circuit is compatible to the DIG-TV2 chip family.

### **QUICK REFERENCE DATA**

| SYMBOL           | PARAMETER                                                                          | MIN. | TYP.      | MAX. | UNIT |

|------------------|------------------------------------------------------------------------------------|------|-----------|------|------|

| $V_{DDA}$        | analog supply voltage                                                              | 4.75 | 5.0       | 5.25 | V    |

| $V_{DDD}$        | digital supply voltage                                                             | 4.75 | 5.0       | 5.25 | V    |

| I <sub>DDA</sub> | analog supply current                                                              | _    | 90        | 110  | mA   |

| I <sub>DDD</sub> | digital supply current                                                             | _    | 220       | 250  | mA   |

| Vi               | input signal voltage levels                                                        | TT   | L compati | ble  |      |

| $V_{o(p-p)}$     | analog output signal voltages Y, C, CVBS and RGB without load (peak-to-peak value) | _    | 2         | _    | V    |

| R <sub>L</sub>   | load resistance                                                                    | 80   | _         | _    | Ω    |

| ILE              | LF integral linearity error                                                        | _    | _         | ±2   | LSB  |

| DLE              | LF differential linearity error                                                    | _    | _         | ±1   | LSB  |

| T <sub>amb</sub> | operating ambient temperature                                                      | 0    | _         | +70  | °C   |

# Digital Video Encoder (EURO-DENC)

SAA7182; SAA7183

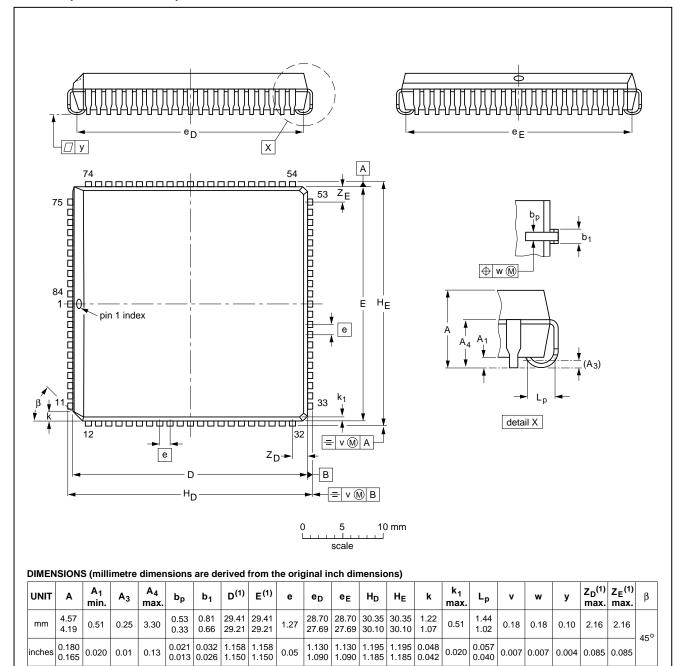

### **ORDERING INFORMATION**

| TYPE NUMBER  |        | PACKAGE                               |          |

|--------------|--------|---------------------------------------|----------|

| I TPE NUMBER | NAME   | DESCRIPTION                           | VERSION  |

| SAA7182WP    | PLCC84 | plastic leaded chip carrier; 84 leads | SOT189-2 |

| SAA7183WP    | PLCC84 | plastic leaded chip carrier; 84 leads | SOT189-2 |

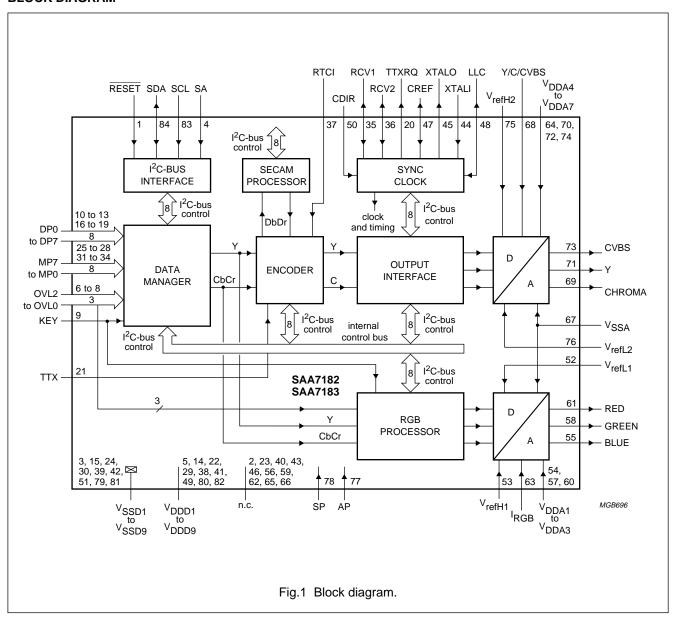

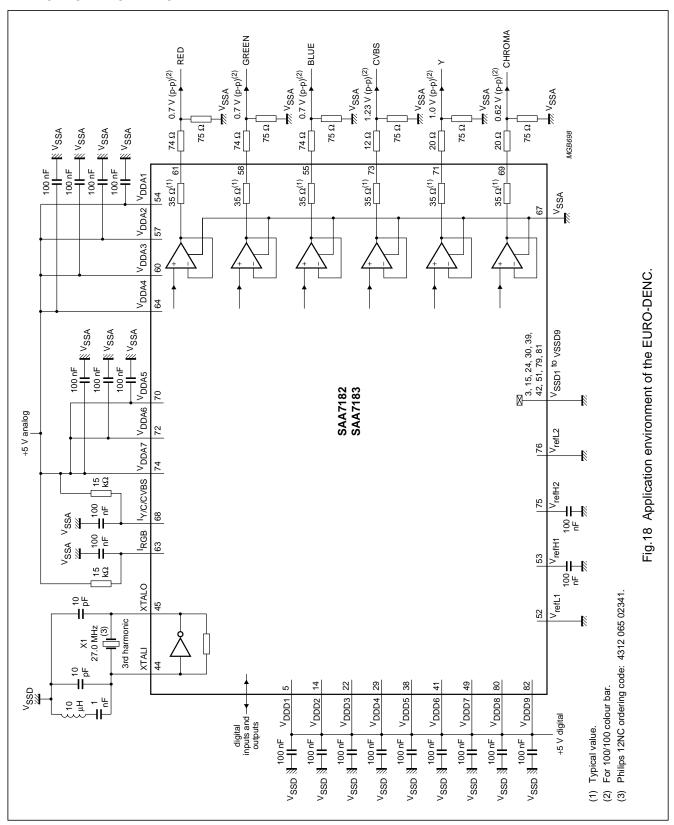

#### **BLOCK DIAGRAM**

# Digital Video Encoder (EURO-DENC)

SAA7182; SAA7183

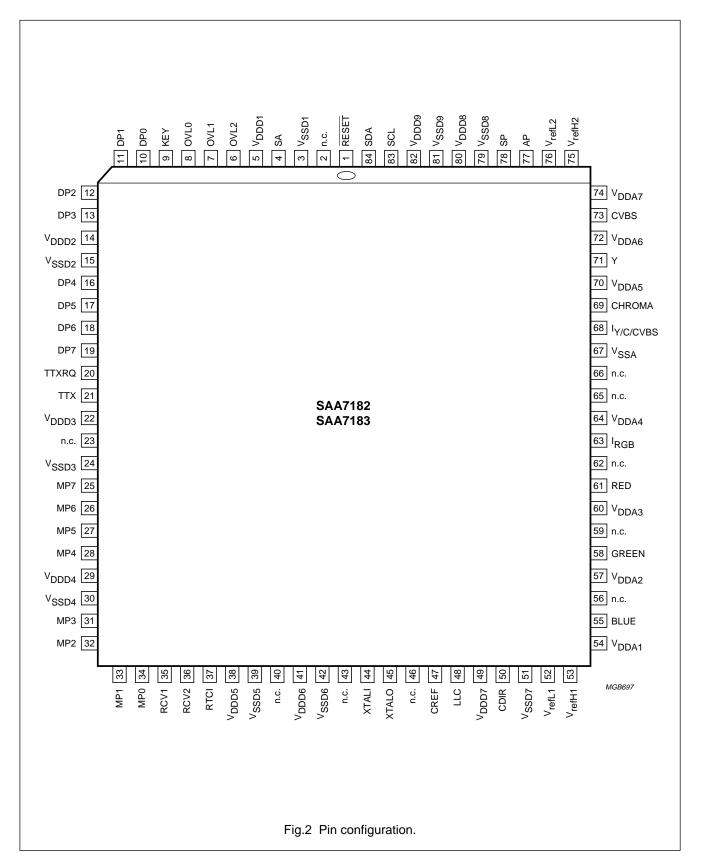

# **PINNING**

| SYMBOL            | PIN | DESCRIPTION                                                                                                                                                                                       |

|-------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESET             | 1   | Reset input, active LOW. After reset is applied, all digital I/Os are in input mode. The I <sup>2</sup> C-bus receiver waits for the START condition.                                             |

| n.c.              | 2   | not connected                                                                                                                                                                                     |

| V <sub>SSD1</sub> | 3   | digital ground 1                                                                                                                                                                                  |

| SA                | 4   | The I <sup>2</sup> C-bus slave address select pin. LOW: slave address = 88H, HIGH = 8CH.                                                                                                          |

| V <sub>DDD1</sub> | 5   | digital supply voltage 1                                                                                                                                                                          |

| OVL2              | 6   |                                                                                                                                                                                                   |

| OVL1              | 7   | 3-bit overlay data input. This is the index for the internal look-up table.                                                                                                                       |

| OVL0              | 8   |                                                                                                                                                                                                   |

| KEY               | 9   | Key input for OVL. When HIGH it selects OVL input.                                                                                                                                                |

| DP0               | 10  |                                                                                                                                                                                                   |

| DP1               | 11  |                                                                                                                                                                                                   |

| DP2               | 12  | Lower 4 bits of the data port. Input for multiplexed Cb, Cr data if 16 line input mode is used.                                                                                                   |

| DP3               | 13  |                                                                                                                                                                                                   |

| V <sub>DDD2</sub> | 14  | digital supply voltage 2                                                                                                                                                                          |

| V <sub>SSD2</sub> | 15  | digital ground 2                                                                                                                                                                                  |

| DP4               | 16  |                                                                                                                                                                                                   |

| DP5               | 17  |                                                                                                                                                                                                   |

| DP6               | 18  | Upper 4 bits of the data port. Input for multiplexed Cb, Cr data if 16 line input mode is used.                                                                                                   |

| DP7               | 19  |                                                                                                                                                                                                   |

| TTXRQ             | 20  | Teletext request output, indicating when the bitstream is valid.                                                                                                                                  |

| TTX               | 21  | Teletext bitstream input.                                                                                                                                                                         |

| $V_{DDD3}$        | 22  | digital supply voltage 3                                                                                                                                                                          |

| n.c.              | 23  | not connected                                                                                                                                                                                     |

| V <sub>SSD3</sub> | 24  | digital ground 3                                                                                                                                                                                  |

| MP7               | 25  | Upper 4 bits of MPEG port. It is an input for "CCIR 656" style multiplexed Cb, Y, Cr data, or                                                                                                     |

| MP6               | 26  | input for Y data only, if 16 line input mode is used.                                                                                                                                             |

| MP5               | 27  |                                                                                                                                                                                                   |

| MP4               | 28  |                                                                                                                                                                                                   |

| V <sub>DDD4</sub> | 29  | digital supply voltage 4                                                                                                                                                                          |

| V <sub>SSD4</sub> | 30  | digital ground 4                                                                                                                                                                                  |

| MP3               | 31  | Lower 4 bits of MPEG port. It is an input for "CCIR 656" style multiplexed Cb, Y, Cr data, or                                                                                                     |

| MP2               | 32  | input for Y data only, if 16 line input mode is used.                                                                                                                                             |

| MP1               | 33  |                                                                                                                                                                                                   |

| MP0               | 34  |                                                                                                                                                                                                   |

| RCV1              | 35  | Raster Control 1 for video port. This pin receives/provides a VS/FS/FSEQ signal.                                                                                                                  |

| RCV2              | 36  | Raster Control 2 for video port. This pin provides an HS pulse of programmable length or receives an HS pulse.                                                                                    |

| RTCI              | 37  | Real Time Control Input. If the LLC clock is provided by an <i>SAA7111</i> or <i>SAA7151B</i> , RTCI should be connected to the RTCO pin of the respective decoder to improve the signal quality. |

SAA7182; SAA7183

| SYMBOL                | PIN | DESCRIPTION                                                                                                                                                                                |

|-----------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $V_{DDD5}$            | 38  | digital supply voltage 5                                                                                                                                                                   |

| V <sub>SSD5</sub>     | 39  | digital ground 5                                                                                                                                                                           |

| n.c.                  | 40  | not connected                                                                                                                                                                              |

| $V_{DDD6}$            | 41  | digital supply voltage 6                                                                                                                                                                   |

| V <sub>SSD6</sub>     | 42  | digital ground 6                                                                                                                                                                           |

| n.c.                  | 43  | not connected                                                                                                                                                                              |

| XTALI                 | 44  | Crystal oscillator input (from crystal). If the oscillator is not used, this pin should be connected to ground.                                                                            |

| XTALO                 | 45  | Crystal oscillator output (to crystal).                                                                                                                                                    |

| n.c.                  | 46  | not connected                                                                                                                                                                              |

| CREF                  | 47  | Clock Reference signal. This is the clock qualifier for DIG-TV2 compatible signals.                                                                                                        |

| LLC                   | 48  | Line-Locked Clock. This is the 27 MHz master clock for the encoder. The I/O direction is set by the CDIR pin.                                                                              |

| $V_{DDD7}$            | 49  | digital supply voltage 7                                                                                                                                                                   |

| CDIR                  | 50  | Clock direction. If the CDIR input is HIGH, the circuit receives a clock and optional CREF signal, otherwise if CDIR is LOW CREF and LLC are generated by the internal crystal oscillator. |

| V <sub>SSD7</sub>     | 51  | digital ground 7                                                                                                                                                                           |

| V <sub>refL1</sub>    | 52  | Lower reference voltage 1 input for the RGB DACs, connect to V <sub>SSA</sub> .                                                                                                            |

| V <sub>refH1</sub>    | 53  | Upper reference voltage 1 input for the RGB DACs, connect via 100 nF capacitor to V <sub>SSA</sub> .                                                                                       |

| V <sub>DDA1</sub>     | 54  | Analog supply voltage 1 for the RGB DACs.                                                                                                                                                  |

| BLUE                  | 55  | Analog output of the BLUE component.                                                                                                                                                       |

| n.c.                  | 56  | not connected                                                                                                                                                                              |

| $V_{DDA2}$            | 57  | Analog supply voltage 2 for the RGB DACs.                                                                                                                                                  |

| GREEN                 | 58  | Analog output of the GREEN component.                                                                                                                                                      |

| n.c.                  | 59  | not connected                                                                                                                                                                              |

| $V_{DDA3}$            | 60  | Analog supply voltage 3 for the RGB DACs.                                                                                                                                                  |

| RED                   | 61  | Analog output of the RED component.                                                                                                                                                        |

| n.c.                  | 62  | not connected                                                                                                                                                                              |

| I <sub>RGB</sub>      | 63  | Current input for RGB amplifiers, connected via 15 k $\Omega$ resistor to V <sub>DDA</sub> .                                                                                               |

| $V_{DDA4}$            | 64  | Analog supply voltage 4 for the Y/C/CVBS DACs.                                                                                                                                             |

| n.c.                  | 65  | not connected                                                                                                                                                                              |

| n.c.                  | 66  | not connected                                                                                                                                                                              |

| V <sub>SSA</sub>      | 67  | Analog ground for the DACs.                                                                                                                                                                |

| I <sub>Y/C/CVBS</sub> | 68  | Current input for the Y/C/CVBS amplifiers, connected via 15 k $\Omega$ resistor to V <sub>DDA</sub> .                                                                                      |

| CHROMA                | 69  | Analog output of the chrominance signal.                                                                                                                                                   |

| $V_{DDA5}$            | 70  | Analog supply voltage 5 for the Y/C/CVBS DACs.                                                                                                                                             |

| Υ                     | 71  | Analog output of the luminance signal.                                                                                                                                                     |

| $V_{DDA6}$            | 72  | Analog supply voltage 6 for the Y/C/CVBS DACs.                                                                                                                                             |

| CVBS                  | 73  | Analog output of the CVBS signal.                                                                                                                                                          |

# Digital Video Encoder (EURO-DENC)

SAA7182; SAA7183

| SYMBOL             | PIN | DESCRIPTION                                                                                                 |

|--------------------|-----|-------------------------------------------------------------------------------------------------------------|

| V <sub>DDA7</sub>  | 74  | Analog supply voltage 6 for the Y/C/CVBS DACs.                                                              |

| V <sub>refH2</sub> | 75  | Upper reference voltage 2 input for the Y/C/CVBS DACs, connected via 100 nF capacitor to V <sub>SSA</sub> . |

| V <sub>refL2</sub> | 76  | Lower reference voltage 2 input for the Y/C/CVBS DACs, connect to V <sub>SSA</sub> .                        |

| AP                 | 77  | Test pin. Connected to digital ground for normal operation.                                                 |

| SP                 | 78  | Test pin. Connected to digital ground for normal operation.                                                 |

| V <sub>SSD8</sub>  | 79  | digital ground 8                                                                                            |

| V <sub>DDD8</sub>  | 80  | digital supply voltage 8                                                                                    |

| V <sub>SSD9</sub>  | 81  | digital ground 9                                                                                            |

| V <sub>DDD9</sub>  | 82  | digital supply voltage 9                                                                                    |

| SCL                | 83  | I <sup>2</sup> C-bus serial clock input.                                                                    |

| SDA                | 84  | I <sup>2</sup> C-bus serial data input/output.                                                              |

SAA7182; SAA7183

# Digital Video Encoder (EURO-DENC)

SAA7182; SAA7183

#### **FUNCTIONAL DESCRIPTION**

The digital video encoder (EURO-DENC) encodes digital luminance and colour difference signals into analog CVBS and simultaneously S-Video signals. NTSC-M, PAL B/G and SECAM standards and sub-standards are supported.

Both interlaced and non-interlaced operation is possible for all standards.

In addition to RED, GREEN and BLUE converted components, the dematrixed YUV input is available on three separate analog outputs.

The basic encoder function consists of subcarrier generation and colour modulation also insertion of synchronization signals. Luminance and chrominance signals are filtered in accordance with the standard requirements of RS-170-A and "CCIR 624".

For ease of analog post filtering the signals are twice oversampled with respect to the pixel clock before digital-to-analog conversion.

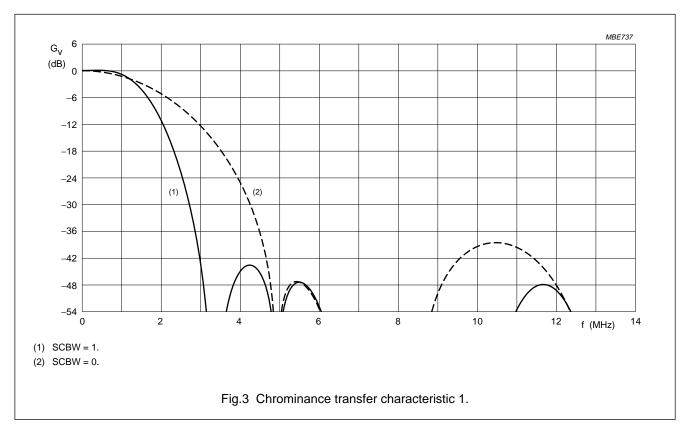

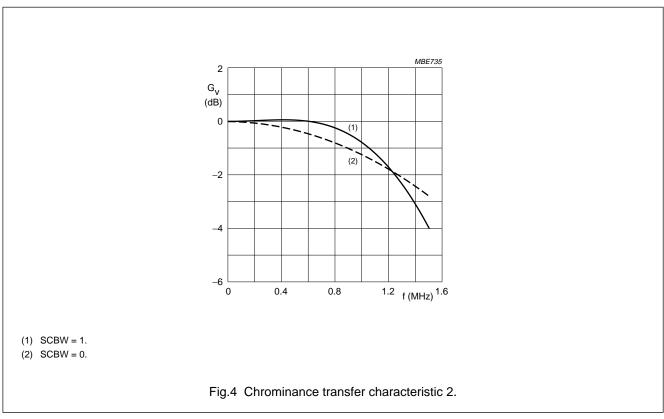

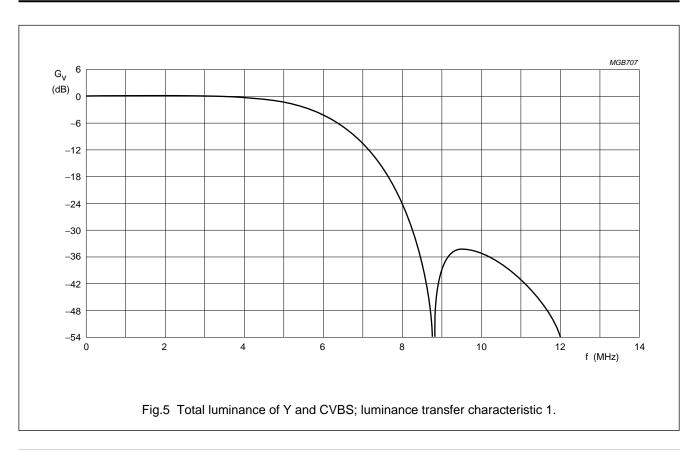

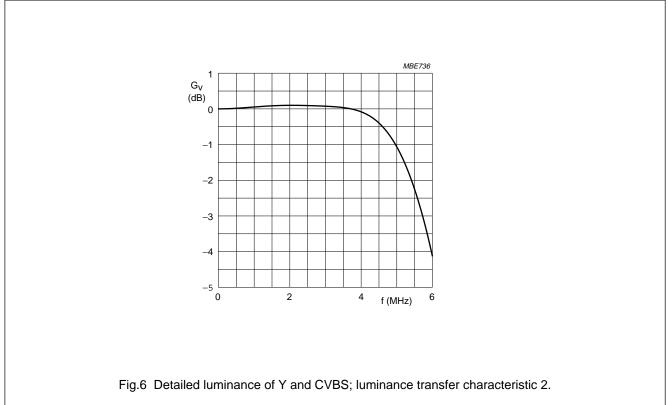

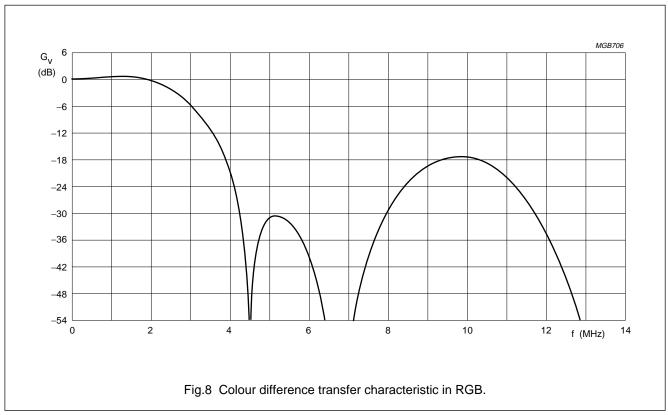

For total filter transfer characteristics see Figs 3, 4, 5, 6, 7 and 8. The DACs for Y, C and CVBS are realized with full 10-bit resolution, DACs for RGB are with 9-bit resolution.

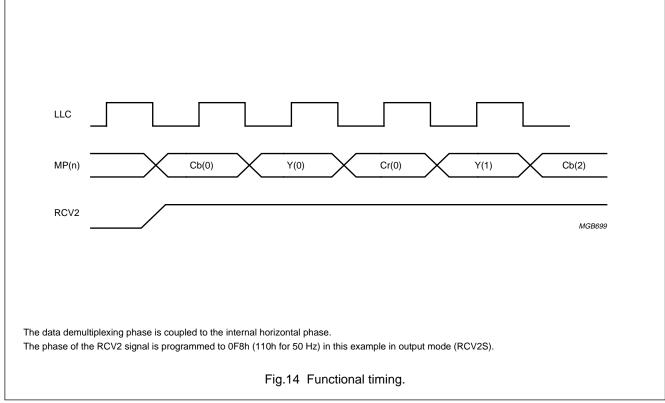

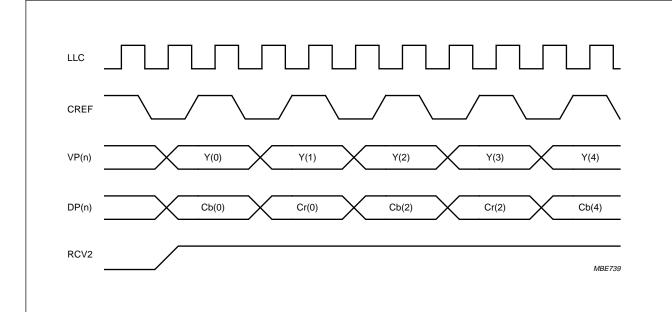

The MPEG port (MP) accept 8 lines multiplexed Cb-Y-Cr data.

The 8-bit multiplexed Cb-Y-Cr formats are "CCIR 656" (D1 format) compatible, but the SAV, EAV etc. codes are not decoded.

Alternatively, 8-bits Y on MP port and 8-bit multiplexed Cb, Cr on DP port can be chosen as input.

A crystal-stable master clock (LLC) of 27 MHz, which is twice the CCIR line-locked pixel clock of 13.5 MHz, needs to be supplied externally. Optionally, a crystal oscillator input/output pair of pins and an on-chip clock driver is provided.

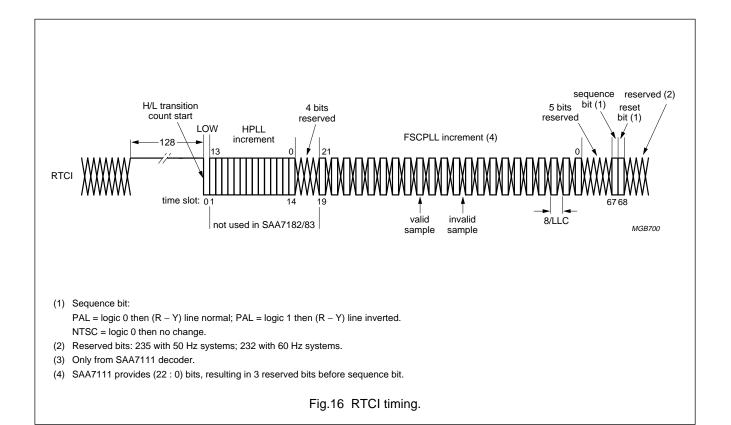

It is also possible to connect a Philips Digital Video Decoder (SAA7111 or SAA7151B) in conjunction with a CREF clock qualifier to EURO-DENC. Via RTCI pin connected to RTCO of a decoder, information concerning actual subcarrier, PAL-ID (see "data sheet SAA7111") definite subcarrier phase can be inserted.

The EURO-DENC synthesizes all necessary internal signals, colour subcarrier frequency, and synchronization signals, from that clock. The encoder is always timing master for the MPEG port (MP), but it can additionally be configured as slave with respect to the RCV trigger inputs.

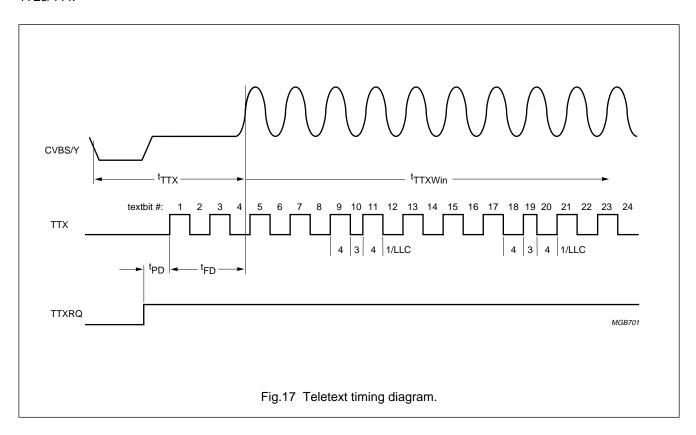

European teletext encoding is supported if an appropriate teletext bitstream is applied to the TTX pin.

The IC also contains Closed Caption and Extended Data Services Encoding (Line 21), and supports anti-taping signal generation in accordance with Macrovision; it also supports overlay via KEY and three control bits by a  $24 \times 8$  LUT.

A number of possibilities are provided for setting of different video parameters such as:

Black and blanking level control

Colour subcarrier frequency

Variable burst amplitude etc.

During reset ( $\overline{\text{RESET}}$  = LOW) and after reset is released, all digital I/O stages are set to input mode. A reset forces the I<sup>2</sup>C-bus interface to abort any running bus transfer and sets register 3A to 03H, register 61 to 06H and registers 6BH and 6EH to 00H. All other control registers are not influenced by a reset.

### Data manager

In the data manager, real time arbitration on the data stream to be encoded is performed.

Depending on the polarity of pin KEY, the MP input (or MP/DP input) or OVL input are selected to be encoded to CVBS and Y/C signals, and output as RGB.

KEY controls OVL entries of a programmable LUT for encoded signals and for RGB output. The common KEY switching signal can be disabled by software for the signals to be encoded (Y, C and CVBS), such that OVL will appear on RGB outputs, but not on Y, C and CVBS.

OVL input under control of KEY can be also used to insert decoded teletext information or other on-screen data.

Optionally, the OVL colour LUTs located in this block, can be read out in a pre-defined sequence (8 steps per active video line), achieving, for example, a colour bar test pattern generator without need for an external data source. The colour bar function is only under software control.

# Digital Video Encoder (EURO-DENC)

SAA7182; SAA7183

#### **Encoder**

VIDEO PATH

The encoder generates out of Y, U and V baseband signals luminance and colour subcarrier output signals, suitable for use as CVBS or separate Y and C signals.

Luminance is modified in gain and in offset (latter programmable in a certain range to enable different black level set-ups). After having been inserted a fixed synchronization level, in accordance with standard composite synchronization schemes, and blanking level, programmable also in a certain range to allow for manipulations with Macrovision anti-taping, additional insertion of AGC super-white pulses, programmable in height, is supported.

In order to enable easy analog post filtering, luminance is interpolated from 13.5 MHz data rate to 27 MHz data rate, providing luminance in 10-bit resolution. This filter is also used to define smoothed transients for synchronization pulses and blanking period. For transfer characteristic of the luminance interpolation filter see Figs 5 and 6.

Chrominance is modified in gain (programmable separately for U and V), standard dependent burst is inserted, before baseband colour signals are interpolated from 6.75 MHz data rate to 27 MHz data rate. One of the interpolation stages can be bypassed, thus providing a higher colour bandwidth, which can be made use of for Y/C output. For transfer characteristics of the chrominance interpolation filter see Figs 3 and 4.

The amplitude of inserted burst is programmable in a certain range, suitable for standard signals and for special effects. Behind the succeeding quadrature modulator, colour in 10-bit resolution is provided on subcarrier.

The numeric ratio between Y and C outputs is in accordance with set standards.

#### TELETEXT INSERTION AND ENCODING

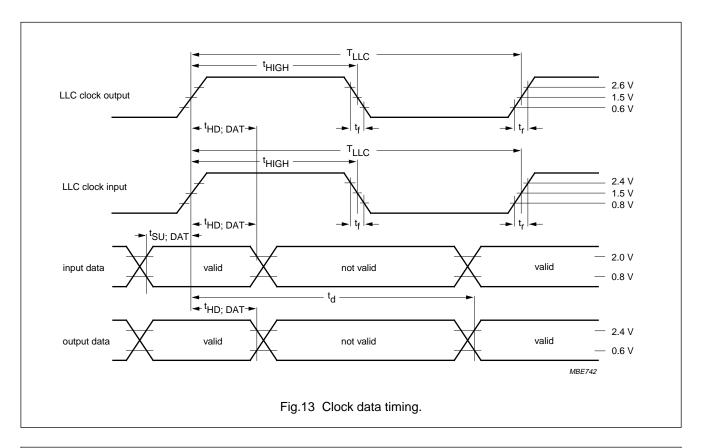

Pin TTX receives a teletext bitstream sampled at the LLC clock, each teletext bit is carried by four or three LLC samples.

Phase variant interpolation is achieved on this bitstream in the internal teletext encoder, providing sufficient small phase jitter on the output text lines.

TTXRQ provides a fully programmable request signal to the teletext source, indicating the insertion period of bitstream at lines selectable independently for both fields. The internal insertion window for text is set to 360 teletext bits including clock run-in bits. For protocol and timing see Fig.17.

#### **CLOSED CAPTION ENCODER**

Using this circuit, data in accordance with the specification of Closed Caption or Extended Data Service, delivered by the control interface, can be encoded (Line 21). Two dedicated pairs of bytes (two bytes per field), each pair preceded by run-in clocks and framing code, are possible.

The actual line number where data is to be encoded in, can be modified in a certain range.

Data clock frequency is in accordance with definition for NTSC-M standard 32 times horizontal line frequency.

Data LOW at the output of the DACs corresponds to 0 IRE, data HIGH at the output of the DACs corresponds to approximately 50 IRE.

It is also possible to encode Closed Caption Data for 50 Hz field frequencies at 32 times horizontal line frequency.

ANTI-TAPING (SAA7183 ONLY)

For more information contact your nearest Philips Semiconductors sales office.

#### **RGB** processor

This block contains a dematrix in order to produce RED, GREEN and BLUE signals to be fed to a SCART plug.

Before Y, Cb, Cr signals are dematrixed, 2 times oversampling for luminance and 4 times oversampling for colour difference signals is performed. For transfer curves of luminance and colour difference components of RGB see Figs 7 and 8.

### **SECAM** processor

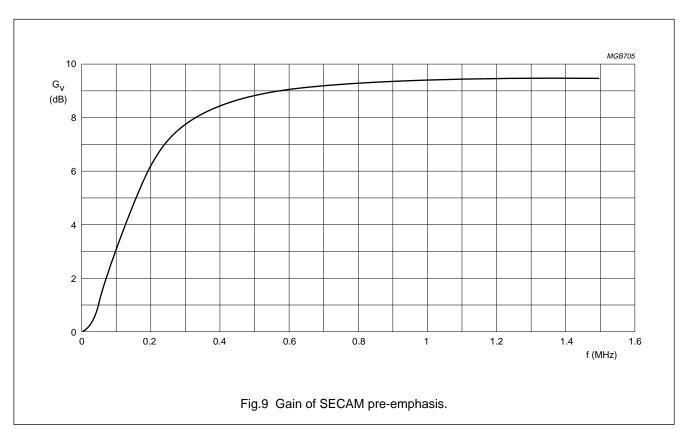

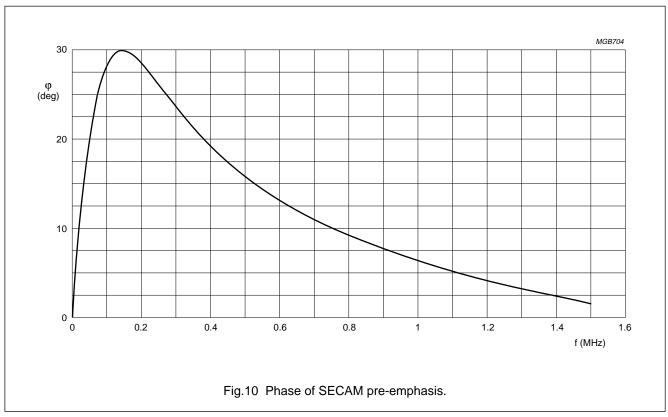

SECAM specific pre-processing is achieved in this block by a pre-emphasis of colour difference signals (for gain and phase see Figs 9 and 10.

A baseband frequency modulator with a reference frequency shifted from 4.286 MHz to DC carries out SECAM modulation in accordance with appropriate standard or optionally wide clipping limits.

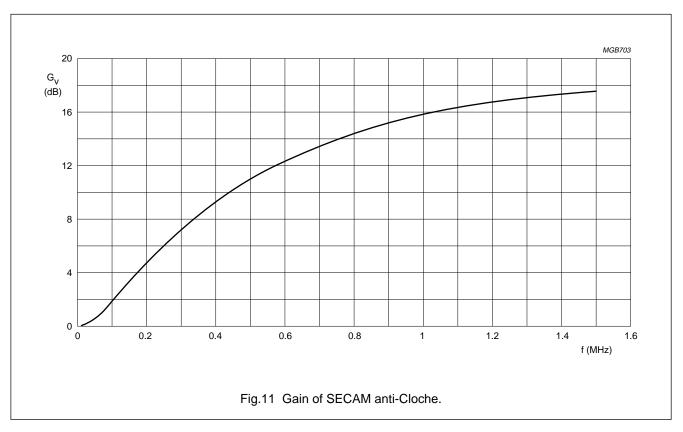

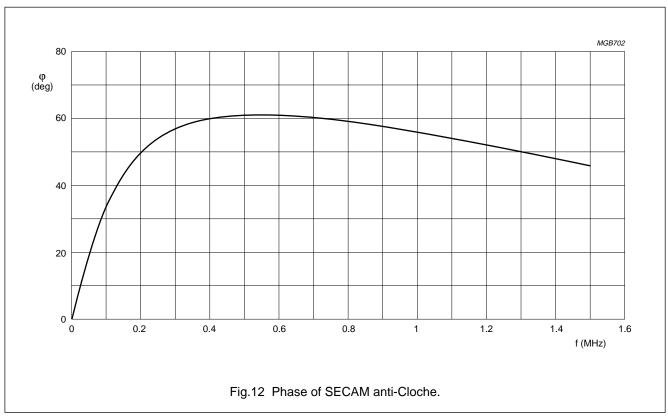

After the HF pre-emphasis, also applied on a DC reference carrier (anti-Cloche filter; see Figs 11 and 12), line-by-line sequential carriers with black reference of 4.25 MHz (Db) and 4.40625 MHz (Dr) are generated using specified values for FSC programming bytes.

Alternating phase reset in accordance with SECAM standard is carried out automatically. During vertical blanking the so-called bottle pulses are not provided.

# Digital Video Encoder (EURO-DENC)

SAA7182; SAA7183

### **Output interface/DACs**

In the output interface encoded both Y and C signals are converted from digital-to-analog in 10-bit resolution. Y and C signals are also combined to a 10-bit CVBS signal.

The CVBS output occurs with the same processing delay as the Y and C outputs. Absolute amplitudes at the input of the DAC for CVBS is reduced by  $^{15}/_{16}$  with respect to Y and C DACs to make maximum use of conversion ranges.

RED, GREEN and BLUE signals are also converted from digital-to-analog, each providing a 9-bit resolution.

Outputs of the DACs can be set together in two groups via software control to minimum output voltage for either purpose.

#### **Synchronization**

Synchronization of the EURO-DENC is able to operate in two modes; slave mode and master mode.

In the slave mode, the circuit accepts synchronization pulses at the bidirectional RCV1 port. The timing and trigger behaviour related to RCV1 can be influenced by programming the polarity and on-chip delay of RCV1. Active slope of RCV1 defines the vertical phase and optionally the odd/even and colour frame phase to be initialized, it can be also used to set the horizontal phase.

If the horizontal phase is not be influenced by RCV1, a horizontal pulse needs to be supplied at the RCV2 pin. Timing and trigger behaviour can also be influenced for RCV2.

If there are missing pulses at RCV1 and/or RCV2, the time base of EURO-DENC runs free, thus an arbitrary number of synchronization slopes may miss, but no additional pulses (such with wrong phase) must occur.

If the vertical and horizontal phase is derived from RCV1, RCV2 can be used for horizontal or composite blanking input or output.

In the master mode, the time base of the circuit continuously runs free. On the RCV1 port, the IC can output:

- A Vertical Sync signal (VS) with 3 or 2.5 lines duration, or

- · An ODD/EVEN signal which is LOW in odd fields, or

- A field sequence signal (FSEQ) which is HIGH in the first of 4 respectively 8 respectively 12 fields.

On the RCV2 port, the IC can provide a horizontal pulse with programmable start and stop phase; this pulse can be inhibited in the vertical blanking period to build up, for example, a composite blanking signal.

The polarity of both RCV1 and RCV2 is selectable by software control.

Field length is in accordance with 50 Hz or 60 Hz standards, including non-interlaced options; start and end of its active part can be programmed. The active part of a field always starts at the beginning of a line, if the standard blanking option SBLBN is not set.

#### I<sup>2</sup>C-bus interface

The I<sup>2</sup>C-bus interface is a standard slave transceiver, supporting 7-bit slave addresses and 400 kbits/s guaranteed transfer rate. It uses 8-bit subaddressing with an auto-increment function. All registers are write only, except one readable status byte.

Two I<sup>2</sup>C-bus slave addresses are selected:

88H: LOW at pin 4 8CH: HIGH at pin 4.

### Input levels and formats

EURO-DENC expects digital Y, Cb, Cr data with levels (digital codes) in accordance with "CCIR 601".

For C and CVBS outputs, deviating amplitudes of the colour difference signals can be compensated by independent gain control setting, while gain for luminance is set to predefined values, distinguishable for 7.5 IRE set-up or without set-up.

For RGB outputs fixed amplification in accordance with *"CCIR 601"* is provided.

Reference levels are measured with a colour bar, 100% white, 100% amplitude and 100% saturation.

1996 Jul 08

# Digital Video Encoder (EURO-DENC)

SAA7182; SAA7183

Table 1 "CCIR 601" signal component levels

| COLOUR  |     |     | SIGN | ALS <sup>(1)</sup>      |                         |                         |

|---------|-----|-----|------|-------------------------|-------------------------|-------------------------|

| COLOUR  | Y   | Cb  | Cr   | <b>R</b> <sup>(2)</sup> | <b>G</b> <sup>(2)</sup> | <b>B</b> <sup>(2)</sup> |

| White   | 235 | 128 | 128  | 235                     | 235                     | 235                     |

| Yellow  | 210 | 16  | 146  | 235                     | 235                     | 16                      |

| Cyan    | 170 | 166 | 16   | 16                      | 235                     | 235                     |

| Green   | 145 | 54  | 34   | 16                      | 235                     | 16                      |

| Magenta | 106 | 202 | 222  | 235                     | 16                      | 235                     |

| Red     | 81  | 90  | 240  | 235                     | 16                      | 16                      |

| Blue    | 41  | 240 | 110  | 16                      | 16                      | 235                     |

| Black   | 16  | 128 | 128  | 16                      | 16                      | 16                      |

#### Notes

- 1. Transformation:

- a)  $R = Y + 1.3707 \times (Cr 128)$

- b)  $G = Y 0.3365 \times (Cb 128) 0.6982 \times (Cb 128)$

- c)  $B = Y + 1.7324 \times (Cb 128)$ .

- 2. Representation of R, G and B at the output is 9 bits at 27 MHz.

Table 2

8-bit multiplexed format (similar to "CCIR 601")

| TIME                   | 0               | 1              | 2               | 2              | 4               | 5              | 6               | 7              |

|------------------------|-----------------|----------------|-----------------|----------------|-----------------|----------------|-----------------|----------------|

| Sample                 | Cb <sub>0</sub> | Y <sub>0</sub> | Cr <sub>0</sub> | Y <sub>1</sub> | Cb <sub>2</sub> | Y <sub>2</sub> | Cr <sub>2</sub> | Y <sub>3</sub> |

| Luminance pixel number | (               | )              | ,               |                | 2               | 2              | 3               | 3              |

| Colour pixel number    |                 | (              | )               |                |                 | 2              | 2               |                |

Table 3 16-bit multiplexed format (DTV2 format)

| TIME                   | 0 | 1          | 2               | 3      | 4               | 5          | 6               | 7          |

|------------------------|---|------------|-----------------|--------|-----------------|------------|-----------------|------------|

| Sample Y line          | Y | <b>'</b> 0 | Y               | ,<br>1 | Y               | <b>'</b> 2 | Y               | <b>'</b> 3 |

| Sample UV line         | С | $b_0$      | Cr <sub>0</sub> |        | Cb <sub>2</sub> |            | Cr <sub>2</sub> |            |

| Luminance pixel number | ( | )          |                 | 1      | 2               |            | 3               |            |

| Colour pixel number    |   | (          | )               |        |                 | :          | 2               |            |

1996 Jul 08

# Digital Video Encoder (EURO-DENC)

SAA7182; SAA7183

|                             | SUB           |        |        |        | DATA   | DATA BYTE |        |        |         |

|-----------------------------|---------------|--------|--------|--------|--------|-----------|--------|--------|---------|

| REGISTER FUNCTION           | ADDRESS       | D7     | 9Q     | D5     | D4     | D3        | D2     | ٦      | D0      |

| Null                        | 00            | 0      | 0      | 0      | 0      | 0         | 0      | 0      | 0       |

|                             | $\rightarrow$ |        |        |        |        |           |        |        |         |

| Null                        | 39            | 0      | 0      | 0      | 0      | 0         | 0      | 0      | 0       |

| Input port control          | 3A            | CBENB  | DISKEY | 0      | 0      | 0         | FMT16  | Y2C    | UV2C    |

| OVL LUT Y0                  | 42            | OVLY07 | OVLY06 | OVLY05 | OVLY04 | OVLY03    | OVLY02 | OVLY01 | OVLY00  |

| OVL LUT U0                  | 43            | OVLU07 | 90NTNO | OVLU05 | OVLU04 | OVLU03    | OVLU02 | OVLU01 | O0/LU00 |

| OVL LUT V0                  | 44            | OVLV07 | OVLV06 | OVLV05 | OVLV04 | OVLV03    | OVLV02 | OVLV01 | OVLV00  |

|                             | $\rightarrow$ |        |        |        |        |           |        |        |         |

| OVL LUT Y7                  | 25            | OVLY77 | OVLY76 | OVLY75 | OVLY74 | OVLY73    | OVLY72 | OVLY71 | OVLY70  |

| OVL LUT U7                  | 58            | OVLU77 | OVLU76 | OVLU75 | OVLU74 | OVLU73    | OVLU72 | OVLU71 | OVLU70  |

| OVL LUT V7                  | 59            | OVLV77 | OVLV76 | OVLV75 | OVLV74 | OVLV73    | OVLV72 | OVLV71 | OVLV70  |

| Chrominance phase           | 5A            | CHPS7  | CHPS6  | CHPS5  | CHPS4  | CHPS3     | CHPS2  | CHPS1  | CHPS0   |

| Gain U                      | 5B            | GAINU7 | GAINU6 | GAINU5 | GAINU4 | GAINU3    | GAINU2 | GAINU1 | GAINU0  |

| Gain V                      | 2C            | GAINV7 | GAINV6 | GAINV5 | GAINV4 | GAINV3    | GAINV2 | GAINV1 | GAINVO  |

| Gain U MSB, black level     | 2D            | GAINU8 | 0      | BLCKL5 | BLCKL4 | BLCKL3    | BLCKL2 | BLCKL1 | BLCKL0  |

| Gain V MSB, blanking level, | 2E            | GAINV8 | DECTYP | BLNNL5 | BLNNL4 | BLNNL3    | BLNNL2 | BLNNL1 | BLNNL0  |

| decoder type                | L             |        |        | 1      |        |           |        | į      | 9       |

| Blanking level VBI          | 5F            | 0      | 0      | BLNVB5 | BLNVB4 | BLNVB3    | BLNVB2 | BLNVB1 | BLNVB0  |

| Null                        | 09            | 0      | 0      | 0      | 0      | 0         | 0      | 0      | 0       |

| Standard control            | 61            | DOWNB  | DOWNA  | INPI   | YGS    | SECAM     | SCBW   | PAL    | FISE    |

| Burst amplitude             | 62            | RTCE   | BSTA6  | BSTA5  | BSTA4  | BSTA3     | BSTA2  | BSTA1  | BSTA0   |

| Subcarrier 0                | 63            | FSC07  | FSC06  | FSC05  | FSC04  | FSC03     | FSC02  | FSC01  | FSC00   |

| Subcarrier 1                | 64            | FSC15  | FSC14  | FSC13  | FSC12  | FSC11     | FSC10  | FSC09  | FSC08   |

| Subcarrier 2                | 65            | FSC23  | FSC22  | FSC21  | FSC20  | FSC19     | FSC18  | FSC17  | FSC16   |

| Subcarrier 3                | 99            | FSC31  | FSC30  | FSC29  | FSC28  | FSC27     | FSC26  | FSC25  | FSC24   |

| Line 21 odd 0               | 29            | L21007 | L21006 | L21005 | L21004 | L21003    | L21002 | L21001 | L21000  |

| Line 21 odd 1               | 89            | L21017 | L21016 | L21015 | L21014 | L21013    | L21012 | L21011 | L21010  |

| Line 21 even 0              | 69            | L21E07 | L21E06 | L21E05 | L21E04 | L21E03    | L21E02 | L21E01 | L21E00  |

| Line 21 even 1              | 6A            | L21E17 | L21E16 | L21E15 | L21E14 | L21E13    | L21E12 | L21E11 | L21E10  |

1996 Jul 08 12

Slave Receiver (Slave Address 88H or 8CH)

Bit allocation map

Table 4

SAA7182; SAA7183

| MOITOMILE GETSIONS              | SUB     |         |         |         | DATA BYTE | BYTE    |         |         |         |

|---------------------------------|---------|---------|---------|---------|-----------|---------|---------|---------|---------|

| REGIOIEN FONCTION               | ADDRESS | D7      | 9Q      | D5      | D4        | D3      | D2      | ٦       | D0      |

| RCV port control                | 6B      | SRCV11  | SRCV10  | TRCV2   | ORCV1     | PRCV1   | CBLF    | ORCV2   | PRCV2   |

| Trigger control                 | 29      | HTRIG7  | HTRIG6  | HTRIG5  | HTRIG4    | HTRIG3  | HTRIG2  | HTRIG1  | HTRIG0  |

| Trigger control                 | О9      | HTRIG10 | HTRIG9  | HTRIG8  | VTRIG4    | VTRIG3  | VTRIG2  | VTRIG1  | VTRIG0  |

| Multi control                   | 99      | SBLBN   | 0       | PHRES1  | PHRES0    | 0       | 0       | FLC1    | FLC0    |

| Closed caption/teletext control | 6F      | CCEN1   | CCENO   | TTXEN   | SCCLN4    | SCCLN3  | SCCLN2  | SCCLN1  | SCCLNO  |

| RCV2 output start               | 20      | RCV2S7  | RCV2S6  | RCV2S5  | RCV2S4    | RCV2S3  | RCV2S2  | RCV2S1  | RCV2S0  |

| RCV2 output end                 | 7.1     | RCV2E7  | RCV2E6  | RCV2E5  | RCV2E4    | RCV2E3  | RCV2E2  | RCV2E1  | RCV2E0  |

| MSBs RCV2 output                | 72      | 0       | RCV2E10 | RCV2E9  | RCV2E8    | 0       | RCV2S10 | RCV2S9  | RCV2S8  |

| TTX request H start             | 73      | TTXHS7  | TTXHS6  | TTXHS5  | TTXHS4    | TTXHS3  | TTXHS2  | TTXHS1  | TTXHS0  |

| TTX request H end               | 74      | TTXHE7  | TTXHE6  | TTXHE5  | TTXHE4    | TTXHE3  | TTXHE2  | TTXHE1  | TTXHE0  |

| MSBs TTX request H              | 22      | 0       | TTXHE10 | TTXHE9  | TTXHE8    | 0       | TTXHS10 | TTXHS9  | TTXHS8  |

| TTX odd request V S             | 92      | TTX0VS7 | TTXOVS6 | TTXOVS5 | TTXOVS4   | TTXOVS3 | TTXOVS2 | TTXOVS1 | TTXOVS0 |

| TTX odd request V E             | 7.2     | TTXOVE7 | TTXOVE6 | TTXOVE5 | TTXOVE4   | TTXOVE3 | TTXOVE2 | TTXOVE1 | TTXOVE0 |

| TTX even request V S            | 82      | TTXEVS7 | TTXEVS6 | TTXEVS5 | TTXEVS4   | TTXEVS3 | TTXEVS2 | TTXEVS1 | TTXEVS0 |

| TTX even request V E            | 62      | TTXEVE7 | TTXEVE6 | TTXEVE5 | TTXEVE4   | TTXEVE3 | TTXEVE2 | TTXEVE1 | TTXEVE0 |

| First active line               | 7.A     | FAL7    | FAL6    | FAL5    | FAL4      | FAL3    | FAL2    | FAL1    | FAL0    |

| Last active line                | 7B      | LAL7    | LAL6    | LAL5    | LAL4      | LAL3    | LAL2    | LAL1    | LAL0    |

| MSBs vertical                   | ) L     | 0       | LAL8    | 0       | FAL8      | TTXEVE8 | TTXOVE8 | TTXEVS8 | TTXOVS8 |

| Null                            | 7D      | 0       | 0       | 0       | 0         | 0       | 0       | 0       | 0       |

| Null                            | 7E      | 0       | 0       | 0       | 0         | 0       | 0       | 0       | 0       |

| Null                            | 7F      | 0       | 0       | 0       | 0         | 0       | 0       | 0       | 0       |

# Digital Video Encoder (EURO-DENC)

SAA7182; SAA7183

# I<sup>2</sup>C-bus format

**Table 5** I<sup>2</sup>C-bus address; see Table 6

| S | SLAVE ADDRESS | ACK | SUBADDRESS | ACK | DATA 0 | ACK |  | DATA n | ACK | Р |  |

|---|---------------|-----|------------|-----|--------|-----|--|--------|-----|---|--|

|---|---------------|-----|------------|-----|--------|-----|--|--------|-----|---|--|

### Table 6 Explanation of Table 5

| PART                | DESCRIPTION                                 |

|---------------------|---------------------------------------------|

| S                   | START condition                             |

| Slave address       | 1 0 0 0 1 0 0 X or 1 0 0 0 1 1 0 X (note 1) |

| ACK                 | acknowledge, generated by the slave         |

| Subaddress (note 2) | subaddress byte                             |

| DATA                | data byte                                   |

|                     | continued data bytes and ACKs               |

| Р                   | STOP condition                              |

#### **Notes**

- 1. X is the read/write control bit; X = logic 0 is order to write; X = logic 1 is order to read, no subaddressing with read.

- 2. If more than 1 byte DATA is transmitted, then auto-increment of the subaddress is performed.

# **Slave Receiver**

Table 7 Subaddress 3A

| DATA BYTE                                                                                                                                                                                    | LOGIC LEVEL                        | DESCRIPTION                                                                       |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-----------------------------------------------------------------------------------|--|

| UV2C                                                                                                                                                                                         | 0 Cb/Cr data are two's complement. |                                                                                   |  |

|                                                                                                                                                                                              | 1                                  | Cb/Cr data are straight binary. Default after reset.                              |  |

| Y2C                                                                                                                                                                                          | 0                                  | Y data are two's complement.                                                      |  |

|                                                                                                                                                                                              | 1                                  | Y data are straight binary. Default after reset.                                  |  |

| FMT16 0 Selects Cb, Y, Cr, Y on 8 lines on MP port ("CCIR 656" cor                                                                                                                           |                                    | Selects Cb, Y, Cr, Y on 8 lines on MP port ("CCIR 656" compatible). Default after |  |

|                                                                                                                                                                                              |                                    | reset.                                                                            |  |

|                                                                                                                                                                                              | 1                                  | Selects Cb, Cr on DP port and Y on MP port.                                       |  |

| DISKEY 0 OVL keying enabled for Y, C and CVBS outputs. Default after reset.                                                                                                                  |                                    | OVL keying enabled for Y, C and CVBS outputs. Default after reset.                |  |

| 1 OVL keying disabled for Y, C and CVBS outputs.                                                                                                                                             |                                    | OVL keying disabled for Y, C and CVBS outputs.                                    |  |

| CBENB  0 Data from input ports are encoded. Default after reset.  1 Colour bar with programmable colours (entries of OVL_LUTs) is The LUTs are read in upward order from index 0 to index 7. |                                    | Data from input ports are encoded. Default after reset.                           |  |

|                                                                                                                                                                                              |                                    | Colour bar with programmable colours (entries of OVL_LUTs) is encoded.            |  |

|                                                                                                                                                                                              |                                    | The LUTs are read in upward order from index 0 to index 7.                        |  |

# Digital Video Encoder (EURO-DENC)

SAA7182; SAA7183

Table 8 Subaddress 42 to 59

| COLOUD  |           | DATA BYTE (note 1) |           |                |

|---------|-----------|--------------------|-----------|----------------|

| COLOUR  | OVLY      | OVLU               | OVLV      | INDEX (note 2) |

| White   | 107 (6BH) | 0 (00H)            | 0 (00H)   | 0              |

|         | 107 (6BH) | 0 (00H)            | 0 (00H)   |                |

| Yellow  | 82 (52H)  | 144 (90H)          | 18 (12H)  | 1              |

|         | 34 (22H)  | 172 (ACH)          | 14 (0EH)  |                |

| Cyan    | 42 (2AH)  | 38 (26H)           | 144 (90H) | 2              |

|         | 03 (03H)  | 29 (1DH)           | 172 (ACH) |                |

| Green   | 17 (11H)  | 182 (B6H)          | 162 (A2H) | 3              |

|         | 240 (F0H) | 200 (C8H)          | 185 (B9H) |                |

| Magenta | 234 (EAH) | 74 (4AH)           | 94 (5EH)  | 4              |

|         | 212 (D4H) | 56 (38H)           | 71 (47H)  |                |

| Red     | 209 (D1H) | 218 (DAH)          | 112 (70H) | 5              |

|         | 193 (C1H) | 227 (E3H)          | 84 (54H)  |                |

| Blue    | 169 (A9H) | 112 (70H)          | 238 (EEH) | 6              |

|         | 163 (A3H) | 84 (54H)           | 242 (F2H) |                |

| Black   | 144 (90H) | 0 (00H)            | 0 (00H)   | 7              |

|         | 144 (90H) | 0 (00H)            | 0 (00H)   |                |

#### **Notes**

- 1. Contents of OVL look-up tables. All 8 entries are 8-bits. Data representation is in accordance with "CCIR 601" (Y, Cb, Cr), but two's complement, e.g. for a  $^{100}/_{100}$  (upper number) or  $^{100}/_{75}$  (lower number) colour bar.

- 2. For normal colour bar with CBENB = logic 1.

Table 9 Subaddress 5A

| DATA BYTE(1) | VALUE | RESULT                              |

|--------------|-------|-------------------------------------|

| CHPS         | 68H   | PAL-B/G and data from input ports   |

|              | 92H   | PAL-B/G and data from look-up table |

|              | 82H   | NTSC-M and data from input ports    |

|              | A4H   | NTSC-M and data from look-up table  |

### Note

1. Phase of encoded colour subcarrier (including burst) relative to horizontal sync. Can be adjusted in steps of 360/256 degrees.

# Digital Video Encoder (EURO-DENC)

SAA7182; SAA7183

Table 10 Subaddress 5B and 5D

| DATA BYTE | DESCRIPTION                                     | CONDITIONS                               | REMARKS                                       |

|-----------|-------------------------------------------------|------------------------------------------|-----------------------------------------------|

| GAINU     | variable gain for Cb signal;                    | white-to-black = 92.5 IRE <sup>(1)</sup> |                                               |

|           | input representation accordance with "CCIR 601" | GAINU = 0                                | output subcarrier of U contribution = 0       |

|           |                                                 | GAINU = 118 (76H)                        | output subcarrier of U contribution = nominal |

|           |                                                 | white-to-black = 100 IRE(2)              |                                               |

|           |                                                 | GAINU = 0                                | output subcarrier of U contribution = 0       |

|           |                                                 | GAINU = 125 (7DH)                        | output subcarrier of U contribution = nominal |

|           | nominal GAINU for SECAM encoding                | value = 106 (6AH)                        |                                               |

#### **Notes**

- 1. GAINU =  $-2.17 \times$  nominal to  $+2.16 \times$  nominal.

- 2. GAINU =  $-2.05 \times$  nominal to  $+2.04 \times$  nominal.

Table 11 Subaddress 5C and 5E

| DATA BYTE | DESCRIPTION                  | CONDITIONS                               | REMARKS                                       |

|-----------|------------------------------|------------------------------------------|-----------------------------------------------|

| GAINV     | variable gain for Cr signal; | white-to-black = 92.5 IRE <sup>(1)</sup> |                                               |

|           | input representation         | GAINV = 0                                | output subcarrier of V contribution = 0       |

|           | accordance with "CCIR 601"   | GAINV = 165 (A5H)                        | output subcarrier of V contribution = nominal |

|           | COIN OUT                     | white-to-black = 100 IRE(2)              |                                               |

|           |                              | GAINV = 0                                | output subcarrier of V contribution = 0       |

|           |                              | GAINV = 175 (AFH)                        | output subcarrier of V contribution = nominal |

|           | nominal GAINV for            | value = -129 (17FH)                      |                                               |

|           | SECAM encoding               |                                          |                                               |

### **Notes**

- 1. GAINV =  $-1.55 \times$  nominal to  $+1.55 \times$  nominal.

- 2. GAINV =  $-1.46 \times$  nominal to  $+1.46 \times$  nominal.

Table 12 Subaddress 5D

| DATA BYTE | DESCRIPTION                 | CONDITIONS                             | REMARKS                     |

|-----------|-----------------------------|----------------------------------------|-----------------------------|

| BLCKL     | variable black level; input | white-to-sync = 140 IRE <sup>(1)</sup> |                             |

|           | representation accordance   | BLCKL = 0                              | output black level = 24 IRE |

|           | with "CCIR 601"             | BLCKL = 63 (3FH)                       | output black level = 49 IRE |

|           |                             | white-to-sync = 143 IRE(2)             |                             |

|           |                             | BLCKL = 0                              | output black level = 24 IRE |

|           |                             | BLCKL = 63 (3FH)                       | output black level = 50 IRE |

### Notes

- 1. Output black level/IRE = BLCKL × 25/63 + 24; recommended value: BLCKL = 60 (3CH) normal.

- 2. Output black level/IRE =  $BLCKL \times 26/63 + 24$ ; recommended value: BLCKL = 45 (2DH) normal.

# Digital Video Encoder (EURO-DENC)

SAA7182; SAA7183

Table 13 Subaddress 5E

| DATA BYTE | DESCRIPTION             | CONDITIONS                             | REMARKS                               |

|-----------|-------------------------|----------------------------------------|---------------------------------------|

| BLNNL     | variable blanking level | white-to-sync = 140 IRE <sup>(1)</sup> |                                       |

|           |                         | BLNNL = 0                              | output blanking level = 17 IRE        |

|           |                         | BLNNL = 63 (3FH)                       | output blanking level = 42 IRE        |

|           |                         | white-to-sync = 143 IRE(2)             |                                       |

|           |                         | BLNNL = 0                              | output blanking level = 17 IRE        |

|           |                         | BLNNL = 63 (3FH)                       | output blanking level = 43 IRE        |

| DECTYP    | RTCI                    | logic 0                                | real time control input from SAA7151B |

|           |                         | logic 1                                | real time control input from SAA7111  |

### Notes

- 1. Output black level/IRE =  $BLNNL \times 25/63 + 17$ ; recommended value: BLNNL = 58 (3AH) normal.

- 2. Output black level/IRE =  $BLNNL \times 26/63 + 17$ ; recommended value: BLNNL = 63 (3FH) normal.

Table 14 Subaddress 5F

| DATA BYTE | DESCRIPTION                                                                                        |

|-----------|----------------------------------------------------------------------------------------------------|

| BLNVB     | variable blanking level during vertical blanking interval is typically identical to value of BLNNL |

### Table 15 Subaddress 61:

| DATA BYTE                                                                                                                                  | LOGIC LEVEL | DESCRIPTION                                                                                                                                                           |  |

|--------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| FISE                                                                                                                                       | 0           | 864 total pixel clocks per line; default after reset                                                                                                                  |  |

|                                                                                                                                            | 1           | 858 total pixel clocks per line                                                                                                                                       |  |

| PAL                                                                                                                                        | 0           | NTSC encoding (non-alternating V component)                                                                                                                           |  |

|                                                                                                                                            | 1           | PAL encoding (alternating V component); default after reset                                                                                                           |  |

| SCBW                                                                                                                                       | 0           | enlarged bandwidth for chrominance encoding (for overall transfer characteristic of chrominance in baseband representation see Figs 3 and 4); wide clipping for SECAM |  |

| 1                                                                                                                                          |             | standard bandwidth for chrominance encoding (for overall transfer characteristic of chrominance in baseband representation see Figs 3 and 4); default after reset     |  |

|                                                                                                                                            |             | no SECAM encoding; default after reset                                                                                                                                |  |

|                                                                                                                                            |             | SECAM encoding activated                                                                                                                                              |  |

| YGS 0   Iuminance gain for white – black 100 IRE; default after reset 1   Iuminance gain for white – black 92.5 IRE including 7.5 IRE set- |             | luminance gain for white – black 100 IRE; default after reset                                                                                                         |  |

|                                                                                                                                            |             | luminance gain for white – black 92.5 IRE including 7.5 IRE set-up of black                                                                                           |  |

| INPI                                                                                                                                       | 0           | PAL switch phase is nominal; default after reset                                                                                                                      |  |

|                                                                                                                                            | 1           | PAL switch phase is inverted compared to nominal                                                                                                                      |  |

| DOWNA 0 DACs for CVBS, Y and C in normal operational mode; defa                                                                            |             | DACs for CVBS, Y and C in normal operational mode; default after reset                                                                                                |  |

|                                                                                                                                            | 1           | DACs for CVBS, Y and C forced to lowest output voltage                                                                                                                |  |

| DOWNB                                                                                                                                      | 0           | DACs for R, G and B in normal operational mode; default after reset                                                                                                   |  |

|                                                                                                                                            | 1           | DACs for R, G and B forced to lowest output voltage                                                                                                                   |  |

# Digital Video Encoder (EURO-DENC)

SAA7182; SAA7183

Table 16 Subaddress 62A

| DATA BYTE | LOGIC LEVEL                                                                            | DESCRIPTION                                            |  |

|-----------|----------------------------------------------------------------------------------------|--------------------------------------------------------|--|

| RTCE      | 0                                                                                      | no real time control of generated subcarrier frequency |  |

|           | real time control of generated subcarrier frequency through SAA715 (timing see Fig.16) |                                                        |  |

#### Table 17 Subaddress 62B

| DATA BYTE | DESCRIPTION                                        | CONDITIONS                                                  | REMARKS |

|-----------|----------------------------------------------------|-------------------------------------------------------------|---------|

| BSTA      | amplitude of colour burst; input representation in | white-to-black = 92.5 IRE;<br>burst = 40 IRE; NTSC encoding |         |

|           | accordance with                                    | BSTA = 0 to $1.25 \times \text{nominal}^{(1)}$              |         |

|           | "CCIR 601"                                         | white-to-black = 92.5 IRE;<br>burst = 40 IRE; PAL encoding  |         |

|           |                                                    | BSTA = 0 to $1.76 \times \text{nominal}^{(2)}$              |         |

|           |                                                    | white-to-black = 100 IRE;<br>burst = 43 IRE; NTSC encoding  |         |

|           |                                                    | BSTA = 0 to $1.20 \times \text{nominal}^{(3)}$              |         |

|           |                                                    | white-to-black = 100 IRE;<br>burst = 43 IRE; PAL encoding   |         |

|           |                                                    | BSTA = 0 to $1.67 \times \text{nominal}^{(4)}$              |         |

|           | fixed burst amplitude with S                       | ECAM encoding                                               |         |

### **Notes**

1. Recommended value: BSTA = 102 (66H).

2. Recommended value: BSTA = 72 (48H).

3. Recommended value: BSTA = 106 (6AH).

4. Recommended value: BSTA = 75 (4BH).

Table 18 Subaddress 63 to 66 (four bytes to program subcarrier frequency)

| DATA BYTE    | DESCRIPTION                                                                                                                                               | CONDITIONS                                                                    | REMARKS                                                     |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------|

| FSC0 to FSC3 | f <sub>fsc</sub> = subcarrier frequency<br>(in multiples of line<br>frequency);<br>f <sub>llc</sub> = clock frequency (in<br>multiples of line frequency) | $FSC = round \left( \frac{f_{fsc}}{f_{Ilc}} \times 2^{32} \right)$ see note 1 | FSC3 = most significant byte  FSC0 = least significant byte |

### Note

1. Examples:

a) NTSC-M:  $f_{fsc}$  = 227.5,  $f_{llc}$  = 1716  $\rightarrow$  FSC = 569408543 (21F07C1FH).

b) PAL-B/G:  $f_{fsc}$  = 283.7516,  $f_{llc}$  = 1728  $\rightarrow$  FSC = 705268427 (2A098ACBH).

c) SECAM:  $f_{fsc}$  = 274.304,  $f_{llc}$  = 1728  $\rightarrow$  FSC = 681786290 (28A33BB2H).

# Digital Video Encoder (EURO-DENC)

SAA7182; SAA7183

Table 19 Subaddress 67 to 6A

| DATA BYTE(1) | DESCRIPTION                               |

|--------------|-------------------------------------------|

| L21O0        | first byte of captioning data, odd field  |

| L21O1        | second byte of captioning data, odd field |

| L21E0        | first byte of extended data, even field   |

| L21E1        | second byte of extended data, even field  |

#### Note

1. LSBs of the respective bytes are encoded immediately after run-in and framing code, the MSBs of the respective bytes have to carry the parity bit, in accordance with the definition of Line 21 encoding format.

Table 20 Subaddress 6B

| DATA BYTE | LOGIC LEVEL | DESCRIPTION                                                                                                                                                                                                                       |

|-----------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PRCV2     | 0           | polarity of RCV2 as output is active HIGH, rising edge is taken when input; default after reset                                                                                                                                   |

|           | 1           | polarity of RCV2 as output is active LOW, falling edge is taken when input                                                                                                                                                        |

| ORCV2     | 0           | pin RCV2 is switched to input; default after reset                                                                                                                                                                                |

|           | 1           | pin RCV2 is switched to output                                                                                                                                                                                                    |

| CBLF      | 0           | if ORCV2 = HIGH, pin RCV2 provides an HREF signal (Horizontal Reference Pulse that is defined by RCV2S and RCV2E, also during vertical blanking Interval); default after reset                                                    |

|           |             | if ORCV2 = LOW, signal input to RCV2 is used for horizontal synchronization only (if TRCV2 = 1); default after reset                                                                                                              |

|           | 1           | if ORCV2 = HIGH, pin RCV2 provides a 'Composite-Blanking-Not' signal, for example a reference pulse that is defined by RCV2S and RCV2E, excluding Vertical Blanking Interval, which is defined by FAL and LAL (PRCV2 must be LOW) |

|           |             | if ORCV2 = LOW, signal input to RCV2 is used for horizontal synchronization (if TRCV2 = 1) and as an internal blanking signal                                                                                                     |

| PRCV1     | 0           | polarity of RCV1 as output is active HIGH, rising edge is taken when input, respectively; default after reset                                                                                                                     |

|           | 1           | polarity of RCV1 as output is active LOW, falling edge is taken when input, respectively                                                                                                                                          |

| ORCV1     | 0           | pin RCV1 is switched to input; default after reset                                                                                                                                                                                |

|           | 1           | pin RCV1 is switched to output                                                                                                                                                                                                    |

| TRCV2     | 0           | horizontal synchronization is taken from RCV1 port; default after reset                                                                                                                                                           |

|           | 1           | horizontal synchronization is taken from RCV2 port                                                                                                                                                                                |

| SRCV1     | _           | defines signal type on pin RCV1; see Table 21                                                                                                                                                                                     |

# Digital Video Encoder (EURO-DENC)

SAA7182; SAA7183

Table 21 Logic levels and function of SRCV1

| DATA BYTE |        | AS OUTPUT      | AS INPUT       | FUNCTION                                                                                                                |

|-----------|--------|----------------|----------------|-------------------------------------------------------------------------------------------------------------------------|

| SRCV11    | SRCV10 | ASOUTPUT       | AS INPUT       | FUNCTION                                                                                                                |

| 0         | 0      | VS             | VS             | vertical sync each field; default after reset                                                                           |

| 0         | 1      | FS             | FS             | frame sync (odd/even)                                                                                                   |

| 1         | 0      | FSEQ           | FSEQ           | field sequence, vertical sync every fourth field (PAL = SECAM = 0), eighth field (PAL = 1) or twelfth field (SECAM = 1) |

| 1         | 1      | not applicable | not applicable | -                                                                                                                       |

# Table 22 Subaddress 6C, 6D

| DATA BYTE | DESCRIPTION                                                                                                                                |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------|

| HTRIG     | sets the horizontal trigger phase related to signal on RCV1 or RCV2 input                                                                  |