# **AN5733**

# Dual Attenuator

#### Outline

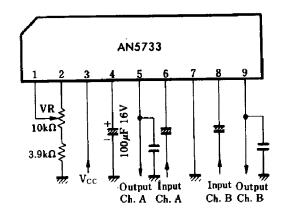

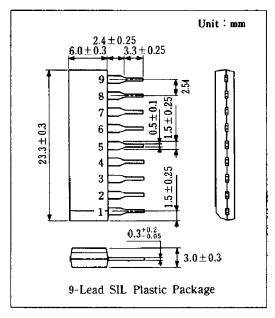

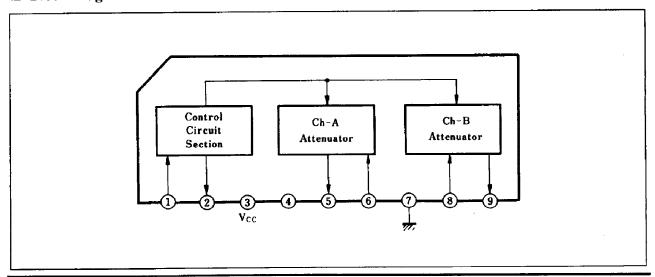

The AN5733 is an integrated circuit designed for dual attenuator and is in SIL package. With this, sets can be made compact.

#### **■** Features

- Output DC control

- Linear Output response

- Two attenuators controlled by one volume control

- Large attenuation

- Small crosstalk and level difference between the two channels

#### Use

• Volume control, etc.

#### Pin

| Pin No. | Pin Name        |

|---------|-----------------|

| 1       | Control Voltage |

| 2       | Ref. Voltage    |

| 3       | Vcc             |

| 4       | Decoupling      |

| 5       | Ch.A Output     |

| 6       | Ch.A Input      |

| 7       | GND .           |

| 8       | Ch.B Input      |

| 9       | Ch.B Output     |

### ■ Block Diagram

**Panasonic**

## Absolute Maximum Ratings $(Ta=25^{\circ}C)$

| Item              |                               | Symbol             | Rating          | Unit |  |

|-------------------|-------------------------------|--------------------|-----------------|------|--|

| Supply Voltage    |                               | $V_{cc}$           | 14.4            | V    |  |

| Power Dissipation |                               | P <sub>D</sub> 197 |                 | mW   |  |

| Temperature       | Operating Ambient Temperature | Topr               | $-20 \sim +70$  | °C   |  |

|                   | Storage Temperature           | Tstg               | $-40 \sim +150$ | °C   |  |

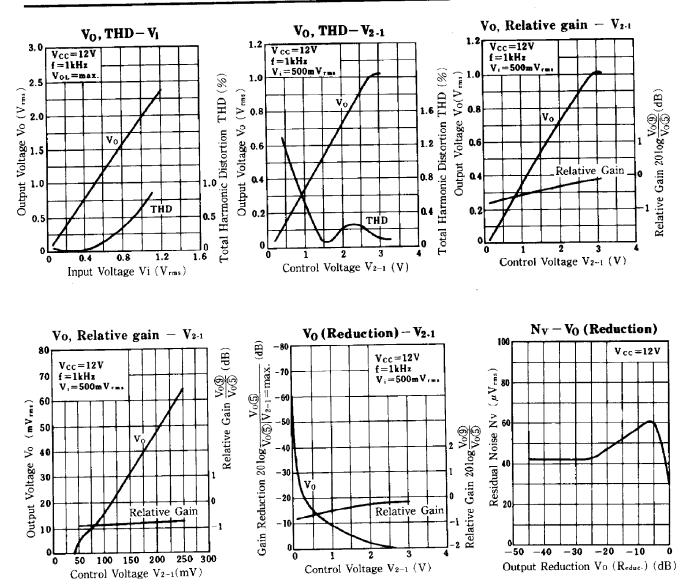

# ■ Electrical Characteristics ( $V_{CC}=12V$ , $Ta=25^{\circ}C$ )

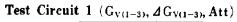

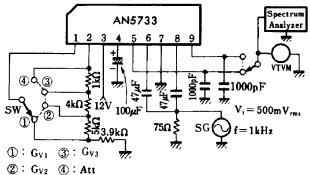

| Item                                         | Symbol                         | Test<br>Circuit | Condition                                  | min. | typ. | max. | Unit |

|----------------------------------------------|--------------------------------|-----------------|--------------------------------------------|------|------|------|------|

| Total Circuit Current                        | Itot                           |                 |                                            | 9.5  | 11.3 | 13.5 | mA   |

| Voltage Gain (1)                             | Gv <sub>1</sub> v <sub>1</sub> | 1               |                                            | 4    | 6    | 7.6  | dB   |

| Voltage Gain Difference Between Channels (1) | <b>⊿</b> G <sub>V(1)</sub>     | 1               | $f=1kHz$ , $V_i=500mV_{rms}$<br>At VR max. | -1.5 |      | 1.5  | dB   |

| Voltage Gain (2)                             | Gv(2)                          | 1               |                                            | -2   | 0    | 2.2  | dB   |

| Voltage Gain Difference Between Channels (2) | 4Gv(2)                         | 1               |                                            | -2   | 777  | 2    | dB   |

| Voltage Gain (3)                             | Gv(3)                          | 1               |                                            | -20  | -16  | -12  | đВ   |

| Voltage Gain Difference Between Channels (3) | <b>∆</b> Gv(3)                 | 1               |                                            | 2.5  |      | 2.5  | dB   |

| Attenuation (max.)                           | Au                             | 1               |                                            | 75   |      |      | dB   |

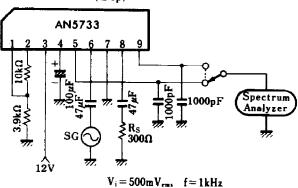

| Separation                                   | Sep                            | 2               |                                            | 70   | ***  |      | dB   |

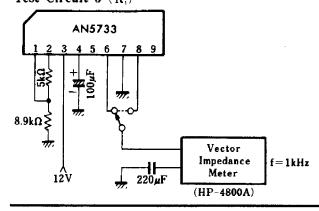

| Input Resistance                             | Ri                             | 3               |                                            |      | 25   |      | kΩ   |

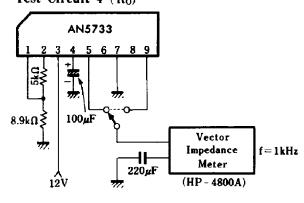

| Output Resistance                            | Ro                             | 4               | f = 1kHz                                   |      | 1.7  |      | kΩ   |

| Ripple Rejection Ratio                       | RR                             |                 |                                            | 34   |      | 1000 | dB   |

- Circuit voltage gain: Gain between Pins (5) and (6)

- Voltage gain difference between channels: Output level difference between Pins ① and ⑤

## Test Circuit 2 (Sep)

• Level difference between Pins (5) and (9)

## Test Circuit 3 (R<sub>i</sub>)

## Test Circuit 4 (Ro)

**Panasonic**

# Application Circuit