# Contents

| ■ Overview                                                  | . 3  |

|-------------------------------------------------------------|------|

| ■ Features                                                  | . 3  |

| ■ Applications                                              | . 3  |

| ■ Package                                                   | . 3  |

| ■ Type                                                      | . 3  |

| ■ Application Circuit Example                               | . 4  |

| ■ Block Diagram                                             | . 5  |

| ■ Pin Descriptions                                          | . 6  |

| ■ Absolute Maximum Ratings                                  | . 8  |

| ■ Operating Supply Voltage Range                            | . 8  |

| ■ Electrical Characteristics                                | . 9  |

| ■ Technical Data                                            | . 11 |

| 1. I/O block circuit diagrams and pin function descriptions | . 11 |

| 2. I <sup>2</sup> C bus                                     | . 16 |

| 3. Video output synchronization                             | . 18 |

| 4. BIAS1 (Pin 2) and BIAS2 (Pin 11) pins capacitors         | . 21 |

| 5. GND1 (Pin 3) and GND2 (Pin 12) pin connection            | . 21 |

| 6. P <sub>D</sub> —T <sub>a</sub> diagram                   | . 22 |

| ■ Usage Notes                                               | . 23 |

|                                                             |      |

# AN15887A

# Audio video SW for TV with multi-signal input output

### Overview

AN15887A has video switch portion which consists of:

- 6 inputs for composite video

- 2 Video output driver with sag compensation

AN15887A has audio switch portion which consists of:

- 5 inputs for left and right channels

- 2 outputs for left and right channels

It contributes to the rationalization design of a TV system.

### ■ Features

- Output frequency can be switched between LPF (6.75 MHz) and through

- Wide bandwidth video frequency –3 dB at 25 MHz in through mode

- 6.0 dB gain for video signal

- Selectable output driver for 75  $\Omega/10 \text{ k}\Omega$  load

- Selectable isolator function for different audio/Video input channels

- 0 dB/-6 dB audio gain switch for audio OUT

- Various input mode (audio and video) can be selected by using flexible internal switch

- Supports I<sup>2</sup>C bus

### Applications

• TV, car navigation

#### ■ Package

• 48 pin plastic quad flat package (QFR type)

# ■ Type

• Bi-CMOS/K

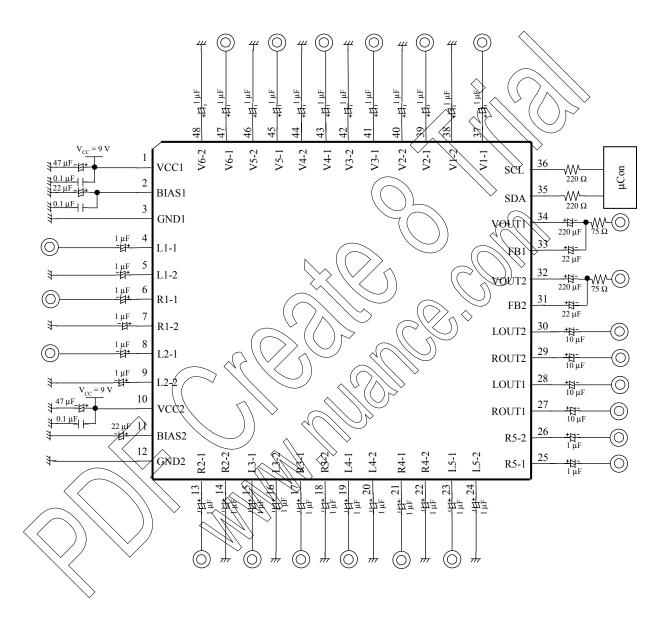

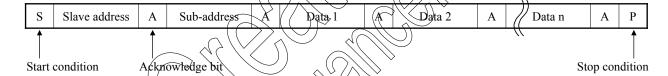

## ■ Application Circuit Example

Note) This application circuit is shown as an example but does not guarantee the design for mass production set.

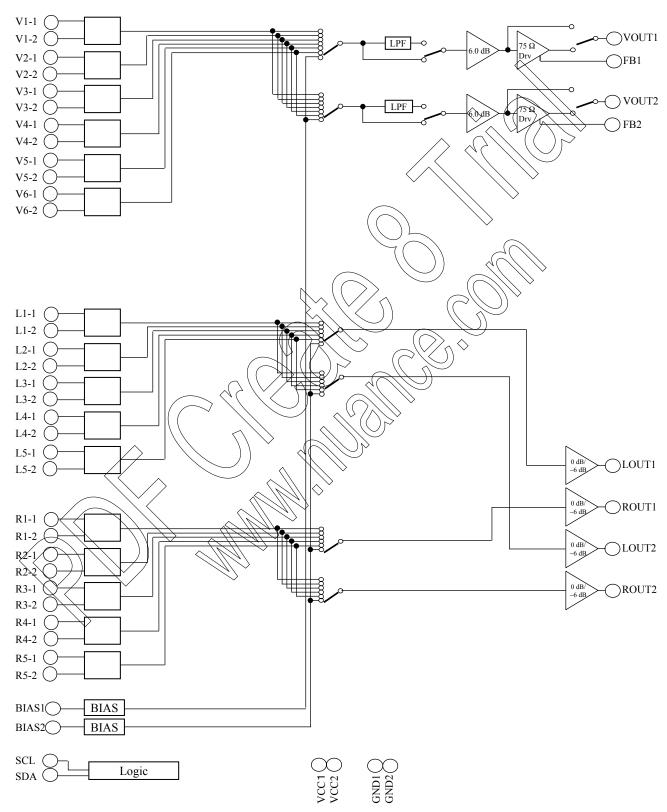

## ■ Block Diagram

Note) This block diagram is for explaining functions. The part of the block diagram may be omitted, or it may be simplified.

# ■ Pin Descriptions

| Pin No. | Pin Name | Туре         | Description                            |

|---------|----------|--------------|----------------------------------------|

| 1       | VCC1     | Power supply | 9.0 V video power supply               |

| 2       | BIAS1    | Output       | Video bias voltage 1                   |

| 3       | GND1     | Ground       | Video ground 1                         |

| 4       | L1-1     | Input        | Left audio signal input 1-1            |

| 5       | L1-2     | Input        | Left audio signal input 1-2            |

| 6       | R1-1     | Input        | Right audio signal input 1-1           |

| 7       | R1-2     | Input        | Right audio signal input 1-2           |

| 8       | L2-1     | Input        | Left audio signal input 2-1            |

| 9       | L2-2     | Input        | Left audio signal input 2-2            |

| 10      | VCC2     | Power supply | 9.0 V audio power supply               |

| 11      | BIAS2    | Output       | Audio bias voltage 2                   |

| 12      | GND2     | Ground       | Audio ground 2                         |

| 13      | R2-1     | Input        | Right audio signal input 2-1           |

| 14      | R2-2     | Input        | Right audio signal input 2-2           |

| 15      | L3-1     | Input        | Left audio signal input 3-1            |

| 16      | L3-2     | Input        | Left audio signal input 3-2            |

| 17      | R3-1     | Input        | Right audio signal input 3-1           |

| 18      | R3-2     | Input        | Right audio signal input 3-2           |

| 19      | L4-1     | Input        | Left audio signal input 4-1            |

| 20      | L4-2     | Input        | Left audio signal input 4-2            |

| 21      | R4-1     | Input        | Right and o signal input 4-1           |

| 22      | R4-2     | Input        | Right audio signal input 4-2           |

| 23      | L5-1     | Input        | Left audio signal input 5-1            |

| 24      | L5-2     | Input        | Left audio signal input 5-2            |

| 25      | R5-1     | Input        | Right audio signal input 5-1           |

| 26      | R5-2     | Input        | Right audio signal input 5-2           |

| 27      | ROUT1    | Output       | Right audio signal output 1            |

| 28      | LOUT1    | Output       | Left audio signal output 1             |

| 29      | ROUT2    | Output       | Right audio signal output 2            |

| 30      | LOUT2    | Output       | Left audio signal output 2             |

| 31      | FB2      | Input        | VOUT2 signal sag correction input      |

| 32      | VOUT2    | Output       | VOUT2 signal output                    |

| 33      | FB1      | Input        | VOUT1 signal sag correction input      |

| 34      | VOUT1    | Output       | VOUT1 signal output                    |

| 35      | SDA      | Input/Output | I <sup>2</sup> C bus data input/output |

**Panasonic**

# ■ Pin Descriptions (continued)

| Pin No. | Pin Name | Туре  | Description                      |

|---------|----------|-------|----------------------------------|

| 36      | SCL      | Input | I <sup>2</sup> C bus clock input |

| 37      | V1-1     | Input | Video composite signal input 1-1 |

| 38      | V1-2     | Input | Video composite signal input 1-2 |

| 39      | V2-1     | Input | Video composite signal input 2-1 |

| 40      | V2-2     | Input | Video composite signal input 2-2 |

| 41      | V3-1     | Input | Video composite signal input 3-1 |

| 42      | V3-2     | Input | Video composite signal input 3-2 |

| 43      | V4-1     | Input | Video composite signal input 4-1 |

| 44      | V4-2     | Input | Video composite signal input 4-2 |

| 45      | V5-1     | Input | Video composite signal input 5-1 |

| 46      | V5-2     | Input | Video composite signal input 5-2 |

| 47      | V6-1     | Input | Video composite signal input 6-1 |

| 48      | V6-2     | Input | Video composite signal input 6-2 |

## ■ Absolute Maximum Ratings

| A No. | Parameter                     | Symbol           | Rating        |                          | Unit   | Note |

|-------|-------------------------------|------------------|---------------|--------------------------|--------|------|

| 1     | Supply voltage                | V <sub>CC</sub>  | 12.0          |                          | V      | *1   |

| 2     | Supply current                | $I_{CC}$         | _             |                          | A      | _    |

| 3     | Input voltage                 | V1               | _             |                          | V      | _    |

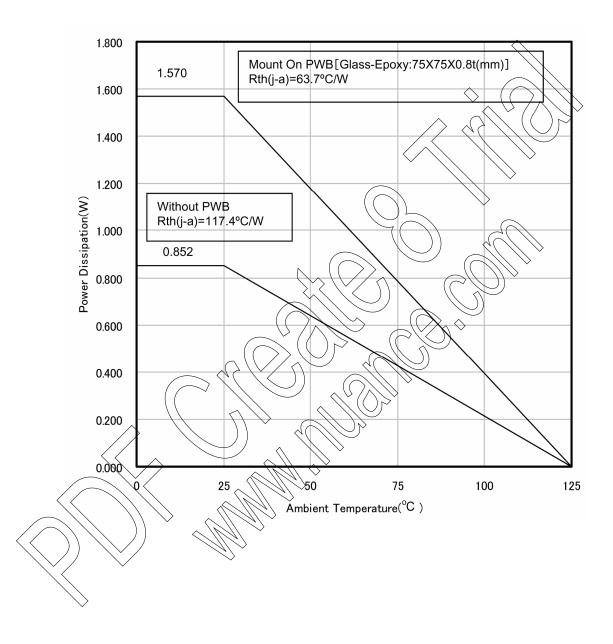

| 4     | Power dissipation             | $P_{\mathrm{D}}$ | 340           | ^                        | Wm     | *2   |

| 5     | Operating ambient temperature | T <sub>opr</sub> | -40 to +85    | $\rightarrow$ $\bigcirc$ | \\&C\\ | *3   |

| 6     | Storage temperature           | T <sub>stg</sub> | -55  to  +125 | W//                      |        | *3   |

Note) \*1: The range under absolute maximum ratings, power dissipation.

\*2: Power dissipation shows the value of only package at  $T_a = 85^{\circ}\text{C}$ .

When using this IC, refer to the 6.  $P_D - T_a$  diagram in the Technical Data-and use under the condition not exceeding the allowable value.

\*3: Expect for the storage temperature and operating ambient temperature, all ratings are for  $T_a = 25^{\circ}C$ .

# ■ Operating Supply Voltage Range

| Parameter            | Symbol  | Range      | Unit | Note |

|----------------------|---------|------------|------|------|

| Supply voltage range | ( Vcc ) | 7.5 to 9.5 | V    | _    |

Note) The values under the condition not exceeding the above absolute maximum ratings and the power dissipation.

# ■ Electrical Characteristics at $V_{CC}$ = 9 V Note) $T_a$ = 25°C±2°C unless otherwise specified.

| В   | Develop                         | 0                  | 0 - 12                                                                                                                     | Limits   |            |       | 11.2    | No |

|-----|---------------------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------|----------|------------|-------|---------|----|

| No. | Parameter                       | Symbol             | Conditions                                                                                                                 | Min      | Тур        | Max   | Unit    | te |

| 1   | Quiescent current               | $I_{CQ}$           | No signal input, no load                                                                                                   | 43       | 30         | 57    | mA      | _  |

| 2   | Voltage gain OUT                | $A_0$              | Gain setting = 0 dB<br>2.0 V[p-p] input at 1 kHz                                                                           | >-0.4    |            | 0.4   | dB      | _  |

| 2   | Voltage gain OU1                | $A_6$              | Gain setting = -6 dB<br>2.0 V[p-p] input at 1 kHz                                                                          | 6.4      | (6.0)      | 5.6   | dB      | _  |

| 3   | Frequency response              | $f_{AI}$           | 2.0 V[p-p] input at 50 kHz/1 kHz                                                                                           | 71.0     | <b>\</b> 0 | 1.0   | dB      | *  |

| 4   | Total harmonic distortion       | THD <sub>0</sub>   | Gain setting = 0 dB<br>2.0 V[p-p] input at 1 kHz<br>400 Hz HPF + 80 kHz LPF                                                | <u> </u> | 0.01       | 0.03  | %       | _  |

| 5   | Residual noise                  | $ m V_{NR0}$       | Gain setting = 0 dB7 All input pins grounded through $Rg = 600 \Omega$ (A-weighted noise filter)                           |          | 8          | 15    | μV[rms] | _  |

| 6   | Source crosstalk                | CT <sub>A</sub>    | 2.0 V[p-p] input at 1 kHz                                                                                                  |          | _          | -75   | dB      | _  |

| 7   | Channel crosstalk               | $CT_{LR}$ (        | (Din audio)                                                                                                                |          | _          | -75   | dB      | _  |

| 8   | Ripple rejection                | Apsper             | Apply 0.3 V[p-p] at 100 Hz to V <sub>CC</sub> . All input pins grounded through capacitors (22 µF at bias pin) set at 0 dB | _        | _          | -45   | dB      |    |

| 9   | Input dynamic range             | D <sub>DA5</sub>   | Gain setting + 6ttB<br>f - 1kHz input, THD < 0.5%                                                                          | 2.8      | _          | _     | V[rms]  | _  |

| 10  | Video gain                      | $G_{V}$            | f = 100  kHz,  Vin = 1  V[p-p]                                                                                             | 5.6      | 6.0        | 6.4   | dB      | _  |

| 11  | Video frequency response        |                    | Input frequency where output amplitude is –3 dB (6.75 LPF OFF)                                                             | 25       | _          | _     | MHz     | _  |

| 12  | LPF characteristic 6.75 MHz (1) | TOPRI I            | 1.0 V[p-p] input<br>at 6.75 MHz/500 kHz<br>(6.75 LPF ON)                                                                   | -1.5     | 0.0        | 1.5   | dB      | _  |

| 13  | LRF characteristic 6.75 MHz (2) | f <sub>LPF12</sub> | 1.0 V[p-p] input<br>at 27 MHz/500 kHz<br>(6.75 LPF ON)                                                                     | _        | -33.0      | -24.0 | dB      | _  |

| 14  | Crosstalk                       | CT <sub>v</sub>    | 1.0 V[p-p] input at 3.58 MHz                                                                                               | _        | -55        | -50   | dB      |    |

| 15  | Output DC level                 | dVD <sub>O</sub>   | Measure the difference from the output DC level while in mute mode                                                         | -0.4     | _          | 0.4   | V       | _  |

| 16  | Input dynamic range             | $V_{DR-V}$         | _                                                                                                                          | 2.0      | 2.1        | _     | V[p-p]  | —  |

Note) \*: Audio frequency response is not guaranteed when external resistors components are used.

# ■ Electrical Characteristics at $V_{CC}$ = 9 V (continued) Note) $T_a$ = 25°C±2°C unless otherwise specified.

| В                  | Daventer                                                                                    | Conditions          |                                            | Limits           |      |              | 11-7   | No |

|--------------------|---------------------------------------------------------------------------------------------|---------------------|--------------------------------------------|------------------|------|--------------|--------|----|

| No.                | Parameter                                                                                   | Symbol              | Conditions                                 | Min              | Тур  | Max          | Unit   | te |

| I <sup>2</sup> C I | nterface                                                                                    | 1                   |                                            | 1                |      |              |        |    |

| 17                 | Suction current during ACK                                                                  | I <sub>ACK</sub>    | Max. suction current value of SDA at 0.4 V | 3.0              | 6.0  | <del>\</del> | mA     | *  |

| 18                 | SCL, SDA signal input high level                                                            | V <sub>IHI</sub>    | _                                          | 2-7              | X+() | 5,2          |        |    |

| 19                 | SCL, SDA signal input low level                                                             | V <sub>ILO</sub>    | - /                                        | 0                | 1    | 1.5          |        |    |

| 20                 | Max. frequency allowable to input                                                           | f <sub>imax</sub>   | _                                          | -/               |      | 400          |        |    |

| 21                 | Hysteresis of schmitt trigger inputs                                                        | V <sub>hys</sub>    |                                            | 0.15             | _    | _            |        |    |

| 22                 | Pulse width of spikes which must be suppressed by the input filter                          | t <sub>sp</sub>     |                                            | 0                |      | 50           |        |    |

| 23                 | Input current each I/O pin with an input voltage between 0.3 V and 2.7 V                    | Ii                  |                                            | 10               |      | 10           |        |    |

| 24                 | Capacitance for each I/O pin                                                                | Ci                  |                                            |                  | _    | 10           |        |    |

| 25                 | Hold time (repeated) START condition. After this period, the first clock pulse is generated | T <sub>HD;STA</sub> |                                            | ♦ <sub>0.6</sub> |      | _            |        |    |

| 26                 | Low period of the SCL clock                                                                 | t <sub>row</sub> ,  |                                            | 1.3              | _    | _            |        |    |

| 27                 | High period of the SCL clock                                                                | t <sub>NIGH</sub>   |                                            | 0.6              | _    | _            | V      | *  |

| 28                 | Set-up time for a repeated START condition                                                  | t                   |                                            | 0.6              |      | _            | V      | *  |

| 29                 | Data hold time. For I <sup>2</sup> C-bus devices                                            | T <sub>HD;DAT</sub> |                                            | 0                | _    | 0.9          | Kbit/s | *  |

| 30                 | Data setup time                                                                             | t <sub>SC(BAT</sub> | _                                          | 100              | _    | _            | V      | *  |

| 31                 | Rise time of both SDA and SCL signals                                                       |                     | _                                          | _                | _    | 300          | ns     | *  |

| 32                 | Fall time of both SDA and SCL signals                                                       | $t_{\rm f}$         | _                                          | _                | _    | 300          | μΑ     | *  |

| 33                 | Set-up time for STOP condition                                                              | t <sub>SU;STO</sub> | _                                          | 0.6              |      |              | pF     | *  |

| 34                 | Bus free time between a STOP and start condition                                            | $t_{ m BUS}$        | _                                          | 1.3              | _    |              | μs     | *  |

| 35                 | Capacitive load for each bus lines                                                          | Cb                  |                                            | _                |      | 400          | μs     | *  |

Note) \*: All values referred to  $V_{\text{IHmin}}$  and  $V_{\text{IL-max}}$  levels.

Design software so that I<sup>2</sup>C communication should not freeze even if an I<sup>2</sup>C bit error occurs due to factors such as external noise.

## ■ Technical Data

1. I/O block circuit diagrams and pin function descriptions

Note) The characteristics listed below are reference values based on the IC design and are not guaranteed.

| Pin<br>No. | Waveform and voltage | Internal circuit                              | Impedance | Description                  |

|------------|----------------------|-----------------------------------------------|-----------|------------------------------|

| 1<br>10    | 9 V                  | Pin 1,10 Circuit                              |           | 9 V system power supply pins |

| 11         | 4.5 V                | 9 V<br>180k<br>Pin 11<br>180k<br>150µ<br>125µ | 90 kΩ     | Reference bias pin           |

| <          |                      |                                               |           |                              |

I/O block circuit diagrams and pin function descriptions (continued)

Note) The characteristics listed below are reference values based on the IC design and are not guaranteed.

| Pin<br>No.                                                                                                     | Waveform and voltage | Internal circuit                                                                                                                     | Impedance   | Description                                                                                                                                    |

|----------------------------------------------------------------------------------------------------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 3 12                                                                                                           | 0 V                  | Pin 3,12 Circuit                                                                                                                     |             | System ground pins                                                                                                                             |

| 4<br>5<br>6<br>7<br>8<br>9<br>13<br>14<br>15<br>16<br>17<br>18<br>19<br>20<br>21<br>22<br>23<br>24<br>25<br>26 | 4.5 V                | 9 V<br>(V <sub>CC</sub> )<br>Pin<br>4, 5, 6,<br>7, 8, 9,<br>13, 14,<br>15, 16,<br>17, 18,<br>19, 20,<br>27, 22,<br>23, 24,<br>25, 26 | 80 kΩ/41 kΩ | Audio signal input pins     If audio signal input pin is not used, connect it with a capacitor to GND     L: Left channel     R: Right channel |

| <                                                                                                              |                      |                                                                                                                                      |             |                                                                                                                                                |

1. I/O block circuit diagrams and pin function descriptions (continued)

Note) The characteristics listed below are reference values based on the IC design and are not guaranteed.

| Pin<br>No.           | Waveform and voltage | Internal circuit                                                       | Impedance | Description                                             |

|----------------------|----------------------|------------------------------------------------------------------------|-----------|---------------------------------------------------------|

| 27<br>28<br>29<br>30 | 4.5 V                | 9 V<br>(V <sub>CC</sub> )<br>Pin 27,28,<br>29,30<br>112k<br>500µ       | E.F. *    | Audio signal Output pins                                |

| 32 34                | 3.7 V                | 9 V<br>Rin 32,34<br>11,2k<br>11,77<br>11,77<br>11,77<br>11,77<br>11,77 | E.F. *    | Video composite, luminance, chrominance signal outputs. |

Note) \*: E.F. means emitter follower (low impedance).

I/O block circuit diagrams and pin function descriptions (continued)

Note) The characteristics listed below are reference values based on the IC design and are not guaranteed.

| Pin<br>No. | Waveform and voltage | Internal circuit                                                                                         | Impedance | Description                           |

|------------|----------------------|----------------------------------------------------------------------------------------------------------|-----------|---------------------------------------|

| 35         | _                    | 3.3 V<br>9 V<br>2.3 V<br>1k 190k 146k                                                                    |           | 1 <sup>2</sup> C bus data input pin.  |

| 36         | _                    | 3.3 V<br>9 V<br>15k<br>12k<br>1k<br>1k<br>1k<br>1k<br>1k<br>1k<br>1k<br>1k<br>1k<br>1k<br>1k<br>1k<br>1k |           | I <sup>2</sup> C bus clock input pin. |

| 2          | 4.5                  | 90k 925µ 925µ                                                                                            | 45 kΩ     | Reference bias pin                    |

1. I/O block circuit diagrams and pin function descriptions (continued)

Note) The characteristics listed below are reference values based on the IC design and are not guaranteed.

| Pin<br>No.                       | Waveform and voltage | Internal circuit                     | Impedance | Description                   |

|----------------------------------|----------------------|--------------------------------------|-----------|-------------------------------|

| 37<br>39<br>41<br>43<br>45<br>47 | 3.7 V                | 9 V Pin 37, 39, 41, 43, 45, 47  12k  | E.F. *    | Video composite signal inputs |

| 38<br>40<br>42<br>44<br>46<br>48 | 3.7 V                | 9 V Pin 38, 40, 42, 44, 3.7 V 48 12k | E.F. *    | Video composite signal inputs |

Note) \*: E.F. means emitter follower (low impedance).

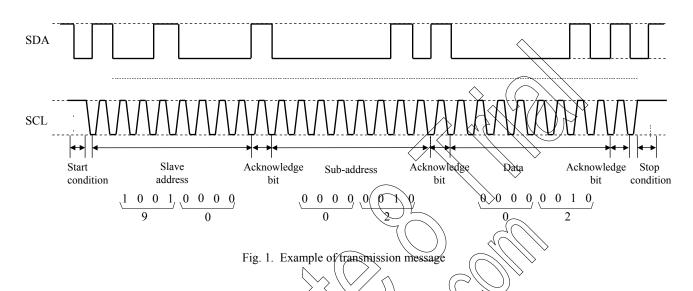

#### 2. I<sup>2</sup>C bus

For transmission messages, both SCL and SDA are transferred in the form of synchronized serial transmission. SCL is a clock of a specific frequency, and SDA indicates address data for controlling the receiving side and is transferred in parallel, being synchronized with SCL. Data is transferred in principle in 3 octets (bytes), and each one octet (one octet = 8 bits) includes one acknowledge bit. Frame structure is described below.

(a) Start condition The receiver becomes possible to receive data when SDA changes from High to Low while SCL is High.

(b) Stop condition The receiver halts receiving when SDA changes from Low to High while SCL is High.

(c) Slave address This is an address which is determined for each device. If other device address is sent, receiving will be halted.

(d) Sub-address This is an address which is determined for each function.

(e) Data This is control data.

This is a bit by which the master acknowledges that data was successfully received in each octet.

Master sends the High signal and the receiver sends back the Low signal as shown in Figure 1 with dotted line, causing the master to acknowledge the reception by the receiver. If the Low signal is not returned, communication will be halted.

Except start and stop conditions, SDA does not change while SCL is High.

- 2. I<sup>2</sup>C bus (continued)

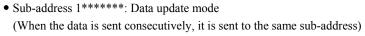

- 1) This contains 6 registers

- 2) Auto-increment function present:

- Sub-address 0\*\*\*\*\*\*: Auto-increment mode

(When the data is sent in consecutive order, the Sub-address will be changed in consecutive order, as data is input)

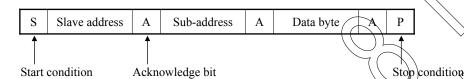

3) I<sup>2</sup>C bus protocol

• Slave address: 10010000 (90H)

• Format (usual)

• Auto-increment mode / data update mode

- Technical Data (continued)

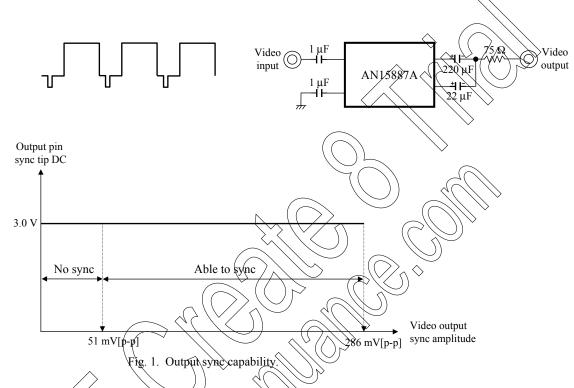

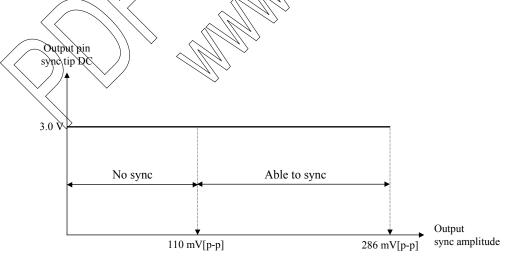

- 3. Video output synchronization

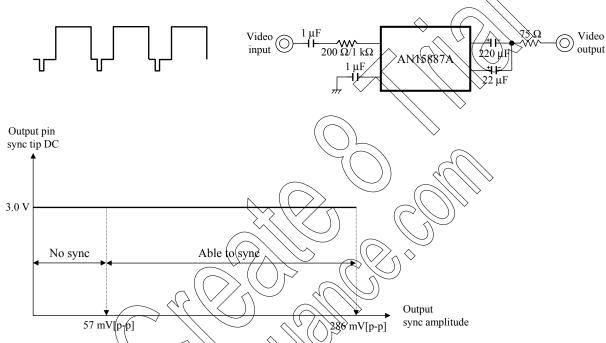

- 1) Video output synchronization with no resistor

At 9 V(25°C) white signal input, the synchronization capability of the Video output is as follows in Figure 1:

At 9 V(25°C) white signal input, for successful synchronization, the Video output sync amplitude must be at least 51 mV[p-

- Technical Data (continued)

- 3. Video output synchronization (continued)

- 2) Video output synchronization with series input resistor

At 9 V (25°C) white signal input, the synchronization capability of the video output (with series input resistor) is as follows in Figure 2 and Figure 3:

Fig. 2. Qutput sync capability with  $200 \Omega$  series input resistor.

At 9 V (25°C) white signal input with 200  $\Omega$  series input resistor, for successful synchronization, the video output sync amplitude must be at least 57 mV[p-p].

Fig 3. Output sync capability with 1  $k\Omega$  series input resistor.

At 9 V (25°C) white signal input with 1 k $\Omega$  series input resistor, for successful synchronization, the video output sync amplitude must be at least 71 mV[p-p].

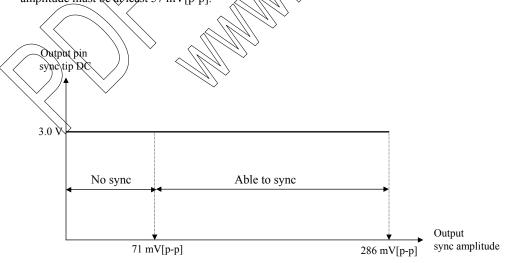

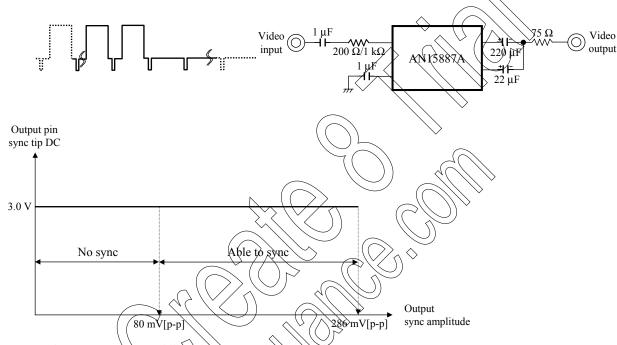

- Technical Data (continued)

- 3. Video output synchronization (continued)

- 2) Video output synchronization with series input resistor (continued)

At 9 V (25°C) alternate black and white signal input, the synchronization capability of the Video output (with series input resistor) is as follows in Figure 4 and Figure 5:

Fig 4. Output syne capability with 200  $\Omega$  series input resistor.

At 9 V (25°C) alternate black and white signal input with 200  $\Omega$  series input resistor, for successful synchronization, the video output sync amplitude must be at least 80 mV (p-p)

Fig 5. Output sync capability with 1  $k\Omega$  series input resistor.

At 9 V (25°C) alternate black and white signal input with 1 k $\Omega$  series input resistor, for successful synchronization, the video output sync amplitude must be at least 110 mV[p-p].

AN15887A Panasonic

### ■ Technical Data (continued)

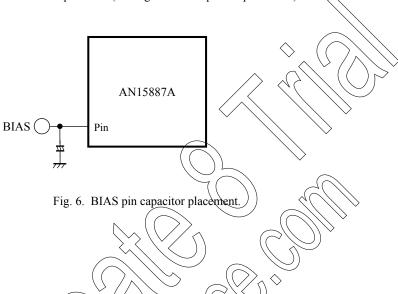

4. BIAS1 (Pin 2) and BIAS2 (Pin 11) pins capacitors

For capacitors placed at the BIAS pins, please use capacitors with a low temperature coefficient so that the capacitor value will not fluctuate too much at different temperatures (see Figure 6 for capacitor placement).

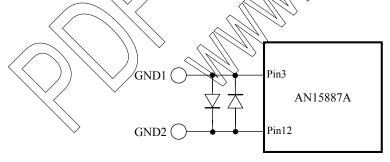

5. GND1 (Pin 3) and GND2 (Pin 12) pin connection

It is not recommended to float either GND2 and GND2 during normal operation. Such a connection could compromise the reliabilities of the AN15887A. This is due to the internal ESD protection diode between GND1 and GND2 can be damaged by large current surge. If the abnormal operation require either GND1 and GND2 to be floated, it is advisable to connect external diodes between GND1 and GND2. The connection details of external diodes is illustrated in Figure 7.

Fig. 7. External diodes

Recommended diode characteristics:

- a. Forward Voltage  $(V_F) \ge 1.1 \text{ V}$  at 1.0 A

- b. Junction Capacitance  $\leq$  12 pF at reverse voltage ( $V_R$ ) = 4.0 V

6.

$$P_D - T_a$$

diagram

### ■ Usage Notes

- 1. This IC is intended to be used for general electronic equipment [car navigation].

Consult our sales staff in advance for information on the following applications:

- Special applications in which exceptional quality and reliability are required, or if the failure or malfunction of this IC may directly jeopardize life or harm the human body.

- Any applications other than the standard applications intended.

- (1) Space appliance (such as artificial satellite, and rocket)

- (2) Medical equipment for life support

- (3) Submarine transponder

- (4) Control equipment for power plant

- (5) Disaster prevention and security device

- (6) Weapon

- (7) Others: Applications of which reliability equivalent to (1) to (7) is required

- 2. Pay attention to the direction of LSI. When mounting it in the wrong direction onto the PCB (printed-circuit-board), it might smoke or ignite.

- 3. Pay attention in the PCB (printed-circuit-board) pattern layout in order to prevent damage due to short circuit between pins. In addition, refer to the Pin Description for the pin configuration.

- 4. Perform a visual inspection on the PCB before applying power, otherwise damage might happen due to problems such as a solder-bridge between the pins of the semiconductor device. Also, perform a full technical verification on the assembly quality, because the same damage possibly can happen due to conductive substances, such as solder ball, that adhere to the LSI during transportation.

- 5. Take notice in the use of this product that it might break or occasionally smoke when an abnormal state occurs such as output pin-V<sub>CC</sub> short (power supply fault), output pin-GND short (ground fault), or output-to-output-pin short (load short).

And, safety measures such as an installation of fuses are recommended because the extent of the above-mentioned damage and smoke emission will depend on the current capability of the power supply.

- 6. When using the LSI for new models, verify the safety including the long term reliability for each product.

- 7. When the application system is designed by using this LSI, be sure to confirm notes in this book. Be sure to read the notes to descriptions and the usage notes in the book.

# Request for your special attention and precautions in using the technical information and semiconductors described in this book

- (1) If any of the products or technical information described in this book is to be exported or provided to non-residents, the laws and regulations of the exporting country, especially, those with regard to security export control, must be observed.

- (2) The technical information described in this book is intended only to show the main characteristics and application circuit examples of the products, and no license is granted under any intellectual property right or other right owned by our company or any other company. Therefore, no responsibility is assumed by our company as to the infringement upon any such right owned by any other company which may arise as a result of the use of technical information described in this book.

- (3) The products described in this book are intended to be used for standard applications or general electronic equipment (such as office equipment, communications equipment, measuring instruments and household appliances).

Consult our sales staff in advance for information on the following applications:

- Special applications (such as for airplanes, aerospace, automobiles, traffic control equipment, combustion equipment, life support systems and safety devices) in which exceptional quality and reliability are required, or if the value or malfunction of the products may directly jeopardize life or harm the human body.

- · Any applications other than the standard applications intended.

- (4) The products and product specifications described in this book are subject to change without notice for modification and/or improvement. At the final stage of your design, purchasing, or use of the products, therefore, ask for the most up-to-date Product Standards in advance to make sure that the latest specifications satisfy your requirements.

- (5) When designing your equipment, comply with the range of absolute maximum rating and the guaranteed operating conditions (operating power supply voltage and operating environment etc.). Especially, please be careful not to exceed the range of absolute maximum rating on the transient state, such as power-on, power-off and mode-switching. Otherwise, we will not be liable for any defect which may arise later in your equipment.

Even when the products are used within the guaranteed values, take into the consideration of incidence of break down and failure

- Even when the products are used within the guaranteed values, take into the consideration of incidence of break down and failure mode, possible to occur to semiconductor products. Measures on the systems such as redundant design, arcesting the spread of fire or preventing glitch are recommended in order to prevent physical injury fire, social damages, for example, by using the products.

- (6) Comply with the instructions for use in order to prevent breakdown and characteristics change due to external factors (ESD, EOS, thermal stress and mechanical stress) at the time of handling, mounting or at customer's process. When using products for which damp-proof packing is required, satisfy the conditions, such as shell life and the elapsed time since first opening the packages.

- (7) This book may be not reprinted or reproduced whether wholl or partially, without the prior written permission of Matsushita Electric Industrial Co., Ltd.