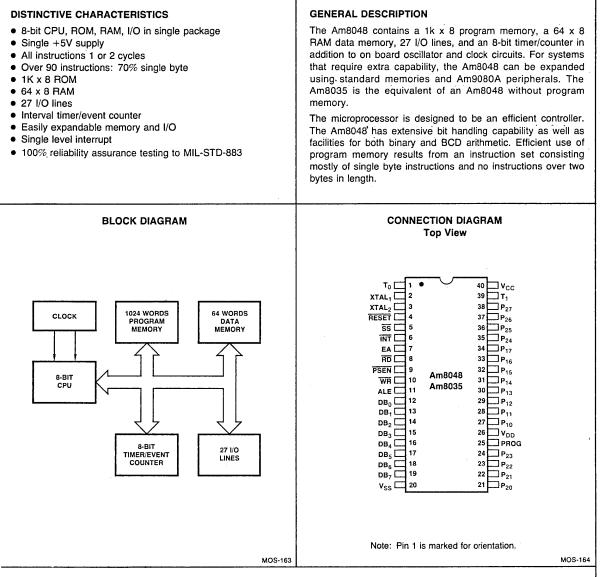

Am8048/8035 Single Chip 8-Bit Microcomputers

# **ORDERING INFORMATION**

| Package<br>Type             | Ambient Temperature<br>Specification      | ure<br>Order Numbers |                      |

|-----------------------------|-------------------------------------------|----------------------|----------------------|

| Hermetic DIP*<br>Molded DIP | $0^{\circ}C \leq T_{A} \leq +70^{\circ}C$ | AM8048DC<br>AM8048CC | AM8035DC<br>AM8035CC |

|                             |                                           | AM8048PC             | AM8035PC             |

\*Hermetic = Ceramic = DC = CC = D-40-1.

## Am8048/8035

# MAXIMUM RATINGS (Above which useful life may be impaired)

| Storage Temperature                       | -65°C to +150°C |

|-------------------------------------------|-----------------|

| Ambient Temperature Under Bias            | 0°C to +70°C    |

| Voltage on Any Pin with Respect to Ground | -0.5V to +7.0V  |

| Power Dissipation                         | 1.5W            |

Power Dissipation

The products described by this specification include internal circuitry designed to protect input devices from damaging accumulations of static charge. It is suggested nevertheless, that conventional precautions be observed during storage, handling and use in order to avoid exposure to excessive voltages.

Limits

# DC AND OPERATING CHARACTERISTICS

| $T_A = 0$ to 70°C | , v <sub>cc</sub> = v <sub>dd</sub> = | = +5.0V ±10% | (Note 1), | $V_{SS} = 0V$ |

|-------------------|---------------------------------------|--------------|-----------|---------------|

|-------------------|---------------------------------------|--------------|-----------|---------------|

| Parameters       | Description                                             | <b>Test Conditions</b>                         | Min | Тур | Max  | Units |

|------------------|---------------------------------------------------------|------------------------------------------------|-----|-----|------|-------|

| V <sub>IĽ</sub>  | Input Low Voltage (All Except RESET, X1, X2)            |                                                | 5   |     | .8   | Volts |

| V <sub>IL1</sub> | Input Low Voltage (RESET, X1, X2)                       |                                                | 5   |     | .6   | Volts |

| VIH              | Input High Voltage (All Except XTAL1, XTAL2, RESET)     |                                                | 2.0 |     | Vcc  | Volts |

| V <sub>IH1</sub> | Input High Voltage (X1, X2, RESET)                      |                                                | 3.8 |     | Vcc  | Volts |

| V <sub>OL</sub>  | Output Low Voltage (BUS)                                | $V_{OL} = 2.0 \text{mA}$                       |     |     | .45  | Volts |

| V <sub>OL1</sub> | Output Low Voltage (RD, WR, PSEN, ALE)                  | $I_{OL} = 1.8 \text{mA}$                       |     |     | .45  | Volts |

| V <sub>OL2</sub> | Output Low Voltage (PROG)                               | $I_{OL} = 1.0 \text{mA}$                       |     |     | .45  | Volts |

| V <sub>OL3</sub> | Output Low Voltage (All Other Outputs)                  | $I_{OL} = 1.6 \text{mA}$                       |     |     | .45  | Volts |

| V <sub>OH</sub>  | Output High Voltage (BUS)                               | $I_{OH} = -400 \mu A$                          | 2.4 | [   |      | Volts |

| V <sub>OH1</sub> | Output High Voltage (RD, WR, PSEN, ALE)                 | $I_{OH} = -100 \mu A$                          | 2.4 |     |      | Volts |

| V <sub>OH2</sub> | Output High Voltage (All Other Outputs)                 | $I_{OH} = -40\mu A$                            | 2.4 |     |      | Volts |

| ILI              | Input Leakage Current (T1, INT)                         | $V_{SS} \leq V_{IN} \leq V_{CC}$               |     |     | ±10  | μA    |

| 1,11             | Input Leakage Current (P10-P17, P20-P27, EA, SS)        | $V_{SS}$ + .45 $\leq$ $V_{IN} \leq$ $V_{CC}$   |     |     | -500 | μA    |

| ILO              | Output Leakage Current (BUS, TO) (High Impedance State) | $V_{SS}$ + .45 $\leq$ $V_{IN}$ $\leq$ $V_{CC}$ |     |     | ±10  | μA    |

| IDD              | V <sub>DD</sub> Supply Current                          |                                                |     | 5   | 15   | mA    |

| IDD + ICC        | Total Supply Current                                    |                                                |     | 60  | 135  | mA    |

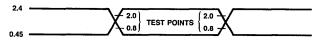

#### INPUT AND OUTPUT WAVEFORMS FOR AC TESTS

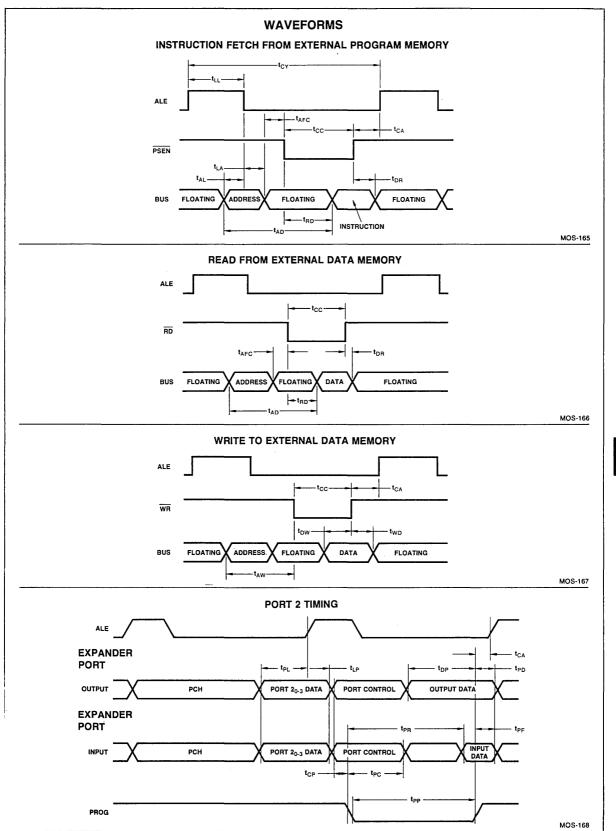

### **AC CHARACTERISTICS**

| $\Gamma_A = 0$ to 70°C | C, $V_{CC} = V_{DD} = +5.0V \pm 10\%$ (Note 1), | / <sub>SS</sub> = 0V<br>Test Conditions | Am8048<br>Am8035 |      |       |

|------------------------|-------------------------------------------------|-----------------------------------------|------------------|------|-------|

| Parameters             | Description                                     | (Note 2)                                | Min              | Max  | Units |

| t <sub>LL</sub>        | ALE Pulse Width                                 |                                         | 400              |      | ns    |

| t <sub>AL</sub>        | Address Set-up to ALE                           |                                         | 120              |      | ns    |

| t <sub>LA</sub>        | Address Hold from ALE                           |                                         | 80               |      | ns    |

| tcc                    | Control Pulse Width (PSEN, RD, WR)              |                                         | 700              |      | ns    |

| t <sub>DW</sub>        | Data Set-up Before WR                           |                                         | 500              |      | ns    |

| t <sub>WD</sub>        | Data Hold After WR                              | $C_L = 20 pF$                           | 120              |      | ns    |

| tCY                    | Cycle Time                                      | 6MHz XTAL (3.6MHz XTAL for -8)          | 2.5              | 15.0 | μs    |

| t <sub>DR</sub>        | Data Hold                                       |                                         | 0                | 200  | ns    |

| t <sub>RD</sub>        | PSEN, RD to Data In                             |                                         |                  | 500  | ns    |

| taw                    | Address Set-up to WR                            |                                         | 230              |      | ns    |

| t <sub>AD</sub>        | Address Set-up to Data in                       |                                         |                  | 950  | ns    |

| tAFC                   | Address Float to RD, PSEN                       |                                         | 0                |      | ns    |

| <sup>t</sup> CA        | Control Pulse to ALE                            |                                         | 10               |      | ns    |

Notes: 1.  $V_{CC}$  and  $V_{DD}$  for Am8035-8 are  $\pm 5\%.$

2. Control Outputs:  $C_L = 80 pF$ .

Bus Outputs:  $C_L = 150 pF$ ,  $t_{CY} = 2.5 \mu s$ .

# Am8048/8035

7

# Am8048/8035

# AC CHARACTERISTICS (Port 2 Timing)

$T_A = 0$  to 70°C,  $V_{CC} = 5V \pm 10\%$  (Note 1),  $V_{SS} = 0V$

| A = 0.0700, VCC = 0.0 = 1000 (1000 - 1), VSS = 0.0 |                                                 |                 |      |      |       |

|----------------------------------------------------|-------------------------------------------------|-----------------|------|------|-------|

| Parameters                                         | Description                                     | Test Conditions | Min. | Max. | Units |

| t <sub>CP</sub>                                    | Port Control Set-up before Falling Edge of PROG |                 | 110  |      | ns    |

| tPC                                                | Port Control Hold after Falling Edge of PROG    |                 | 100  |      | ns    |

| t <sub>PR</sub>                                    | PROG to Time P2 Input Must be Valid             |                 |      | 810  | ns    |

| t <sub>DP</sub>                                    | Output Data Set-up Time                         |                 | 250  |      | ns    |

| t <sub>PD</sub>                                    | Output Data Hold Time                           |                 | 65   |      | ns    |

| t <sub>PF</sub>                                    | Input Data Hold Time                            |                 | 0    | 150  | ns    |

| t <sub>PP</sub>                                    | PROG Pulse Width                                |                 | 1200 |      | ns    |

| t <sub>PL</sub>                                    | Port 2 I/O Data Set-up                          |                 | 350  |      | ns    |

| t <sub>LP</sub>                                    | Port 2 I/O Data Hold                            |                 | 150  |      | ns    |

## **PIN DESCRIPTION**

#### VSS

Circuit GND potential.

#### VDD

Power supply; +5V during operation. Low power standby pin for Am8048 ROM.

## Vcc

Main power supply; +5V.

# PROG

Output strobe for Am8243 I/O expander.

## P<sub>10</sub>-P<sub>17</sub> Port 1

8-bit quasi-bidirectional port.

#### P20-P27 Port 2

8-bit quasi-bidirectional port.

$\mathsf{P}_{20}\text{-}\mathsf{P}_{23}$  contain the four high order program counter bits during an exteral program memory fetch and serve as a 4-bit I/O expander bus for Am8243.

#### D<sub>0</sub>-D<sub>7</sub> BUS

True bidirectional port which can be written or read synchronously using the  $\overline{\text{RD}}$ ,  $\overline{\text{WR}}$  strobes. The port can also be statically latched.

Contains the 8 low order program counter bits during an external program memory fetch, and receives the addressed instruction under the control of PSEN. Also contains the address and data during an external RAM data store instruction, under control of ALE, RD and WR.

## T<sub>0</sub>

Input pin testable using the conditional transfer instructions  $JT_0$  and  $JNT_0.$   $T_0$  can be designated as a clock output using ENT0 CLK instruction.  $T_0$  is also used during programming.

# $\mathbf{T}_1$

Input pin testable using the  $JT_1$ , and  $JNT_1$  instructions. Can be designated the timer/counter input using the STRT CNT instruction.

# INT

Interrupt input. Initiates an interrupt if interrupt is enabled. Interrupt is disabled after a reset. Also testable with conditional jump instruction (Active low).

Am8048

## RD

Output strobe activated during a BUS read. Can be used to enable data onto the BUS from an external device.

Used as a Read Strobe to External Data Memory (Active low).

#### RESET

Input which is used to initialize the processor. Also used during power down (Active low).

## WR

Output strobe during a BUS write (Active low) (Non-TTL VIH).

Used as write strobe to External Data Memory.

#### ALE

Address Latch Enable. This signal occurs once during each cycle and is useful as a clock output.

The negative edge of ALE strobes address into external data and program memory.

## PSEN

Program Store Enable. This output occurs only during a fetch to external program memory (Active low).

#### SS

Single step input can be used in conjunction with ALE to "single step" the processor through each instruction (Active low).

# EA

External Access input which forces all program memory fetches to reference external memory. Useful for emulation and debug, and essential for testing and program verification (Active high).

### XTAL<sub>1</sub>

One side of crystal input for internal oscillator. Also input for external source (Not TTL compatible).

#### XTAL<sub>2</sub>

Other side of crystal input.