# Am29CPL141/Am29CPL151

Advanced Micro Devices

CMOS Field Programmable Controller (FPC)

## DISTINCTIVE CHARACTERISTICS

- Implements complex state machines

- High-speed, low-power CMOS EPROM technology

- Direct plug-in replacement for the bipolar Am29PL141

- Seven conditional inputs (each can be registered as a programmable option), 16 outputs

- 64-word by 32-bit CMOS EPROM

- Up to 30-MHz clock rate

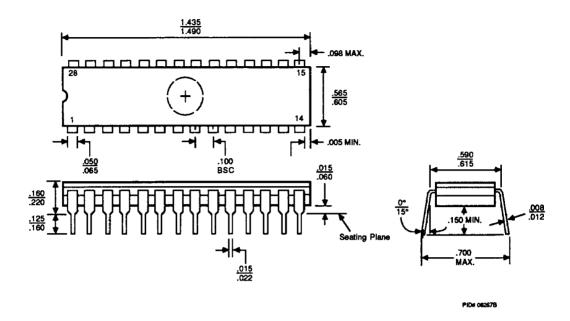

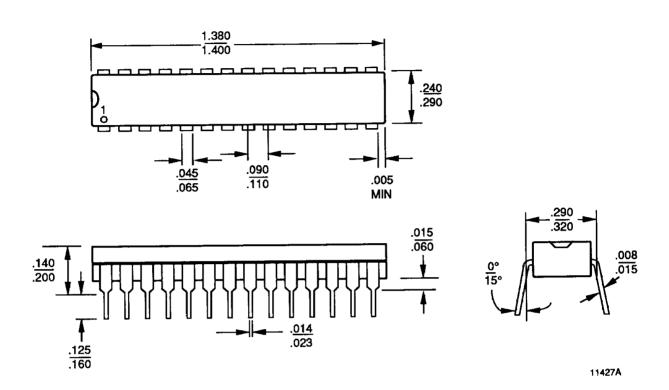

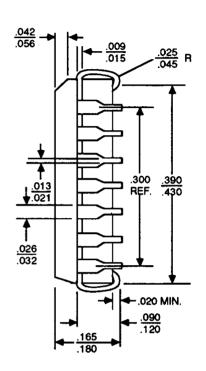

- Available in a wide selection of 28-pin packages, including SKINNYDIP™

0.6" CERDIP windowed, 0.3" CERDIP windowed,

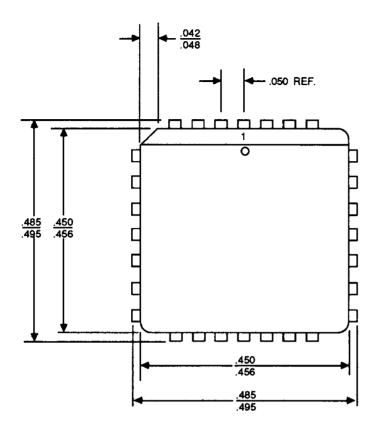

0.3" plastic DIP OTP, PLCC OTP

- 29 instructions

Conditional branching, conditional looping, conditional subroutine call, multiway branch

## **GENERAL DESCRIPTION**

The Am29CPL141, a direct plug-in replacement for the Am29PL141, is a CMOS, single-chip Field Programmable Controller (FPC). It allows implementation of complex state machines and controllers by programming the appropriate sequence of instructions. Jumps, loops, and subroutine calls, conditionally executed based on the test inputs, provide the designer with powerful control flow primitives.

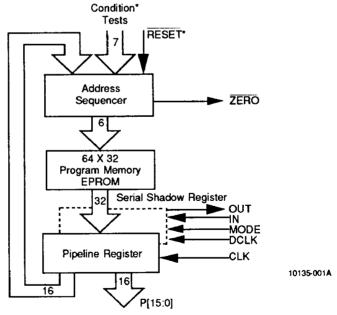

Intelligent control may be distributed throughout the system by using FPCs to control various self-contained functional units, such as register file/ALU, I/O, interrupt, diagnostic, and bus control units. An Address sequencer, the heart of the FPC, provides the address to an internal 64-word by 32-bit EPROM.

The Am29CPL151 is electrically and functionally identical to the Am29CPL141 but is manufactured in a space-saving 300 mil DIP package as well as being offered in surface mount packaging.

This UV-erasable and reprogrammable device utilizes proven floating-gate CMOS EPROM technology to ensure high reliability, easy programming, and better than 99.9% programming yields. The Am29CPL141/151 is offered in both windowed and One-Time Programmable (OTP) packages. OTP plastic DIP and PLCC devices are ideal for volume production.

## SIMPLIFIED BLOCK DIAGRAM

<sup>\*</sup>Each condition test input can be individually registered as a programmable option; the RESET input can be registered as a programmable option.

SKINNYDIP is a trademark of Advanced Micro Devices, Inc.

Publication # Rev. Amendment 10135 B /0 Issue Date: May 1989

## Am29CPL100 FAMILY FIELD-PROGRAMMABLE CONTROLLERS

| Part No.   | Technology | Memory | Word | Input | Output | Package                                                        |

|------------|------------|--------|------|-------|--------|----------------------------------------------------------------|

| Am29CPL141 | CMOS       | EPROM  | 64   | 7     | 16     | 600 mil 28-pin<br>CERDIP Windowed                              |

| Am29CPL142 | CMOS       | EPROM  | 128  | 8     | 16     | 600 mil 28-pin<br>CERDIP Windowed                              |

| Am29CPL151 | CMOS       | EPROM  | 64   | 7     | 16     | 300 mil 28-pin<br>CERDIP Windowed<br>Plastic OTP,<br>PLCC OTP  |

| Am29CPL152 | CMOS       | EPROM  | 128  | 8     | 16     | 300 mil 28-pin<br>CERDIP Windowed,<br>Plastic OTP,<br>PLCC OTP |

| Am29CPL154 | CMOS       | EPROM  | 512  | 8     | 16     | 300 mil 28-pin<br>CERDIP Windowed,<br>Plastic OTP,<br>PLCC OTP |

# **RELATED AMD PRODUCTS**

| Part No  | Description                                    |

|----------|------------------------------------------------|

| Am27S35A | 1024 x 8 Registered PROM                       |

| Am29C01  | CMOS 4-Bit Slice Microprogrammable CPU         |

| Am2914   | Vectored Priority Interrupt Controller         |

| Am2925   | Clock Generator                                |

| Am2940   | DMA Address Generator                          |

| Am29C101 | CMOS 16-Bit Microcontroller Slice              |

| Am29C116 | CMOS 16-Bit Microprocessor                     |

| Am29C117 | CMOS 2-Port Version of Am29C116                |

| Am29C3XX | CMOS 32-Bit Microprogrammable Family           |

| Am29C325 | CMOS Single-Precision Floating-Point Processor |

| Am29C327 | CMOS Double Precision Floating-Point Processor |

| Am29C8XX | CMOS High-Performance Bus Interface Family     |

| Am29C818 | CMOS SSR™ Diagnostics Pipeline Register        |

SSR is a trademark of Advanced Micro Devices, Inc.

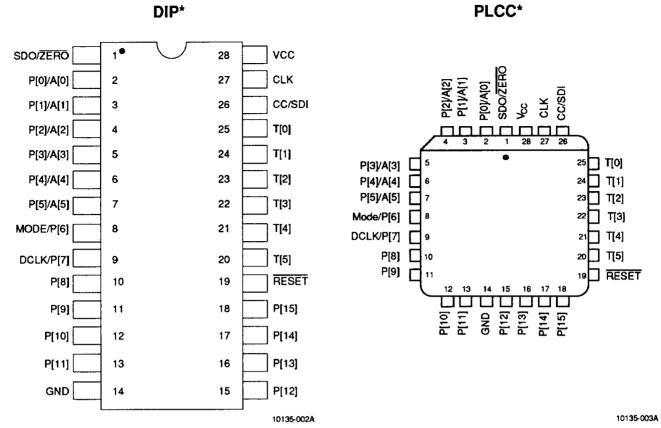

# CONNECTION DIAGRAMS Top View

Note: Pin 1 is marked for orientation.

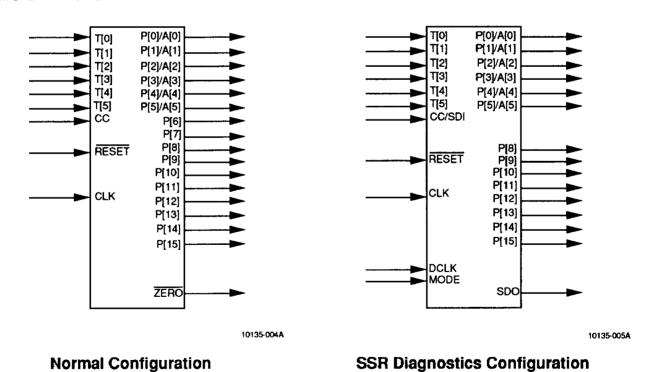

## LOGIC SYMBOLS

<sup>\*</sup>Also available in 28-pin LCC; pinout identical to PLCC. Plastic DIP and PLCC are One-Time Programmable (OTP), non-windowed packages.

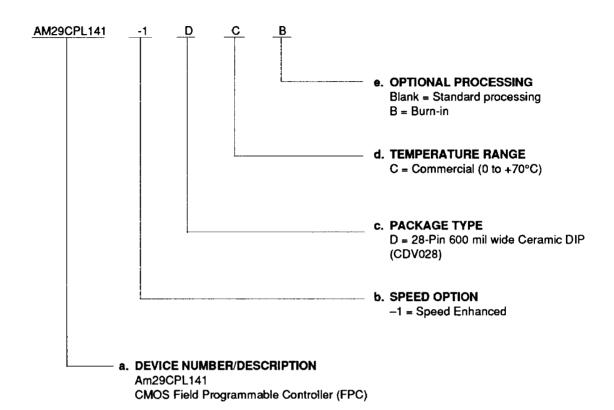

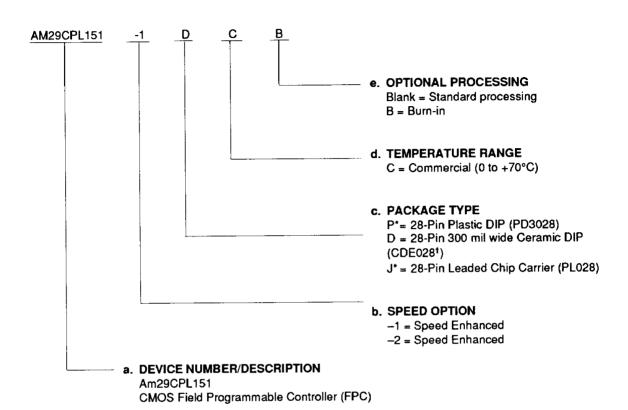

## ORDERING INFORMATION

## **Standard Products**

AMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of:

- a. Device Number

- b. Speed Option (if applicable)

- c. Package Type

- d. Temperature Range

- e. Optional Processing

| Valid Combinations |         |  |  |  |  |  |

|--------------------|---------|--|--|--|--|--|

| AM29CPL141         | DC. DCB |  |  |  |  |  |

| AM29CPL141-1       | DC, DCB |  |  |  |  |  |

## **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations, to check on newly released valid combinations, and to obtain additional data on AMD's standard military grade products.

Note: The Am29CPL141 is the ordering part number for devices packaged in 28-pin, 0.6" ceramic windowed DIP packages. All specifications and functional description in this data sheet refer equally to the Am29CPL141 and Am29CPL151 except for package drawings.

## ORDERING INFORMATION Standard Products

AMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of:

- a. Device Number

- b. Speed Option (if applicable)

- c. Package Type

- d. Temperature Range

- e. Optional Processing

| Valid Comb   | Valid Combinations |  |  |  |  |  |  |

|--------------|--------------------|--|--|--|--|--|--|

| AM29CPL151   |                    |  |  |  |  |  |  |

| AM29CPL151-1 | PC, DC, DCB,<br>JC |  |  |  |  |  |  |

| AM29CPL151-2 |                    |  |  |  |  |  |  |

## **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations, to check on newly released valid combinations, and to obtain additional data on AMD's standard military grade products.

<sup>\*</sup>Plastic DIP and PLCC are One-Time Programmable (OTP), non-windowed packages.

<sup>†</sup>Preliminary; package in development

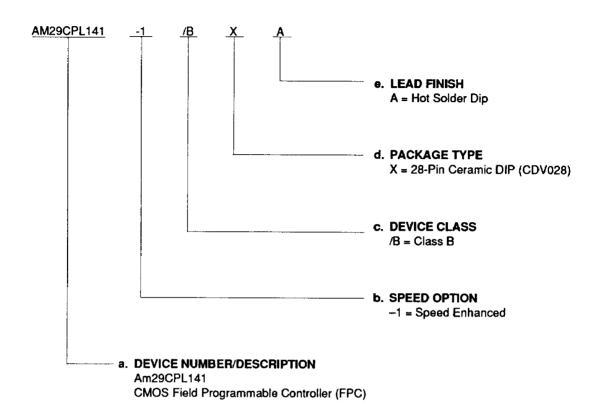

## **MILITARY ORDERING INFORMATION**

## **APL Products**

AMD products for Aerospace and Defense applications are available in several packages and operating ranges. APL (Approved Products List) products are fully compliant with MIL-STD-883C requirements. The order number (Valid Combination) is formed by a combination of:

- a. Device Number

- b. Speed Option (if applicable)

- c. Device Class

- d. Package Type

- e. Lead Finish

| Valid Comb   | inations |

|--------------|----------|

| AM29CPL141   | (DVA     |

| AM29CPL141-1 | /BXA     |

## Valid Combinations

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations, to check on newly released valid combinations, and to obtain additional data on AMD's standard military grade products.

## **Group A Tests**

Group A tests consists of Subgroups 1, 2, 3, 7, 8, 9, 10, 11.

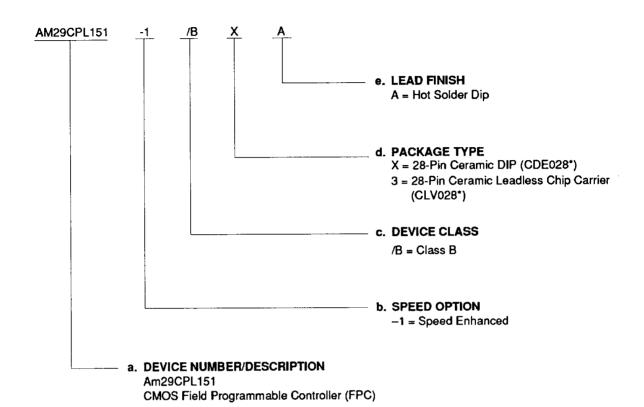

## **MILITARY ORDERING INFORMATION**

## **APL Products**

AMD products for Aerospace and Defense applications are available in several packages and operating ranges. APL (Approved Products List) products are fully compliant with MIL-STD-883C requirements. The order number (Valid Combination) is formed by a combination of:

a. Device Number

- b. Speed Option (if applicable)

- c. Device Class

- d. Package Type

- e. Lead Finish

| Valid Combinations |            |  |  |  |  |  |

|--------------------|------------|--|--|--|--|--|

| AM29CPL151         | /DVA /D2A  |  |  |  |  |  |

| AM29CPL151-1       | /BXA, /B3A |  |  |  |  |  |

## **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations, to check on newly released valid combinations, and to obtain additional data on AMD's standard military grade products.

## **Group A Tests**

Group A tests consists of Subgroups 1, 2, 3, 7, 8, 9, 10, 11.

\*Preliminary; package in development

## PIN DESCRIPTION

# CC[SDI] Optionally Registered Condition Code-TEST (Input)

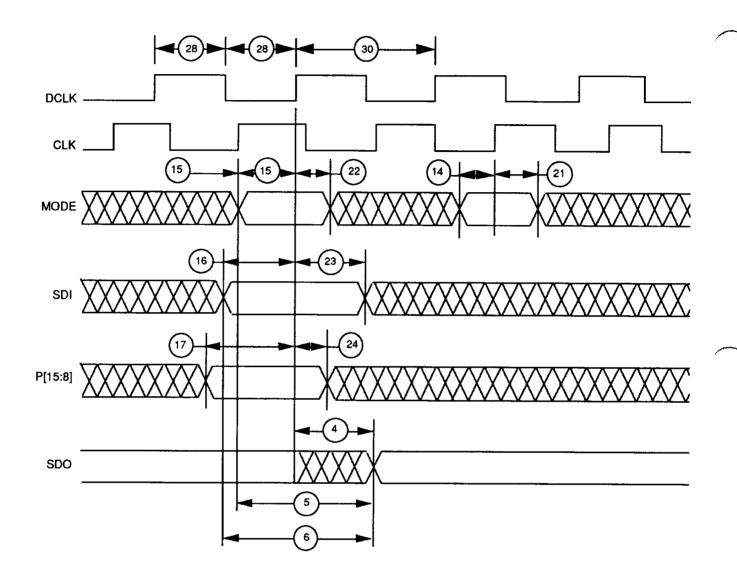

When the TEST (P[24:22]) field of the executing instruction is set to 6 (binary 110), CC is selected to be the conditional input. In SSR diagnostic configuration, CC is also the Serial Data Input (SDI). An EPROM bit associated with this input may be programmed to make this input a registered input. The default state of this input is unregistered.

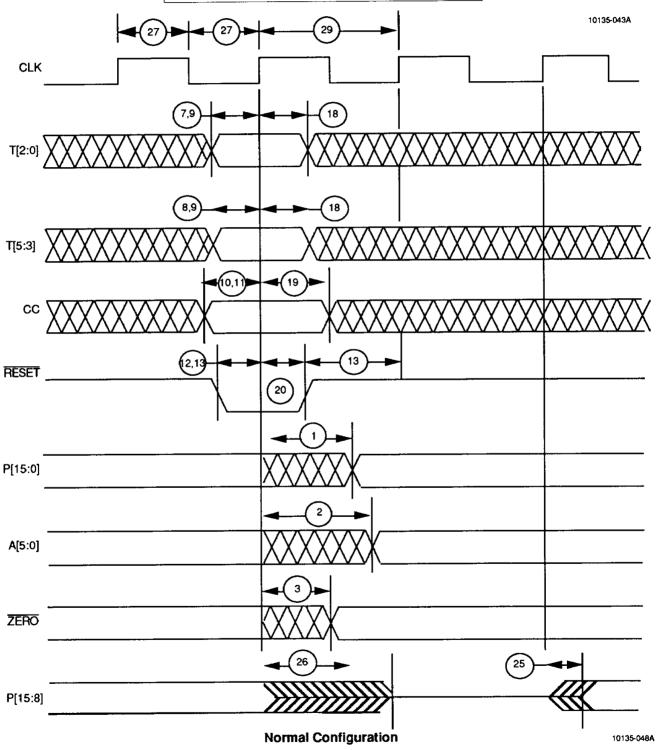

### CLK Clock (Input)

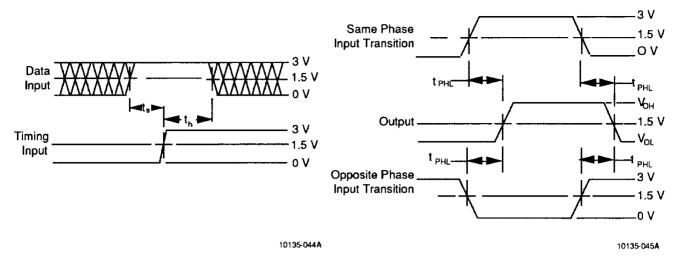

The rising edge of the clock latches the program counter, count register (CREG), subroutine register (SREG), pipeline register, and EQ flag. The rising edge of the clock also latches the test input registers, CC register, and the RESET register if their respective configuration bits are set to enable internal synchronizing registers.

## P[15:8] (Outputs)

The upper eight general-purpose control outputs are enabled by the OE signal from the pipeline register. When OE is HIGH, P[15:8] are enabled, and when LOW, P[15:8] are three-stated.

## P[7:6], P[5:0]/A[5:0] [DCLK, MODE] (Outputs)

The lower eight general-purpose control outputs are permanently enabled. In the SSR diagnostic configuration, P[7] becomes the diagnostic clock input DCLK and P[6] becomes the diagnostic control input MODE. In expand mode (when the EXP bit is programmed) bits P[5:0] become the Program Memory address outputs A[5:0].

# RESET Optionally Registered Reset (Input; Active LOW)

When the reset input is LOW, the output of the PC MUX is forced to the uppermost program address (63). On the next rising edge of the clock, this address (63) is loaded into the program counter; the instruction at location 63 is loaded into the pipeline register, and the EQ flag is cleared. A programmable configuration bit allows the option of making this a registered input. If RESET is internally registered, the first rising edge of the clock latches it. On the next rising edge of the clock, the EQ flip-flop is cleared and the contents of memory location 63 are loaded into the pipeline register. The default state of this input is unregistered.

## T[5:0] Optionally Registered Test (Inputs)

In conditional instructions, the TEST inputs can be used as individual condition codes selected by the TEST field in the pipeline register. The T[5:0] inputs can also be used as a branch address when performing a program branch or as a count value to be loaded into the CREG. Each of these inputs has an EPROM bit associated with it. This bit may be programmed such that the corresponding input becomes a registered input. The default state of these inputs is unregistered.

## ZERO [SDO] Zero (Output; Active LOW)

A LOW state on the ZERO output indicates that the CREG value is zero. In the SSR diagnostic configuration, ZERO becomes the Serial Data Output (SDO). This change is only on the output pin; internally, the zero-detect function is unchanged.

## **FUNCTIONAL DESCRIPTION**

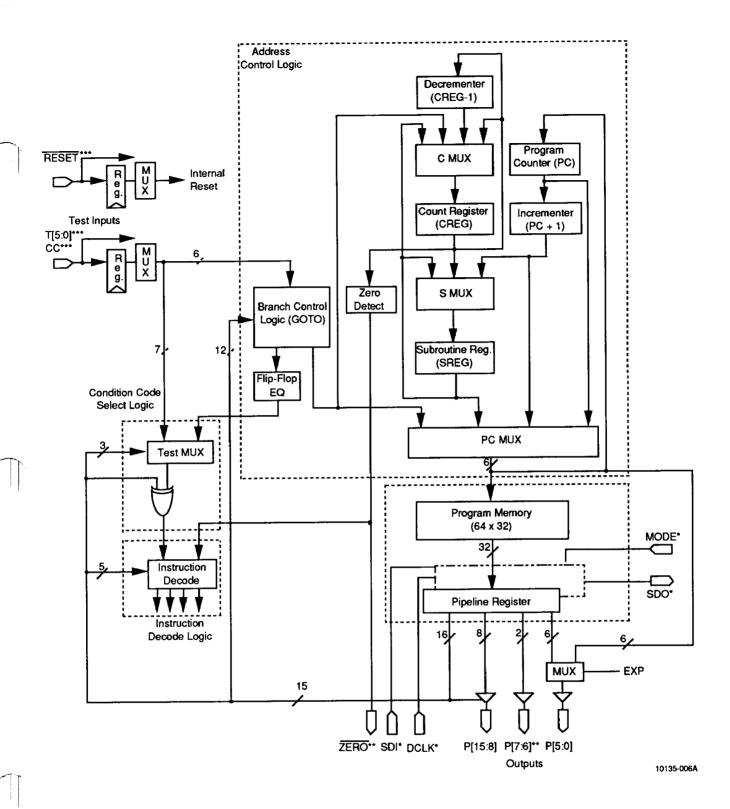

Figure 1, the detailed block diagram of the Am29CPL141 PIC, shows logic blocks and interconnecting buses that permit parallel performance of different operations in a single instruction. The FPC consists of four main logic blocks: the program memory, address control logic, condition code selection logic, and instruction decode. A fifth optional block is the Serial Shadow Register (SSR).

The program memory contains the user-defined instruction flow and output sequence. The address control logic addresses the program memory. This control logic supports high-level instruction functions including conditional branches, subroutine calls and returns, loops, and multiway branches. The condition code selection logic selects the condition code input to be tested when a conditional instruction is executed. The polarity of the selected condition code input is controlled by the POL bit in the microword. The instruction decode generates the control signals necessary to perform the instruction specified by the instruction part (P[31:16]) of the microword. The SSR enables in-system testing to isolate problems down to the IC level.

## **Program Memory**

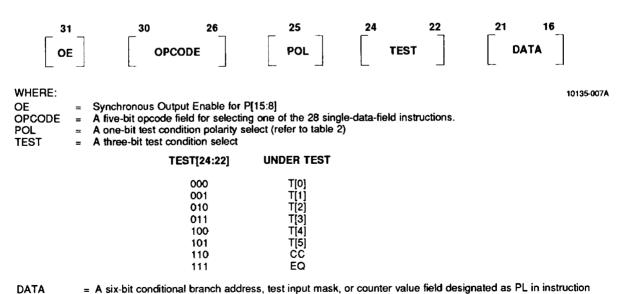

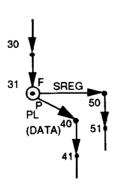

The FPC program memory is a 64-word by 32-bit EPROM with a 32-bit pipeline register at its output. The upper 16 bits (P[31:16]) of the pipeline register are internal to the PIC and form the instruction to control address sequencing. The format for instructions is: a one-bit synchronous Output Enable OE, a five-bit OP-CODE, a one-bit test polarity select POL, a three-bit TEST condition select field, and a six-bit immediate DATA field. The DATA field is used to provide branch addresses, test input masks, and counter values.

The lower 16 bits (P[15:0]) of the pipeline register are brought out as user-defined, general-purpose control outputs. The upper eight control outputs (P[15:8]) are three-stated when OE is programmed as a LOW. The lower eight control bits (P[7:0]) are always enabled. Outputs P[5:0] will contain the next instruction address when the optional EXP EPROM cell is programmed.

\* These pins available only in SSR mode.

\*\* These pins available only in normal mode.

\*\*\* Each of the T[5:0], RESET, and CC inputs can be individually registered or left unregistered as a programmable option.

Figure 1. Am29CPL141 Detailed Block Diagram

## **Address Control Logic**

The address control logic consists of five smaller logic blocks. These are:

PC MUX - Program counter multiplexer

P CNTR - Program counter (PC) and incrementer

(PC + 1)

SUBREG - Subroutine register (SREG) with subrou-

tine mux (S MUX)

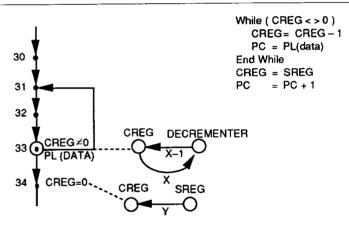

- Count register (CREG) with counter mux **CNTR** (C MUX), decrementer (CREG-1), and

**GOTO** - Specialized branch control logic

The PC MUX is a six-bit, four-to-one multiplexer. It selects either the PC, PC + 1, SREG, or GOTO output as the next microaddress input to the Program Memory and to the PC. The PC thus always contains the address of the instruction in the pipeline register. During a Reset, the PC MUX output is forced to all ones, selecting location 63 from Program Memory.

The P CNTR block consists of a six-bit register (PC) driving a six-bit combinatorial incrementer (PC + 1). Either the present or the incremented values of PC can address the Program Memory. The incremented value of PC can be saved as a subroutine return address. The present PC value can address the Program Memory when waiting for a condition to become valid. PC + 1 addresses the Program Memory for sequential program flow, for unconditional instructions, and as a default for conditional instructions.

The SUBREG block consists of a six-bit, three-to-one multiplexer (S MUX) driving a six-bit register (SREG). The three possible SREG inputs are PC + 1, CREG. and SREG. SREG normally operates as a one-deep stack to save subroutine return addresses. PC + 1 is the input source when performing subroutine calls, and PC MUX is the output destination when performing return from subroutine.

The CNTR block consists of a six-bit, four-to-one multiplexer (C MUX), driving a six-bit register (CREG); a sixbit combinatorial decrementer (CREG-1); and a zerodetection circuit. The CNTR logic block is typically used for timing functions and iterative loop counting.

The SUBREG and CNTR can be considered as one logic block because of their unique interaction. Both have the other as an additional input source and output destination. The CREG can therefore be an additional stack location when not used for counting, and the SREG can be a nested-count location when not used as a stack location. Thus the SREG and CREG can operate in three different modes:

- 1. As a separate one-deep stack and counter

- 2. As a two-deep stack

- 3. As a two-deep nested counter

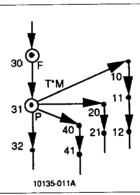

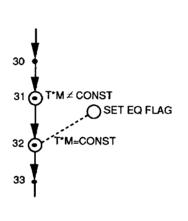

The GOTO logic block serves three functions:

- 1. It provides a six-bit count value from the DATA field in the pipeline register (P[21:16]) or from the TEST inputs T[5:0] masked by the DATA field P[21:16]. This is represented by T\*M.

- 2. It provides a branch address from the DATA field in the pipeline register P[21:16] or from the TEST inputs T[5:0] masked by the DATA field P[21:16]. This is represented by T\*M.

- 3. It compares T[5:0] masked by the MASK field P[21:16], called T\*M, to the CONSTANT field from the pipeline register P[27:22]. If a match occurs, the EQ flip-flop is set. EQ remains unchanged if there is no match. Constant field bits that correspond to masked test bits must be zero.

The EQ flag can be tested by the condition code selection logic. Multiple tests of any group of T inputs in a manner analogous to sum-of-products can be performed since a no-match comparison does not reset the EQ flag. Any conditional branch on EQ will reset the EQ flag. Conditional returns on EQ will not change the EQ flag. RESET input LOW will reset the EQ flag.

NOTE: A zero in the MASK field blocks the corresponding bit in the TEST field; a one activates the corresponding bit.

The constant field bits that correspond to masked test field bits must be zero. A zero is substituted for masked test field bits. The "POL" bit is a "don't care" when using test inputs to load registers.

Note that when the inputs are internally registered (programmable option) they must meet the register setup time on the cycle preceding the one in which they are to be used.

## Condition Code Selection Logic

The condition code selection logic consists of an eightto-one multiplexer. The eight test condition inputs are the device inputs CC, T[5:0], and the EQ flag. The TEST field P[24:22] selects one of the eight conditions to test.

The polarity bit POL in the instruction allows the user to test for either a pass or fail condition. Refer to table 2 for details.

Note that when the inputs are internally registered (programmable option) they must meet the register setup time on the cycle preceding the one in which they are to be used.

## Instruction Decode

The instruction decoder is a PLA that generates the control for 29 different instructions. The decoder inputs include the OPCODE field P[30:26], the zero detection output from the CNTR, and the selected test condition code from the condition code selection logic.

## **Operational Modes**

The Am29CPL141 operates as a six-bit microcontroller in normal mode, and there are several configuration bits that can be programmed to modify this normal operation (see diagram below). The EXP bit allows the six program address lines from the PC MUX to be output on the lower six bits of the output pins (P[5:0]) so that a user can expand the width of the control lines by using external registered memories. The SSR bit allows onchip diagnostic capabilities for in-system testing. The remaining bits serve to individually select whether the input pins will be unsynchronized or not. The default setting of these bits (unprogrrammed,1) will cause each pin to be unsynchronized, and so programming a given bit (to 0) will cause that corresponding input to become internally synchronized.

| EPROM<br>Address | EPR | OM—Config | uration Bits |          |     |                |     |                   |

|------------------|-----|-----------|--------------|----------|-----|----------------|-----|-------------------|

| Byte 7<br>Row 1  |     |           |              | i        |     | EXP            | SSR | Reset<br>Register |

|                  |     |           |              |          |     |                |     |                   |

| Byte 7           |     |           | T            | <b>T</b> | T _ | т              | т   |                   |

| Row 0            |     | cc        | 15           | 4        | , s | T <sub>2</sub> | '1  | T <sub>e</sub>    |

## Am29CPL141 SSR Diagnostics Option

As a programmable option, the Am29CPL141 FPC may be configured to contain Serial Shadow Register (SSR) diagnostics capability. SSR diagnostics is a simple, straightforward method of in-system testing to isolate problems down to the IC level.

The SSR diagnostics configuration activates a 32-bitwide D-type register called a "shadow" register, on the pipeline register inputs. The shadow register can be serially loaded from the SDI pin, parallel loaded from the pipeline register, or held. The pipeline register can be loaded from the Program Memory in normal mode or from the shadow register during diagnostics. A redefinition of four device pins is required to control the different diagnostics functions. CC also functions as the Serial Data Input (SDI), ZERO becomes the Serial Data Output (SDO), P[7] becomes the diagnostic clock (DCLK), and P[6] becomes the diagnostic mode control (MODE). The various diagnostic and normal modes are shown in table 1.

Serially loading a test instruction into the shadow register and parallel loading the shadow register contents into the pipeline register forces execution of the test instruction. The test result can then be clocked into the pipeline register as in normal operation mode, parallel loaded into the shadow register, and serially shifted out for system diagnostics.

## Am29CPL141 General Instruction Format

= A six-bit conditional branch address, test input mask, or counter value field designated as PL in instruction mnemonics

## **Am29CPL141 Comparison Instruction Format**

31

WHERE:

Synchronous Output Enable for P[15:8]

**OPCODE**

Compare instruction (binary 100)

CONSTANT MASK

A six-bit constant for equal to comparison with T\*M

A six-bit mask field for masking the incoming T[5:0] inputs

10135-008A

## Table 1

| Inputs |      |       |          |                | Output                                          | s                                  | _                                               |  |  |

|--------|------|-------|----------|----------------|-------------------------------------------------|------------------------------------|-------------------------------------------------|--|--|

| SDI    | MODE | DCLK  | CLK      | SDO            | Shadow<br>Register                              | Pipeline<br>Register               | Operation                                       |  |  |

| D      | L    | 1     | H,L,↓    | S <sub>o</sub> | $S_{i-1} \leftarrow S_i \\ S_{31} \leftarrow D$ | Hold                               | Serial Right-Shift Register                     |  |  |

| СС     | L    | H,L,↓ | <b>↑</b> | S <sub>o</sub> | Hold                                            | P <sub>i</sub> ←EPROM <sub>i</sub> | Normal Load Pipeline<br>Register from EPROM     |  |  |

| L      | н    | 1     | H,L,↓    | L              | S <sub>i</sub> ←P <sub>i</sub>                  | Hold                               | Load Shadow Register*<br>from Pipeline Register |  |  |

| х      | н    | H,L,↓ | 1        | SDI            | Hold                                            | P <sub>i</sub> ←S <sub>i</sub>     | Load Pipeline Register from Shadow Register     |  |  |

| н      | н    | 1     | H,L,↓    | н              | Hold Hold                                       |                                    | Hold Shadow Register                            |  |  |

<sup>\*</sup>S7, S6 are undefined. S[15:8] load from the source driving pins P[15:8]. If P[31] in the microword is a ONE, S[15:8] are loaded from the pipeline register. If P[31] in the microword is a ZERO, S[15:8] are loaded from an external source.

Key:

HIGH

LOW

Don't Care

LOW-to-HIGH transition HIGH-to-LOW transition

Table 2

| Input Condition<br>Being Tested | POL | Condition |

|---------------------------------|-----|-----------|

| 0                               | 0   | Fail      |

| 0                               | 1   | Pass      |

| 1                               | 0   | Pass      |

| 1                               | 1   | Fail      |

## Am29CPL141 INSTRUCTION SET DEFINITION

- = Other instruction

- Instruction being described

- = Register in part

P = Test Pass

F = Test Fail

X,Y are arbitrary values in the CREG or SREG

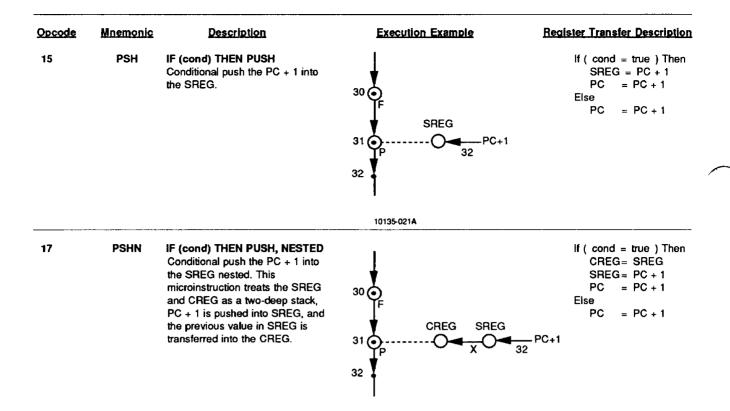

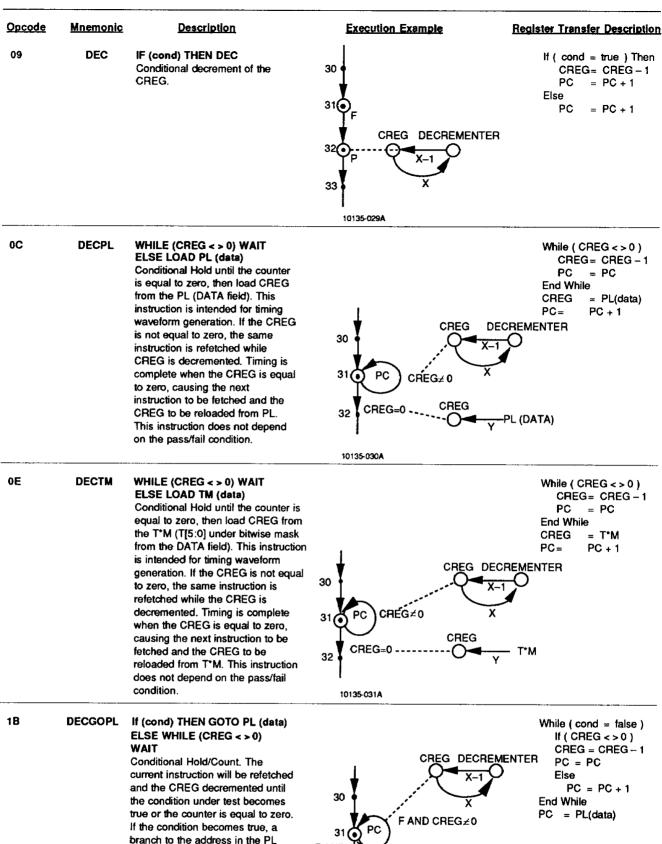

Opcode Mnemonic

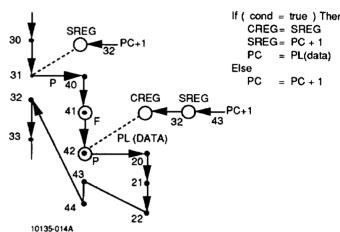

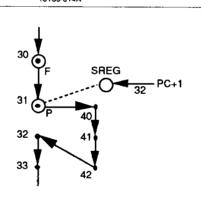

19 GOTOPL

<u>Description</u>

IF (cond) THEN GOTO PL (data)

Conditional branch to the address

in the PL (DATA field). The EQ

flag will be reset if the test field

selects it and the condition

passes.

Register Transfer Description

If ( cond = true ) Then PC = PL(data) Else PC = PC + 1

10135-009A

0B GOTOPLZ

IF (CREG=0) THEN GOTO PL (data)

Conditional branch to the address in the PL (DATA field) when CREG is equal to zero. This instruction does not depend on the pass/fail condition. The EQ flag will be reset if the test field selects it and the CREG is equal to zero.

If ( CREG = 0 ) Then PC = PL(data) Else PC = PC+1

10135-010A

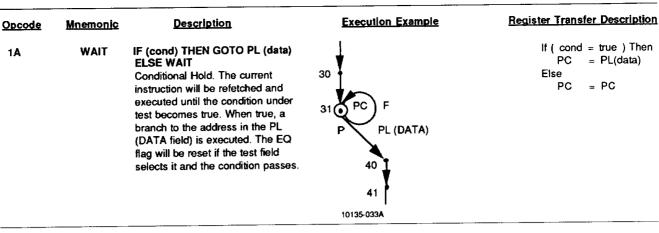

0F

GOTOTM IF (cond) THEN GOTO TM (data)

Conditional branch to the address defined by the T\*M (T[5:0] under bitwise mask from the DATA field). This instruction is intended for multiway branches. The EQ flag will be reset if the test field selects it and the condition passes.

If ( cond = true ) Then

PC = T\*M

Else

PC = PC + 1

18

**FORK**

IF (cond) THEN GOTO PL (data) ELSE GOTO (SREG)

Conditional branch to the address in the PL (DATA field) or the SREG. A branch to PL is taken if the condition is true and a branch to SREG if false. The EQ flag will be reset if the test field selects it and the condition passes.

If ( cond = true ) Then

PC = PL (data)

Else

PC = SREG

10135-012A

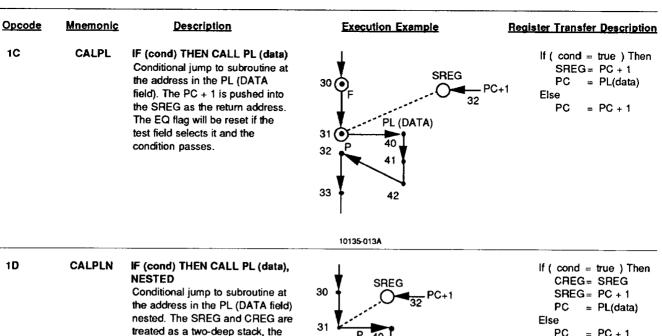

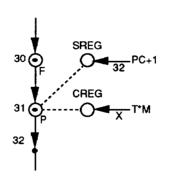

treated as a two-deep stack, the PC + 1 is pushed into the SREG as the return address, and the previous SREG value is transferred into the CREG as a nested return address. The EQ flag will be reset if the test field selects it and the condition passes.

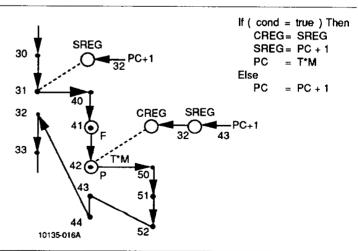

#### 1E CALTM

IF (cond) THEN CALL TM (data) Conditional jump to subroutine at the address specified by the T\*M (T[5:0] under bitwise mask from the DATA field). The PC + 1 is pushed into the SREG as the return address. The EQ flag will be reset if the test field selects it and the condition passes.

If ( cond = true ) Then SREG = PC + 1 PC  $= T^*M$ Else PC = PC + 1

10135-015A

#### 1F **CALTMN**

## IF (cond) THEN CALL TM (data) **NESTED**

Conditional jump to subroutine at the address specified by the T\*M (T[5:0] under bitwise mask from the DATA field) nested. The PC + 1 is pushed into the SREG as the return address and the previous SREG value is transferred into the CREG as a nested return address. The EQ flag will be reset if the test field selects it and the condition passes.

10135-022A

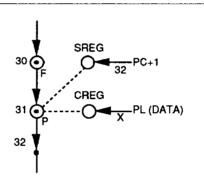

14 PSHPL IF (cond) THEN PUSH, LOAD PL (data)

Conditional push the PC + 1 into the SREG and load the CREG from the PL (DATA field).

Else PC = PC + 1

10135-023A

16 PSHTM IF (cond) THEN PUSH, LOAD TM (data)

Conditional push the PC + 1 into the SREG and load the CREG from the T\*M (T[5:0] under bitwise mask from the DATA field).

If ( cond = true ) Then CREG= T\*M

SREG = PC + 1 PC = PC + 1 Else

PC = PC + 1

10135-024A

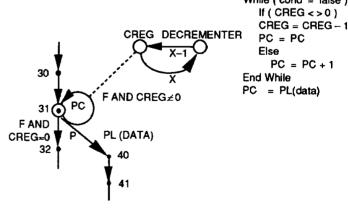

branch to the address in the PL (DATA field) is executed. If the counter becomes zero without the condition becoming true, a CONTINUE is executed. The EQ flag will be reset if the test field selects it and the condition passes.

10135-032A

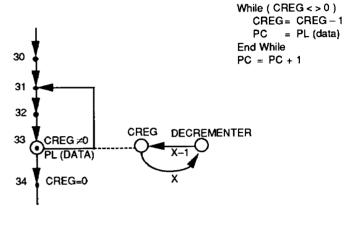

# 08 LPPL WHILE (CREG < > 0) LOOP TO PL (data) Conditional loop to the address in the PL (DATA field). This instruct is intended to be placed at the bottom of an iterative loop. If the

the PL (DATA field). This instruction is intended to be placed at the bottom of an iterative loop. If the CREG is not equal to zero, it is decremented (signifying completion of an iteration), and a branch to the PL (DATA field) (top of the loop) is executed. If the CREG is equal to zero, looping is complete and the next sequential instruction is executed. This instruction does not depend on the pass/fail condition. The EQ flag will be reset if the test field selects it and CREG is not equal to zero.

10135-034A

## OA LPPLN

## WHILE (CREG < > 0) LOOP TO PL (data) ELSE NEST

Conditional loop to the address in the PL (DATA field) nested. The SREG and CREG are treated as a two-deep nested count register, and the instruction is intended to be placed at the bottom of an "innernested" iterative loop. If the CREG is not equal to zero, the CREG is decremented (signifying completion of an interation), and a branch to the PL (DATA field) (top of the inner loop) is executed. If the CREG is equal to zero, the inner loop is complete, and the count value for the outer loop is transferred from the SREG into the CREG. This instruction does not depend on the pass/fail condition. The EQ flag will be reset if the test field selects it and the CREG is not equal to zero.

10135-035A

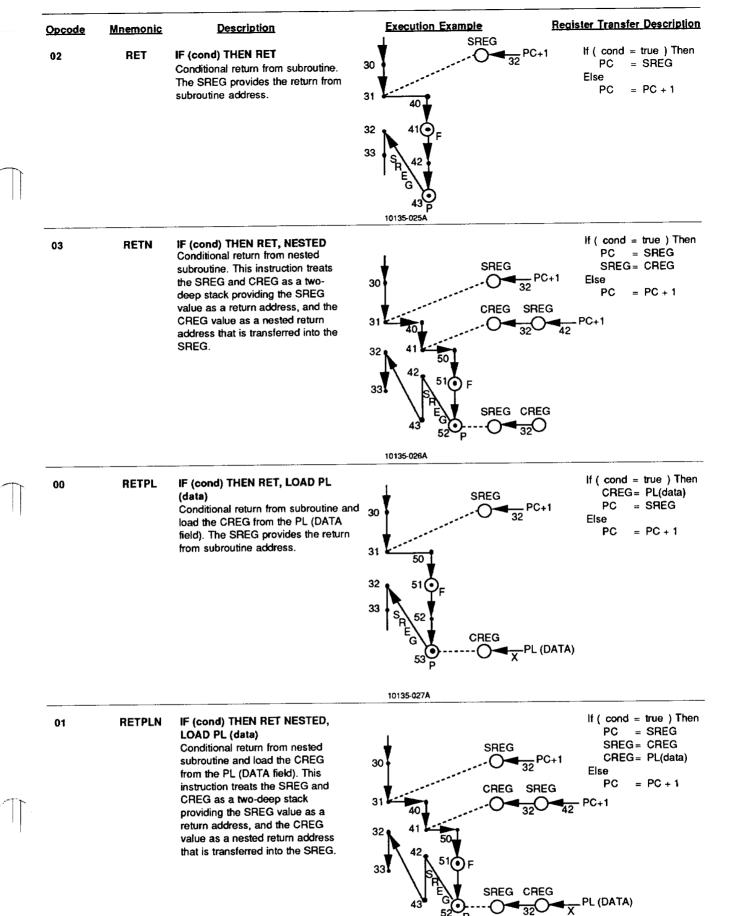

| <u>Opcode</u> | <u>Mnemonic</u> | <u>Description</u>                                                   | <b>Execution Example</b>                  | Register Transfer Description |

|---------------|-----------------|----------------------------------------------------------------------|-------------------------------------------|-------------------------------|

| OD            | CONT            | CONTINUE The next sequential instruction is fetched unconditionally. | 30 <b>(a)</b> 31 <b>(a)</b> 32 <b>(b)</b> | PC = PC + 1                   |

10135-036A

10-13 (100XX binary)

CMP

CMP TM (mask) TO PL (constant) This instruction performs bitwise exclusive-or of T\*M (T[5:0] under bitwise mask from the MASK field) with CONSTANT (P[27:22]). If T\*M equals CONSTANT, the EQ flag is set to one, which may be branched on in a following instruction. If not equal, the EQ flag is unaffected. This allows sequences of compares, in a manner analogous to sum-of-products, to be performed which can be followed by a single conditional branch if one or more of the comparisons are true. Note: The EQ flag is set to zero on reset or when EQ is selected as the test condition in a branch. Conditional returns on EQ leave the flag unchanged. Constant field bits that correspond to masked test field bits must be zero. This instruction does not depend on the pass/fail condition.

Compare T\*M and CONSTANT EQ = ((T [5:0] .AND.MASK). XNOR. CONSTANT) OR. EQ

10135-037A

# **INSTRUCTIONS BASED ON TEST CONDITIONS**

|        |          |                                                   |           | Conditio     | n Pass       | Condition Fall |           |       |            |      |              |

|--------|----------|---------------------------------------------------|-----------|--------------|--------------|----------------|-----------|-------|------------|------|--------------|

| Opcode | Mnemonic | Assembler Statement                               | PC<br>MUX | STACK        | CREG         | EQ<br>FLAG     | PC<br>MUX | STACK | EQ<br>CREG | FLAG | Notes        |

| 00     | RETPL    | IF (cond) THEN RET, LOAD<br>PL (data)             | SREG      | Hold         | Load<br>PL   | NC             | PC + 1    | Hold  | Hold       | NC   |              |

| 01     | RETPLN   | IF (cond) THEN RET<br>NESTED, LOAD PL (data)      | SREG      | Load<br>CREG | Load<br>PL   | NC             | PC + 1    | Hold  | Hold       | NC   |              |

| 02     | RET      | IF (cond) THEN RET                                | SREG      | Hold         | Hold         | NC             | PC + 1    | Hold  | Hold       | NC   |              |

| 03     | RETN     | IF (cond) THEN RET,<br>NESTED                     | SREG      | Load<br>CREG | Hold         | NC             | PC + 1    | Hold  | Hold       | NC   |              |

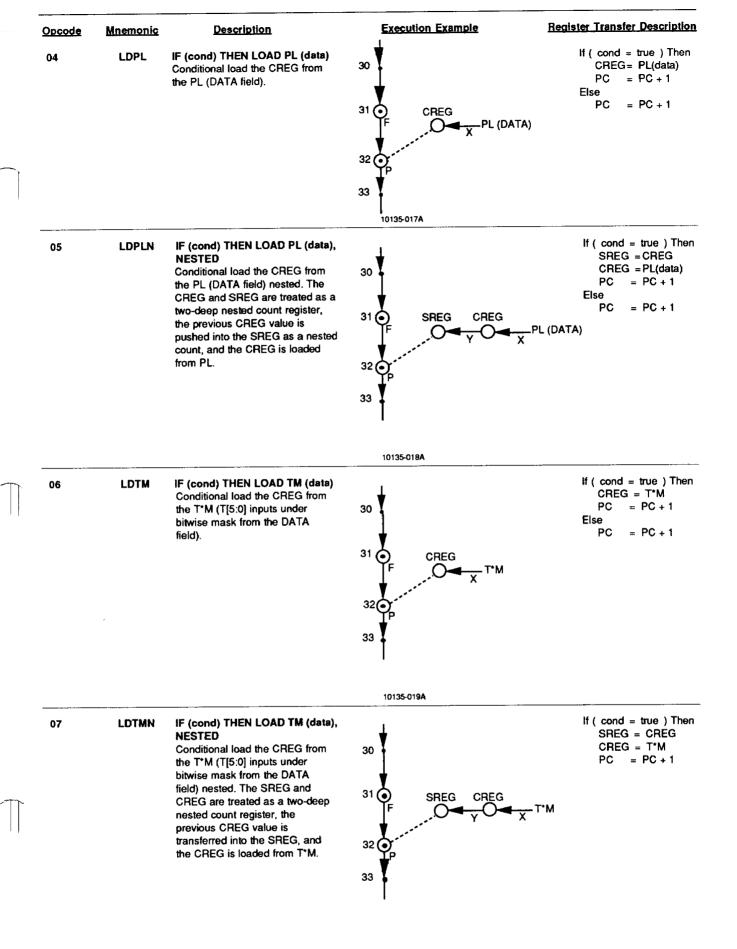

| 04     | LDPL     | IF (cond) THEN LOAD PL (data)                     | PC + 1    | Hold         | Load<br>PL   | NC             | PC + 1    | Hold  | Hold       | NC   |              |

| 05     | LDPLN    | IF (cond) THEN LOAD PL<br>(data), NESTED          | PC + 1    | Load<br>CREG | Load<br>PL   | NC             | PC + 1    | Hold  | Hold       | NC   |              |

| 06     | LDTM     | IF (cond) THEN LOAD TM (data)                     | PC + 1    | Hold         | Load<br>TM   | NC             | PC + 1    | Hald  | Hold       | NC   |              |

| 07     | LDTMN    | IF (cond) THEN LOAD TM (data), NESTED             | PC + 1    | Load<br>CREG | Load<br>TM   | NC             | PC + 1    | Hold  | Hold       | NC   |              |

| 09     | DEC      | IF (cond) THEN DEC                                | PC + 1    | Hold         | DEC          | NC             | PC + 1    | Hold  | Hold       | NC   | ] <u>.</u> . |

| 0F     | GOTOTM   | IF (cond) THEN GOTO TM (data)                     | TM        | Hold         | Hold         | Reset          | PC + 1    | Hold  | Hold       | NC   | 1            |

| 14     | PSHPL    | IF (cond) THEN PUSH, LOAD PL (data)               | PC + 1    | PC + 1       | Load<br>PL   | NC             | PC + 1    | Hold  | Hold       | NC   |              |

| 15     | PSH      | IF (cond) THEN PUSH                               | PC + 1    | PC + 1       | Hold         | NC             | PC + 1    | Hold  | Hold       | NC   |              |

| 16     | PSHTM    | IF (cond) THEN PUSH, LOAD<br>TM (data)            | PC + 1    | PC + 1       | Load<br>TM   | NC             | PC + 1    | Hold  | Hold       | NC   |              |

| 17     | PSHN     | IF (cond) THEN PUSH,<br>NESTED                    | PC + 1    | PC + 1       | Load<br>SREG | NC             | PC + 1    | Hold  | Hold       | NC   |              |

| 18     | FORK     | IF (cond) THEN GOTO PL<br>(data) ELSE GOTO (SREG) | PL        | Hold         | Hold         | Reset          | SREG      | Hold  | Hold       | NC   | 1            |

| 19     | GOTOPL   | IF (cond) THEN GOTO PL (data)                     | PL        | Hold         | Hold         | Reset          | PC + 1    | Hold  | Hold       | NC   | 1            |

| 1A     | WAIT     | IF (cond) THEN GOTO PL<br>(data) ELSE WAIT        | PL        | Hold         | Hold         | Reset          | PC        | Hold  | Hold       | NC   | 1            |

| 1C     | CALPL    | IF (cond) THEN CALL PL (data)                     | PL        | PC + 1       | Hold         | Reset          | PC + 1    | Hold  | Hold       | NC   | 1            |

| 1D     | CALPLN   | IF (cond) THEN CALL PL<br>(data), NESTED          | PL        | PC + 1       | Load<br>SREG | Reset          | PC + 1    | Hold  | Hold       | NC   | 1            |

| 1E     | CALTM    | IF (cond) THEN CALL TM (data)                     | ТМ        | PC + 1       | Hold         | Reset          | PC + 1    | Hold  | Hold       | NC   | 1            |

| 1F     | CALTMN   | IF (cond) THEN CALL TM (data), NESTED             | ТМ        | PC + 1       | Load<br>SREG | Reset          | PC + 1    | Hold  | Hold       | NC   | 1            |

# INSTRUCTIONS DEPENDENT ON CREG

|        |          |                                                    | CREG = 0  |       |              |            |           |       |      |            |       |

|--------|----------|----------------------------------------------------|-----------|-------|--------------|------------|-----------|-------|------|------------|-------|

| Opcode | Mnemonic | Assembler Statement                                | PC<br>MUX | STACK | CREG         | EQ<br>FLAG | PC<br>MUX | STACK | CREG | EQ<br>FLAG | Notes |

| 08     | LPPL     | WHILE (CREG < > 0) LOOP<br>TO PL (data)            | PC + 1    | Hold  | Hold         | NC         | PL        | Hold  | DEC  | Reset      | 2     |

| OA     | LPPLN    | WHILE (CREG < > 0) LOOP<br>TO PL (data), ELSE NEST | PC + 1    | Hold  | Load<br>SREG | NC         | PL        | Hold  | DEC  | Reset      | 2     |

| ов     | GOTOPLZ  | IF (CREG = 0) THEN GOTO<br>PL (data)               | PL        | Hold  | Hold         | Reset      | PC + 1    | Hold  | Hold | NC         | 3     |

| 0C     | DECPL    | WHILE (CREG < > 0) WAIT<br>ELSE LOAD PL (data)     | PC + 1    | Hold  | Load<br>PL   | NC         | PC        | Hold  | DEC  | NC         |       |

| 0E     | DECTM    | WHILE (CREG < > 0) WAIT<br>ELSE LOAD TM (data)     | PC + 1    | Hold  | Load<br>TM   | NC         | PC        | Hold  | DEC  | NC         |       |

## INSTRUCTIONS DEPENDENT ON TEST CONDITION AND CREG VALUE

|        | Mnemonic | Assembler<br>Statement             | CREG<br>Content |           | Conditi | on Pass |            |           | Condition | on Fall |            |       |

|--------|----------|------------------------------------|-----------------|-----------|---------|---------|------------|-----------|-----------|---------|------------|-------|

| Opcode |          |                                    |                 | PC<br>Mux | STACK   | CREG    | EQ<br>FLAG | PC<br>MUX | STACK     | CREG    | EQ<br>FLAG | Notes |

|        |          | IF (cond) THEN<br>GOTO PL (data)   | ≠0              | PL        | Hold    | Hold    | Reset      | PC        | Hold      | DEC     | NC         |       |

| 18     | DECGOPL  | ELSE WHILE<br>(CREG < > 0)<br>WAIT | = 0             | PL        | Hold    | Hold    | Reset      | PC + 1    | Hold      | Hold    | NC         | 1     |

## **UNCONDITIONAL INSTRUCTIONS**

| Opcode                  | Mnemonic | Assembler Statement            | PC<br>MUX | STACK | CREG | EQ<br>FLAG | Notes |

|-------------------------|----------|--------------------------------|-----------|-------|------|------------|-------|

| OD                      | CONT     | CONTINUE                       | PC + 1    | Hold  | Hold | NC         |       |

| 10-13 (Binary<br>100XX) | СМР      | CMP TM (mask) TO PL (constant) | PC + 1    | Hold  | Hold | Set        | 4     |

Key: PC = Program Counter

SREG = Stack Register CREG = Counter Register PL = Pipeline (data) Field

TM = Test Inputs Masked by MASK Field

DEC = Decrement = No Change NC

Notes: 1. If COND = EQ and condition PASSES, reset EQ flag. 2. If COND = EQ and CREG  $\neq$  0, reset EQ flag.

3. If COND = EQ and CREG = 0, reset EQ flag.

4. Set EQ flag if CONST field = T\*M.

## **APPLICATIONS**

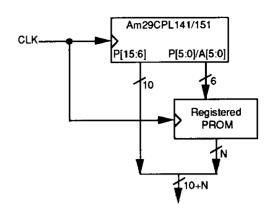

## Using the Am29CPL141 to Control External PROM

By programming the EXP bit, PC MUX is output over pins P[5:0]/A[5:0]. This feature can be used to extend the width of the output control word when external registered memories are used. In the diagram below, the Am29CPL141 controls external registered PROMs to provide an output control word (10 + N) bits wide (where N is the bit width of the PROMs).

10135-038A

## **PROGRAMMING**

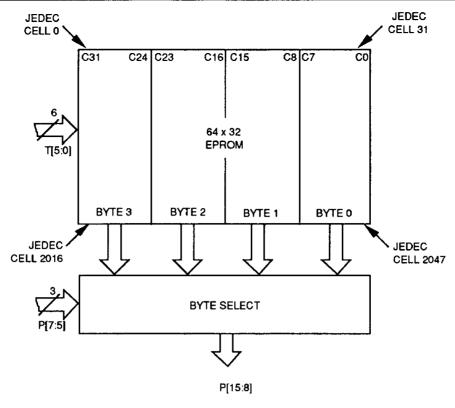

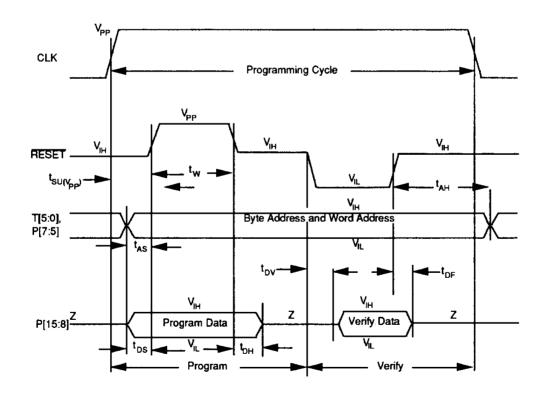

The Am29CPL141 FPC controller is programmed using a simple algorithm. The internal EPROM is organized as a 64-word by 32-bit array. The array is divided up into four bytes for programming. Data is written bytewide through pins P[15:8] using a simple sequence of voltages on two pins (CLK and RESET). The Am29CPL141 uses pins P[7:5] for byte addressing; the EPROM array resides in the four lower bytes (0 through 3), while the most significant byte (7) is reserved for user-configuration registers. Bytes, 4, 5, and 6 are not used on the Am29CPL141. Pins T[5:0] are used to address the word with T[5] being the MSB.

The Am29CPL141 programming cycle is shown in the Programming Waveform diagram. Each programming cycle consists of a program mode followed by a verify mode. To begin programming, the CLK pin is raised from a TTL level to VPP. The Am29CPL141 enters program mode and disables output pins P[15:5] and accepts these pins as data I/O and address inputs. Now that the chip is in program mode, the RESET pin controls the program and verify modes. With a TTL-level HIGH on RESET, the data I/O is high impedance, and the program data (P[15:8]) and address (P[7:5]) can be set up. The data is written into memory by applying VPP to RESET for time tw(PGMI) as described in the Programming Parameter table. RESET is then switched back to a TTL-level HIGH; the program data is removed. The verify (read) cycle begins when RESET is switched to a TTL LOW level and the data resident at the addressed byte is output on the data I/O (P[15:8]). Raising RESET back to a TTL-level HIGH completes one programming cycle.

To ensure reliable programming, if the data does not verify, the programming cycle could be repeated up to a total of 25 times. After a valid verification, a final overprogramming should be executed using a VCC = 5.0 V and an extended pulse width  $t_{\text{W(PGMM)}}$  equal to twice the sum of initial programming pulse width. At the conclusion of programming the Am29CPL141, the EPROM memory should be reverified for correct data at all addresses using two supply voltages ( $V_{\text{CC}}$  = 5.5 V and  $V_{\text{CC}}$  = 4.5 V).

## **Erasure**

In order to fully erase all memory locations, it is necessary to expose the memory array to an ultraviolet light source having a wavelength of 2537 angstroms. The minimum recommended dose (UV intensity  $\times$  exposure time) is 15 Wsec/cm². For a UV lamp with a 12 mW/cm² power rating, the exposure time would be about 30 minutes. The device should be located one inch from the source in a direct line.

It should be noted that erasure will begin with exposure to light having wavelengths less than 4000 angstroms. To prevent exposure to sunlight or fluorescent lighting, an opaque label should be affixed over the window after programming.

OTP (One-Time Programmable) Am29CPL151 devices are available in plastic and are ideal for volume production. They can be inventoried unprogrammed and used with current software revisions; there is no window to be covered to prevent light from changing data.

10135-039A

JEDEC cell number definitions:

Cell no. =  $32 \times (Row Address) + 8 \times (3 - Byte) + (7 - Bit)$ ; for Byte  $\leq 3$

Example computations:

Row 0, Byte 3, Bit 4 Cell no. = 32(0) + (3-3) + (7-4) = 3Row 63, Byte 0, Bit 0 Cell no. = 32(63) + 8(3-0) + (7-0) = 2047

The cell numbers for the configuration bits are as follows (Byte 7 only):

Sync. Registers for CC, T5 through T0 are cells 2048 through 2054

EXP is cell 2055

SSR is cell 2056

RESET is cell 2057

Figure 2. Programming

| Byte      | Byte Select |      |      |       | Bit Select |       |       |          |          |      |                  |  |  |

|-----------|-------------|------|------|-------|------------|-------|-------|----------|----------|------|------------------|--|--|

| Dyte      | P[7]        | P[6] | P[5] | P[15] | P[14]      | P[13] | P[12] | P[11]    | P[10]    | P[9] | P[8]             |  |  |

| 0         | L           | L    | L    | C7    | C6         | C5    | C4    | СЗ       | C2       | C1   | CO               |  |  |

| 1         | L           | L    | Н    | C15   | C14        | C13   | C12   | C11      | C10      | C9   | C8               |  |  |

| 2         | L           | Н    | L    | C23   | C22        | C21   | C20   | C19      | C18      | C17  | C16              |  |  |

| 3         | L           | Н    | н    | C31   | C30        | C29   | C28   | C27      | C26      | C25  | C24              |  |  |

| 4         | Н           | L    | L    | -     | -          | -     | -     | _        | _        | _    | _                |  |  |

| 5         | Н           | L    | Н    | -     | -          | -     | -     | -        | _        | -    | -                |  |  |

| 6         | Н           | Н    | L    | -     | -          | -     | -     | <u>-</u> | <u> </u> | -    | _                |  |  |

| 7 (Row 0) | н           | н    | н    | _     | cc         | T5    | T4    | Т3       | T2       | T1   | TO               |  |  |

| 7 (Row 1) | Н           | н    | Н    |       | -          |       | -     | -        | EXP      | SSR  | Reset<br>Registe |  |  |

# **PROGRAMMING PARAMETERS** $(T_A + 25^{\circ}C \pm 5^{\circ}C)$

| Parameter<br>Symbol  | Parameter<br>Description     |                         | Min. | Тур. | Max. | Unit |

|----------------------|------------------------------|-------------------------|------|------|------|------|

| V <sub>cc</sub>      | Supply Voltage               | I <sub>cc</sub> = 50 mA | 5.75 | 6.0  | 6.25 | ٧    |

| V <sub>PP</sub>      | Programming Voltage          | I <sub>pp</sub> = 30 mA | 13   | 13.5 | 14   | ٧    |

| V <sub>IH</sub>      | Input HIGH Level             |                         | 2.4  |      | 5.5  | ٧    |

| V <sub>IL</sub>      | Input LOW Level              |                         | 0    |      | 0.5  | ٧    |

| t <sub>w(PGMi)</sub> | Program Pulse Duration (Init | ial)                    | 0.95 | -    | 1.05 | ms   |

| t <sub>w(PGMf)</sub> | Program Pulse Duration (Fin  | 2.0                     |      | 50   | ms   |      |

| t <sub>AS</sub>      | Address Setup Time           |                         | 2    |      |      | μs   |

| t <sub>DS</sub>      | Data Setup Time              |                         | 2    |      |      | μs   |

| t <sub>su(VPP)</sub> | VPP Setup Time               |                         | 2    |      |      | μs   |

| t <sub>AH</sub>      | Address Hold Time            |                         | 1    |      |      | μs   |

| t <sub>DH</sub>      | Data Hold Time               |                         | 1    |      |      | μs   |

| t <sub>DV</sub>      | Data Valid from RESET LOV    | ٧                       |      |      | 100  | νs   |

| t <sub>DF</sub>      | Data Float from RESET HIG    | H                       | 0    |      | 100  | ns   |

10135040A

## **Programming Waveforms**

## **ABSOLUTE MAXIMUM RATINGS**

| Storage Temperature                | 65 to +150°C                    |

|------------------------------------|---------------------------------|

| (Ambient) Temperature Under Bias   | 55 to +125°C                    |

| Supply Voltage to Ground Potential |                                 |

| (Pin 28 to Pin 14) Continuous      | 0.5 to +7.0 V                   |

| DC Voltage Applied to Outputs      | 0.3 to +V <sub>cc</sub> + 0.3 V |

| DC Input Voltage                   | 0.3 to $+V_{cc}$ +0.3 V         |

| DC Input Current                   | 10 to +10 mA                    |

Stresses above those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

## **OPERATING RANGES**

| Ambient Temperature (T <sub>A</sub> )0 to +70°C Supply Voltage (V <sub>Cc</sub> )+4.5 to +5.5 V                           |

|---------------------------------------------------------------------------------------------------------------------------|

| Military* (M) Devices Ambient Temperature (T <sub>A</sub> )55 to +125°C Supply Voltage (V <sub>CC</sub> )+4.5 V to +5.5 V |

| Thermal Impedance Values (θ <sub>JA</sub> ), Typical                                                                      |

| 28-Pin Plastic DIP (PD3028)50°C/W                                                                                         |

| 28-Pin Ceramic DIP (CDV028, CDE028)40°C/W                                                                                 |

| 28-Pin Plastic Leaded Chip Carrier (PL028)55°C/W                                                                          |

| 28-Pin Ceramic Leadless Chip Carrier (CLV028)55°C/W                                                                       |

|                                                                                                                           |

Operating ranges define those limits between which the functionality of the device is guaranteed.

\*Military Product 100% tested at T<sub>a</sub> = +25°C, +125°C, and

DC CHARACTERISTICS over operating range unless otherwise specified (for APL F Subgroups 1, 2, 3 are tested unless otherwise noted)

| Parameter<br>Symbol         | Parameter<br>Description               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Test Condition                    | ns                    |                                          | Min. | Max.        | Uni |

|-----------------------------|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-----------------------|------------------------------------------|------|-------------|-----|

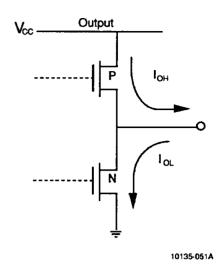

| V <sub>он</sub>             | Output HIGH Voltage                    | V <sub>CC</sub> = Min.,<br>V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | COM'L<br>MIL                      | I <sub>OH</sub> = -3  | .0 n.<br>0 mA                            | 2.4  |             | ٧   |

| <b>%</b> L                  | Output LOW Voltage                     | V <sub>cc</sub> = Min.,<br>V <sub>IN</sub> = V <sub>IL</sub> or V <sub>IH</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | COM'L                             | Ι <sub>οι</sub> 16    | amA                                      |      | 0.50        | ٧   |

| V <sub>IH</sub><br>(Note 1) | Input HIGH Level                       | Guaranteed Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Logica                            | follow for            | All Inputs                               | 2.0  |             | ٧   |

| V <sub>IL</sub><br>(Note 1) | Input LOW Level                        | Guaranteed Inpu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ogle LOV                          | altage for            | All Inputs                               |      | 0.8         | ٧   |

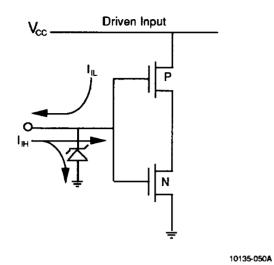

| ارر                         | Input LOW Current                      | V <sub>cc</sub> = Max V <sub>N</sub> C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <b>***</b>                        |                       |                                          |      | -10         | μΑ  |

| L <sub>H</sub>              | Input HIGH Current                     | V <sub>cc</sub> - Man                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -08 V                             |                       |                                          |      | 10          | μA  |

| l <sub>ozh</sub>            | Output Leakage Current                 | V <sub>cc</sub> = ( X.,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0.0V                              | V <sub>0</sub> =      | 2.4 V                                    |      | 10          |     |

| OZL                         | (Note 2)                               | V <sub>IH</sub> = 2.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                   | $V_0 = 0.5 \text{ V}$ |                                          |      | -10         | μΑ  |

|                             |                                        | THE PARTY OF THE P | COM'L                             | смоѕ                  | V <sub>IN</sub> = V <sub>CC</sub> or GND |      | 105         |     |

| l <sub>cc</sub>             | Power Supply Cur                       | C C C C C C C C C C C C C C C C C C C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | (T <sub>A</sub> = 0 to<br>+ 70°C) | TTL                   | V <sub>IN</sub> = 0.5 V or 2.4 V         |      | 115         | mA  |

|                             | (Note 3)                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | MiL<br>(T <sub>x</sub> = -55 to   | CMOS                  | V <sub>IN</sub> = V <sub>CC</sub> or GND |      | 120         |     |

|                             |                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | +125°C)                           | TTL                   | V <sub>IN</sub> = 0.5 V or 2.4 V         |      | 130         | mA  |