## Am29705A/707

16-Word by 4-Bit 2-Port RAM

#### DISTINCTIVE CHARACTERISTICS

- 16-word by 4-bit, 2-port RAM

- Two output ports, each with separate output control

- Separate four-bit latches on each output port (Am29707 has separate output control)

- Data output is noninverting with respect to data input

- Chip select and write enable inputs for ease in cascading

- Am29707 offers 20% improved cycle time over Am29705A when used with Am29203 in three address architecture

- Am29705A is a pin-for-pin replacement for the Am29705 but is significantly faster on critical paths

#### **GENERAL DESCRIPTION**

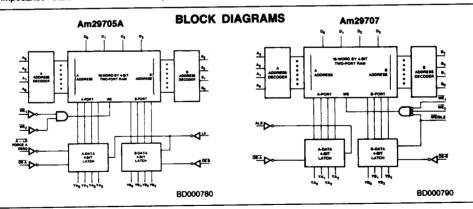

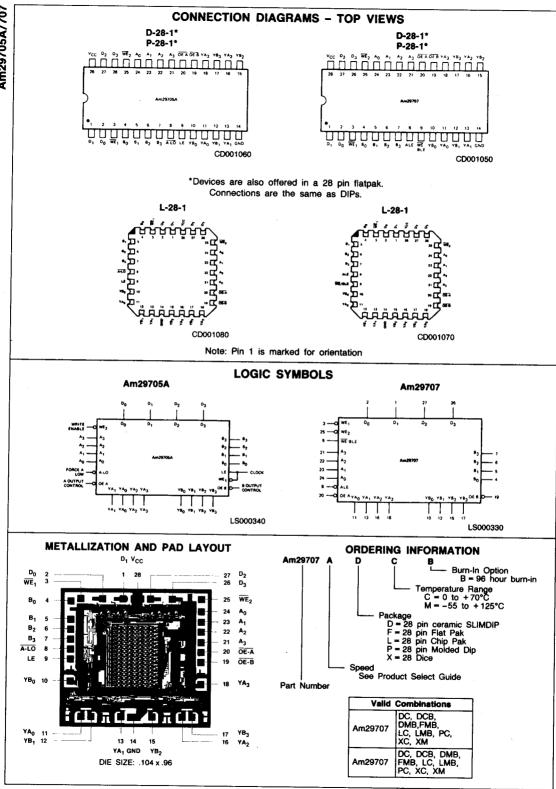

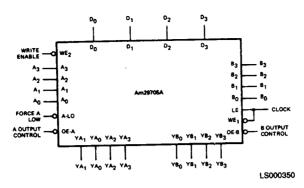

The Am29705A is a 16-word by 4-bit, two-port RAM. This RAM features two separate output ports such that any two 4-bit words can be read from these outputs simultaneously. Each output port has a four-bit Latch but a common Latch Enable (LE) input is used to control all eight latches. The device has two Write Enable (WE) inputs and is designed such that the Write Enable 1 (WE1) and Latch Enable (LE) inputs can be wired together to make the operation of the RAM appear edge triggered.

The device has a fully decoded four-bit A-address field to address any of the 16 memory words for the A-output port. Likewise, a four-bit B-address input is used to simultaneously select any of the 16 words for presentation at the B-output port. New incoming data is written into the four-bit RAM word selected by the B-address. The D inputs are used to load new data into the device.

The Am29705A features three-state outputs and several devices can be cascaded to increase the total number of memory words in the system. The A-output port is in the high-impedance state when the OE-A input is HIGH. Likewise, the B-output port is in the high-impedance state when the OE-B input is HIGH. Four devices can be paralleled using only one Am25LS139 decoder for output

The Write Enable inputs control the writing of new data into the RAM. When both Write Enable inputs are LOW, new data is written into the word selected by the B-address field. When either Write Enable input is HIGH, no data is written into the RAM.

The Am29707 is an identical circuit to the Am29705A, except each output port has a separate Latch Enable (LE) input. An extra write enable input (WE2) may be connected directly to the IEN of the Am29203 for improved cycle times over the Am29705A. The WE/BLE input can then be connected directly to system clock.

The Am29705A is a plug-in replacement for the Am29705, but is significantly faster. The Am29705A and Am29707 feature AMD's advanced ion-implanted micro-oxide (IMOX™) processing.

#### RELATED PRODUCTS

Am29751A Am2921 Am25LS138 Am25LS139 Am25LS157 Am29203 Am2902A

Bipolar PROM One-of-Eight Decoder One-of-Four Decoder Dual One-of-Four Decoder Quad 2-by-1 MUX

Four Bit Bipolar Microprocessor Slice Carry Look Ahead Generator

Am2904 Am2910A Am2914 Am2940 Am2950-54 Am29118

Status and Shift Control Unit Microprogram Controller Vectored Priority Interrupt Controller DMA Address Generator 8 Bit Bidirectional I/O Port 8 Bit Bidirectional I/O Port with ACC

#### PIN DESCRIPTION

LE

A-LO

ALE

Data Inputs  $D_0 - D_3$ New data is written into the RAM through these inputs.

The A-Address inputs

The four-bit field presented at the A inputs selects one of the 16 memory words for presentation to the A-Data Latch.

The B-Address Inputs Bo - Ba

The four bit field presented at the B inputs selects one of the 16 memory words for presentation to the B-Data Latch. The B address field also selects the word into which new data is

The Four A-Data Latch Outputs YA0-YA3 The Four B-Data Latch Outputs

YBo - YB3 WE1, WE2 Write Enables

When both Write Enables are LOW, new data is written into the word selected by the B-address field. If either Write Enable input is HIGH, no new data can be written into the memory.

A-Port Output Enable OE-A

When OE-A is LOW, data in the A-Data Latch is present at the YAi outputs. If OE-A is HIGH the YB; outputs are in the high-impedance (off) state.

ŌE-B **B-Port Output Enable**

When OE-B is LOW, data in the B-Data Latch is present at the YB; outputs. When OE-B is HIGH the YB; outputs are in the high-impedance (off) state.

Latch Enable

The LE input controls the latches for both the RAM A-output port and RAM B-output port. When the LE input is HIGH, the latches are open (transparent) and data from the RAM, as selected by the A and B address fields, is present at the outputs. When LE is LOW, the latches are closed and they retain the last data read from the RAM independent of the current A and B address field inputs. (Am29705A only.) Force A Zero

This input is used to force the outputs of the Aport latches LOW independent of the Latch Enable input or A-address field select inputs. Thus, the A-output bus can be forced LOW using this control signal. When the A-LO input is HIGH, the A latches operate in their normal fashion. Once the A latches are forced LOW, they remain LOW independent of the A-LO input if the latches are closed. (Am29705A only.)

A-Output Port Latch Enable

When ALE is HIGH, the A latch is open (transparent) and data from the RAM, as selected by the A address field, is present at the A output. When ALE is LOW, the A latch is closed and retains the last data read from the RAM independent of the current A address field input. (Am29707 only.)

WE/BLE Write Enable/B-Output Port Latch Enable

When WE/BLE is LOW together with WE1 and WE2, new data is written into the word selected by the B address field. When WE/BLE or any Write Enable input is HIGH, no data is written into the RAM.

WE/BLE also controls the 8 output port. When WE/BLE is HIGH, the B latch is open (transparent), and when this input is LOW, the B latch is closed (Am29707 only).

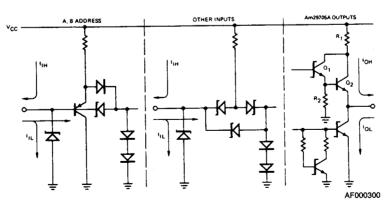

#### INPUT/OUTPUT CURRENT INTERFACE CONDITIONS

Note: Actual current flow direction shown.

03587D

#### **FUNCTION TABLES**

#### Am29705A

#### WRITE CONTROL

|                 |                 |                | RAM Outputs at Latch input |            |  |  |

|-----------------|-----------------|----------------|----------------------------|------------|--|--|

| WE <sub>1</sub> | WE <sub>2</sub> | Function       | A-Port                     | B-Port     |  |  |

| L               |                 | Write D into B | A data (A ≠ B)             | Input Data |  |  |

| L               | L               | Write D into B | (A = B) Input Data         | Input Data |  |  |

| X               | Н               | No Write       | A Data                     | B Data     |  |  |

| Н               | Х               | No Write       | A Data                     | B Data     |  |  |

H = HIGH L = LOW X = Don't Care

YA READ

| Inputs       |   |           |                  |                     |

|--------------|---|-----------|------------------|---------------------|

| OE-A A-LO LE |   | YA Output | Function         |                     |

| H            | X | Х         | Z High Impedance |                     |

| L            | ī | Х         | L                | Force YA LOW        |

| L            | H | Н         | A-Port RAM Data  | Latches Transparent |

| L            | Н | L         | NC               | Latches Retain Data |

H = HIGH X = Don't Care NC = No Change L = LOW Z = High Impedance

YB READ

| Inp     | uts |                 |                     |

|---------|-----|-----------------|---------------------|

| OE-B LE |     | YB Output       | Function            |

| Н       | Х   | Z               | High Impedance      |

| L       | Н   | B-Port RAM Data | Latches Transparent |

| L       | L   | NC              | Latches Retain Data |

H = HiGH X = Don't Care NC = No change L = LOW Z = High Impedance

#### Am29707

#### WRITE CONTROL

|                 |                 |        |                | RAM Outputs at Latch Inputs |            |  |  |  |

|-----------------|-----------------|--------|----------------|-----------------------------|------------|--|--|--|

| WE <sub>1</sub> | WE <sub>2</sub> | WE/BLE | Function       | A-Port                      | B-Port     |  |  |  |

| L               | ٦               | L      | Write D into B | A Data (A = B)              | Input Data |  |  |  |

| X               | Х               | Н      | No Write       | A Data                      | B Data     |  |  |  |

| X               | Ŧ               | Х      | No Write       | A Data                      | B Data     |  |  |  |

| I               | Х               | Х      | No Write       | A Data                      | B Data     |  |  |  |

H = HIGH L = LOW X = Don't Care

#### YA READ

| Inputs   |   |                 |                     |

|----------|---|-----------------|---------------------|

| OE-A ALE |   | YA Output       | Function            |

| Н        | Х | Z               | High Impedance      |

| L        | Н | A-Port RAM Data | Latches Transparent |

| L        | L | NC              | Latches Retain Data |

H = HIGH D = Don't Care NC = No Change L = LOW Z = High Impedance

#### YB READ

| inputs      |   |                 |                     |

|-------------|---|-----------------|---------------------|

| OE-B WE/BLE |   | YB Output       | Function            |

| Н           | Х | Z               | High Impedance      |

| L           | Н | B-Port RAM Data | Latches Transparent |

| L           | L | NC              | Latches Retain Data |

H = HIGH D = Don't Care NC = No Change L = LOW Z = High Impedance

#### **LOADING RULES (In Unit Loads)**

| Input/Output                 | Pin No.'s | Input<br>Unit Load |         | out<br>Output<br>LOW |

|------------------------------|-----------|--------------------|---------|----------------------|

| D <sub>1</sub>               | 1         | 1                  | -       |                      |

| D <sub>0</sub>               | 2         | 1                  | -       |                      |

| WE <sub>1</sub>              | 3         | 1                  | -       |                      |

| ₽0                           | 4         | 0.55               | _       | -                    |

| B <sub>1</sub>               | 5         | 0.55               | _       |                      |

| B <sub>2</sub>               | 6         | 0.55               | -       |                      |

| B <sub>3</sub>               | 7         | 0.55               |         |                      |

| <b>A-LO</b><br>(29705A Only) | 8         | 1                  | _       | -                    |

| <b>LE</b><br>(29705A Only)   | 9         | 1                  | -       | -                    |

| <b>ALE</b><br>(29707 Only    | 8         | 1                  | -       | _                    |

| <b>WE/BLE</b> (29707 Only)   | 9         | 1                  | _       | _                    |

| YB <sub>0</sub>              | 10        | -                  | 100/200 | 33                   |

| YA <sub>0</sub>              | 11        | -                  | 100/200 | 33                   |

|                 |           |                    | Fan-out        |               |  |

|-----------------|-----------|--------------------|----------------|---------------|--|

| Input/Output    | Pin No.'s | Input<br>Unit Load | Output<br>HIGH | Output<br>LOW |  |

| YB <sub>1</sub> | 12        | _                  | 100/200        | 33            |  |

| YA <sub>1</sub> | 13        | =                  | 100/200        | 33            |  |

| GND             | 14        | _                  | -              | _             |  |

| YB <sub>2</sub> | 15        |                    | 100/200        | 33            |  |

| YA <sub>2</sub> | 16        |                    | 100/200        | 33            |  |

| YB <sub>3</sub> | 17        | <del>-</del>       | 100/200        | 33            |  |

| YA <sub>3</sub> | 18        |                    | 100/200        | 33            |  |

| OE-B            | 19        | 1                  | _              |               |  |

| OE-A            | 20        | 1                  | _              |               |  |

| A <sub>3</sub>  | 21        | 0.55               | -              |               |  |

| A <sub>2</sub>  | 22        | 0.55               |                |               |  |

| A <sub>1</sub>  | 23        | 0.55               | _              |               |  |

| A <sub>0</sub>  | 24        | 0.55               | _              |               |  |

| WE <sub>2</sub> | 25        | 1                  | -              | -             |  |

| D <sub>3</sub>  | 26        | 1                  | -              |               |  |

| D <sub>2</sub>  | 27        | 1                  | -              | _             |  |

| V <sub>CC</sub> | 28        | -                  | _              |               |  |

#### **ABSOLUTE MAXIMUM RATINGS**

| Storage Temperature          | 65°C to +150°C               |

|------------------------------|------------------------------|

| Ambient Temperature with     |                              |

| Power Applied                | 55°C to +125°C               |

| Supply Voltage to Ground     |                              |

| Potential Continuous         | 0.5V to +7.0V                |

| DC Voltage Applied to OUtput |                              |

| for HIGH Output State        | 0.5V to +V <sub>CC</sub> max |

| DC Input Voltage             | 0.5V to +5.5V                |

| DC Output Current, Into      |                              |

| Output                       | 30mA                         |

| DC Input Current             | 30mA to +5.0mA               |

Stresses above those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

#### **OPERATING RANGES**

| Commercial (C) Devices             |                               |

|------------------------------------|-------------------------------|

| Temperature                        | 0°C to +70°C                  |

| Supply Voltage                     | +4.75V to +5.25V              |

| Military (M) Devices               |                               |

| Temperature                        | 55°C to +125°C                |

| Supply Voltage                     | + 4.5V to + 5.5V              |

| Operating ranges define those limi | ts over which the functional- |

| ity of the device is quaranteed.   |                               |

#### DC CHARACTERISTICS over operating range unless otherwise specified

| Symbol          | Parameter                             | Test Conditions (Note                               | 1)                               | Min | Typ<br>(Note 2) | Max   | Units |  |

|-----------------|---------------------------------------|-----------------------------------------------------|----------------------------------|-----|-----------------|-------|-------|--|

|                 |                                       | V <sub>CC</sub> = MIN.                              | MIL, I <sub>OH</sub> = -2.0mA    | 2.4 |                 |       | Volts |  |

| VOH             | Output HIGH Voltage                   | VIN = VIH or VIL                                    | COM'L, IOH # - 4.0mA             | 2.4 |                 |       | VOILS |  |

|                 |                                       | V <sub>CC</sub> = MIN.                              | IOL = 16mA (MIL)                 |     |                 | 0.5   | Volts |  |

| VOL             | Output LOW Voltage                    | VIN = VIH or VIL                                    | I <sub>OL</sub> = 20mA (COM)     |     |                 | 0.5   | Vota  |  |

| VIH             | Input HIGH Level                      | Guaranteed input logical voltage for all inputs     | HIGH                             | 2.0 |                 |       | Volts |  |

| VIL             | Input LOW Level                       | Guaranteed input logical LOW voltage for all inputs |                                  |     |                 | 8.0   | Volts |  |

| VI              | Input Clamp Voltage                   | V <sub>CC</sub> = MIN., I <sub>IN</sub> = -18mA     |                                  |     |                 | -1.5  | Volts |  |

| ħι_             | Input LOW Current                     | V <sub>CC</sub> = MAX.,<br>V <sub>IN</sub> = 0.5V   | All                              |     |                 | -0.36 | mA    |  |

| I <sub>IH</sub> | Input HIGH Current                    | V <sub>CC</sub> = MAX., V <sub>IN</sub> = 2.7V      |                                  | Ι   |                 | 20    | μА    |  |

| l <sub>1</sub>  | Input HIGH Current                    | V <sub>CC</sub> = MAX., V <sub>IN</sub> = 55V       |                                  |     |                 | 0.1   | mA    |  |

|                 | Off State (High Impedance)            | V <sub>CC</sub> = MAX.                              | V <sub>O</sub> = 2.4V            |     |                 | 20    | μΑ    |  |

| Ю               | Output Current                        | VIN = VIH or VIL                                    | V <sub>O</sub> = 0.5V            |     | <u> </u>        | -20   | , m·  |  |

| ¹sc             | Output Short Circuit Current (Note 3) | V <sub>CC</sub> = MAX.                              |                                  | -30 |                 | -85   | mA    |  |

|                 |                                       | Vcc = MAX.                                          | T <sub>A</sub> = 0°C to + 70°C   |     | -               | 210   |       |  |

| lcc             | Power Supply Current                  | (Worst case ICC is at                               | T <sub>A</sub> = 70°C            | 1   |                 | 170   | mA.   |  |

| icc             | Towar Cappiy Current                  | minimum temperature)<br>(Note 4)                    | T <sub>C</sub> = -55°C to +125°C | 1   | †               | 210   | 1     |  |

|                 |                                       |                                                     | T <sub>C</sub> = 125°C           |     | 1               | 150   | 1     |  |

#### Notes:

- For conditions shown as MIN. or MAX., use the appropriate value specified under Electrical Characteristics for the applicable device type.

- Typical limits are at V<sub>CC</sub> = 5.0V, 25°C ambient and maximum loading.

- Not more than one output should be shorted at a time. Duration of the short circuit test should not exceed one second.

- 4. All inputs grounded except  $\overline{OE-A}$  and  $\overline{OE-B} = 2.4V$ .

### SWITCHING CHARACTERISTICS over operating range unless otherwise specified

| Parameters        | From                                    | То                     | Test Conditions             | COM'L | MIL  |

|-------------------|-----------------------------------------|------------------------|-----------------------------|-------|------|

| Access Time       | A Address Stable or B<br>Address Stable | YA Stable or YB Stable | LE = HIGH                   | 25)   | (30) |

| Turn-On Time      | OE-A or OE-B LOW                        | YA or YB Stable        |                             | 20    | 20   |

| Turn-Off Time     | OE-A or OE-B HIGH                       | YA or YB Off           | C <sub>L</sub> = 5pF Note 1 | 20    | 20   |

| Reset Time        | A-LO LOW                                | YA LOW                 |                             | 20    | 20   |

| Latch Enable Time | LE HIGH                                 | YA and YB Stable       |                             | 20    | 22   |

| Transparency      | WE <sub>1</sub> and WE <sub>2</sub> LOW | YA or YB               | LE = HIGH                   | 30    | 35   |

| тапэрагопсу       | D                                       | YA or YB               | LE = HIGH                   | 30    | 35   |

Note 1. Measured from 1.5V at the input to 0.5V change in the output level.

#### MINIMUM SETUP AND HOLD TIME (in ns)

| Parameters                           | From           | То             | Test Conditions     | COM'L | MIL |

|--------------------------------------|----------------|----------------|---------------------|-------|-----|

| Data Setup Time                      | D Stable       | Either WE HIGH |                     | 12    | 15  |

| Data Hold Time                       | Either WE      | D Changing     |                     | 0     | 0   |

| Address Setup Time                   | B Stable       | Both WE LOW    |                     | 6     | 8   |

| Address Hold Time                    | Either WE HIGH | B Changing     |                     | 0     | 0   |

| Latch Close Before<br>Write Begins   | LE LOW         | WE1 LOW        | WE <sub>2</sub> LOW | 0     | 0   |

|                                      | LE LOW         | WE2 LOW        | WE <sub>1</sub> LOW | 0     | 0   |

| Address Setup<br>Before Latch Closes | A or B Stable  | LE LOW         |                     | 12    | 15  |

#### MINIMUM PULSE WIDTHS

| Parameters          | Input           | Pulse         | Test Conditions     | COM'L | MIL |

|---------------------|-----------------|---------------|---------------------|-------|-----|

| Write Pulse Width   | WE <sub>1</sub> | HIGH-LOW-HIGH | WE <sub>2</sub> LOW | 15    | 15  |

|                     | WE <sub>2</sub> | HIGH-LOW-HIGH | WE <sub>1</sub> LOW | 15    | 15  |

| A Latch Reset Pulse | Ā-LO            | HIGH-LOW-HIGH |                     | 15    | 15  |

| Latch Data Capture  | LE              | LOW-HIGH-LOW  |                     | 15    | 18  |

Note: The Am29705A meets or exceeds all of the specifications of the Am29705.

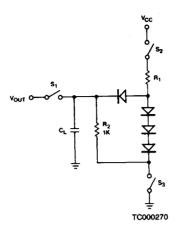

#### A. THREE-STATE OUTPUTS

$$R_1 = \frac{5.0 - V_{BE} - V_{OL}}{I_{OL} + V_{OL}/1K}$$

#### Notes:

- C<sub>L</sub> = 50pF includes scope probe, wiring and stray capacitances without device in test fixture.

- S<sub>1</sub>, S<sub>2</sub>, S<sub>3</sub> are closed during function tests and all A.C. tests except output enable tests.

- S<sub>1</sub> and S<sub>3</sub> are closed while S<sub>2</sub> is open to tp<sub>ZH</sub> test.

S<sub>1</sub> and S<sub>2</sub> are closed while S<sub>3</sub> is open for tp<sub>ZL</sub> test.

- 4. CL = 5pF for output disable tests.

#### TEST OUTPUT LOADS FOR Am29705A

| Pin #<br>(DIP) | Pin Label        | Test<br>Circuit | R <sub>1</sub> | R <sub>2</sub> |

|----------------|------------------|-----------------|----------------|----------------|

| _              | YA0-YA3, YB0-YB3 | Α               | 230            | 1k             |

#### Notes on Testing

Incoming test procedures on this device should be carefully planned, taking into account the high complexity and power levels of the part. The following notes may be useful:

- Insure the part is adequately decoupled at the test head.

Large changes in V<sub>CC</sub> current as the device switches may cause erroneous function failures due to V<sub>CC</sub> changes.

- Do not leave inputs floating during any tests, as they may start to oscillate at high frequency.

- 3. Do not attempt to perform threshold tests at high speed. Following an input transition, ground current may change by as much as 400mA in 5-8ns. Inductance in the ground cable may allow the ground pin at the device to rise by 100s of millivolts momentarily.

- 4. Use extreme care in defining input levels for AC tests. Many inputs may be changed at once, so there will be significant noise at the device pins and they may not actually reach V<sub>IL</sub> or V<sub>IH</sub> until the noise has settled. AMD recommends using V<sub>II</sub> ≤ OV and V<sub>IH</sub> ≥ 3V for AC tests.

- To simplify failure analysis, programs should be designed to perform DC, Function, and AC tests as three distinct groups of tests.

- To assist in testing, AMD offers complete documentation on our test procedures and, in most cases, can provide Fairchild Sentry programs, under license.

#### USING THE Am29705A AND Am29707

The Am2903 and Am29203 each contain only 16 scratchpad registers plus the Q register. For applications which require more than 17 registers, the register set of the Am2903 and Am29203 can be easily expanded.

For further applications information on using the Am29705A with the Am2903A, see Chapter III of *Bit Slice Microprocessor Design*, Mick and Brick, McGraw-Hill Publications.

- Use the Am29705A with the Am2903A

- Use the Am29707 with the Am29203

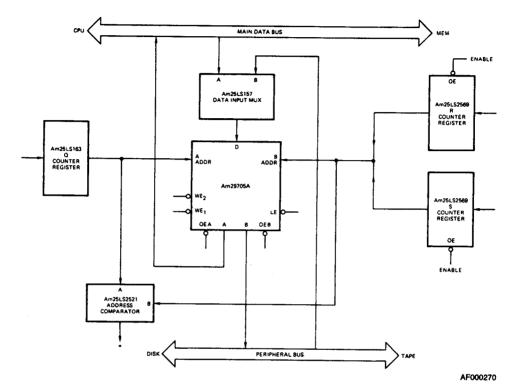

The Am29705A as a two-way interface buffer. Data may be passed between the main data bus and the peripheral data bus under I/O control. The two-port RAM allows data to be written into buffer storage from a peripheral device, using the B address port and the S counter register, while it is being read into main memory, using the A address port and the Q counter register. This simultaneous read/write capability facilitates DMA transfers because the CPU can ignore write requests

from the peripheral device. Data output from CPU to the peripheral device is handled by sequential write and read operations. Data is written into buffer storage from the CPU, using the B address port and the R counter register. It is read onto the peripheral device using the B address port and either the R register, for single word transfers, or the S register, for block transfers.

#### **APPLICATIONS (Cont.)**

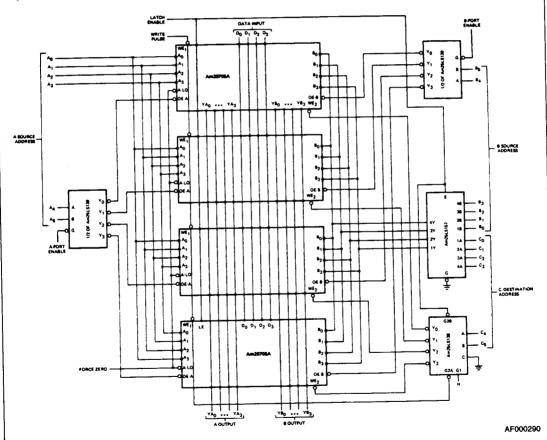

A 16-word by 4-bit two-port RAM with LE and WE $_1$  connected to make the device appear edge triggered. WE $_1$  and WE $_2$  are logically identical but are electrically slightly different. For

synchronous operation without possibility of race,  $WE_1$  should be connected to LE.

A 64-word by 4-bit three address memory. Data is read from the A address to the YA outputs and from the B address to the YB outputs while the latch enable is HIGH. When the latch enable goes LOW, the YA and YB data is held in the internal

latches, and the RAM B address is switched to the C-destination address lines. A write pulse will then deposit the input data into the location selected by the C address.

# **APPLICATIONS (Cont.)** WE FOR EXT DEST ŌĒB 1 OF 4 DECODER Am25LS139 1 OF 4 DECODER Am25LS139 CP IEN ŌĔγ AF000310

#### Am29203 EXPANDED MEMORY

A 48-word by 4-bit expanded memory for the Am29203 using the Am29707. The Am29751 PROM serves as a constant store.