# **Quad Differential Backplane Transceiver**

Advanced Micro **Devices**

## DISTINCTIVE CHARACTERISTICS

- 10 Mb data rate

- 0.45 V DC noise margin

- Biasing line terminations allow low voltage swing while maintaining high noise margin

- Pair delay 55 ns maximum

- Controlled driver skew to minimize noise

- Driver register and receiver latch with register bypass mode

- Driver output short-circuit protected to Vcc

- Outputs disabled during power-up and down

- Three-state receiver outputs maintain Hi-Z during power-up and down and over Vcc range

#### GENERAL DESCRIPTION

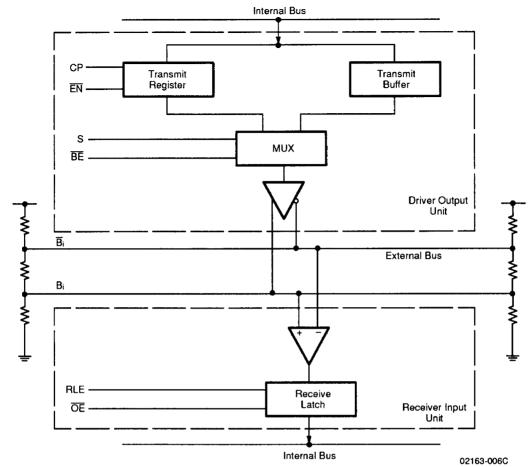

The Am26LS38 is a high performance backplane transceiver designed to integrate Schottky TTL performance, high noise immunity and wired logic capability into a low cost differential backplane structure. The resulting backplane can have up to 24 receiver unit loads in a party-line, wired-OR logic configuration, with a guaranteed fail-safe state, and operates from a single 5 V power supply.

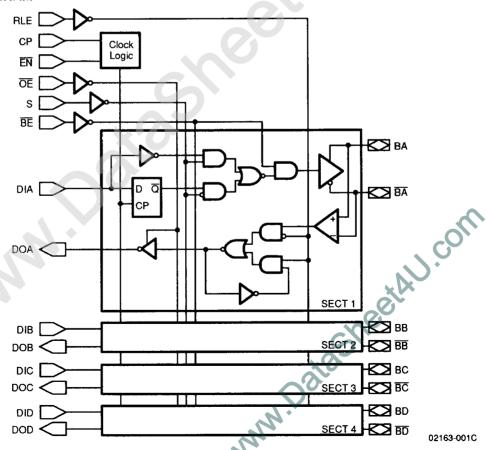

#### **BLOCK DIAGRAM**

02163-001C

Publication# 02163 Rev. C Amendment/0 Issue Date: May 1991

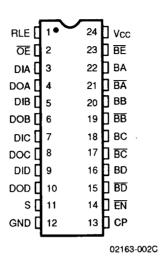

# CONNECTION DIAGRAM Top View

DIP

#### Note:

Pin 1 is marked for orientation.

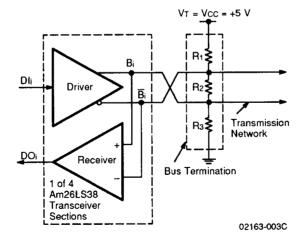

## SYSTEM CONFIGURATION DIAGRAM

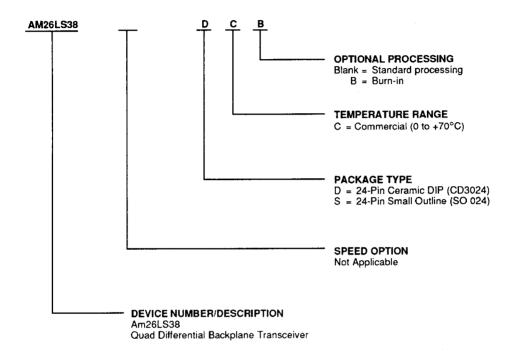

# ORDERING INFORMATION Standard Products

AMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of:

| Valid Combinations |             |  |  |  |  |  |  |

|--------------------|-------------|--|--|--|--|--|--|

| AM26LS38           | DC, DCB, SC |  |  |  |  |  |  |

#### **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations or to check on newly released combinations, and to obtain additional data on AMD's standard military grade products.

## PIN DESCRIPTION

| THE DESCRIPTION                        |                                                    |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

|----------------------------------------|----------------------------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Pin No.                                | Name                                               | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| 22, 20<br>18, 16,<br>21, 19,<br>17, 15 | BA, BB,<br>BC, BD<br>(B), BA,<br>BB, BC,<br>BD (B) | 1/0 | Paired open emitter (B <sub>i</sub> )/ open collector ( $\overline{B}_i$ ) driver outputs and receiver inputs. The driver outputs are either simultaneously active or simultaneously inactive. In the inactive state (Dl <sub>i</sub> = LOW) both drivers (B <sub>i</sub> and $\overline{B}_i$ ) are turned off and the voltage differential representing the OFF state is determined by the line terminating resistor networks. In the active state (Dl <sub>i</sub> = HIGH), both drivers are driven on and act to reverse the voltage differential across the line to produce the ON state. The open-emitter/open-collector outputs are always connected in a wried-OR (or wired-AND) configuration. A driver is disabled by making its outputs inactive. |  |  |  |  |  |

| 23                                     | BE                                                 | -   | Bus Enable operates to enable or disable all output drivers by making them inactive when $\overline{BE}$ = HIGH and controlled by data input when $\overline{BE}$ = LOW.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| 13                                     | СР                                                 | 1   | Clock Pulse input to the driver register enters data on the LOW-to-HIGH transition.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| 3, 5, 7,<br>9                          | DIA, DIB,<br>DIC,<br>DID (DI;)                     | ı   | Data inputs each driver's buffer or register. A HIGH input to DI will result in an active (ON) output. A LOW input will cause an inactive (OFF) output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| 4, 6, 8,<br>10                         | DOA, DOB,<br>DOC,<br>DOD (DOi)                     | 0   | Receiver data latch outputs. An inactive bus (OFF state) will produce a LOW DO output and an active bus (ON state) will produce a HIGH DO output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| 14                                     | ĒN                                                 | I   | Clock Enable for the driver registers. $\overline{EN}$ = LOW enables DI data to be clocked into the respective register. $\overline{EN}$ = HIGH acts to hold previous data in each register regardless of the state of CP.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| 2                                      | ŌĒ                                                 | 1   | Output Enable for the receiver latch output buffer. When $\overline{OE}$ is LOW the outputs are enabled. When $\overline{OE}$ is HIGH all receiver outputs are in the high impedance state.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| 1                                      | RLE                                                | ı   | Receiver Latch Enable for the receiver latches. When RLE is HIGH the latches are transparent. When RLE is LOW received data meeting the setup and hold requirements relative to the HIGH-to-LOW transition of RLE will be stored.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| 11                                     | S                                                  | 1   | Select input control for the drivers. When S is HIGH driver data from the registers will be selected (Register Mode). When S is LOW (Buffer Mode) the drivers respond to the DI inputs directly, bypassing the driver registers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

|     |    |    |    | Input | S  |     |    |    | (  | Outpu | ts     |                                         |

|-----|----|----|----|-------|----|-----|----|----|----|-------|--------|-----------------------------------------|

| RLE | СР | EN | ŌĒ | s     | BE | Dli | Bi | Bi | Bi | Bi    | DOi    | Function                                |

| Н   | Х  | Х  | L  | L     | L  | L   | NA | NA | L  | Н     | L      | Driver buffer mode (loop test)          |

| Н   | Х  | Х  | L  | L     | L  | Н   | NA | NA | Н  | L     | Н      |                                         |

| Н   | 1  | L  | L  | Н     | L  | L   | NA | NA | L  | Н     | L      | Driver register mode                    |

| Н   | 1  | L  | L  | Н     | L  | Н   | NA | NA | Н  | L     | Н      |                                         |

| H   | Х  | Х  | L  | Х     | Н  | Х   | L  | Н  | NA | NA    | L      | Receiver latch mode                     |

| Н   | Х  | Х  | L  | Х     | Н  | х   | н  | L  | NA | NA    | Н      |                                         |

| L   | Х  | Х  | L  | Х     | Н  | Х   | Х  | Х  | Х  | Х     | DOin-1 | Receiver in circulation                 |

| Х   | х  | х  | Н  | Х     | Н  | Х   | ×  | х  | Х  | Х     | Z      | Receiver output in high impedance state |

H = HIGH

L = LOW

↑ = LOW-to-HIGH transition of clock

DOin-1 = Previous state of DOi

Z = High impedance

X = Don't care

NA = Not applicable

#### FUNCTIONAL DESCRIPTION

The Am26LS38 represents a new approach in backplane transceiver design. Its unipolar differential signaling scheme minimizes problems associated with crosstalk and the loss of noise immunity due to common mode voltage while providing high speed, party line and wired logic capabilities.

A good ground system and shielding are the best methods for limiting noise on the backplane. Ground planes can significantly reduce inductive ground voltage ringing. Where multilayer PC backplane are not a reasonable choice, a differential bus can be created using the Am26LS38 and twisted pair or any balanced transmission medium.

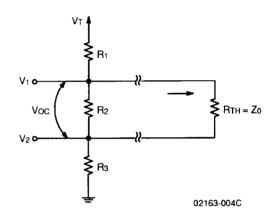

A backplane designed with an Am26LS38 has 3 main elements; 1) a driver section, 2) a receiver section, 3) and a controlled impedance differential line with a prebiasing line termination. The scheme for driver, receiver, and termination resistors is shown in Figure A.

#### **System Operation**

The system has two operational states.

- 1. Active driver outputs on

- 2. Passive driver outputs off

This 2-state (active/passive) operation makes passive or wired logic functions possible. In the passive state, the lines assume a known polarity and voltage (pre-biased bus). The passive bus state may be assigned either the false (wired-OR) or true (wired-AND) sense, potentially reducing the number of backplane signal lines.

The 2-state driver employs active pull-down (open collector) and active pull-up (open emitter) output stages (Figure A). When a driver is active, both output stages turn on. This impresses a 0.5 V minimum voltage differential on the bus, reversing the voltage across R<sub>2</sub>. In the passive mode both output stages are off. The voltage levels and polarities return to the conditions set by the pre-biasing resistive network. In either state the voltage across the differential lines are symmetrical about Vcc/2. The system achieves high speeds because the

voltage levels required to change state are very close together.

The receiver is designed with a  $\pm 50$  mV threshold voltage. This low threshold level combined with a driver output greater than 500 mV provides a high degree of tolerance to attenuation and reflection effects in the cable. Receiver hysteresis provides differential noise immunity. Without hysteresis, a small amount of noise around the switching threshold could cause errors.

Propagation delay skew (tphl – tplh) is controlled. The system allows up to 1.5 V of common mode voltage.

#### Terminating the Transmission Line or Bus

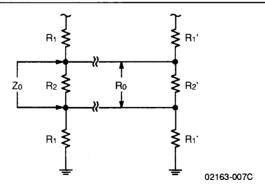

Common mode reflections in the line can be reduced significantly by symmetrically terminating the bus. This increases the tolerance to common mode noise. Centering the network at Vcc/2 (R<sub>1</sub> = R<sub>3</sub>) further improves the performance by causing all induced noise and reflections to appear as a common mode signal (Figure B).

Figure B. Termination Circuit

02163-005C

Figure A. The Scheme for Driver, Receiver, and Termination Resistors

A first order approximation of resistor values may be developed by letting the ratio of  $R_1$  to  $R_2$  be 2:1, and the Thevenin equivalent resistance of the termination equal the characteristic impedance of the line  $(Z_0)$ .

Then:

(1)

$$Voc = V_T \frac{R_2}{R_2 + 2R_1}$$

(2)

$$R_{TH} = \frac{2R_1R_2}{2R_1 + R_2}$$

From equation (1) and (2),

(3)

$$R_1 = \frac{V_T R_{TH}}{2V_{OG}}$$

(4)

$$R_2 = \frac{V_T R_{TH}}{V_T - V_{QC}}$$

If V<sub>T</sub> = 5 V, V<sub>OC</sub> = 1.0 V, and R<sub>TH</sub> =  $90\Omega$  = Z<sub>0</sub>, we can derive that R<sub>1</sub> ~220 $\Omega$ , R<sub>2</sub> ~110 $\Omega$ .

Second order adjustments require attention to unit loading factors (receiver differential input resistance is in parallel with R<sub>2</sub>), transmission rates and a host of other factors.

#### **Data Path**

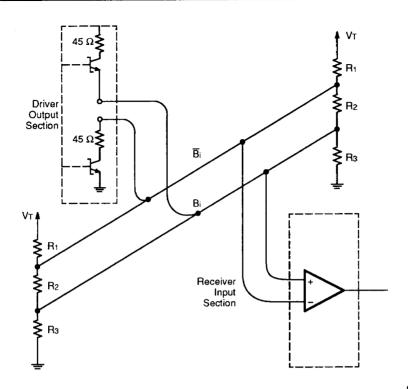

Figure C shows the data path from one driver to another receiver for one bit of the bus interface.

The transmit register or buffer and receiver latch are configured to provide two modes of operation. The register and latch can provide local storage for output and input data. In the non-storage mode the buffer input to the driver can be selected and the receiver can be wired transparent. Incorporating storage on-chip provides improved speed and lower package count without significant penalty in the non-storage mode.

Figure C. The Data Path for One Bit of the Bus Interface

**Equivalent Circuit Recommended Termination**

## Termination Resistors and Equivalent Impedance

| Zo   | R <sub>1</sub> = R <sub>1</sub> ' | $R_2 = R_2$ |

|------|-----------------------------------|-------------|

| 90Ω  | 220Ω                              | 110Ω        |

| 120Ω | 300Ω                              | 150Ω        |

Minimum line Vo (differential voltage) = 0.5 V

# **Equivalent Termination Versus DC Resistance**

| - | Zo     | R₀    |

|---|--------|-------|

|   | 88.0Ω  | 44.0Ω |

|   | 120.0Ω | 60.0Ω |

# **ABSOLUTE MAXIMUM RATINGS**

Supply Voltage 7.0 V

Common Mode Range 0 to Vcc

Differential Mode Range (REC) 0 to Vcc

Logic Inputs 5.5 V

Storage Temperature Range -65 to +150°C

Stresses above those listed under Absolute Maximum Ratings may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

# **OPERATING RANGES**

#### Commercial (C) Devices

Temperature 0 to  $+70^{\circ}$ C Supply Voltage +4.75 V to +5.25 V

Operating ranges define those limits between which the functionality of the device is guaranteed.

# DC CHARACTERISTICS over operating ranges unless otherwise specified

| Parameter<br>Symbol | Parameter Description                                                               | Test Condition                                | ıs                                                           | Min.       | Тур.        | Max.       | Unit           |

|---------------------|-------------------------------------------------------------------------------------|-----------------------------------------------|--------------------------------------------------------------|------------|-------------|------------|----------------|

| Bus Driver          | Output                                                                              |                                               |                                                              |            |             |            |                |

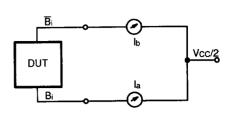

| Vo                  | Output Differential<br>Voltage (Driver Active)<br>V <sub>Bi</sub> – V <sub>Bi</sub> | BE = LOW DI <sub>i</sub> =<br>Test Circuit #1 | 0.5                                                          |            |             | ٧          |                |

| lss                 | Output Current                                                                      | DIi = HIGH                                    | la                                                           | -22.5      | <i>–</i> 55 | -115       | A              |

|                     | '                                                                                   | Test Circuit #2<br>BE = LOW                   | lb                                                           | +22.5      | +55         | +115       | mA             |

| Isc                 | Output Short Circuit<br>Current                                                     | Vcc = 5.5 V                                   |                                                              | <b>-75</b> | -150        | 250        | mA             |

| Bus Receiv          | er Input                                                                            |                                               |                                                              |            |             |            |                |

| Vтн                 | Differential Input<br>Threshold Voltage                                             | Vout = 0 to Vcc                               | <b>У</b> он                                                  | -50        | ±10         | +50        | m∨             |

| Rin                 | Input Resistance to GND                                                             | 0 ≤ Vcc ≤ Vcc                                 | Max.                                                         | 4          | 5.7         |            | kΩ             |

| Rin                 | Differential Input Resistance                                                       | 0 ≤ Vcc ≤ Vcc                                 | Max.                                                         | 8          | 11.4        |            | kΩ             |

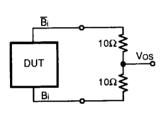

| Vos                 | Center Voltage                                                                      | Test Circuit #3                               | Active and Passive                                           | 2.0        | Vcc/2       | 3.0        | V              |

| Vos - Vos           | Center Voltage Difference (Active vs Passive)                                       | Test Circuit #3                               |                                                              | 90         | 300         | mV_        |                |

| Non-Bus Ir          | put and Outputs                                                                     |                                               |                                                              |            |             |            |                |

|                     | O. Arvit I II O. I. Veltogo                                                         | $\Delta V_{IN} = +0.1 V$                      | I <sub>OH</sub> = -15 mA                                     | 2.4        | 3.4         |            | l <sub>v</sub> |

| Vон                 | Output HIGH Voltage                                                                 | ∆VIN = +0.1 V                                 | 1он = <del>-</del> 24 mA                                     | 2.0        | 3.3         | 2.5        |                |

| Vol                 | Output LOW Voltage                                                                  | ΔVIN = −0.1 V                                 | MIL, $lo_L = 32 \text{ mA}$<br>COM'L, $lo_L = 48 \text{ mA}$ |            |             | 0.5<br>0.5 | v              |

| ViH                 | Input HIGH Voltage                                                                  | Guaranteed In<br>Voltage for All              | put Logical HIGH                                             | 2.0        |             | 0.0        | ٧              |

| VIL                 | Input LOW Voltage                                                                   | Guaranteed In<br>Voltage for All              | put Logical LOW<br>Inputs                                    |            |             | 0.8        | ٧              |

|                     |                                                                                     |                                               | Data                                                         |            | -275        | -400       | μΑ             |

| 1 <sub>Մ</sub>      | Input LOW Current                                                                   | VIN = 0.4 V                                   | Control                                                      |            | -0.65       | -1.0       | mA             |

|                     |                                                                                     |                                               | Clock                                                        |            | -0.65       | -1.0       | mA             |

| liн                 | Input HIGH Current                                                                  | V <sub>IN</sub> = 2.7 V                       |                                                              |            | 0.1         | +50        | μΑ             |

| Isc                 | Output Short Circuit Current                                                        | Vcc = 5.5 V                                   |                                                              | -75        | -150        | -250       | mA             |

| lı                  | Input Leakage Current                                                               | V <sub>IN</sub> = 5.5 V                       |                                                              |            |             | 1          | mA             |

| Vic                 | Input Clamp Voltage                                                                 | I <sub>IN</sub> = -18 mA                      |                                                              |            | -0.75       | -1.2       | V              |

|                     |                                                                                     | $V_0 = 2.4 \text{ V}$                         | <u> </u>                                                     | ļ <u> </u> | +50         | μA         |                |

| loz                 | Leakage Current Passive                                                             | $V_0 = 0.4 \text{ V}$                         |                                                              |            | <u> </u>    | -50        |                |

| Icc                 | Power Supply Current                                                                | BE, OE = HIGH                                 | <u> </u>                                                     | L          | 145         | mA         |                |

# **SWITCHING CHARACTERISTICS** (T<sub>A</sub> = +25°C, V<sub>CC</sub> = 5.0 V)

| Parameter<br>Symbol | Parameter Description                | Test Conditio   | ns                                                 | Min.              | Тур. | Max. | Unit |     |

|---------------------|--------------------------------------|-----------------|----------------------------------------------------|-------------------|------|------|------|-----|

| toba                | Dli to Bi/Bi Propagation             | Active          | BE = LOW                                           | BE = LOW          |      | 7    | 10   |     |

| tosp                | Delay                                | Passive         | S = LOW                                            | Test Circuit #1   |      | 7    | 10   | ns  |

| tcba                | CP to Bi/Bi Propagation              | Active          | BE = LOW                                           | T1 0: 11 414      |      | 10.5 | 16   | ns  |

| tcbp                | Delay                                | Passive         | S = HIGH                                           | Test Circuit #1   |      | 13   | 16   | 115 |

| <b>t</b> PA         | BE to Bi/Bi Propagation              | Active          | Dli = HIGH                                         | To at Oires it #4 |      | 8.5  | 12   | ns  |

| tpp                 | Delay                                | Passive         | S = LOW                                            | Test Circuit #1   |      | 4    | 8    |     |

| ts                  | Dli to Clock Setup Time              |                 |                                                    |                   | 5    | 2.5  |      |     |

| tн                  | Dli to Clock Hold Time               |                 |                                                    |                   | 2    | 0    |      |     |

| ts                  | EN to Clock Setup Time               |                 | BE = LOW                                           |                   | 8    | 4    |      | ns  |

| tн                  | EN to Clock Hold Time                |                 | BL = LOW                                           |                   | 0    | -4   |      | 113 |

| ts                  | Bi/Bi to RLE Setup Time              |                 | ]                                                  |                   | 5    | 2.5  |      |     |

| tн                  | Bi/B̄i to RLE Hold Time              |                 |                                                    |                   | 2    | 0.7  |      |     |

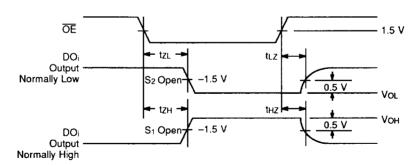

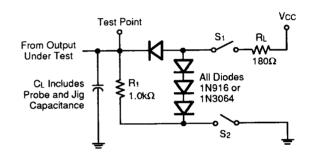

| tplz/tpHz           | <u> </u>                             |                 | C <sub>L</sub> = 50 pF                             | Test Circuit #4   |      |      | 20   | na  |

| tplz/tpHz           | OE to DOi Disable Time               |                 | C <sub>L</sub> = 5 pF                              | Test Circuit #4   |      |      | 13   | ns  |

| <b>t</b> PZL        | OF to DO Disable Time                | Test Circuit #4 |                                                    |                   |      | 17   | ns   |     |

| tezh                | OÈ to DOi Disable Time               | Test Circuit #4 |                                                    |                   | 17   |      |      |     |

| <b>t</b> PLH        | RLE to DO                            |                 | OE = LOW Test Circuit #4                           |                   | 11   | 13   | ns   |     |

| <b>t</b> PHL        | ALE IO DO                            |                 |                                                    |                   | 14   | 17   |      |     |

| tpax                | Bi/Bi to DOi                         |                 | RLE = HIGH<br>OE = LOW                             | Test Circuit #4   |      | 12   | 17   | ns  |

| <b>t</b> PLH        | 5E                                   |                 | RLE = HIGH                                         | Test Circuits     |      | 15   | 25   | ns  |

| <b>TPHL</b>         | BE to DOi Propagation Do             | eiay            | OE = LOW                                           | #1, #4            |      | 15   | 25   | 113 |

| tрцн                | Dli to DOi (Buffer Mode)             |                 | S = LOW<br>RLE = HIGH                              | Test Circuits     |      | 18   | 25   | ns  |

| tphL                | Dir to DOI (Daner Mode)              |                 | OE = LOW                                           | #1, #4            |      |      | 20   |     |

| t <sub>PLH</sub>    | CD to DO (Dociotos Mod               | - >             | S = HIGH                                           | Test Circuits     |      | 00   | 00   | ns  |

| <b>t</b> PHL        | CP to DOi (Register Mode             | e)<br>          | RLE = HIGH<br>OE = LOW                             | #1, #4            |      | 22   | 28   | 112 |

| <b>t</b> PWL        | Clock Pulse Width                    | LOW             |                                                    |                   | 10   | 3    |      |     |

| tрwн                | HIGH                                 |                 |                                                    |                   | 10   | 5    |      | ns  |

| tрwн                | RLE Pulse Width                      | HIGH            |                                                    |                   | 10   | 6    |      | ns  |

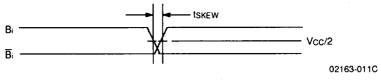

| tskew               | Propagation Delay Skew (tplh – tphl) | 7.1             | Vcc = 5 V<br>C <sub>L</sub> = 50 pF<br>Measurement | Test Circuit #1   |      | ±1   | ±5   | ns  |

# SWITCHING CHARACTERISTICS over operating range unless otherwise specified

|                       |                                                    |          |                                          | T <sub>A</sub> = 0 to<br>V <sub>CC</sub> = 5.0 |      |          |     |

|-----------------------|----------------------------------------------------|----------|------------------------------------------|------------------------------------------------|------|----------|-----|

| Parameter  <br>Symbol | Parameter Description                              |          | Test Conditi                             | Min.                                           | Max. | Unit     |     |

| toba                  | DIi to Bi/ Bi Propagation                          | Active   | BE = LOW                                 | Test Circuit #1                                |      | 12       | ns  |

| tobp                  | Delay                                              | Passive  | S = LOW                                  |                                                |      | 12       | 113 |

| tcba                  | CP to Bi/ Bi Propagation                           | Active   | BE = LOW                                 | Test Circuit #1                                |      | 20       | ns  |

| <b>t</b> CBP          | Delay                                              | Passive  | S = HIGH                                 |                                                |      | 20       |     |

| t <sub>PA</sub>       | BE to Bi/ Bi Propagation                           | Active   | Dli = HIGH                               | Test Circuit #1                                |      | 17       | ns  |

| tpp                   | Delay                                              | Passive  | S = LOW                                  |                                                |      | 12       |     |

| ts                    | Dli to Clock Setup Time                            |          |                                          |                                                | 7    |          |     |

| tн                    | Dlito Clock Hold Time                              |          |                                          |                                                | 3    |          |     |

| ts                    | EN to Clock Setup Time                             |          | BE = LOW                                 |                                                | 10   |          | ns  |

| tн                    | EN to Clock Hold Time                              |          | BC = LOW                                 |                                                | 0    |          |     |

| ts                    | B <sub>i</sub> / B̄ <sub>i</sub> to RLE Setup Time |          |                                          |                                                | 7    |          |     |

| tн                    | B <sub>i</sub> / B <sub>i</sub> to RLE Hold Time   |          |                                          |                                                | 3    |          |     |

| tpLz/tpHz             | OF to DO Disable Time                              |          | C <sub>L</sub> = 50 pF                   | Test Circuit #4                                |      | 17       | ns  |

| tplz/tpHz             | OE to DOi Disable Time                             |          | C <sub>L</sub> = 5 pF                    | Test Circuit #4                                |      | 10       |     |

| <b>t</b> PZL          | OF L BO SHALL TIME                                 |          | Test Circuit #4                          |                                                |      | 15       | ns  |

| tрzн                  | OE to DOi Enable Time                              |          | Test Officult #4                         |                                                |      | 15       |     |

| tрцн                  | 2151 22                                            |          | OE = LOW                                 | Test Circuit #4                                |      | 15       | ns  |

| <b>t</b> PHL          | RLE to DOi                                         |          | OL = LOW                                 |                                                |      | 20       |     |

| tpax                  | Bi∕ B̄i to DOi                                     |          | RLE = HIGH<br>OE = LOW                   | Test Circuit #4                                |      | 21       | ns  |

| t <sub>PLH</sub>      | BE to DO <sub>i</sub> Propagation                  |          | RLE = HIGH                               | Test Circuits                                  |      | 32       | ns  |

| t <sub>PHL</sub>      | Delay                                              |          | OE = LOW                                 | #1, #4                                         |      | <u> </u> |     |

| t <sub>PLH</sub>      |                                                    |          | S = LOW                                  | Test Circuits                                  |      |          |     |

| 11 (11                | DIi to DOi (Buffer Mode)                           |          | RLE = HIGH                               | #1, #4                                         |      | 30       | ns  |

| t <sub>PHL</sub>      |                                                    |          | OE = LOW                                 |                                                | ļ    | ļ        |     |

| tpLH                  |                                                    |          | S = HIGH                                 | Test Circuits                                  |      |          |     |

| tphL                  | CP to DOi (Register Mode)                          |          | RLE = HIGH<br><del>OE</del> = LOW        | #1, #4                                         |      | 35       | ns  |

| tpw.                  |                                                    | LOW      |                                          |                                                | 10   |          |     |

| tpwh                  | Clock Pulse Width                                  | HIGH     | 1                                        |                                                | 10   |          | ns  |

| tpwH                  | RLE Pulse Width                                    | HIGH     |                                          |                                                | 13   |          | ns  |

| tskew                 | Propagation Delay Skew (tp.h – tph.)               | i riidri | Vcc = 5 V<br>CL = 50 pF<br>Measurement \ | Test Circuit #1                                |      | ±7       | ns  |

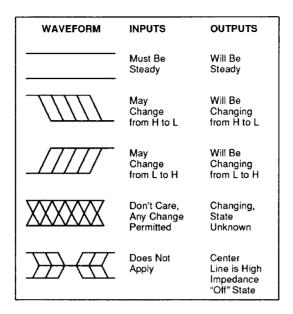

# **KEY TO SWITCHING WAVEFORMS**

KS000010

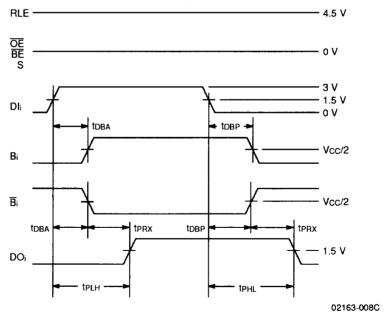

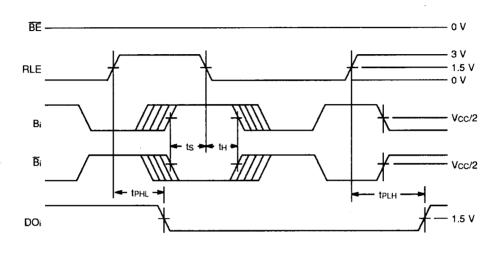

Dli to Bi, Bi, DOi (Buffer Mode)

CP to Bi, Bi, DOi (Register Mode)

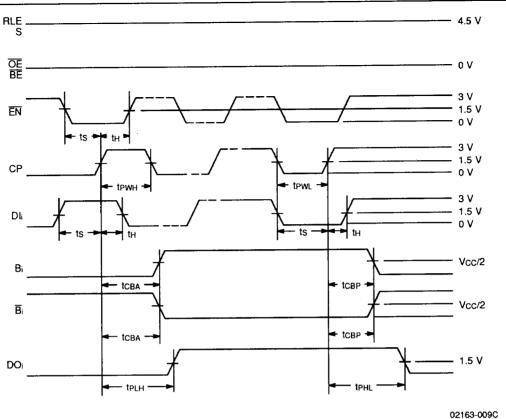

$\overline{BE}$  to  $B_i, \overline{B}_i,$  DOi (Passive and Active)

02163-010C

## **Output to Output**

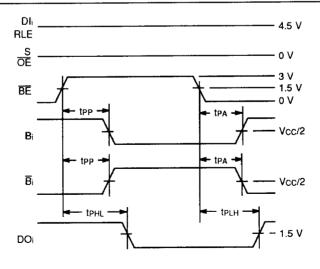

RLE to DOi

02163-013C

02163-012C

OE to DOi

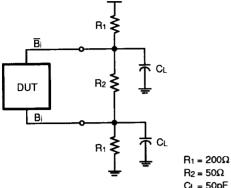

# **SWITCHING TEST CIRCUITS**

Test Circuit #2

$R_2 = 50\Omega$

CL = 50pF

02163-014C

02163-015C

Test Circuit #1

02163-017C

02163-016C

**Test Circuit #3**

**Test Circult #4**

#### Notes:

- 1. C<sub>L</sub> = 50 pF unless otherwise specified.

- 2. S1 and S2 are closed except where shown.