## **SPECIFICATIONS**

| CUSTOMER          |                    |

|-------------------|--------------------|

| CUSTOMER PART NO. |                    |

| AMP PART NO.      | AM7201280ETZQW-00H |

| APPROVED BY       |                    |

| DATE              |                    |

# ☑ Approved For Specifications □ Approved For Specifications & Sample

# **AMP DISPLAY INC**

9856 SIXTH STREET RANCHO CUCAMONGA CA 91730 TEL: 909-980-1310 FAX: 909-980-1419 WWW.AMPDISPLAY.COM

| APPROVED BY | CHECKED BY | ORGANIZED BY |

|-------------|------------|--------------|

|             |            |              |

|             |            |              |

|             |            |              |

#### **RECORD OF REVISION**

| Revision<br>Date | Page | Contents    | Editor  |

|------------------|------|-------------|---------|

| 2015/8/03        | -    | New Release | Lawlite |

|                  |      |             |         |

|                  |      |             |         |

|                  |      |             |         |

|                  |      |             |         |

|                  |      |             |         |

|                  |      |             |         |

|                  |      |             |         |

|                  |      |             |         |

|                  |      |             |         |

|                  |      |             |         |

|                  |      |             |         |

|                  |      |             |         |

|                  |      |             |         |

|                  |      |             |         |

|                  |      |             |         |

|                  |      |             |         |

|                  |      |             |         |

|                  |      |             |         |

|                  |      |             |         |

## **1. PHYSICAL SPECIFICATIONS**

| Item                | Specifications                     | Remark |

|---------------------|------------------------------------|--------|

| LCD size            | 4.99 inch(Diagonal)                |        |

| Driver element      | a-Si TFT active matrix             |        |

| Display resolution  | 720 (W) × 3(RGB) x 1280(H) dots    |        |

| Pixel Configuration | 16.7M                              |        |

| Pixel pitch         | 0.08625 (W) x0.08625 (H) mm        |        |

| Active area         | 62.1 (W) x 110.4 (H) mm            |        |

| Module size         | 65.4 (W) x 118.9 (H) × 1.45 (D) mm |        |

| Color arrangement   | R.G.B-stripe                       |        |

| LED Numbers         | 12 LED                             |        |

| Weight (g)          | TBD                                |        |

| Driver IC           | ILI9881C                           |        |

Note 1: Requirements on Environmental Protection: Q/S0002

Note 2: LCM weight tolerance: ± 5%

## 2. ABSOLUTE MAXIMUM RATINGS

**GND=0V**, Ta = 25℃

| Item                              | Symbol | MIN       | MAX       | Unit | Remark          |

|-----------------------------------|--------|-----------|-----------|------|-----------------|

| Logic Supply Voltage              | VDDI   | -0.3      | 3.3       | V    |                 |

| Dower Cupply Voltage              | VDD+   | -0.3      | 6.5       | V    |                 |

| Power Supply Voltage              | VDD-   | 0.3       | -6.5      | V    |                 |

| Logic Low Level Input<br>voltage  | VIL    | -0.3      | IOVCC*0.3 | V    |                 |

| Logic High Level Input<br>voltage | VIH    | IOVCC*0.3 | IOVCC     |      |                 |

| Back Light Forward Current        | ILED   | -         | 25        | mA   | For Each<br>LED |

| Operating Temperature             | TOPR   | -20       | 70        | °C   |                 |

| Storage Temperature               | TSTG   | -30       | 80        | °C   |                 |

## **3. ELECTRICAL SPECIFICATIONS**

| lte                             | m             | Symbol    | MIN       | TYP  | MAX       | Unit | Remark |

|---------------------------------|---------------|-----------|-----------|------|-----------|------|--------|

| Logic S<br>Volt                 |               | IOVCC     | 1.75      | 1.8  | 3.3       | V    |        |

| Power                           | Supply        | VDD+(VSP) | 4.5       | 5.0  | 6.0       | V    |        |

| Volt                            | age           | VDD-(VSN) | -6.0      | -5.0 | -4.5      |      |        |

| Input                           | Low<br>Level  | VIL       | GND       |      | 0.3*VDDI  | V    |        |

| Signal<br>Voltage High<br>Level |               | VIH       | 0.7* VDDI |      | VDDI      | V    |        |

| Output<br>Signal                | Low<br>Level  | VOL       | GND       |      | 0.2* VDDI | V    |        |

| Voltage                         | High<br>Level | Vон       | 0.8* VDDI |      | VDDI      | V    |        |

## 4 Timing Characteristics

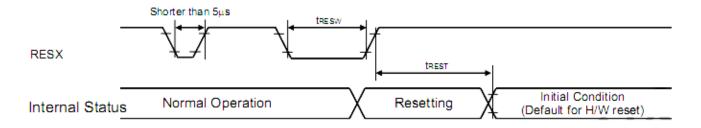

#### 4.1 Reset timing characteristics

#### Reset input timing

| Symb<br>ol        | Parameter                   | Related<br>Pins | MIN | TY<br>P | MA<br>X | Note                                           | Uni<br>t |

|-------------------|-----------------------------|-----------------|-----|---------|---------|------------------------------------------------|----------|

| t <sub>RESW</sub> | *1)Reset low Pulse<br>width | RESX            | 10  | -       | -       | -                                              | μs       |

|                   | *2)Reset complete           | -               | -   | -       | 5       | When reset applied<br>during Sleep in<br>mode  | ms       |

| t <sub>REST</sub> | time                        | -               |     | -       | 120     | When reset applied<br>during Sleep out<br>mode | ms       |

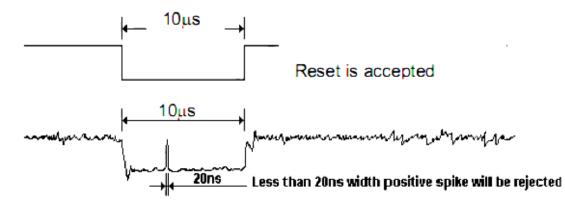

Note 1. Spike due to an electrostatic on RESX line does not cause irregular system reset according to the table below.

| RESX Pulse           | Action                                                            |

|----------------------|-------------------------------------------------------------------|

| Shorter than 5µs     | Reset Rejected                                                    |

| Longer than 10µs     | Reset                                                             |

| Between 5µs and 10µs | Reset starts<br>(It depends on voltage and temperature condition) |

Note 2. During the resetting period, the display will be blanked (The display is entering blanking sequence, which maximum time is 120 ms, when Reset Starts in Sleep Out –mode. The display remains the blank state in Sleep In –mode) and then return to Default condition for H/W reset.

Note 3. During Reset Complete Time, ID1/ID2/ID3/ID4 and VCOM value in OTP will be latched to internal register during this period. This loading is done every time when there is H/W reset complete time ( $t_{REST}$ ) within 5ms after arising edge of RESX.

Note 4. Spike Rejection also applies during a valid reset pulse as shown below:

Note 5. It is necessary to wait 5msec after releasing RESX before sending commands. Also Sleep Out command cannot be sent for 120msec.

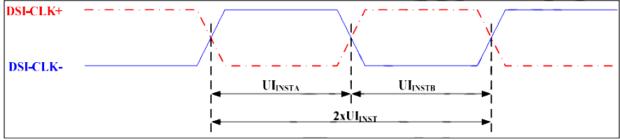

#### 4.2 High Speed Mode

| Parameter    | Symbol                                   | Parameter                        | S    | pecification | on     | Unit |

|--------------|------------------------------------------|----------------------------------|------|--------------|--------|------|

| Parameter    | Symbol                                   | Parameter                        | MIN  | TYP          | MAX    | Unit |

| High Speed m | node                                     |                                  |      |              |        |      |

| DSI-CLK+/-   | 2xUI <sub>INST</sub>                     | Double UI instantaneous          | 4    | -            | 25     | ns   |

| DSI-CLK+/-   | UI <sub>INSTA</sub> , UI <sub>INSS</sub> | UI instantaneous Halfs           | 2    | -            | 12.5   | ns   |

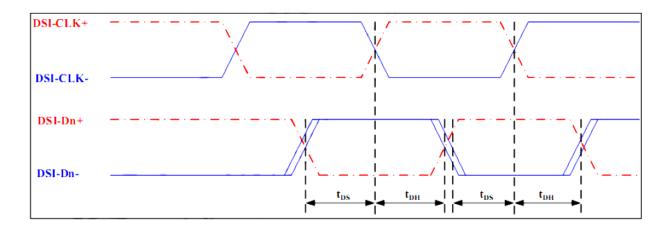

| DSI-Dn+/-    | t <sub>DS</sub>                          | Data to clock setup time         | 0.15 | -            | -      | UI   |

| DSI-Dn+/-    | t <sub>DH</sub>                          | Data to clock hole time          | 0.15 | -            | -      | UI   |

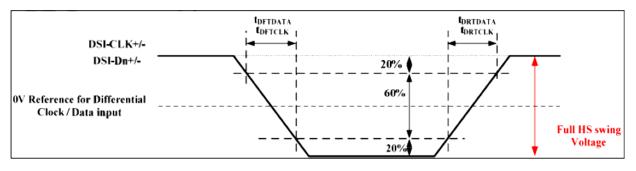

| DSI-CLK+/-   | t <sub>DRTCLK</sub>                      | Differential rise time for clock | 150  | -            | 0.31UI | ps   |

| DSI-Dn+/-    | t <sub>drtdata</sub>                     | Differential rise time for data  | 150  | -            | 0.31UI | ps   |

| DSI-CLK+/-   | t <sub>DFTCLK</sub>                      | Differential fall time for clock | 150  | -            | 0.31UI | ps   |

| DSI-Dn+/-    | t <sub>dftdata</sub>                     | Differential fall time for data  | 150  | -            | 0.31UI | ps   |

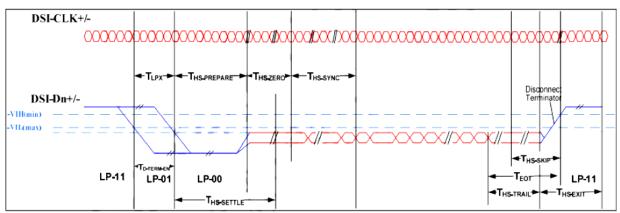

AC characteristics for MIPI-DSI High speed mode

| Parameter   | Symbol                 | Parameter                                                                        | Sp                   | oecific | ation                | Unit |

|-------------|------------------------|----------------------------------------------------------------------------------|----------------------|---------|----------------------|------|

| Falametei   | Symbol                 | Falailletei                                                                      | MIN                  | TYF     | P MAX                | Unit |

| Low Power m | ode                    |                                                                                  |                      |         |                      |      |

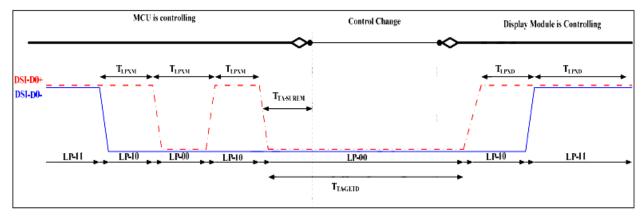

| DSI-D0+/-   | T <sub>LPXM</sub>      | Length of LP-00, LP-01,<br>LP-10 or LP-11 periods<br>MPU→ Display Module         | 50                   | -       | -                    | ns   |

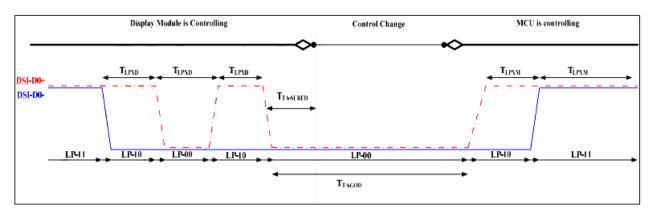

| DSI-D0+/-   | T <sub>lpxd</sub>      | Length of LP-00, LP-01,<br>LP-10 or LP-11 periods<br>Display Module→ MPU         | 58                   | -       | -                    | ns   |

| DSI-D0+/-   | T <sub>TA.SURED</sub>  | Time-out before the MPU<br>Start driving                                         | T <sub>LPXD</sub>    | -       | 2X T <sub>LPXD</sub> | ns   |

| DSI-D0+/-   | T <sub>TA.GETD</sub>   | Time to drive LP-00 by<br>Display module                                         | 5X T <sub>LPXD</sub> | -       | -                    | ns   |

| DSI-D0+/-   | T <sub>TA.GOD</sub>    | Time to drive LP-00 after<br>Turnaround request-MPU                              | 4X T <sub>LPXD</sub> | -       | -                    | ns   |

| DSI-D0+/-   | Ratio T <sub>LPX</sub> | Ratio of T <sub>LPXM</sub> / T <sub>LPXD</sub> between<br>MCU and display module | 2/3                  | -       | 3/2                  |      |

BTA from the MCU to the Display Module

BTA from the Display Module to the MCU

#### 4.4 Bursts

| Doromotor   | Symbol                                            | Parameter                                                                                                      | Spe                                                | cificati | on             | Unit |

|-------------|---------------------------------------------------|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------|----------|----------------|------|

| Parameter   | Symbol                                            | Farameter                                                                                                      | MIN                                                | TYP      | MAX            | Unit |

| Hight Speed | Data Transm                                       | ission Bursts                                                                                                  |                                                    |          |                |      |

| DSI-Dn+/-   | T <sub>LPX</sub>                                  | Length of any low-power state<br>period                                                                        | 50                                                 | -        | -              | ns   |

| DSI-Dn+/-   | T <sub>HS.PREPARE</sub>                           | Time to drive LP-00 to prepare for HS transmission                                                             | 40ns+<br>4UI                                       | -        | 85ns+<br>6UI   | ns   |

| DSI-Dn+/-   | T <sub>HS.PREPARE</sub><br>+ T <sub>HS.ZERO</sub> | T <sub>HS.PREPARE</sub> + time to drive HS-0<br>before the sync sequence                                       | 145ns+<br>10UI                                     | -        | -              | ns   |

| DSI-Dn+/-   | T <sub>D.TERM.EN</sub>                            | Time to enable Data Lane<br>receiver line termination<br>measured from when Dn crosses<br>V <sub>IL(max)</sub> | Time for<br>Dn to<br>reach<br>V <sub>TERM.EN</sub> | -        | 35ns+<br>4UI   | ns   |

| DSI-Dn+/-   | T <sub>HS.SKIP</sub>                              | Time-out at RX to ignore<br>transition period of EoT                                                           | 40                                                 | -        | 55ns+<br>4UI   | ns   |

| DSI-Dn+/-   | T <sub>HS.TRAIL</sub>                             | Time to drive flipped differential state after last payload data bit of a HS transmission burst                | max(8UI<br>,60ns+<br>4UI)                          | -        | -              | ns   |

| DSI-Dn+/-   | T <sub>HS.EXIT</sub>                              | Time to drive LP-11 after HS<br>burst                                                                          | 100                                                | -        | -              | ns   |

| DSI-Dn+/-   | Τ <sub>ΕοΤ</sub>                                  | Time from start of T <sub>HS-TRAIL</sub> period to start of LP-11 state                                        | -                                                  | -        | 105ns<br>+12UI | ns   |

High Speed Data Transmission Bursts

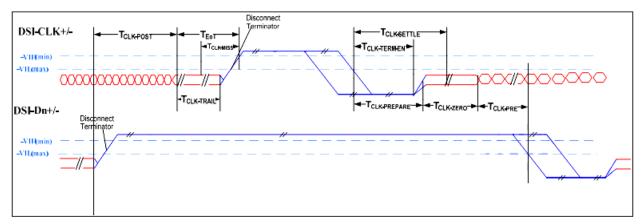

| Parameter                                                                | Symbol                                                 | Parameter                                                                                                                          | Spe                                                | Unit |                |      |  |  |  |

|--------------------------------------------------------------------------|--------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|------|----------------|------|--|--|--|

| Farameter                                                                | Symbol                                                 | Farameter                                                                                                                          | MIN                                                | TYP  | MAX            | Unit |  |  |  |

| Switching the clock Lance between clock Trans mission and Low Power Mode |                                                        |                                                                                                                                    |                                                    |      |                |      |  |  |  |

| DSI-CLK+/-                                                               | T <sub>CLK-POST</sub>                                  | Time that the transmitter shall<br>continue sending HS clock after<br>the last associated Data Lane<br>has transitioned to LP mode | 60ns<br>+52UI                                      | -    | -              | ns   |  |  |  |

| DSI-CLK+/-                                                               | T <sub>CLK-PRE</sub>                                   | Time that the HS clock shall be<br>driven prior to any associated<br>Data Lane beginning the<br>transition from LP to HS mode      | 8                                                  | -    | -              | UI   |  |  |  |

| DSI-CLK+/-                                                               | T <sub>CLK.PREPAR</sub><br>E                           | Time to drive LP-00 to prepare<br>for HS clock transmission                                                                        | 38                                                 | -    | 95             | ns   |  |  |  |

| DSI-CLK+/-                                                               | T <sub>CLK.TERM.E</sub><br>N                           | Time to enable Clock Lane<br>receiver line termination<br>measured from when Dn<br>crosses V <sub>IL(max)</sub>                    | Time for<br>Dn to<br>reach<br>V <sub>TERM.EN</sub> | -    | 38             | ns   |  |  |  |

| DSI-CLK+/-                                                               | T <sub>CLK.PREPAR</sub><br>E<br>+T <sub>CLK.ZERO</sub> | T <sub>CLK.PREPARE</sub> + time for lead HS-0<br>drive period before starting<br>Clock                                             | 300                                                | -    | -              | ns   |  |  |  |

| DSI-CLK+/-                                                               | T <sub>CLK.TRAIL</sub>                                 | Time to drive HS differential state after last payload clock bit of a HS transmission burst                                        | 60                                                 | -    | -              | ns   |  |  |  |

| DSI-CLK+/-                                                               | Τ <sub>ΕοΤ</sub>                                       | Time from start of T <sub>CLK.TRAIL</sub><br>period to start of LP-11 state                                                        | -                                                  | -    | 105ns<br>+12UI | ns   |  |  |  |

Switching the clock Lane between clock Transmission and Low Power Mode

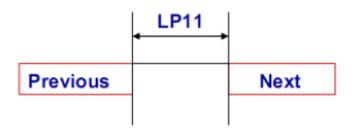

#### 4.5 LP-11 between High Speed and Low Power Modes

D SI-D0 High Speed or Low Power modes are starting or finishing from/to Stop State (SS, LP-11) when 4 different combinations, what are listed below, are possible:

- 1. High Speed Mode => Stop State (SS, LP-11) => High Speed Mode

- 2. High Speed Mode => Stop State (SS, LP-11) => Low Speed Mode

- 3. Low Speed Mode => Stop State (SS, LP-11) => High Speed Mode

- 4. Low Speed Mode => Stop State (SS, LP-11) => Low Speed Mode

The Low Power Mode is also including 2 different functions:

- 1. Escape

- 2. Bus Turnaround (BTA)

| Next        | Escape        | e mode | HSDT          |     | BTA           |     |

|-------------|---------------|--------|---------------|-----|---------------|-----|

| Previous    | Min           | Max    | Min           | Max | Min           | Max |

| Escape mode | 100ns         | -      | 100ns         | -   | 100ns         | -   |

| HSDT        | 60ns+<br>52UI | -      | 60ns+<br>52UI | -   | 60ns+<br>52UI | -   |

| BTA         | 100ns         | -      | 100ns         | -   | 100ns         | -   |

#### Stop State (SS, LP-11) Timings from previous mode to Next mode

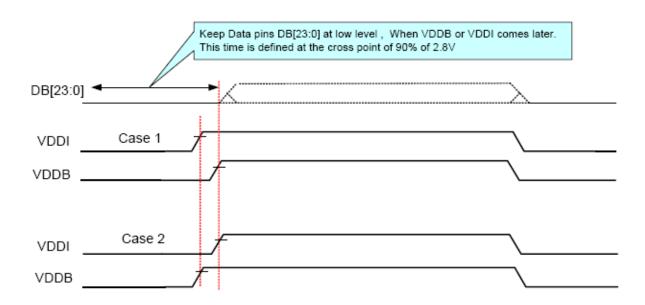

#### 4.6 POWER ON/OFF SEQUENCE

VDDI and VDDA can be applied (or powered down) in any order. During the power off sequences, if LCD is in the Sleep Out mode, VDDA and VDDI must be powered down with minimum 120msec, and if LCD is in the Sleep In mode, VDDA and VDDI can be powered down with minimum 0msec after RESX has been released. CSX can be applied at any timing or can be permanently grounded. RESX has priority over CSX.

#### Note:

- 1. There will be no damage to ILI19806C if the power sequences are not met.

- 2. There will be no abnormal visible effects on the display panel during the Power On/Off Sequences.

- There will be no abnormal visible effects on the display between end of Power On Sequence and before receiving Sleep Out command. Also between receiving Sleep In command and Power Off Sequence.

- 4. If RESX line is not held stable by host during Power On Sequence as defined in Sections 13.1 and 13.2, then it will be necessary to apply a Hardware Reset (RESX) after Host Power On Sequence is complete to ensure correct operation. Otherwise function is not guaranteed.

5. Keep data pins DB[23:0] at low level, when VDDB or VDDI comes later

## 5 Input/Output Terminals

| Pin No. | Symbol       | I/O | Function                     |  |

|---------|--------------|-----|------------------------------|--|

| 1       | GND          | р   | Power ground                 |  |

| 2       | LEDK2        | Р   | Cathode for LED backlighting |  |

| 3       | LEDK1        | р   | Cathode for LED backlighting |  |

| 4       | LEDA         | Р   | Anode for LED backlighting   |  |

| 5       | GND          | р   | Power ground                 |  |

| 6       | CABC         | Р   | CABC function enable         |  |

| 7       | GND          | Р   | Power ground                 |  |

| 8       | TE           | I/O |                              |  |

| 9       | ID_GPIO(GND) | I   | ID                           |  |

| 10      | RESET        | Ι   | Reset pin                    |  |

| 11      | ID_ADC       | I   | ID                           |  |

| 12      | IOVCC(1.8V)  | Р   | 1.8V                         |  |

| 13      | GND          | Р   | Power ground                 |  |

| 14      | VDD(+5V)     | Ρ   | +5V                          |  |

| 15      | GND          | Р   | Power ground                 |  |

| 16      | VDD(-5V)     | Р   | -5V                          |  |

| 17      | GND          | Ρ   | Power ground                 |  |

| 18      | OTP          | I/O | NC                           |  |

| 19      | GND          | Ρ   | Power ground                 |  |

| 20      | LAN3_P       | Ι   | MIPI data input              |  |

| 21      | LAN3_N       | Ι   | MIPI data input              |  |

| 22      | GND          | Ρ   | Power ground                 |  |

| 23 | LAN2_P | I | MIPI data input |

|----|--------|---|-----------------|

| 24 | LAN2_N | Ι | MIPI data input |

| 25 | GND    | Р | Power ground    |

| 26 | CLK_P  | I | MIPI CLK input  |

| 27 | CLK_N  | Ι | MIPI CLK input  |

| 28 | GND    | Ρ | Power ground    |

| 29 | LAN1_P | I | MIPI data input |

| 30 | LAN1_N | Ι | MIPI data input |

| 31 | GND    | Ρ | Power ground    |

| 32 | LAN0_P | Ι | MIPI data input |

| 33 | LAN0_N | I | MIPI data input |

| 34 | GND    | Ρ | Power ground    |

Note1 : Please add the FPC connector type and matched one if necessary.

## **6** Optical Characteristics

| ltem           |         | Symbol           | Condition          | Min   | Тур   | Мах   | Unit              | Remark   |

|----------------|---------|------------------|--------------------|-------|-------|-------|-------------------|----------|

|                |         | θΤ               |                    |       | 80    |       | Deerroe           |          |

|                |         | θB               |                    |       | 80    |       |                   |          |

| View Angles    |         | θL               | CR≧10              |       | 80    |       | Degree            | Note2,3  |

|                |         | θR               |                    |       | 80    |       |                   |          |

| Contrast Ratio | )       | CR               | θ=0°               | 600   | 800   |       |                   | Note 3   |

| Baananaa Tim   |         | T <sub>ON</sub>  | <b>25</b> ℃        |       | 25    |       | 122.0             | Note 4   |

| Response Time  |         | T <sub>OFF</sub> | 25 (               | -     | 35    |       | ms                | NOLE 4   |

|                | White X |                  | 0.26               | 0.29  | 0.32  |       | Note 1,5          |          |

|                |         | у                | Backlight is<br>on | 0.28  | 0.30  | 0.34  |                   |          |

|                | Red     | х                |                    | 0.571 | 0.621 | 0.671 |                   | Note 1,5 |

| Chromaticity   |         | У                |                    | 0.271 | 0.321 | 0.371 |                   |          |

| Chilomaticity  | Green   | х                |                    | 0.261 | 0.311 | 0.361 |                   | Note 1,5 |

|                | Green   | У                |                    | 0.579 | 0.629 | 0.679 |                   |          |

|                | Blue    | x                |                    | 0.105 | 0.155 | 0.205 |                   | Note 1,5 |

|                | Diue    | У                |                    | 0.002 | 0.052 | 0.102 |                   |          |

| Uniformity     |         | U                |                    | 70    | 80    |       | %                 | Note 6   |

| NTSC           |         |                  |                    |       | 70    |       | %                 | Note 5   |

| Luminance      |         | L                |                    | 400   | 430   |       | cd/m <sup>2</sup> | Note 7   |

Test Conditions:

1. IF= 20mA, and the ambient temperature is  $25^{\circ}$ C.

2. The test systems refer to Note 1 and Note 2.

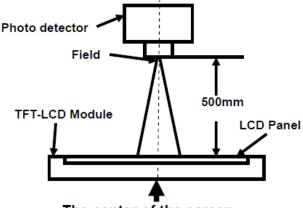

Note 1: Definition of optical measurement system.

The optical characteristics should be measured in dark room. After 5 Minutes operation, the optical

properties are measured at the center point of the LCD screen. All input terminals LCD panel must

be ground when measuring the center area of the panel.

| Item           | Photo detector | Field |  |

|----------------|----------------|-------|--|

| Contrast Ratio |                |       |  |

| Luminance      |                | 1°    |  |

| Chromaticity   | SR-3A          | I     |  |

| Lum Uniformity |                |       |  |

| Response Time  | BM-7A          | 2°    |  |

The center of the screen

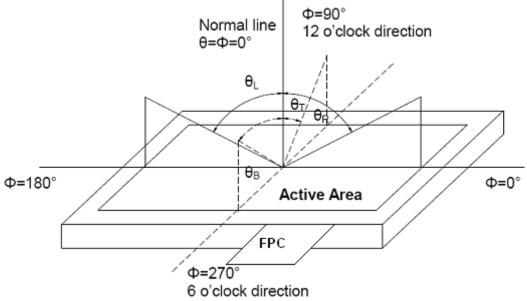

Note 2: Definition of viewing angle range and measurement system.

viewing angle is measured at the center point of the LCD by CONOSCOPE(ergo-80).

Note 3: Definition of contrast ratio

$Contrast ratio (CR) = \frac{Luminance measured when LCD is on the "White" state}{Luminance measured when LCD is on the "Black" state}$

"White state ": The state is that the LCD should drive by Vwhite.

"Black state": The state is that the LCD should drive by Vblack.

Vwhite: To be determined Vblack: To be determined.

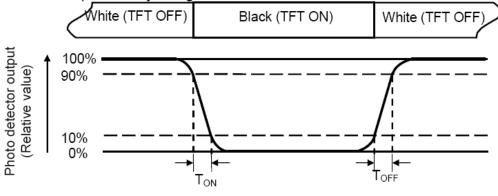

Note 4: Definition of Response time

The response time is defined as the LCD optical switching time interval between "White" state and "Black" state. Rise time ( $T_{ON}$ ) is the time between photo detector output intensity changed from 90% to 10%. And fall time ( $T_{OFF}$ ) is the time between photo detector output intensity changed from 10% to 90%.

Note 5: Definition of color chromaticity (CIE1931)

Color coordinates measured at center point of LCD.

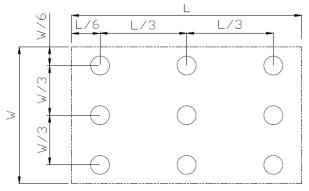

Note 6: Definition of Luminance Uniformity

Active area is divided into 9 measuring areas (Refer Fig. 2). Every measuring point is placed at the center of each measuring area.

Luminance Uniformity (U) = Lmin/ Lmax

L-----Active area length W----- Active area width

Lmax: The measured Maximum luminance of all measurement position.

Lmin: The measured Minimum luminance of all measurement position.

Note 7: Definition of Luminance:

Measure the luminance of white state at avg of 9 point.

## 7 Environmental / Reliability Test

| No | Test Item                              | Test condition                                                                                                        | Remark      |

|----|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-------------|

| 1  | High Temperature Storage               | 70℃±2℃96Hrs                                                                                                           |             |

| 2  | Low Temperature Storage                | -30℃±2℃ 96Hrs                                                                                                         |             |

| 3  | High Temperature Operation             | 60℃±2℃96Hrs                                                                                                           |             |

| 4  | Low Temperature Operation              | -20℃±2℃ 96Hrs                                                                                                         |             |

|    | High Temperature & Humidity<br>Storage | 60℃±2℃ 90%RH 96Hrs                                                                                                    |             |

| 6  | Temperature Cycle                      | - 30° ← →70° C<br>30 min 30 min<br>after 32 cycle, change time 30 s<br>Restore 2H at 25° C                            |             |

| 7  | Vibration Test                         | Power off<br>Frequency:10Hz~55Hz<br>Stroke:1.5mm<br>Sweep:10Hz~55Hz~10Hz, 120min<br>±x,±Y,±Z for each direction       | 1Carton-box |

| 8  | Shock Test                             | Half-sine wave,600m/s2,6ms<br>±x,±Y,±Z 3 times,for each<br>direction                                                  | -           |

| 9  | Drop Test(package state)               | 800mm, concrete floor,1corner,<br>3edges, 6 sides each time                                                           | 1Carton-box |

| 10 | ESD Sensitivity test                   | 5points/panel<br>Contact ±4KV <sup>,</sup> 150PF/330 <sup>,</sup><br>5times<br>Air ±8KV,150PF/330 <sup>,</sup> 5times | -           |

NOTE:

1.Sample size for each test item is 5~10pcs.

2.For Damp Proof Test, Pure water(Resistance  $\!>\!10M\Omega)$  should be used.

3.In case of malfunction defect caused by ESD damage, if it would be recovered to normal

state after resetting, it would be judge as a good part. Using ionizer(an antistatic blower)

is recommended at working area in order to reduce electro-static voltage. When removing protection film from LCM panel, peel off the tag slowly( recommended more than one second) while blowing with ionizer toward the peeling face to minimize ESD which may damage electrical circuit.

4. EL evaluation should be excepted from reliability test with humidity and temperature: Some defects such as black spot/blemish can happen by natural chemical reaction with humidity and Fluorescence EL has.

5. Polarizer test criteria

a. when testing avoid samples take out then return, It can cause water coagulation in Polarizer. Increase the distance of samples , And put samples before the wind.

b. When the samples are put into the test, put them upright so that the glasses keep spaces between them each other. (Picture 9.1)

Picture 9.1

Picture 9.2

c. Put samples into testing machine as small as possible so that it is drafty.

d. Do not put samples under wick because water will fall.( Picture 9.2)

e. Do not open testing machine except for taking them out in order to prevent moisture condensation.

6. Please use automatic switch menu(or roll menu) testing mode when test operating mode

7. The inspection terms after reliability test, as below

| ITEM       | Inspection standard |

|------------|---------------------|

| Contrast   | CR>50%              |

| IDD        | IDD<200%            |

| Brightness | Brightness>60%      |

| Color Tone | Color Tone+/-0.05   |

## 8. OUTLINE DIMENSION